Abstract

Developing of new photovoltaic inverter topologies is received more attention in the last few years. In particular, designing an active neutral-point-clamping inverter type structure is quite popular for PV applications. The output voltage is always half of the input voltage (vin), which further increases the voltage rating of dc-link capacitors in the conventional three-level ANPC. To rectify the above problem and increase the output voltage by reducing dc-link capacitors voltage rating, a new boost type seven-level ANPC inverter topology is proposed. The proposed topology consists of seven switches and one floating capacitor. The floating capacitor voltage is self-balanced, and the output voltage is 1.5 times higher than the input voltage. A detailed comparison for some power components, power loss and cost with other existing topologies are presented. Further, the proposed topology is validated in a prototype hardware setup for different load values.

Similar content being viewed by others

Introduction

The photovoltaic (PV) inverter structure is considerably simple yet highly efficient because the researchers develop a new design with fewer components and compact size. Among the various existing PV inverters, the transformerless (TL) inverter has more advantages like single-stage operation, no bulky transformers and less leakage current. The PV-TL inverters start from a few hundred to kilowatts ranges. Nevertheless, the novel topologies are often developed for single-phase grid-connected systems, more suitable for rooftop utility PV applications. It is worth mentioning that the TL inverters with the Switched-Capacitor Multilevel Inverter (SCMLI) topologies are paid more attention among the researchers to generating a high number of voltage levels with reduced switches and dv/dt stress1,2,3. The researchers develop a new SCMLI topology to produce better efficiency compared to other existing SCMLI topologies. However, in ANPC type topologies, output voltage (vo) is always half of the input voltage (vin) due to the mid-point clamping of the dc-link capacitors and the load, which increases the voltage rating of dc-link capacitors. Thus, to reduce the voltage rating and size of the dc-link capacitors, the floating capacitors (FCs) are used as a voltage multiplier to boost the output voltage. Many switched capacitor topologies are presented in the literature, and few are discussed here. In Ref.4, a new switched capacitor topology with a high inductive load is proposed for a fundamental frequency of 1 kHz. This topology produces a 7L level output voltage with a gain of 1:3. It also can be extended to the "m" level. Another topology with the same structure in which few IGBTs are replaced with power diodes is presented5. In Ref.6, a hybrid SCMLI is presented with reduced switches and the possibility of generating m number of levels. A newly developed topology in Ref.7 reduces switch count and can be extended by cascading the proposed basic unit.

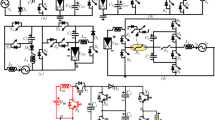

The topologies presented in Refs.4,5,6,7,8 have the advantage of self-voltage balancing and boosting capability with a maximum of gain 1:3. However, these topologies needed a separate isolated dc source for a three-phase inverter system due to the non-availability of a common dc bus. Further, the stress on the switches is equal to 3vin. A single floating capacitor with ten IGBTs is used in Ref.9. The output voltage gain is 1.5 times higher than the input voltage. A new seven-level inverter topology with a logic form equation is proposed in the Ref.10. The rating of the floating capacitor voltage is vin/4. This topology needs an additional sensor to balance the capacitor voltage, increasing the inverter's complexity. New self-balanced neutral point clamped type SCMLI topologies are presented in Refs.11,12,13,14. A new 5L ANPC type inverter topology with a voltage boosting gain of 1:1 is presented in Ref.10 to overcome these challenges (see Fig. 1a). In this, seven switches and one floating capacitor is used. A new boost-type switched ANPC inverter topology with two floating capacitors is proposed in Ref.11. In this topology, the number of switches is ten, and this needs ten driver circuits as per the presented modes of operation. Furthermore, when the modulation index is less than or equal to 0.66, the upper floating capacitor always charges and has no path for discharge. A new high gain 7L inverter topology with ten switches and one floating capacitor is proposed in Ref.12 to avoid this overcharging of the upper capacitor under low modulation index, as shown in Fig. 1b. The and the improved structure of Ref.12 is presented in Refs.13,14 with a reduction of one switch, but still, the switch count is high, as shown in Fig. 1c. Six-switch seven-level inverter topology with a gain of three is recently reported in Refs.15,16. This topology uses a fewer number of switches and diodes. However, the number of capacitors is increasing and also the voltage stress on the capacitor is high. Further, the capacitors having low reliability as compared to other power components.

From the above literature, the SCMLI topology with voltage boosting ability is presented with many switches that increase the inverter's cost and size. However, the ANPC type topologies10,11,12,13,14 have the maximum blocking voltage of vin, which is one of the significant advantages of these topologies. In this letter, a new 7L ANPC topology is presented. The following points summarize the advantages of the proposed topology:

-

(1)

the conventional NPC and ANPC topologies output voltage is half of the input voltage, which is rectified, and the output voltage is boosted to be 1.5 times higher than the vin,

-

(2)

the FC has self-voltage balancing,

-

(3)

due to a smaller number of components, it features reduced power losses and cost of the inverter,

-

(4)

the maximum voltage stress on the switch is vin, i.e. 2/3rd of output voltage and

-

(5)

the number of switches in high current stress is two.

This article aims to prove the operation of the proposed topology with supporting evidence of the experimental validation. The proposed topology performance is observed during the various dynamic changes of external parameters like dc input voltage variations, load variations and internal variation of modulation index (Ma).

Proposed self-balanced and boost (RSC-SB2) type 7L-ANPC inverter topology

Circuit descriptions

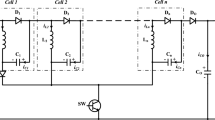

Figure 2 shows the circuit diagram of the proposed ANPC type 7L inverter. The proposed circuit diagram comprises two dc-link capacitors (C1 and C2), six switches (S1, S1′, S2, S2′, S3, and S3′), one bidirectional switch (SB), six diodes and one floating capacitor (FC). The switch S1 and S1′ are connected with upper and lower dc-link capacitors. Further, the mid-point of the dc-link capacitors is connected to the negative terminal of the load and bidirectional switch (SB). Therefore, the dc-link capacitors are directly connected to the dc input voltage (vin), and these capacitors share the input voltage to vin/2. Furthermore, since the mid-point of the dc-link capacitor is connected directly to the load, it maintains the voltage (vin/2) itself.

Modes of operations

Figure 3a–h for both positive and negative half cycle, the current path for various output voltage generation levels. From Fig. 3, the ON state switches are highlighted in a dark-black line.

The upper dc-link capacitor is connected with load for the positive half cycle, and in the negative half cycle, the bottom dc-link capacitor is connected to the load. A detailed explanation of each mode of operation is as follows:

- + vin/2:

-

S1, Da, Db & S1′ the switches are turned ON to charging the FC to vin and simultaneously, the S2 is turned ON to supply the + vin/2 to the load.

- + vin:

-

SB, Da, S3 and S2 the switches are turned ON to discharging the FC voltage to load. Now, the load voltage is equal to FC stored value (+ vin).

- + 3vin/2:

-

S1, S3 and S2 switches are turned ON, and the upper dc-link capacitor is the positive terminal connected to the negative terminal of FC. Now, the load voltage is equal to the sum of the C1 and FC i.e. vo = + 3vin/2.

- ± 0 vin:

-

in zero levels, the topology provides two redundant paths as either SB, S3 & S2′ or SB, S3′ and S2 switches turned ON.

- − vin/2:

-

S1, Da, Db and S1′ the switches are turned ON to charging the FC to vin and simultaneously, the S2′ is turned ON to supply the − vin/2 to the load.

- − vin:

-

SB, D, S3′ and S2′ the switches are turned ON to discharging the FC voltage to load. Now, the load voltage is equal to FC stored value (− vin).

- − 3vin/2:

-

S1′, S3′ and S2′ switches are turned ON, and the bottom dc-link capacitor is the negative terminal connected to the positive terminal of FC.

Now, the load voltage is equal to sum of the C2 and FC i.e. vo = − 3vin/2. The Diode Dx provides the current path during the lagging or leading power factor. The above discussion clearly shows that the proposed topology uses fewer ON state switches in each voltage level. The stress analysis on the switches is the important parameter for capacitor self-balanced inverter topologies. The high inrush current will occur during the parallel connection of FC and vin. To prevent the inrush, current the small inductor can be added to the circuit loop. The switched capacitor circuits facing a high inrush current, which is a notable drawback. To reduce the inrush current, a current limiting inductor is used. The inductor size is small, limiting the high inrush current to the required current15. The mathematical expression for the current limiting inductor is given in Eq. (1).

where the iind is the maximum inrush current or loop current during the charging the FCs, Lind is inductor value, and Cf is FC capacitance value. The charging current i.e. FC current four to five times higher than the load current. The voltage and current stress for the individual switch are given in Tables 1 and 2, respectively. It confirms that the proposed topology's maximum voltage stress is equal to vin and current stress is io + ic occurred in only two switches. Other topologies presented in Refs.8,9,10,11 needed four switches with high current stress.

Modulation technique and comparison of recent 7L SCMLIs

A variety of modulation methods such as selective harmonic elimination (SHE) PWM, multi-carrier PWM and can be applied to MLI. The SHEPWM can remove specific lower order harmonics. Similar to the SHEPWM, the pulse width modulation with phase disposition (PD-PWM) gives the overall lower THD compare to SHEPWM. In PD-PWM, the reference signal is compared with the carriers to generate the gate signals for each switch over a fundamental period. As shown in Fig. 4a, three triangular carriers vc1–vc6 with the same frequency, phase and amplitude are arranged from top to bottom in series, compared to sinusoidal vref. Figure 4b demonstrates the 7L output voltage of the PD-PWM modulation for the proposed topology. According to Fig. 4, the PWM pulses for all switches are generated from the carrier and reference signal comparison. Longest Discharging Cycle (LDC) during the positive half-cycle occurs for FC1 during the time interval [t2–t6] and in the negative half-cycle for FC1 during the time interval [t10–t12]. The ripple value (ΔVrip) across each capacitor is shown in Eq. (2) as Ro is the resistive load and fo (fundamental frequency) is the output voltage frequency. The optimum value for each capacitor (Copt) can be given as in Eq. (3).

The proposed topology with other recent SCMLI topologies of both NPC and non-NPC types are compared in Table 3. From the comparison, the non-NPC topologies need high voltage and current stress switches. In a family of NPC types, topologies use more switches with high current stress except for the proposed topology. As compared to Refs.4,5,6,7,8,9,10,11,12,13,14, the proposed topology has low TSV and increased efficiency as compared to other topologies.

Results and discussions

The scaled-down experimental setup is fabricated for the real-time implementation of the proposed topology, as shown in Fig. 5. The detailed components list and corresponding ratings are summarized in Table 4. Finally, the practical validation for the various condition is tested and the corresponding values are measured as shown in Fig. 6a–i. Initially, the typical resistive and inductive load with values of 80 Ω and 100 mH is applied, and the results are shown in Fig. 6a with the maximum output voltage of 300 V and the current value of 3.1 A for vin = 200 V.

Experimental results of proposed 7L boost type ANPC Inverter, (a) output voltage and current, (b) sudden load changes from 100 Ω and 50 mH to 80 Ω and 100 mH, (c) no-load to 100 Ω and 50 mH, modulation index (Ma) variations (d) 0.33–066, (e) 0.66–0.8, (f) 0.8–1.0, (g) sudden input voltage changes from 50 to 100 V, Switch (S1 and S1′) voltage and current (h) without loop inductor and (i) with loop inductor.

In this prototype mode, the switching frequency and fundamental frequency is 2.5 kHz/50 Hz is used. Sudden load changes test the dynamic performance of the proposed topology. During this load changing, the corresponding waveforms are captured in DSO and presented in Fig. 6b for the load value from 80 Ω and 100 mH to 100 Ω and 80 mH with a load current of 5.4 A (pk–pk). Further, the disconnected load to 100 Ω and 80 mH is applied, and the corresponding waveforms are presented in Fig. 6c. Due to load variations, the modulation index will be adjusted in the closed-loop. The modulation index (Ma) is varied from 0.33 to 0.66/0.66 to 0.8 and 0.8–1.0, respectively and the respective output results are Fig. 6d–f, respectively. This Ma variation is done under the load value of 80 Ω and 100 mH. In all these conditions, the FCs voltage is not affected, and it maintains the voltage of 200 V. It confirms that the FC is independent of the load value. Further, the dynamic input variation from 100 to 200 V is applied, and the corresponding waveform is shown in Fig. 6g.

Initially, the dc-link capacitors are charged to 100 V for vin = 200 V, and FC is charged to 200 V. However, most of the Self-balanced FCs suffer from the inrush current. Therefore, a small loop inductor (50 µH) is used in the circuit to suppress the inrush current, and the switches S1 and S1′ are in the loop path with high inrush current. The switch voltage and current waveform of with and without loop inductor are shown in Fig. 6h,i. Further, to conclude the experimental section, the cost comparison of recent boost ANPC-type topologies and proposed is shown in Table 5, and the chosen IGBT device is half-bridge type. The proposed topology gives a lower cost as compared to the other topologies. The power loss for the individual component is calculated using PLECS simulation tool and the same is listed in Table 6. The cost of the proposed topology is compared with similar ANPC topologies as given in Table 7. It is confirming that the proposed topology is required low cost. Based on the power loss calculation, the efficiency versus output power is plotted in Fig. 7, and for the experimental efficiency is calculated using the Fluke meter. The application of the proposed topology is the PV system, as shown in Fig. 8a, and the possible three-phase extension is shown in Fig. 8b. The PV panel’s source-side ‘n’ is connected in series to meet the required grid voltage. The dc/dc converter is used to regulate the unregulated PV voltages and fed to the dc-link capacitors.

Conclusion

A new 7L-RSC-SB2 inverter topology with reduced switch count and self-balanced and boosting ability topology was proposed in this letter. The output voltage is 1.5 times higher than the vin. The proposed topology used one floating capacitor, and the voltage stress on the individual switch is vin, reducing the inverter's overall voltage stress. The comprehensive analysis in terms of components and cost comparison is presented, and it is evident that the proposed topology is better than the other 7L SCMLI topologies. Further, the experimental results are validated, and the proposed boost type ANPC topology is a better alternative topology for the conventional ANPC inverter, and it's suitable for rooftop PV applications.

Abbreviations

- PV:

-

Photovoltaic

- NPC:

-

Neutral point clamped

- ANPC:

-

Active neutral point clamped

- v in :

-

Input voltage

- TL:

-

Transformerless

- SCMLI:

-

Switched-capacitor multilevel inverter

- FCs:

-

Floating capacitors

- IGBT:

-

Insulated bipolar gate transistor

- v o :

-

Output voltage

- Ma:

-

Modulation index

- ic :

-

Charging current

- io :

-

Output current

- PWM:

-

Pulse width modulation

- Copt :

-

Optimum capacitor value

References

Pakdel, M. & Jalilzadeh, S. A new family of multilevel grid-connected inverters based on packed U cell topology. Sci. Rep. 7, 12396 (2017).

Xu, S. et al. Fault-tolerant control of ANPC three-level inverter based on order-reduction optimal control strategy under multi-device open-circuit fault. Sci. Rep. 7, 14447 (2017).

Sathik, M. J. et al. Experimental validation of new self-voltage balanced 9L-ANPC inverter for photovoltaic applications. Sci. Rep. 11, 5067 (2021).

Hinago, Y. & Koizumi, H. A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans. Ind. Electron. 59(2), 878–887 (2012).

Babaei, E. & Gowgani, S. S. Hybrid multilevel inverter using switched capacitor units. IEEE Trans. Ind. Electron. 61(9), 4614–4621 (2014).

Ye, Y., Cheng, K. W. E., Liu, J. & Ding, K. A step-up switched-capacitor multilevel inverter with self-voltage balancing. IEEE Trans. Ind. Electron. 61(12), 6672–6680 (2014).

Peng, W., Ni, Q., Qiu, X. & Ye, Y. Seven-Level inverter with self-balanced switched-capacitor and its cascaded extension. IEEE Trans. Power Electron. 34(12), 11889–11896 (2019).

Liu, J., Zhu, X. & Zeng, J. A seven-level inverter with self-balancing and low-voltage stress. IEEE J. Emerg. Sel. Top. Power Electron. 8(1), 685–696 (2020).

Sathik, M. J., Bhatnagar, K., Sandeep, N. & Blaabjerg, F. An improved seven-level PUC inverter topology with voltage boosting. IEEE Trans. Circ. Syst. II Exp. Briefs. 67(1), 127–131 (2020).

M. J. Sathik, Z. Tang, Y. Yang, K. Vijayakumar & F. Blaabjerg. A new 5-level ANPC switched capacitor inverter topology for photovoltaic applications. in Proc. 45th Annual Conf. IEEE Ind. Electron. Soc., Lisbon, Portugal 3487–3492 (2019).

Lee, S. S. & Lee, K.-B. Dual-T-type seven-level boost active-neutral-point-clamped inverter. IEEE Trans. Power Electron. 34(7), 6031–6035 (2019).

Sathik, M. J., Sandeep, N. & Blaabjerg, F. High gain active neutral point clamped seven-level self-voltage balancing inverter. IEEE Trans. Circ. Syst. II Exp. Briefs. 67(11), 2567–2571 (2020).

Lee, S. S., Lim, C. S., Siwakoti, Y. P. & Lee, K. Hybrid 7-level boost active-neutral-point-clamped (H-7L-BANPC) inverter. IEEE Trans. Circ. Syst. II Exp. Briefs. 67(10), 2044–2048 (2020).

Zeng, J., Lin, W. & Liu, J. Switched-capacitor-based active-neutral-point-clamped seven-level inverter with natural balance and boost ability. IEEE Access. 7, 126889–126896 (2019).

Sathik, M. J., Sandeep, N., Siddique, M. D., Almakhles, D. & Mekhilef, S. Compact seven-level boost type inverter topology. IEEE Trans. Circ. Syst. II Express Briefs. https://doi.org/10.1109/TCSII.2020.3039387 (2021).

Chen, M., Loh, P. C., Yang, Y. & Blaabjerg, F. A six-switch seven-level triple-boost inverter. IEEE Trans. Power Electron. 36(2), 1225–1230 (2021).

Acknowledgements

This work was supported by the Research Project [A Rooftop PV fed Grid-tied System]; Prince Sultan University, Riyadh, Saudi Arabia [83]. The authors would like to acknowledge the support of Prince Sultan University for paying the Article processing fees.

Author information

Authors and Affiliations

Contributions

All authors have contributed equally to the work. M.J.S. wrote the main manuscript text, prepared the figures and tables, and developed the experimental hardware setup. D.J.A. validated the experimental results, reviewed the paper and corrected the grammatical mistakes. All authors contributed to and have approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

M., J.S., Almakhles, D.J. A new seven level boost-type ANPC inverter topology for photovoltaic applications. Sci Rep 11, 22487 (2021). https://doi.org/10.1038/s41598-021-01669-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-01669-6

This article is cited by

-

Design and Analysis of Transformerless Grid-Tied PV Inverter with Hybrid Switching for a Wide Range of PV Voltage Adaptability

Journal of Electrical Engineering & Technology (2023)

-

Common ground type five level inverter with voltage boosting for PV applications

Scientific Reports (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.