Abstract

Valley pseudospin is an electronic degree of freedom that promises highly efficient information processing applications. However, valley-polarized excitons usually have short pico-second lifetimes, which limits the room-temperature applicability of valleytronic devices. Here, we demonstrate room-temperature valley transistors that operate by generating free carrier valley polarization with a long lifetime. This is achieved by electrostatic manipulation of the non-trivial band topology of the Weyl semiconductor tellurium (Te). We observe valley-polarized diffusion lengths of more than 7 μm and fabricate valley transistors with an ON/OFF ratio of 105 at room temperature. Moreover, we demonstrate an ion insertion/extraction device structure that enables 32 non-volatile memory states with high linearity and symmetry in the Te valley transistor. With ultralow power consumption (~fW valley contribution), we enable the inferring process of artificial neural networks, exhibiting potential for applications in low-power neuromorphic computing.

Similar content being viewed by others

Introduction

Charge-based electronics with conventional semiconductors are reaching their fundamental limits in power efficiency due to inevitable carrier scattering. Valley (a quantum degree of freedom of electrons) is an information carrier with high energy efficiency1,2,3, which is robust against low-energy phonons4,5, promising for next-generation electronics6,7,8. It still remains a grand challenge to realize room-temperature valley transistors, because the widely investigated excitonic valley has a short lifetime (<1 ps) due to long-range Coulomb interaction4,6,9. Room-temperature valley devices require the lifetime of valley polarization to be sufficiently long for propagating through the channel9. To achieve the valley polarization with a long lifetime10, researchers mainly adopted plasmonic hot-electron injection3 or interlayer excitation in van der Waals heterostructures11. However, it usually requires relatively complicated optical pumping designs and is incompatible with conventional field-effect transistors (FETs) modulated by the electric field.

Chiral anomaly in Weyl/Dirac materials allows to generate valley polarization that can diffuse over a long distance (~100 μm in theory) and sustain under thermal perturbation12, providing an alternative mechanism for room-temperature valley transistors (Supplementary Note 1). By applying an electric field that is parallel to the magnetic field, the valley polarization generated by the chiral anomaly can transport over a long distance at room temperature, because the relaxation process involves a large quasi-momentum transfer12,13,14. As the chiral anomaly-based valley transport arises from the non-trivial Berry curvature, we can realize valley transistors by modulating the strength of Berry curvature through the electrostatic gating at room temperature. By controlling the energy separation between Weyl point and Fermi level, the valley transistors can exhibit non-volatile multiple resistance states with high linearity and symmetry. Due to the robust valley transport against low-energy phonons15, the valley transistors have the potentials of realizing a high signal-to-noise ratio under low readout power, which are advantageous over conventional charge-based transistors with relatively large readout power ranging from nW to μW16,17,18. The valley transistors show the potentials for low-power neuromorphic computing, especially for the inference process.

In this work, we demonstrate room-temperature valley transistors with Weyl semiconductor tellurium (Te) with valley diffusion length over 7 μm. The valley transistors exhibit an ON/OFF ratio of 105 through electrostatic gating. The ion insertion/extraction into the Te channel results in non-volatile valley resistance change with high linearity and symmetry, which allows to emulate artificial synaptic states. The robust valley transport characteristics enable to operate the synaptic valley devices with the ultralow readout voltage, allowing to construct an artificial neural network (ANN) with low power consumption (~fW valley contribution and ~pW Ohmic contribution) in the inferring process. This study provides a strategy for low-power neuromorphic computing with the low-loss valley devices.

Results

Valley transport of Weyl semiconductor

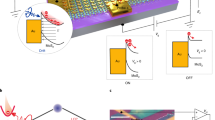

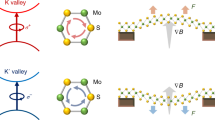

The topological properties in Weyl materials arise from the non-trivial Berry curvature. The arrows in Fig. 1a show the flux of the Berry curvature from one Weyl point (W+, light brown) to the other (W-, blue). Non-local structure (Fig. 1b) can significantly reduce the effects of conventional Ohmic transport, which enables generating, propagating (the blue arrow), detecting and modulating valley transport. Based on the non-trivial Berry curvature, chiral anomaly generates the imbalanced valley polarization under parallel magnetic field and electric field (B//E)19,20 (Fig. 1c). Different from widely investigated excitonic valley polarization, the absence of strong Coulomb interaction can retain a long lifetime of imbalanced valley generated by chiral anomaly. The intervalley scattering determines the lifetime of valley during propagating (described by \({\tau }_{v}\)), which requires a large momentum transfer (Fig. 1d)12,21. Theoretically, valley can reach a long transport length of 100 μm (\({L}_{v}=\sqrt{D{\tau }_{v}}\), \({L}_{v}\) is the intervalley scattering length and \(D\) is the charge diffusion coefficient)12. We can control valley transport by modulating Berry curvature, which determines the pumping rate (\(w\)) of imbalanced valley according to Eq. (1)13,22:

where e is the electron charge, and \(\hslash\) is the reduced Planck constant. As Berry curvature is highly sensitive to the energy separation (Δε) between EF and Weyl point23,24, electrostatic gating can effectively control Berry curvature and valley transport. Figure 1e shows a typical distribution of the Berry curvature as a function of Δε24. When EF shifts close to the Weyl point, Δε ≈ 0, the Berry curvature is strong, which can generate high valley resistance; while EF moves away from the Weyl point, Δε » 0, the Berry curvature rapidly decays, showing low valley resistance. Therefore, we can modulate the valley resistance by controlling the position of EF to switch valley FETs (inset of Fig. 1e).

a Non-trivial Berry curvature in the Weyl materials. The vector plots of the Berry curvature connect Weyl points (W + and W-) in the momentum space. b Schematic illustration of the device structure of valley transistor with Weyl semiconductor. In this non-local structure, we apply constant current (I) through terminal 1–2 and detect the valley diffusion (blue arrow) through terminal 3–4 voltage (V). Electrostatic gating voltage (Vg) is used for controlling the Fermi level (EF) and Berry curvature. H is the applied magnetic field. c Generation of imbalanced valley based on the chiral anomaly. L and R are left-and right-handed Weyl Fermions, respectively. μL and μR are the chemical potentials of left and right chirality, respectively. d Relaxation of imbalanced valley through intervalley scattering. The valley pseudospin (indicated by node position ±K) imbalance relaxes through intervalley scattering at a rate of \({\tau }_{v}^{-1}\) since intravalley scattering (\({\tau }_{c}^{-1}\)) cannot change the chirality. e Modulating valley through controlling the strength of Berry curvature (Ω). Δε is the energy separation between EF and Weyl point. The inset shows that electrostatic gating can shift EF and Berry curvature to achieve “ON” and “OFF” state in the transfer curve.

Compared to the tested valley transport in topological semimetals14,25, the modulation of EF and valley transport in Weyl semiconductor is more efficient due to the tunable carrier density (Supplementary Table 1). Te is a Weyl semiconductor that can exhibit exotic transport behaviours from the Weyl point and non-trivial Berry curvature23,26. The intrinsic defects of Te make its EF near the valence band maximum23,27, which results in a small energy separation (Δε of about 20 meV) between the EF and the Weyl point (Supplementary Fig. 1, Supplementary Fig. 2 and Supplementary Note 2) and facilitates electrostatic modulation of transistors based on Berry curvature (Supplementary Fig. 3).

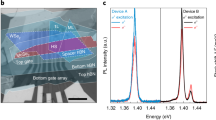

Conventional Ohmic transport decays very fast due to unavoidable phonon scattering. In contrast, valley transport exhibits low-loss transport characteristics because of its robustness to low-energy phonon scattering4,15. The non-local device structure (Fig. 2a) allows the detection of the valley non-local resistance (RVNL)25,28. For the Weyl-based valleytronics, RVNL follows the relationship in Eq. (2)12,25:

where L is the length between the Hall bar terminals and Lv is the intervalley scattering length. By applying a constant current through terminals 1 and 2, we measure the local resistance (RL) between terminals 1 and 2 and the non-local resistance (RNL) between terminals 3 and 4. The tested RNL includes a mixed contribution from Ohmic non-local resistance (RONL) and RVNL. Since the non-local response from RVNL vanishes at B = 0, we can extract RONL from RNL (details in Supplementary Note 3). The temperature-dependent RVNL (Fig. 2b) shows that the valley resistance decreases as the temperature increases from 50 to 300 K. At room temperature, we can still observe significant non-local valley resistance (RVNL = −6.4 Ω under 9 T) because intervalley scattering requires a large momentum transfer.

a Schematic and scanning electron microscopy image of the “H” geometry Te valley device. After applying the constant current Id through terminal 1–2, imbalanced valley (red arrow) propagates to the detection terminal 3–4. The scale bar is 3 μm. b Temperature-dependent valley transport from 50 to 300 K. Valley non-local resistance (RVNL) decreases as the temperature increases. c The ratio of non-local valley resistances under different widths. R34-VNL and R56-VNL are corresponding to the non-local valley resistance from terminals 3–4 and 5–6, respectively. Inset is the schematic of width-dependent valley device with width of x1 = 2 μm and x2 = 1 μm. d Length-dependent valley transport as a function of B at 300 K. Inset is the schematic of the length-dependent valley device with the channel of 2 μm (R34-VNL), 4 μm (R56-VNL) and 7 μm (R78-VNL). e Length-dependent valley transport under 9 T at 300 K. | RVNL | is shown as a function of channel length in a semi-log curve. The yellow line is a visual guide that corresponds to a valley diffusion length (Lv) of ~2.5 μm, fitted by Eq. (2). f Decay curves of the normalized valley and Ohmic resistance as a function of length. Valley transport can persist over much longer distances than charge transport.

The valley transport characteristics can be further supported by width-dependent and length-dependent non-local valley transport measurements. Supplementary Figure 4 presents RVNL with different channel widths. R34-VNL (with a width of 2 μm) and R56-VNL (with a width of 1 μm) exhibit −2.1 and −1.1 Ω, respectively. The ratio of R34-VNL to R56-VNL is ~2 (Fig. 2c), matching well with the width ratio of 2 (inset of Fig. 2c). Supplementary Fig. 5 shows the reproducible temperature- and width-dependent valley transport results, supporting the valley transport behaviours in Te.

In addition, we investigate the length-dependent valley transport behaviour with different channel lengths of 2 μm, 4 μm and 7 μm. Figure 2d shows RVNL as a function of the magnetic field, clearly exhibiting length-dependent valley transport characteristics. The valley resistance is still sufficiently detectable (RVNL = −1.0 Ω under 9 T), even with a long transport distance of 7 μm. Figure 2e shows the |RVNL| as a function of channel length in a semi-log curve, fitting well with Eq. (2). The extracted Lv of 2.5 μm is much longer than the mean free path of electrons (tens of nm in Si at room temperature29), which reveals the low-loss transport characteristics in Te. Figure 2f presents the length dependence of the normalized valley and conventional charge transport contribution. The Ohmic resistance shows fast decay with the increase of distance (described by the Drude model). In contrast, the valley resistance can still be detected over a long distance because the relaxation process of valley transport involves a large quasi-momentum transfer.

We further investigate the carrier-density-dependent valley transport (Supplementary Fig. 6). We conducted the Hall tests of different samples (Supplementary Fig. 6a) and extracted the hole density values, ranging from 6.3 × 1013 cm−2 (grey line) to 9.2 × 1013 cm−2 (pink line) due to different concentrations of intrinsic Te vacancies23. For the Te sample with a higher carrier density, the device shows a higher valley resistance (Supplementary Fig. 6b). This trend arises from the carrier-density-dependent EF and Δε. For the Te flakes with the higher hole density, it has a lower EF position and smaller Δε, which results in a stronger Berry curvature and higher valley resistance. It is noteworthy that these topological properties are highly resistant to the structural defects30. We also simulate the voltage potential distribution of conventional charge transport in the non-local configuration under B//E (Supplementary Fig. 7). The simulation results suggest that the signal from conventional charge diffusion (Ohmic contribution) is negligible due to its short mean free path of electrons (e.g. tens of nm in Si), consistent with the previous non-local chiral anomaly work13. These length-, width- and carrier-density-dependent results reveal the presence of low-loss valley transport based on the chiral anomaly in the Te samples.

Room-temperature volatile and non-volatile valley transistors

To efficiently modulate the strength of Berry curvature and valley resistance at room temperature, we adopt ionic liquid (DEME-TFSI) with a high equivalent capacitance of ~10 μF/cm2 for electrostatic gating. Researchers use the dimensionless coefficient αVNL = |RVNL/RL | to quantitatively describe the relative strength of the valley resistance12,25. Figure 3a shows αVNL as a function of B2 of a 46 nm thick Te flake, exhibiting a linear shape under different gating voltages. The αVNL-Vg curve shows an ON/OFF ratio of 103 (Fig. 3b). For this thick sample, EF is close to the Weyl point, which results in strong valley transport at Vg = 0. For the 28 nm thick Te flake, it also exhibits nearly linear αVNL-B2 curves under the Vg from −2 to 2 V (Fig. 3c). The αVNL-Vg curve of the Te valley FET shows an ON/OFF ratio of 105 (Fig. 3d), which is comparable to that of reported charge-based Te FETs (104–106) and much higher than that of other valley FETs (102–103) in the existing literature (Supplementary Table 2). The strong dependence of valley transport on the position of EF in the Weyl semiconductor Te leads to a high ON/OFF ratio of valley FETs. When we apply negative gate voltages, negative ions [TFSI]- are adsorbed on the Te flake, which gives rise to an ultrathin electrical double layer at the surface of Te. The induced holes downshift EF close to the Weyl point of Te, increasing the valley resistance. When we remove the gate voltage, the valley resistance rapidly decays, exhibiting volatile behaviour and unique ion dynamics.

Figure 3e shows the thickness-dependent ON/OFF ratio of valley FETs. As the thickness of Te flakes increases from 28 to 50 nm, the ON/OFF ratio of Te valley devices under 9 T decreases from 1.4 × 105 to 2.6 × 103. To reveal the thickness-dependent carrier densities and EF, we carried out the Hall resistance experiments for the samples with different thicknesses (Supplementary Fig. 8a), along with the theoretical calculation (Supplementary Fig. 8b, c) and mechanism analysis (Supplementary Note 4). Consistent with existing works based on solution-prepared Te, higher hole carrier density exists in the thicker Te samples26,31,32. For performance comparison, we used the 28 nm thick Te flake as the channel of charge-based FETs with ionic liquid. The Id-Vd curve of the Te charge-based FET exhibits a linear shape under Vds of 0 to 1 V and an ON/OFF ratio of 240 (Supplementary Fig. 9). This tested ON/OFF ratio is comparable to the Te charge-based FET works with a similar thickness on the high-k dielectric layer32 (Supplementary Table 2), but much smaller than our valley FETs. Implementing the ferromagnetic material interface or using the alternating current can potentially trigger valley transport in the Weyl materials without using the magnetic field33,34.

In addition to volatile behaviours of valley FETs, we adopt stable solid-state electrolyte PEO/LiClO4 to realize non-volatile valley states (Fig. 4a). Li+ can be inserted into Te flakes under positive gate voltages and be extracted under negative gate voltages35,36. The Li+ insertion can upshift the EF and enlarge the Δε (Supplementary Fig. 10), which results in the non-volatile valley resistance. Ion doping is a common technique for investigating the physical properties of topological materials by only shifting the EF without changing the band structure37,38. The Weyl point is topologically protected and robust against external disturbance (thermal, ion insertion, etc)39,40. Figure 4b presents the transfer curves in the sequence of 0 → +2 V → 0 → −2 V → 0. For Vg > 0, Li+ is adsorbed and inserted into the Te flakes. Thus, the valley resistance decreases from 0 → +2 V and keeps stable during +2 V → 0. For Vg < 0, due to the coexistence of Li+ extraction and the electrical double layer, the valley resistance increases during 0 → −2 V; as the Vg varies from −2 V → 0, the strength of the electrical double layer becomes weak, decreasing the valley resistance.

a Schematic of non-volatile valley transistors with the solid-electrolyte PEO/LiClO4. The black arrow indicates the movement of Li ions. b Transfer curves with hysteresis under B//E and B = 0.1 T. The black arrow indicates the sweeping direction of Vg. c Output curves of different states. Inset shows the non-volatile valley states under the retention tests of 10,000 s. Set corresponds to the gating of +2 V with 1 s, while reset is the gating of −2 V with 1 s. d XPS 3d spectra of Te. The vertical dashed lines and the arrow indicate the shift of peaks. The peak shifts from ~573.1 eV (orange) in the initial Te to ~572.7 eV (blue) after +2 V pulse (set). With a further gating of −2 V pulse (reset), the peak moves back to ~573.1 eV (grey). e XPS Li 1 s spectra. The +2 V pulse results in the emergence of a rough peak (blue), while the following −2 V pulse causes this peak to disappear (grey). f Energy separation between EF and the Weyl point for defective Te (1.23% Te vacancies), defective TeLi1 (1.23% Te vacancies and 1.23% Li doping), defective TeLi2 (1.23% Te vacancies and 2.46% Li doping) and defective TeLi3 (1.23% Te vacancies and 3.69% Li doping).

Figure 4c shows the output curves of different states before and after gating. After applying Vg = +2 V for 1 s (set operation), the valley resistance decreases due to the non-volatile Li+ insertion and larger Δε. Then, we apply Vg = −2 V for 1 s to reset the devices, which results in the valley resistance close to the initial state, indicating the reversible ion insertion/extraction. We further investigated the stability of non-volatile states through the retention tests of 10,000 s (inset of Fig. 4c). The tested curves show slight variation during the retention tests, revealing the stable non-volatile valley states based on valley transport.

To validate the working mechanism of Li+ insertion/extraction, we carry out X-ray photoelectron spectroscopy (XPS) characterization of the Te samples at different stages: initial Te and Te with Vg = ±2 V. Upon applying Vg = +2 V for 1 s, the XPS spectra of the Te sample (Fig. 4d, blue curve) shows a peak at ~572.7 eV between the peak of Te0 (~573.1 eV) and the peak of Li2Te (572.4 eV)41. This characteristic peak is consistent with the Li spectra (Fig. 4e), indicating that Li+ exist in the Te after applying Vg = +2 V for 1 s. Following Vg = −2 V for 1 s, the peak of Te (Fig. 4d, grey curve) is similar to that of the pristine Te, and the Li peak disappears (Fig. 4d, grey curve), indicating the extraction of Li+. In addition, the XPS spectra (Supplementary Fig. 11) show the absence of Cl peaks in the Te samples at different stages, suggesting the complete removal of PEO/LiCl4 after washing. These results reveal that Li+ can be successfully inserted and extracted by applying appropriate gate pulses.

Furthermore, we calculate the effects of carrier concentrations of ions on the non-volatile shift of Δε through the density functional theory (Fig. 4f and Supplementary Fig. 12). In the Li-inserted defective TeLi1 structure (1.23% Li intercalation), Δε increases to 0.05 eV. With more Li inserted into the TeLi2 structure (2.46% Li concentration), Δε is 0.10 eV. As the Li concentration increases from 2.46 to 3.69%, Δε further increases by 0.16 eV. These results reveal that Li insertion can be used to enlarge the Δε of Te step-by-step with increasing Li concentration. Li insertion/extraction can quantitatively control multiple non-volatile valley resistance states.

Synaptic valley transistors for low-power neuromorphic computing

Conventional charge-based synaptic transistors suffer from relatively large readout power (nW to μW) in the inference process for neuromorphic computing16,17,18,42,43,44. It is of significance to adopt a low-loss transport mechanism to realize low-power computing45. Synaptic valley transistors show the potentials of achieving a high signal-to-noise ratio with low readout power due to the robust valley transport.

Training of the ANN requires programmable non-volatile states and weight updating. Through ion insertion/extraction into Te channel with the electrolyte PEO/LiClO4, we can realize non-volatile resistance modulation for emulating synaptic functions (Fig. 5). By applying writing voltage pulses (+2 V/−2 V, 130 ms) to the gate terminal of the valley FETs, the device shows depression/potentiation of the valley resistance with 20 distinct states (Fig. 5a), which correspond to long-term depression (LTD) and long-term potentiation (LTP) synaptic behaviours. By applying a gate voltage pulse (Vg = −2 V, 130 ms), Li+ insertion and narrower Δε cause an increase in the valley resistance. After the removal of the gate voltage (Fig. 5b), the valley resistance first drops, and then remains stable at a relatively higher level compared to the pristine one because of Li+ extraction.

a Potentiation and depression states under the control of voltage pulses with the solid-state electrolyte PEO/LiClO4. Vg = +2 V is applied to adsorb and intercalate Li+ into Te and move EF away from the Weyl point. Vg = −2 V is applied to relax and extract Li+ and move EF back. The test temperature is 300 K under B = 0.1 T. b A zoomed-in view of a with multiple linear states. The dash lines indicate the stable states. c Stable valley states under retention tests of 3000 s. Vg > 0 for reducing the valley resistance and Vg < 0 for increasing the valley resistance. d, e Cycle-to-cycle performance of valley synapses with d 8 and e 32 stable states under the applied constant current of 100 nA and 1 μA, respectively. f Readout current and voltage in our valley transistors and reported works. The dash lines are corresponding from 10−16 to 10−8 W. g Artificial neural network for classifying handwritten digits. The linear and stable valley states are used for the connected synapses between neurons. Inset shows a three-layer artificial neural network for classifying handwritten digits in the MNIST database. h Neuromorphic classification based on the non-volatile valley transistors. The black dash line corresponds to the 90% recognition accuracy. i Classification accuracy after 50 epochs for different non-volatile states and ideal numeric.

We demonstrate LTP and LTD behaviours with 8, 16, 24 and 32 stable valley resistance states under different pulse configurations (Supplementary Fig. 13) under B = 0.1 T. As summarized in Supplementary Fig. 14, our devices show linear weight update behaviour with high symmetry (e.g. the nonlinearity of 0.012/−0.442 and asymmetry of 0.454 for 8 states). The multiple resistance states show negligible deviation for 3000 s (Fig. 5c), indicating good retention of non-volatile valley FET states. Thus, the relatively low magnetic field (B = 0.1 T) can trigger the valley transport and retain linear, analogue, non-volatile valley synaptic weights for neuromorphic computing. The cycling tests (Fig. 5d, e and Supplementary Fig. 15) exhibit low cycle-to-cycle variation for 8 to 32 states (e.g. 0.371% variation for 32 states). The LTP and LTD characteristics exhibit highly linear features, paving the way for the realization of ANN with high learning accuracy.

The valley transport is robust against thermal perturbation25, which enables to use the relatively low readout current (100 nA level) and voltage (10 nV level) for readout while maintaining a high signal-to-noise ratio. Figure 5f compares readout voltage (Uread), readout current (Iread) and readout power (Pread) with reported works (details in Supplementary Table 3). The readout power can be calculated from Pread = UreadIread16. The valley devices show 100 fW level (solid brown ball) for 32 states under the read current of 1 μA, and ~ fW level (solid orange ball) for 8 states under the read current of 100 nA (sufficient to ensure a relatively high signal-to-noise ratio and linear synaptic behaviours). The readout process of synaptic valley transistors requires Ohmic-based drive current through the local terminal, which gives rise to the power consumption of ~pW level (hollow pink triangle in Fig. 5f, details in Supplementary Note 5). In this work, the synaptic valley transistor exhibits low power consumption during readout (Ohmic contribution of ~pW and valley contribution of ~fW), orders of magnitude lower than conventional charge-based synaptic devices with the readout power of nW to μW levels in the inference process16,17,43,46,47,48,49,50. The valley transport is robust against low-energy events in the environment, which allows us to observe discrete and stable synaptic states with ultralow reading current/voltage and provides the potential for realizing low-power neuromorphic computing.

We further simulate a three-layer ANN based on valley synaptic behaviour to classify handwritten data with a widely used Modified National Institute of Standards and Technology (MNIST) database. The detailed training procedures for weight update based on valley transistors (Fig. 5g) are summarized in the Method and Supplementary Note 6. As the number of states increases from 8 to 32, the classification accuracy gradually increases (Fig. 5h). With 8 states, the recognition accuracy is higher than 91% due to the ultralow nonlinearity (0.012/−0.442); with 32 states, the accuracy reaches 95.2%. Even with the consideration of cycle-to-cycle variation (0.371%), the classification accuracy is still higher than 95%, which is close to the accuracy value for the ideal numeric simulation (96.5%). The classification accuracy after 50 training epochs (Fig. 5i) is comparable to the state-of-the-art performance of neuromorphic computing works43,44. We demonstrate low-power neuromorphic computing based on valley synaptic devices by utilizing robust valley transport.

Discussion

In summary, we demonstrate room-temperature valley transistors with a Weyl semiconductor. Our devices show robust valley transport characteristics, which can propagate over 7 μm at room temperature. Through the electrical generation and modulation of valley transport, the valley transistors show 105 ON/OFF ratio. We also demonstrate the non-volatile change of valley resistance through ion insertion/extraction by modulating non-trivial Berry curvature, which enables the emulation of the synaptic functions with 32 linear, high symmetry and discrete non-volatile states for ANN. Non-volatile valley FET exhibits low readout power (Ohmic contribution of ~pW and valley contribution of ~fW), a few orders of magnitude lower than reported synaptic works (from nW to μW). The accuracy reaches up to 95.2% for neuromorphic classifying handwriting data. With the low-loss characteristics of the valley degree of freedom, our valley transistor provides an alternative to conventional charge-based devices for low-power neuromorphic computing.

Methods

Device fabrication

We prepared Te flakes by hydrothermal methods32 and transferred them to a Si substrate with 300 nm thick SiO2. The thickness of Te flakes is more than 10 nm, which can retain the band structure similar to bulk Te and exhibit magnetotransport signatures of the Weyl point51. Electron beam lithography was used to define the pattern of metal electrodes in a Hall bar configuration with a side gate. Metal contacts were prepared by thermal evaporation of Au (80 nm) at a rate of 0.3 Å/s under a vacuum of 3 × 10−7 Torr. The Te flake for the non-local valley transport measurement was etched by a focused ion beam to achieve the “H” configuration25. A low beam current of 10 pA at 20 kV was adopted in the etching process to avoid severe damage to the sample.

Device characterization

Electrical measurements were carried out with the Physical Property Measurement System from Quantum Design (DC resistivity and ETO modules with the typical noise floor of 1 nV/rtHz) and the Keithley 4200. After applying a constant current (Iconstant), the equipment directly tested the voltage signal (U), and exported the resistance signal (R). To modulate the valley FET, a droplet of the ionic liquid DEME-TFSI was used to cover the Te flake and the side gate electrode. Before the test, the device was kept under a high vacuum of 4 × 10−8 Torr for 24 h to remove the water. We also chose solid-state PEO/LiClO4 as the electrolyte because it is stable and can act as a source of Li ions. PEO/LiClO4 (PEO and LiClO4 in methanol with a mass ratio of 9:1) was coated on the sample, and then the sample was heated at 70 °C for 30 min to remove the solvent before the electrical tests. We characterized non-volatile valley synaptic behaviours at the temperature of 300 K and the magnetic field of 0.1 T. We extracted the carrier density based on the linear part of the Hall resistance curves (e.g. −4T ≤ B ≤ 4 T region in Supplementary Fig. 1).

Material characterization

Scanning electron microscopy images were acquired by a JEOL Model JSM-6490. XPS spectra were acquired by a Thermo Fisher Nexsa. For the gated Te, the samples were carefully washed with water and methanol to remove PEO/LiClO4 before XPS characterization.

First-principles calculations

The band structure and density of states calculations were carried out using density functional theory (DFT) implemented in the Vienna Ab initio Simulation Package (VASP)52. The Perdew-Burke-Ernzerhof-type generalized gradient approximation53 and the projector augmented-wave (PAW) method were employed54. A plane-wave basis set with a default energy cut-off and a 16 × 16 × 12 k-point mesh was used. A 3 × 3 × 3 Te supercell was used to calculate the density of states with or without Te vacancies. After removing one Te atom (marked by the yellow ball, Supplementary Fig. 2b) from the supercell, the vacancy density in the calculated deficient Te sample was 1/81 (~1.23%).

Modelling the contribution of conventional charge transport

We modelled the distribution of non-local voltages from Ohmic contribution in the COMSOL Multiphysics. As conventional charge transport can be described by the Drude model, the contribution of charge when B//E (σ||) can be described by the Equation (3)13:

where σ0 = neμ, n is the carrier density, e is the electron charge, μ is the mobility.

Neuromorphic computing simulations

A three-layer ANN was used to execute supervised learning over the training examples. There are 748 input elements, 100 hidden neurons and 10 output neurons. The experimental non-volatile valley resistance states are the synaptic weights between connected neurons. The MNIST dataset, a large image version (28 × 28 pixels) of handwritten digits, was used for training and classification. The recognition accuracy was compared with the test examples in a single training epoch.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

Code availability

The codes for the simulations are available from the corresponding author upon request.

References

Sheng, F. et al. Rashba valleys and quantum Hall states in few-layer black arsenic. Nature 593, 56–60 (2021).

Gong, S.-H., Alpeggiani, F., Sciacca, B., Garnett, E. C. & Kuipers, L. Nanoscale chiral valley-photon interface through optical spin-orbit coupling. Science 359, 443–447 (2018).

Jones, A. M. et al. Optical generation of excitonic valley coherence in monolayer WSe2. Nat. Nanotechnol. 8, 634–638 (2013).

Mak, K. F., Xiao, D. & Shan, J. Light–valley interactions in 2D semiconductors. Nat. Photonics 12, 451–460 (2018).

Tang, Y., Mak, K. F. & Shan, J. Long valley lifetime of dark excitons in single-layer WSe2. Nat. Commun. 10, 4047 (2019).

Li, L. et al. Room-temperature valleytronic transistor. Nat. Nanotechnol. 15, 743–749 (2020).

Zeng, Y. et al. Electrically pumped topological laser with valley edge modes. Nature 578, 246–250 (2020).

Yin, J. et al. Tunable and giant valley-selective Hall effect in gapped bilayer graphene. Science 375, 1398–1402 (2022).

Schaibley, J. R. et al. Valleytronics in 2D materials. Nat. Rev. Mater. 1, 16055 (2016).

Zhao, S. et al. Valley manipulation in monolayer transition metal dichalcogenides and their hybrid systems: status and challenges. Rep. Prog. Phys. 84, 026401 (2021).

Jiang, C. et al. A room-temperature gate-tunable bipolar valley Hall effect in molybdenum disulfide/tungsten diselenide heterostructures. Nat. Electron. 5, 23–27 (2021).

Parameswaran, S., Grover, T., Abanin, D., Pesin, D. & Vishwanath, A. Probing the chiral anomaly with nonlocal transport in three-dimensional topological semimetals. Phys. Rev. X 4, 031035 (2014).

De Boer, J. C. et al. Nonlocal signatures of the chiral magnetic effect in the Dirac semimetal Bi0.97Sb0.03. Phys. Rev. B 99, 085124 (2019).

Chen, J. W. et al. Field-effect chiral anomaly devices with dirac semimetal. Adv. Funct. Mater. 31, 2104192 (2021).

Zeng, H., Dai, J., Yao, W., Xiao, D. & Cui, X. Valley polarization in MoS2 monolayers by optical pumping. Nat. Nanotechnol. 7, 490–493 (2012).

Li, Y. et al. Oxide-based electrolyte-gated transistors for spatiotemporal information processing. Adv. Mater. 32, 2003018 (2020).

Fuller, E. J. et al. Li-ion synaptic transistor for low power analog computing. Adv. Mater. 29, 1604310 (2017).

Sangwan, V. K. & Hersam, M. C. Neuromorphic nanoelectronic materials. Nat. Nanotechnol. 15, 517–528 (2020).

Li, H. et al. Negative magnetoresistance in Dirac semimetal Cd3As2. Nat. Commun. 7, 10301 (2016).

Başar, G., Kharzeev, D. E. & Yee, H.-U. Triangle anomaly in Weyl semimetals. Phys. Rev. B 89, 035142 (2014).

Kharzeev, D. E. The chiral magnetic effect and anomaly-induced transport. Prog. Part. Nucl. Phys. 75, 133–151 (2014).

Son, D. & Spivak, B. Chiral anomaly and classical negative magnetoresistance of Weyl metals. Phys. Rev. B 88, 104412 (2013).

Zhang, N. et al. Magnetotransport signatures of Weyl physics and discrete scale invariance in the elemental semiconductor tellurium. Proc. Natl Acad. Sci. USA 117, 11337–11343 (2020).

Zhang, C.-L. et al. Signatures of the Adler–Bell–Jackiw chiral anomaly in a Weyl fermion semimetal. Nat. Commun. 7, 10735 (2016).

Zhang, C. et al. Room-temperature chiral charge pumping in Dirac semimetals. Nat. Commun. 8, 13741 (2017).

Chen, J. et al. Topological phase change transistors based on tellurium Weyl semiconductor. Sci. Adv. 8, eabn3837 (2022).

Calavalle, F. et al. Gate-tuneable and chirality-dependent charge-to-spin conversion in tellurium nanowires. Nat. Mater. 21, 526–532 (2022).

Wu, Z. et al. Intrinsic valley Hall transport in atomically thin MoS2. Nat. Commun. 10, 611 (2019).

Qiu, B. et al. First-principles simulation of electron mean-free-path spectra and thermoelectric properties in silicon. Europhys. Lett. 109, 57006 (2015).

Lv, Y.-Y. et al. Experimental observation of anisotropic Adler-Bell-Jackiw anomaly in type-II Weyl semimetal WTe 1.98 crystals at the quasiclassical regime. Phys. Rev. Lett. 118, 096603 (2017).

Lin, Z. et al. Two‐dimensional tellurene transistors with low contact resistance and self‐aligned catalytic thinning process. Adv. Electr. Mater. 8, 2200380 (2022).

Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. Nat. Electron. 1, 228–236 (2018).

Yesilyurt, C. et al. Electrically tunable valley polarization in Weyl semimetals with tilted energy dispersion. Sci. Rep. 9, 4480 (2019).

Deng, M.-X., Hu, Y.-C., Luo, W., Duan, H.-J. & Wang, R.-Q. Connection between topological pumping effect and chiral anomaly in Weyl semimetals. Phys. Rev. B 106, 075139 (2022).

Qin, J.-K. et al. Anisotropic signal processing with trigonal selenium nanosheet synaptic transistors. ACS Nano 14, 10018–10026 (2020).

Yang, C. S. et al. All-solid-state synaptic transistor with ultralow conductance for neuromorphic computing. Adv. Funct. Mater. 28, 1804170 (2018).

Collins, J. L. et al. Electric-field-tuned topological phase transition in ultrathin Na3Bi. Nature 564, 390–394 (2018).

Gatti, G. et al. Radial spin texture of the Weyl fermions in chiral tellurium. Phys. Rev. Lett. 125, 216402 (2020).

Sbierski, B., Pohl, G., Bergholtz, E. J. & Brouwer, P. W. Quantum transport of disordered Weyl semimetals at the nodal point. Phys. Rev. Lett. 113, 026602 (2014).

Chen, C.-Z. et al. Disorder and metal-insulator transitions in Weyl semimetals. Phys. Rev. Lett. 115, 246603 (2015).

Zhang, J., Yin, Y. X., You, Y., Yan, Y. & Guo, Y. G. A high-capacity Tellurium@ carbon anode material for lithium-ion batteries. Energy Technol. 2, 757–762 (2014).

Yang, J. J. & Xia, Q. Battery-like artificial synapses. Nat. Mater. 16, 396–397 (2017).

van de Burgt, Y. et al. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 16, 414–418 (2017).

Fuller, E. J. et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 364, 570–574 (2019).

Song, K. M. et al. Skyrmion-based artificial synapses for neuromorphic computing. Nat. Electron. 3, 148–155 (2020).

van De Burgt, Y., Melianas, A., Keene, S. T., Malliaras, G. & Salleo, A. Organic electronics for neuromorphic computing. Nat. Electron. 1, 386–397 (2018).

Zhou, Y. et al. In 2019 IEEE International Electron Devices Meeting. 6.5.1–6.5.4 (IEEE, 2019).

Melianas, A. et al. Temperature-resilient solid-state organic artificial synapses for neuromorphic computing. Sci. Adv. 6, eabb2958 (2020).

Zhang, H.-T. et al. Reconfigurable perovskite nickelate electronics for artificial intelligence. Science 375, 533–539 (2022).

Zhou, Y. et al. Reconfigurable two-WSe2-transistor synaptic cell for reinforcement learning. Adv. Mater. 34, 2107754 (2022).

Qiu, G. et al. Quantum Hall effect of Weyl fermions in n-type semiconducting tellurene. Nat. Nanotechnol. 15, 585–591 (2020).

Kresse, G. & Furthmüller, J. Efficiency of ab-initio total energy calculations for metals and semiconductors using a plane-wave basis set. Comput. Mater. Sci. 6, 15–50 (1996).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865 (1996).

Blöchl, P. E. Projector augmented-wave method. Phys. Rev. B 50, 17953 (1994).

Acknowledgements

This work was supported by the Research Grant Council of Hong Kong (Grant No. PolyU 15301621), the Hong Kong Polytechnic University (Grant Nos.: 1-ZE1T, SB4C and CD42) and the Science, Technology and Innovation Commission of Shenzhen (JCYJ20180507183424383 and SGDX2020110309540000).

Author information

Authors and Affiliations

Contributions

Y.C. supervised this project. Y.C. and J.C. conceived the original concept, analyzed the data and wrote the manuscript. J.C. and J.Y. performed the experiments. J.C. performed DFT calculations. Y.Z. and Y.H. performed neuromorphic computing simulations. J.L. and W.Z. grew materials. L.X. performed the simulations of Ohmic transport. J.W. and T.W. took part in the discussion of manuscript. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Weibo Gao and the anonymous reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Chen, J., Zhou, Y., Yan, J. et al. Room-temperature valley transistors for low-power neuromorphic computing. Nat Commun 13, 7758 (2022). https://doi.org/10.1038/s41467-022-35396-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-022-35396-x

This article is cited by

-

Magnetoresistive-coupled transistor using the Weyl semimetal NbP

Nature Communications (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.