Abstract

The uncontrollable rupture of the filament accompanied with joule heating deteriorates the resistive switching devices performance, especially on endurance and uniformity. To suppress the undesirable filaments rupture, this work presents an interface engineering methodology by inducing a thin layer of NiOx into a sandwiched Al/TaOx/ITO resistive switching device. The NiOx/TaOx interface barrier can confine the formation and rupture of filaments throughout the entire bulk structure under critical bias setups. The physical mechanism behind is the space-charge-limited conduction dominates in the SET process, while the Schottky emission dominates under the reverse bias.

Similar content being viewed by others

Introduction

The modern non-volatile memory has been successfully scaled down to achieve ultra-high-density storage with the development of photolithography technology. However, the conventional charge storage memory is approaching the technical limit and three-dimensional (3D) crossbar structure would be a promising scaling scheme for next generation non-volatile memory1,2. Resistive switching random access memory (RRAM) is favorable with its high-density 3D crossbar integration ability, fast operation speed and low power consumption3,4. In the last two decades, oxide based RRAM has been intensively studied5,6, and TaOx has been recognized as one of potential choices due to its excellent endurance and retention performance7,8. It is well acknowledged that there are only two stable stoichiometric solid phases in TaOx: (a) high oxygen defective phase (or conductive path) and (b) low oxygen defective phase (or insulating matrix)9,10. Such property guarantees relatively stable filaments formation in the TaOx based RRAM devices11,12.

However, nearly all the filaments-type RRAM could not avoid a critical issue that the RESET of device will involve the rupture of filaments, either by ion migration or Joule heating13,14. This issue inevitably causes some negative effects, such as scattered switching voltage distribution and endurance deterioration15,16. Recently, some groups have proposed different designs to improve the filaments property in TaOx based RRAM. For example, Lee et. al. has presented a so-called Metal-Insulator-Base-Metal (MIBM) structure to constrain the filaments in a thin highly insulating Ta2O5-x layer and to use another less insulating TaO2-x layer as the reservoir of oxygen vacancies to enhance the filaments transition in the insulator layer17. By applying different voltages on the 1-transistor-1-memoristor (1T1M) device, Miao et al. realized the manipulation of the filaments in TaOx which related to the oxygen vacancies, and obtained varying switching behavior18. However, these designs still involve the destruction of filaments at the interface area during the reset process, which infers to the abrupt decrease of current by several orders in the I-V characteristic19,20. In this paper, we introduce a thin NiOx layer between TaOx and top electrode to introduce a barrier, which successively prevents the abrupt rupture of the filaments in the RESET process. Our proposal in using a hybrid structure of n-type TaOx and p-type NiOx interface engineering to control the formation of the filaments, instead of breaking and reconnecting them. Our design effectively improves the endurance and uniformity of resistive switching (RS) behavior, and offers an alternative design for future RRAM device.

Results

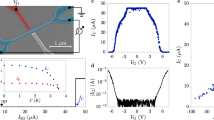

The bipolar RS cycles of ITO/TaOx/NiOx/Al device is demonstrated in Fig. 1a. The electroforming procedure is needed to initialize the resistive switching process (not shown here). As the arrow indicates, the device is initially at the high resistance state (HRS) and the switching cycle starts with a positive DC sweep. A dramatic current increment occurs at around 0.7 V, which corresponds to the SET operation, and the device reaches the low resistance state (LRS). A compliance current (CC) of 10 mA is imposed in order to prevent the permanent breakdown of oxide layers at >1.5 V. As the bias sweeps back from positive to negative region, the device maintains the linear I-V characteristics from 1.5 to ~−0.8 V. The device is reset to HRS again and this completes one switching cycle. The same multiple switching cycles of the regular ITO/TaOx/Al device (without the added NiOx barrier) is also plotted in the inset of Fig. 1a. Several apparent distinctions could be noticed through the comparison. The distribution of the switching threshold voltage is more concentrated and the switching curves are more uniform for the device with the inserted NiOx layer. The two batch of switching curves having different shapes could be further distinguished in the log-log I-V plotting as shown in Fig. 1b. The LRS behaviors of both two devices are similar, however, an obvious abrupt change of current in both SET and RESET processes could be observed only in the regular ITO/TaOx/Al device, but not in our newly proposed ITO/TaOx/NiOx/Al design. The transition of the high and low resistance states becomes smoother after the introduction of NiOx layer between TaOx and top electrode, which indicates that two different switching mechanisms are present in these two different devices (see below).

The HRS and LRS resistance of ITO/TaOx/NiOx/Al device at 200 DC switching cycles is shown in Fig. 2a in order to characterize the endurance performance. The LRS resistance shows excellent consistency and the HRS resistance also becomes relatively stable after first several cycles. The resistance window is maintained well at about one order of magnitude difference, which is sufficient to realize binary storage. The retention characteristic at room temperature is shown Fig. 2b. After continuous sampling for around 106 s, the LRS resistance remains unchanged while the HRS resistance shows a little bit of decay after 105 s. These results manifest the potential application of non-volatile memory with such proposed device structure.

To further reveal the improvement by inserting a thin NiOx layer into the ITO/TaOx/Al structure, the cumulative distribution of switching voltages and two states resistance are also analyzed. In Fig. 3a, both SET and RESET voltages of ITO/TaOx/NiOx/Al device are highly centralized, which are respectively ranged from 0.64 to 0.78, and −0.68 to −0.88 volts, while the voltage distribution of ITO/TaOx/Al one is much scattered (1.3to 4.9 volts, −1.7 to −5.0 volts), which is consistent with the feature shown in Fig. 1. In Fig. 3b, the distributions of the LRS resistance of two devices are both in narrow range (100 Ω to 200 Ω); however, the distribution of the HRS resistance is greatly optimized in the ITO/TaOx/NiOx/Al structure (from a big range of 10 KΩ–100 MΩ to a smaller range of 1–4KΩ). Moreover, the ITO/TaOx/Al device only exhibits less than 100 stable switching cycles at our DC measurement, and the endurance has been improved with additional NiOx layer as indicated in Fig. 2a.

Analysis and Discussions

To determine the mechanism for such a remarkable improvement by introducing a thin p-type NiOx layer, the conduction properties of the as-prepared device and the RS processes are studied. Before electroforming operation, the as-prepared ITO/TaOx/NiOx/Al stacks are in the high resistance state. At this state, the I-V curves with increasing temperatures were plotted in log-log scale in Fig. 4a and b, and we can observe that the cases in the positive and negative sweep ranges are totally different. When the positive bias is applied on top electrode, the IV curves all have a slope of around one at low voltage region (ohmic conduction), but gradually converge to Vc as the electric field increases as demonstrated in Fig. 4a. This is the typical behavior of the trap-limited-conduction21,22. We consider the energy state of the traps solid is described by an exponential function N(E) = Nt/(kTt)exp[(E − Ec)/kTt], where Nt is the trap density, Ec is the band edge energy, k is Boltzmann’s constant and Tt is the characteristic trap temperature. This regime is known as the trap-limited SCLC or Mark-Helfrich (MH) law23 with its current density given by:

where Nc is the effective density of states corresponding to the energy at the bottom of the conduction band, μ is the electron mobility, and 1 = Tt/T is the ratio of distribution of traps to the free carriers. The traps will be gradually filled as the electric field increased at all temperatures. When the applied voltage reach a critical value, all traps will be filled. This critical voltage is independent of temperature and given by ref. 22:

where q is the electron charge. By extrapolating the I-V curves, we obtain a typical value for Vc, which is about 10 volts for our device. The electron transport behavior is confirmed to be in the trap-limited region.

When negative bias is applied, the IV curves follow the Schottky emission24:

where  is the Richardson constant, T is the temperature, ϕ is the barrier height. By re-plotting the I-V curves in the form of

is the Richardson constant, T is the temperature, ϕ is the barrier height. By re-plotting the I-V curves in the form of  (see Fig. 4b), the linear and parallel feature at high (negative) voltage region agrees well with the Schottky emission process. Furthermore, the Arrhenius plots in Fig. 4c show the linearity of

(see Fig. 4b), the linear and parallel feature at high (negative) voltage region agrees well with the Schottky emission process. Furthermore, the Arrhenius plots in Fig. 4c show the linearity of  relationship, which also confirms the dominant conduction in the negative voltage region is Schottky emission25. For comparison, we also analyzed the I-V characteristics of Al/NiOx/Al and ITO/TaOx/ITO stacks. It is found that the SCLC is the main conduction mechanism in these two stacks, which excludes the barrier effect at Al/NiOx and ITO/TaOx interfaces. Thus, we conclude the Schottky emission observed in ITO/TaOx/NiOx/Al is attributed to the n-type TaOx and p-type NiOx interface barrier.

relationship, which also confirms the dominant conduction in the negative voltage region is Schottky emission25. For comparison, we also analyzed the I-V characteristics of Al/NiOx/Al and ITO/TaOx/ITO stacks. It is found that the SCLC is the main conduction mechanism in these two stacks, which excludes the barrier effect at Al/NiOx and ITO/TaOx interfaces. Thus, we conclude the Schottky emission observed in ITO/TaOx/NiOx/Al is attributed to the n-type TaOx and p-type NiOx interface barrier.

The conduction properties in LRS and HRS are also investigated. From the I-V curves plotted in the log-log scale in Fig. 5a, a typical SCLC behavior in HRS could be identified. As the injected carriers are not comparable with intrinsic thermal carriers in low voltage region, ohmic conduction with slope of about 1 ( = 1.05 indicated in Fig. 5a) is expected. The current density depends proportionally on the concentration of thermally generated carriers n0, given as

With higher injecting current density, the injected carriers promptly fill the traps in the oxides, which lead to a high current gain with a slope of 21.74. These traps are well known to be as oxygen vacancies for n-type TaOx and Ni vacancies for p-type NiOx. This region is known as the trap-limited SCLC or Mark-Helfrich (MH) law23 given by Eq. (1) with slop 1 + 1. When the traps are gradually occupied fully, the slope reduces to around 2 ( = 2.09 indicated in Fig. 5a), indicating that the conduction enters the trap-free SCLC, and the current density is determined by the Mott-Gurney (MG) law26,27:

For the LRS, the high current with ohmic conduction is the standard metallic property of filament formed in oxide28. In the RESET process as shown in Fig. 5b, the ohmic behavior with the slope of 1 is still maintained in LRS until the filament based conduction is gradually impeded and the device gets back to HRS. The slope of 1 in HRS corresponds to the low thermal current in oxide again.

Based on the above results, the different RS process in these two stacks could be described by taking into the consideration of both filaments and interface barriers effects (see Fig. 6). For a ITO/TaOx/NiOx/Al device (Fig. 6c), the positive voltage on top electrode will reduce the TaOx/NiOx barrier and enables injected electron hopping among the traps (usually oxygen vacancies in TaOx) to realize the conduction throughout the whole stacks29. When the voltage increase, we enter the SCLC regime, and the oxygen vacancies migrate along the applied field (to the bottom ITO/TaOx interface), which will trigger soft dielectric breakdown from bottom up. When the filaments formed completely with the migration of oxygen vacancies and successively passed through the n-TaOx/p-NiOx interface to the top electrode, the device is set to LRS states. Concurrently, the oxygen vacancies in NiOx will be extracted to TaOx with the positive bias, which will also make both oxide layers to be more conductive to facilitate the filament based conduction. Thus the LRS is sustainable even after removing the external field due to the existence of filament, which satisfies the non-volatile storage.

Subsequently, when negative voltage is applied on the top electrode (Fig. 6d), the filamentary conduction still maintains in a small region. However, the increasing reverse bias on n-TaOx/p-NiOx junction will raise the barrier height and hinder the conduction to reset the device to HRS. Similarly, the negative voltage will also absorb some oxygen vacancies from TaOx back into NiOx and make them to be highly resistive, further impeding the reverse current. It is worth to mention that the filaments in TaOx are not broken here, because the current is reducing gently instead of abrupt drops as shown in Fig. 1b. This provides the evident that the gradually rising TaOx/NiOx barrier weakens the filamentary conduction through the interface, avoiding the rupture of filaments. Therefore, the next SET cycle will only need to lower the barrier and enable the filaments passing through again without the requirement of reconnecting or repairing any rupture filaments.

For the traditional ITO/TaOx/Al device (Fig. 6a and b), a filament rupture procedure at TaOx/ITO interface with negative bias is required in RESET operation, which is consistent to a sudden current drop of several orders depicted in Fig. 1b 30. From the comparison, we could understand that the improvement of RS by inserting a NiOx layer is mainly ascribed to employing an interface barrier effect to control the filaments conduction without making any destructive operation on the filaments as in the RS processes. The resistance fluctuation, especially in the HRS, is greatly suppressed because the HRS originates from the reverse bias of barrier, not from the randomly broken filaments. The switching threshold value is also optimized because tuning the barrier height is much more stable than the ruinous handling of filaments. At the same time, a better endurance could be also obtained by selecting this gentle RESET strategy. The major defect in NiOx is Ni vacancy, so under the reverse bias, the oxygen vacancies migrate into NiOx, counteracting the Ni vacancies and form more stoichiometric NiO which are higher resistive. The process is similar like the formation of space charge region in PN junction, which is due to the major carrier election in N region diffusing into P region. Such process somehow causes some so-called “damage” on the filament but only at the TaOx/NiOx interface region. Such “damage” is actually a part of the “barrier tuning filament” effect, and will not affect the whole filament establish inside TaOx.

Summary

In conclusion, an interface engineering resistive switching device of ITO/TaOx/NiOx/Al structure was designed and fabricated. The device shows an enhanced improvement in the endurance performance and the distribution of switching voltages and resistance over the traditional ITO/TaOx/Al structure. For the as-prepared device, SCLC is the main conduction mechanism in the positive bias regime, and Schottky emission dominates the conduction in negative bias regime, which proves the formation of a confined TaOx/NiOx interface barrier. The introduction of such an interface barrier with TaOx can control and manipulate the passing status of filaments efficiently. The proposed design avoids the rupture of filaments in RESET process, which will enable a more uniform and stable resistive switching behavior comparable to other RRAM devices12,17,31.

Experiment Section

The Al/NiOx/TaOx/ITO RRAM devices were fabricated by magnetron sputtering system at room temperature. The ITO commercial glass was employed as the substrate for deposition and bottom electrode. A 50 nm n-type TaOx layer was deposited by using a Ta2O5 target with the RF sputtering power of 100 W. The pressure sputtering chamber was maintained at an Ar (Argon) atmosphere of 5 × 10−3 Torr. A 10 nm p-type NiOx layer followed in the same chamber atmosphere by using a NiO target with the RF power of 70 W. Lastly, a 200 nm Al top electrode layer was deposited with a shadow mask by using DC sputtering power of 60 W. A traditional ITO/TaOx/Al RRAM device was also fabricated for comparison. The conduction type of TaOx and NiOx were confirmed by Hall effect measurement. I-V characterization was carried out on a probe station with the Keithley 4200 SCS semiconductor parameter analyzer. During the DC mode measurement, the biases with different polarities were applied on the Al top electrode and the ITO bottom electrode was always grounded.

Additional Information

How to cite this article: Zhu, Y. B. et al. Enhanced stability of filament-type resistive switching by interface engineering. Sci. Rep. 7, 43664; doi: 10.1038/srep43664 (2017).

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

Chang, S. H. et al. Oxide double-layer nanocrossbar for ultrahigh-density bipolar resistive memory. Adv. Mater. 23, 4063 (2011).

Kang, B. S. et al. High-current-density CuOx/InZnOx thin-film diodes for cross-point memory applications. Adv. Mater. 20, 3066 (2008).

Sawa, A., Resistive switching in transition metal oxides. Mater. Today 11, 28 (2008).

Linn, E., Rosezin, R., Kugeler, C. & Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 9, 403 (2010).

Hsu, C. W. et al. Homogeneous barrier modulation of TaOx/TiO2 bilayers for ultra-high endurance three-dimensional storage-class memory. Nanotechnology 25, 165202 (2014).

Lee, M. J. et al. Electrical manipulation of nanofilaments in transition-metal oxides for resistance-based memory. Nano Lett. 9, 1476 (2009).

Yang, J. et al. Engineering nonlinearity into memristors for passive crossbar applications. Appl. Phys. Lett. 100, 113501 (2012).

Rahaman, S. Z. et al. Excellent resistive memory characteristics and switching mechanism using a Ti nanolayer at the Cu/TaOx interface. Nanoscale Res. Lett. 7, 345 (2012).

Yang, J. J. et al. High switching endurance in TaOx memristive devices. Appl. Phys. Lett. 97, 232102 (2010).

Yang, J. J. et al. Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotech. 3, 429 (2008).

Wu, X. et al. Evolution of filament formation in Ni/HfO2/SiOx/Si-Based RRAM devices. Adv. Electron. Mater. 1, 6 (2015).

Yang, Y. C. et al. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 3, 8 (2012).

Kurnia, F., Liu, C., Jung, C. U. & Lee, B. W. The evolution of conducting filaments in forming-free resistive switching Pt/TaOx/Pt structures. Appl. Phys. Lett. 102, 152902 (2013).

Zhang, L. J. et al. Unipolar TaOx-based resistive change memory realized with electrode engineering. IEEE Electron Device Lett. 31, 966 (2010).

Alexandrov, A. S. et al. Current-controlled negative differential resistance due to joule heating in TiO2 . Appl. Phys. Lett. 99, 202104 (2011).

Singh, B., Mehta, B. R., Varandani, D., Savu, A. V. & Brugger, J. CAFM investigations of filamentary conduction in Cu2O ReRAM devices fabricated using stencil lithography technique. Nanotechnology 23, 495707 (2012).

Lee, M. J. et al. A high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x/TaO2-x bilayer structures. Nat. Mater. 10, 625 (2011).

Miao, F. et al. Continuous electrical tuning of the chemical composition of TaOx-based memristors. ACS Nano 6, 2312 (2012).

Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 6, 833 (2007).

Yang, J. J., Borghetti, J., Murphy, D., Stewart, D. R. & Williams, R. S. A family of electronically reconfigurable nanodevices. Adv. Mater. 21, 3754 (2009).

Yang, Y. C., Pan, F., Liu, Q., Liu, M. & Zeng, F. Fully room-temperature-fabricated nonvolatile resistive memory for ultrafast and high-density memory application. Nano Lett. 9, 1636 (2009).

Kumar, V., Jain, S. C., Kapoor, A. K., Poortmans, J. & Mertens, R. Trap density in conducting organic semiconductors determined from temperature dependence of J-V characteristics. J. Appl. Phys. 94, 1283 (2003).

Mark, P. & Helfrich, W. Space-charge-limited currents in organic crystals. J. Appl. Phys. 33, 205 (1962).

Choi, J. S. et al. Different resistance switching behaviors of NiO thin films deposited on Pt and SrRuO3 electrodes. Appl. Phys. Lett. 95, 022109 (2009).

Chang, C. W. et al. Electrically and optically readable light emitting memories. Sci. Rep. 4, 5121 (2014).

Rose, A. Space-charge-limited currents in solids. Physical Review 97, 1538 (1955).

Lampert, M. A. & Mark, P. Current injection in solids(Academic, New York) (1970).

Chang, W. Y. et al. Improvement of resistive switching characteristics in TiO2 thin films with embedded Pt nanocrystals. Appl. Phys. Lett. 95, 042104 (2009).

Harada, T. et al. Trap-controlled space-charge-limited current mechanism in resistance switching at Al/Pr0.7Ca0.3MnO3 interface. Appl. Phys. Lett. 92, 222113 (2008).

Cha, D., Lee, S., Jung, J., An, I. & Kim, D. W. Bipolar resistive switching characteristics of Cu/TaOx/Pt structures. J. Korean Phys. Soc. 56, 846 (2010).

Evegeny M., Hoskins, B. D., Strukov, D. B. & Stemmer, S. Resistive switching and its suppressionin Pt/Nb:SrTiO3 junctions. Nat. Comm. 5, 3990 (2014).

Acknowledgements

This project is funded by Singapore MOE T2 grant (T2MOE1401). X. Wu would like to acknowledge support from National Natural Science Foundation of China (11504111, 61574060), Projects of Science and Technology Commission of Shanghai Municipality (15JC1401800, 14DZ2260800), and the Program for Professor of Special Appointment (Eastern Scholar) at Shanghai Institutions of Higher Learning and Shanghai Rising-Star Program (17QA1401400).

Author information

Authors and Affiliations

Contributions

Y.B. Zhu and X. Wu designed the experiments. K. Zheng fabricated the RRAM device. Y.B. Zhu carried out the electrical measurements and did the modeling on the space-charge mechanism. X. Wu and L.K. Ang analysis the data. All authors read and revised the manuscripts.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Zhu, Y., Zheng, K., Wu, X. et al. Enhanced stability of filament-type resistive switching by interface engineering. Sci Rep 7, 43664 (2017). https://doi.org/10.1038/srep43664

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep43664

This article is cited by

-

On resistive switching and dielectric spectroscopy characteristics of topological insulator-based heterojunction for memory applications

Applied Physics A (2024)

-

Mimicking biological synapses with a-HfSiOx-based memristor: implications for artificial intelligence and memory applications

Nano Convergence (2023)

-

Impact of crystallinity on coexistence of negative differential resistance (NDR) and write once read many (WORM) resistive switching memory in multiferroic BiFeO3 (BFO)

Applied Physics A (2023)

-

Multilayer redox-based HfOx/Al2O3/TiO2 memristive structures for neuromorphic computing

Scientific Reports (2022)

-

Conduction and Resistive Switching in Dropcast CdTe/CdSe Core-Shell Quantum Dots Embedded Chitosan Composite

Iranian Journal of Science and Technology, Transactions A: Science (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.