Abstract

Realizing a low-temperature polycrystalline-silicon (LTPS) thin-film transistor (TFT) with sub-kT/q subthreshold slope (SS) is significantly important to the development of next generation active-matrix organic-light emitting diode displays. This is the first time a sub-kT/q SS (31.44 mV/dec) incorporated with a LTPS-TFT with polycrystalline-Pb(Zr,Ti)O3 (PZT)/ZrTiO4 (ZTO) gate dielectrics has been demonstrated. The sub-kT/q SS was observed in the weak inversion region at −0.5 V showing ultra-low operating voltage with the highest mobility (250.5 cm2/Vsec) reported so far. In addition, the reliability of DC negative bias stress, hot carrier stress and self-heating stress in LTPS-TFT with negative capacitance was investigated for the first time. It was found that the self-heating stress showed accelerated SS degradation due to the PZT Curie temperature.

Similar content being viewed by others

Introduction

Almost 40 years have passed since several groups first demonstrated the amorphous-Si (a-Si) thin-film transistor (TFT) on a glass substrate1,2,3,4. It was successful in encouraging the mass-production of liquid crystal displays (LCDs) because of its simple and low-thermal budget. However, it is now limited for use in the active-matrix organic light-emitting diode (AMOLED) display, which is considered the next generation display. To address the poor electrical properties of the TFT, such as low current density, low field-effect mobility and high power dissipation, the low-temperature polycrystalline-Si (LTPS) TFT was introduced to continue the development of AMOLED displaysx4. However, the ongoing stringent performance and scaling of TFT will eventually be limited in the near future10,11. Although the LTPS-TFT shows a relatively higher electrical performance than the a-Si TFT, LTPS-TFT still has issues of unreliability and high voltage operation, which is believed to have originated from the grain boundary12,13,14. It was previously reported that the high power dissipation or high voltage operation can be significantly reduced if the high-k dielectric is incorporated with the LTPS-TFT15,16,17. In addition, the operation voltages are significantly related to the subthreshold slope (SS) which is an inverse of the drain current (Ids) variation that can be obtained for a unit gate voltage (Vgs) variation. According to Boltzmann thermodynamics, the SS of an ideal Si metal-oxide-semiconductor field-effect transistor (MOSFET) cannot be lower than 60 mV/dec (~2.3 kT) at room-temperature. For the development of a capable high-k dielectric, it is significantly important that SS can reach 60 mV/dec. Recent reports demonstrate a tunneling MOSFET18,19,20,21 using the band-to-band tunneling or impact ionization and ferroelectric-gate MOSFET22,23,24,25,26 using negative capacitance, where the carrier transports are independent of the Boltzmann thermodynamics. In the case of tunnel MOSFETs, the electrical properties are less sensitive to the gate dielectric than ferroelectric-gate MOSFET, but are strongly sensitive to the channel defect state which may not be suitable for the high defect-state LTPS27,28. On the other hand, the ferroelectric-gate MOSFET was not sensitive to the channel defect state, but was sensitive to the negative capacitance of the gate dielectric29,30. However, in the context of semiconductor manufacturing, integrating a single-crystal ferroelectric thin-film to Si is impossible. For example, perovskite-structured SrTiO3 is an excellent substrate for the growth of high qualified crystalline BaTiO3, but cannot be used as part of a Si-based gate dielectric because of its undesirable reaction and negligible band offset31,32,33. In order to integrate a ferroelectric thin-film in LTPS or c-Si, polycrystalline-ferroelectric thin-film needs to be used.

In this work, we developed a LTPS-TFT with ZrTiO4(ZTO)/Pb(Zr,Ti)O3(PZT) gate stacks to realize an ultra-steep SS for the first time. Using the negative capacitance in PZT, the SS was 38.2 mV/dec, which is the best SS in LTPS-TFT reported so far. The concept of using negative capacitance is consistent with the Landau-Khalatnikov (L-K) equation. Moreover, the reliability was investigated under DC positive-bias stress, hot-carrier stress and self-heating stress.

Results and Discussion

According to an ideal Si-based MOSFET, the SS is defined as:34

where ψs is the surface potential of Si, Cs is the Si capacitance and Cinv is the gate insulator capacitance. Note that Ids is restricted to the kTxln10/q term because the carrier transport diffusion is limited to the Boltzmann thermodynamics. If the Cs/Cinv reaches 0, the SS would be 60 mV/dec at room temperature. In order words, this minimum SS puts a fundamental lower limit on the operating voltage and power dissipation. In fact, it is impossible for Cs/Cinv to reach 0 because the Cinv cannot be infinite. Cinv is a series of the multi-stack dielectrics where CZTO and CPZT in our case are in equivalent circuits as shown in Fig. 1a:

(a) Configuration of LTPS-TFT with equivalent capacitance circuit. The PZT/ZTO/poly-Si cross-section was observed from the HR-TEM image. From the HR-TEM image, the EDS profile of the Pt/PZT/ZTO/poly-Si was observed. (b) XRD 2-theta profile of Pt/PZT/ZTO/poly-Si structured device. (c) AES depth profile for different elements of PZT/ZTO/poly-Si.

where CZTO was 2.21 pF/m2 with 2-nm thickness and CPZT was 62.66 pF/m2 with 200-nm thickness. Thus, Cinv was 2.13 pF/m2, which is not infinite. This confirms that the ferroelectric-gate MOSFET is related to the m-factor determined by the ψs and capacitance while, the tunneling MOSFET is related to the n-factor. Generally, the m-factor has a limited value in the range from 0 to 1, but this limited range is not considered when the capacitance is negatively expressed, as in the equation:

when the CPZT becomes negative, equation (3) becomes:

The m-factor eventually becomes a negative value ranging from −1 to 0. Thus, the surface potential could be amplified to achieve SS less than 60 mV/dec. As shown in Fig. 1a, the LTPS-TFT with the PZT/ZTO gate stacks is well formed with a smooth interface with PZT/ZTO and ZTO/LTPS, as observed from high-resolution transmission microscopic images (HR-TEM). The PZT and ZTO were crystallized by rapid thermal annealing (RTA) for 30 sec at 600 °C in air ambient. The crystallized PZT and ZTO showed various crystal planes observed from the x-ray diffraction (XRD) 2-theta profile (Fig. 1b). The PZT showed perovskite-structured with (100), (111) and (200) orientated textures. When using crystallized PZT on top of Si, it is important to prevent the interdiffusion of Pb elements because of the undesirable reaction between PZT and Si. The role of thin ZTO is to block the Pb diffusion during the crystallization35,36. Although the Pb element can be perfectly blocked in a thick-ZTO, a thick ZTO shows a large charge compensation loss which could easily depolarize the PZT. Unfortunately, a depolarization field (Dde) is always present when the PZT is used in a metal-ferroelectric-insulator-semiconductor (MFIS) structure. The depolarization field in the MFIS structure can be expressed as34:

Here, P is the polarization dipole moment and ε is the PZT dielectric constant. It is found that the minimum thickness of ZTO with a maximum inter-diffusion barrier needs to be determined in order to reduce the Ede. The thickness of 2 nm is the optimized minimum ZTO. The atomic percentage measured by auger electron spectroscopy (AES) is shown in Fig. 1c. A large Pb element with high percentage was observed in the interface of ZTO, whereas it significantly dropped to 0% in the center of the ZTO thin-film. It is confirmed that even a 2.5-nm thick ZTO is sufficient for preventing the diffusion of Pb toward Si. This result is consistent with the energy-dispersive x-ray spectroscopy (EDS) images shown in the inset in Fig. 1a. To address these material characteristics, the buffer layer needs to be reduced to 1 nm to realize the full potential of the ferroelectric-gate MOSFET.

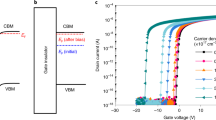

To understand the negative capacitance in PZT, the capacitance in terms of energy (U) is shown in Fig. 2. U can be expressed in terms of a variation in U as a function of variation in stored charges (Qf):

(a) Energy diagram of ferroelectric in the absent bias in Pt. The capacitance is negative in the unstable region of Qf = 0. (b) Evolution of the energy diagram with small bias to polarize the PZT layer. (c) Evolution of the energy diagram with larger bias than (b) but smaller than the coercive voltage of PZT. The schematic MFIS structure represents the polarization switching in each energy diagram.

From the equation, a quadratic relation occurs between U and Qf. Some materials, known as paraelectric materials, show a nonlinear P as a function of the electric field, which implies that U and P have a slight possibility of having a single point corresponding to P = 0. In the case of the initial state P, the U landscape is titled and induces the polarized dipoles to move to the nearest minimum U when a voltage is applied to the Pt gate (Fig. 2a). In this situation, it is difficult to observe a negative capacitance. After applying more voltage to the Pt gate, but less than the PZT coercive voltage (Ec), the polarization dipole would move to the P = 0 point with balancing U (Fig. 2b). If the voltage is larger than the PZT Ec, the polarization will move to the other side of the remaining minimum energy (Fig. 2c). This implies that the negative capacitance will descend when the PZT is more biased than the Ec. Therefore, the PZT has a strong possibility of passing through the negative differential capacitance. In addition, the total capacitance (PZT+ZTO) should be stabilized in series with the paraelectric and ferroelectric capacitors. The negative capacitance of a single-layer of ferroelectric could not be observed.

Figure 3a shows the Qfe-Eeff characteristics of Pt/PZT(100-nm)/ZTO(2-nm)/LTPS and Pt/ZTO(102-nm)/LTPS. The capacitor with PZT showed a clear saturation remnant polarization (Pr) and large Ec, while the capacitor without PZT showed no Pr or Ec. The Landau-Khalatnikov (L-K) model is applied to the P-E data, giving the Qfe-Eeff relation39,40,41,42,43:

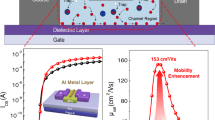

(a) Qfe-Eeff measurements of Pt/PZT(100-nm)/ZTO(2-nm)/LTPS and Pt/ZTO(102-nm)/LTPS and its Landau-Khalatnikov (L-K) fitting. (b) Ids-Vgs measurements at Vds = −0.1 V and W = L = 3.5/2 μm. The C-V characteristic is shown in inset figure. (c) Steep switching during turn on observed in weak inversion region. (d) Ids-Vds characteristics with 7 steps of Vgs from 0 to −15 V.

where α, β and γ are the material dependent constants. The α, β and γ were obtained as 4.82 × 108 m/F, 4.1 × 108 m5/F/C2 and 4.8 × 1010 m10/F/C4, respectively. This constant is consistent with the other epitaxial-PZT. These results are the proof of negative capacitance in PZT. As shown in Figs 2 and 3a, starting from the initial P, as a voltage is applied across the ferroelectric capacitor, the energy landscape is tilted and the polarization will move to the nearest local minimum. During this mechanism, the negative capacitance spontaneously appears. This transition respect to the voltage appears when the applied voltage is smaller than coercive voltage (Vc). If the gate voltage is larger than Vc, one of the minima energy potential disappears and Qf moves to the remaining minimum of the energy. In other word, the negative capacitance is vanished when the gate voltage is larger than the Vc. In our case, the Vc of PZT was −0.5 to 0.5 V indicating the negative capacitance range. Increasing the Vgs above 0.5 V shows normally positive capacitance. Fortunately, the system of our PZT/ZTO/LTPS stacked TFT shows a subthreshold region and weak inversion. The general chemical formula for PZT-perovskite compounds is ABO3, where ‘A’ and ‘B’ are two cations of very different sizes and X is an anion that both to both A and B. Typically, the ‘A’ atoms are larger than the ‘B’ atoms. In the PZT system, ‘A’ corresponds to Pb atom, ‘B’ corresponds to Zr and Ti atoms and ‘O’ was oxygen atom. The ideal cubic-symmetry structure has B cation in 6-fold coordination, surrounded by an octahedron of anions and the A cation in 12-fold cub-octahedral coordination. According to the crystal structure of PZT, the Zr and Ti atoms move up-and-downward depending on the electrical field. These movements form polarization dipoles. As a result, it is possible to create a negative capacitor by tuning the polarization by Zr and Ti atoms. Moreover, the increasing voltage induces the opposite polarity to the Si channel. These polarizations behave nonlinearly, meaning that small increments in the voltage can lead to disproportionate changes in the PZT polarization. It is mainly reported that PZT have a spontaneous polarization that flips above a certain critical voltage which is Vc, yielding an enormous and sudden accumulation of bound charge at the poly-Si surface44,45,46. Previously, Salahuddin et al. confirmed that PZT ferroelectric ‘negative-capacitance’ state maintains only for as long as the ferroelectric polarization is switching and remained unscreened47. To prevent the screening, an insulator (in our case ‘ZTO’) is inserted at the interface between the ferroelectric and poly-Si (Figure S1). There were already some experimentally demonstration of negative capacitance based on the PZT48,49. Figure 3b shows the Ids-Vgs characteristics of the Pt/PZT/ZTO/LTPS device at Vds = −0.1 V to measure the SS. The SS of LTPS-TFT showed 31.44 mV/dec at the upper curve and 37.73 mV/dec at the lower curve. Both curves of SS are observed not at low Vgs, but at high Vgs, which is a weak inversion region (Fig. 3c). The off-current is observed at 10−5 A/μm with hysteresis of 0.26 V. The charges for strong inversion are formed at approximately 0.25 V, which is the lowest operation voltage of LTPS reported so far. In the inset figure, the negative capacitance having −0.5 pF/cm2 was observed in the weak inversion region near the Vgs = 0.25 V measured at 100 kHz. Moreover, we have measured the capacitance-frequency curves where the frequency was swept from 100 Hz to 1 MHz at Vgs = 0 and −0.5 V. It was confirmed that the negative capacitance values were observed in all frequency spectrum (Figure 2S). The value of negative capacitance has started to decrease and almost showed saturation. We believe that the deep depletion originated from the high-frequency in the LTPS channel affects the total capacitance. This experiment confirms that the sub-kT/q SS is obtained when the Vgs ranges from −0.5 to 0 at the upper curve and from −0.3 to 0.5 at the lower curve. Both curves of SS are observed not at low Vgs, but at high Vgs, which is a weak inversion region (Fig. 3c). In addition, the Ion/Ioff ratio was 1.1 × 105 at Vds = −0.1 and was increased to 1.0 × 106 at Vds = −1V. The Ids-Vds characteristics are shown in Fig. 3d. The LTPS-TFT showed clear saturation even at a −1 V of low Vds and a good ohimic contact was observed in the linear region. No kink or snap-back effect was observed in our LTPS-TFT, which is important to drive the AMOLED displays50,51. The saturation field-effect mobility (μfe) that is independent of Vds was obtained from the following expression:

The square root of the saturation current is linearly dependent of the Vgs and the μfe can be extracted from the slope of Ids1/2 vs the Vgs curve. The μfe was 250.5 cm2/Vsec, which is the highest mobility in LTPS-TFT52,53,54. We can estimate that μfe strongly depends on Cox. In the device, the Cox with the use of PZT/ZTO is much higher than that of typical SiO2 due to the high dielectric constant of PZT (εr ~ 1050).

One of the important characteristics of the LTPS-TFT is its reliability. It has been identified that the LTPS-TFT has three main degradation mechanisms under DC bias-stress, hot-carrier stress and self-heating stress. Figure 4a shows the degradation of LTPS-TFT with negative capacitance as a function of the DC negative bias-stress. The −10 V of the DC negative bias was applied at the Pt gate and grounding of the S/D. From our result, SS was slightly increased after stress for 100 sec, with a slight decrease to 90% of the on-current. Applying −10 V to the Pt-gate shows a strong inversion of hole carriers at the interface between ZTO and LTPS. These inversion carriers strongly influence the interface state, trap state generation and fixed charge formation originating from the depassivation of the weak Si-H bonds located at the interface of the grain boundaries55,56,57. The increase in the number of interfacial traps and the increased depolarization field, which are generated by the broken hydrogen atoms, might be the main source of SS degradation. Figure 4b shows the degradation in the hot-carrier (HC) stress. The Pt gate was biased at −1 V for the strong inversion without any damage to the interface and Vds was biased to −10 V. The carrier is exposed to a high electrical field in the near drain junction; it therefore gains enough energy to become HCs, creating a defect and carrier injection in the PZT at the grain-boundary near the drain junction. This shows that the on-current decreased to 70% and the SS has slightly decreased to 40 mV/dec after stress for 103 sec. Damaging the interface near the drain junction is significantly related to the on-current because of the pinch-off phenomenon, whereas the SS is not strongly affected because the injected charges are insufficient and could become trapped in the ZTO, thus diminishing the negative capacitance. In addition, for conventional LTPS-TFTs with SiO2 gate dielectric, the shorter channel length induces larger HC degradation, which is attributed to the higher electric field for the shorter channel length. The degradation of self-heating stress is shown in Fig. 4c. The self-heating stress was performed at −0.5 V of Vgs and 70 μW/μm2 (Vds x Jds = −1 V x −7 × 10−5 A/μm2). In contrast to the DC negative bias-stress, the self-heating stress combined with high electric field and high power could distort the strong Si-Si bonds located in the entire channel grain boundary58,59. It has been reported that grains with high angle-grain boundary and microtwins intensify the degradation60. Unlike the conventional LTPS-TFT with SiO2 dielectrics, the LTPS-TFT with ferroelectric dielectric is more seriously degraded because of its temperature-dependent polarization. Self-heating stress generates Joule heat and degrades the whole interface and grain boundaries. To alleviate the self-heating stress, an effective method is to dissipate the heat quickly in the substrate. Ferroelectric materials exhibit a spontaneous electric polarization below a critical temperature. However, the negative capacitance will be unstable or not observable and eventually PZT would be paraelectric in the high temperature caused by the self-heating stress61,62,63. The Joule heat can increase to about 500 K in LTPS with 120 μW/μm2. As shown in Fig. 5a, the total capacitance (PZT+ZTO) shows ferroelectric properties as indicated by the two negative minimum U points. It is found that the negative capacitance is unstable or not observed unless it is electrically biased to tilt the U at room-temperature (300 K). In Fig. 5b, the total capacitance (PZT+ZTO) shows a stable point in the negative capacitance U and ferroelectric properties. The roles of the two layers are ferroelectric in PZT and paraelectric in ZTO. However, the total capacitance of (PZT+ZTO) changed to the paraelectric capacitor because the temperature is above the Curie temperature of PZT (Fig. 5c)64. Thus, it is not possible to observe a negative capacitance.

Degradation of subthreshold slope (SS) and drain current (Ids) as a function of (a) DC negative-bias stress, (b) hot-carrier stress and (c) self-heating stress. The DC negative-bias stress was performed under −10 V of Vgs with grounding Vds. The hot-carrier stress was performed under −0.5 V of Vgs and −10 V of Vds to induce the ion-impact ionization near the drain junction. The self-heating stress was performed at −0.5 V of Vgs and 70 μW/μm2 (Vds × Jds = −1 V × −7 × 10−5 A/μm2). All device dimensions were W = 3 μm and L = 2.5 μm.

(a) At 100 K, PZT as a ferroelectric and ZTO as a paraelectric capacitor where the total capacitor (PZT+ZTO) remains. (b) At 300 K, PZT as a ferroelectric and ZTO as a paraelectric capacitor, where the total capacitance (PZT+ZTO) is dominated in the paraelectric capacitor. (c) At 500 K, both PZT and ZTO are combined with two paraelectric capacitors.

For over a decade, several groups have attempted to improve the μfe and SS in LTPS. Starting from SiO2 (εr = 3.9)65, which is known as the most stable and perfect interface between Si among the other oxides, dielectrics with Si3N4, Al2O3, Y2O3, Eu2O3, ZrTiO4 and HfO2, etc. were developed and a steep SS was successfully realized, reaching up to 60 mV/dec (Fig. 6)66,67,68,69,70,71. However, a larger dielectric constant is needed to reach 60 mV/dec. Although some ultra-high-k dielectrics such as TiO2 (80~100)72, SrTiO3 (200~300)73, and BaSrTiO3 (1000~1250)74 have been attempted, they cannot be used with the LTPS-TFT because of its high gate current, poor thermal stability and rare-earth elements. Thus, using PZT with a ZTO buffer layer shows good gate stacks for realizing the high performance LTPS-TFT.

Conclusion

In summary, we successfully demonstrated for the first time a sub-kT/q SS (31.44 mV/dec) incorporating a negative capacitance in LTPS-TFT. The total structure of the proposed LTPS-TFT was Pt (200 nm)/PZT(100 nm)/ZTO(2 nm)/LTPS(50 nm) in a p-type channel. We systematically investigated the negative capacitor as a function of energy and stored charges to explain a way to achieve a sub-kT/q SS (<60 mV/dec). Moreover, the reliability of DC negative bias stress, hot-carrier stress and self-heating stress was measured. Unlike the conventional LTPS-TFT with SiO2 gate dielectrics, the LTPS-TFT with PZT/ZTO showed a significant SS degradation on the self-heating stress because the PZT showed paraelectric properties rather than ferroelectric properties. It can be concluded that the performance of LTPS-TFT using negative capacitance can be realized by true low power LTPS-TFT for future AMOLED displays.

Methods

Fabrication

LTPS-TFT using negative capacitance structure was fabricated on glass substrate (Corning Eagle XG, 100 × 100 mm2). The total structure was Pt(200 nm)/PZT(100 nm)/ZTO(2 nm)/LTPS/(200 nm)SiO2/glass as shown in Fig. 1a. The fabrication process begins with depositing a 50-nm-thick a-Si on a 200-nm-thick SiO2 coated glass substrate. The a-Si was then crystallized with 5-nm thick Ni for metal-induced lateral crystallization (MILC) by annealing at 550 °C for 2 hrs in H2 ambient. The detailed MILC conditions and mechanism have been reported elsewhere75,76. After the crystallization, the LTPS surface was subsequently cleaned with RCA1 (NH4OH:H2O2:D.I = 5:1:1), RCA2 (HCl:H2O2:D.I = 6:1:1) and piranha solution (H2SO4:H2O2:D.I = 3:2:1) to remove the Ni and residual defects. A 2-nm-thick ZrTiO4 (ZTO) was deposited by RF reactive magnetron sputtering using a single composite target (99.999% purity) with O2:Ar = 10:1 at 200 °C. A 100-nm-thick Pb(Zr, Ti)O3 (PZT) was subsequently deposited using a single composite target (PbZr0.52Ti0.48O3, 99.9999% purity) with O2:Ar = 10:1 at 200 °C. After the deposition, the ZTO/PZT was crystallized using a 0.5-sec Xe-lamp pulse at 700°C in air ambient. The crystallization is confirmed by the XRD profile (Fig. 1b). Next, a 200-nm-thick Pt gate electrode was deposited by DC magnetron sputtering at room-temperature. The Pt/ZTO/ZTO was patterned for the self-aligned source and drain B2H6 doping. Boron dopants were implanted at accelerating voltages of 17 keV and RF power of 150 W. Finally, the dopant was electrically activated by annealing for 2 hr in H2 ambient. The whole fabrication process was carried out in a 1000-class clean room (Eui-San Research Center, Seoul National University).

Measurement

The measurements for electrical properties and capacitance properties were carried out by E5270B semiconductor analyzer (Agilent Technologies) and 4284A precision LCR meter (Agilent Technologies, Inc.). In addition, the Qfe-Eeff measurements were performed by RT66A (Radiant Technologies, Inc.).

Characterization

The crystal orientations of PZT/ZTO were measured by XRD (PANalytical, X’pert Pro). The cross-sectional image was observed by high-resolution transmission electron microscopic image (JEOL, JEM-2100F).

Additional Information

How to cite this article: Park, J. H. et al. Sub-kT/q Subthreshold-Slope Using Negative Capacitance in Low-Temperature Polycrystalline-Silicon Thin-Film Transistor. Sci. Rep. 6, 24734; doi: 10.1038/srep24734 (2016).

References

A. J. Sneel et al. Application of amorphous silicon field effect transistors in addressable liquid crystal display panels. Appl. Phys. A 24, 357–362, doi: 10.1007/BF00899734 (1981).

K. D. Mackenzie et al. The characteristics and properties of optimized amorphous silicon field effect transistors. Appl. Phys. A 31, 87–92, doi: 10.1007/BF00616310 (1983).

J. M. Powell . The physics of amorphous-silicon thin-film transistor. IEEE Trans. Electron Devices 36, 2753–2763 doi: 10.1109/16.40933 (1989).

M. Shur, M. Hack & J. G. Shaw . A new analytic model for amorphous silicon thin-film transistors, J. Appl. Phys. 66, 3371 (1989).

M. K. Hatalis & D. W. Greve . Large grain polycrystalline silicon by low-temperature annealing of low-pressure chemical vapor deposited amorphous silicon films. J. Appl. Phys. 63, 2260 doi: 10.1063/1.341065 (1988).

S. Uchikoga. Low-temperature polycrystalline silicon thin-film transistor or technologies for system-on-glass displays. MRS Bull. 27, 881–886 doi: 10.1557/mrs2002.277 (2002).

G. Liu & S. J. Fonash . Polycrystalline silicon thin film transistors on corning 7059 glass substrate using short time, low-temperature processing. Appl. Phys. Lett. 62, 2254 doi: 10.1063/1.109294 (1993).

S.-W. Lee & S.-K. Joo . Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization. IEEE Electron Device Lett. 17, 160–162 doi: 10.1109/55.485160 (1996).

T. Serikawa, S. Shirai, A. Okamoto & S. Suyama . Low-temperature fabrication of high-mobility poly-Si TFTs for large-area LCDs. IEEE Trans. Electron Devices 36, 1929–1933 doi: 10.1109/16.34272 (1989).

A. Kumar, A. Nathan & G. E. Jabbour. Does TFT mobility impact pixel size in AMOLED backplanes? IEEE Trans. Electron Devices 52, 2386–2394 doi: 10.1109/TED.2005.857937 (2005).

G. Gu & S. R. Forrest . Design of flat-panel displays based on organic light-emitting devices. IEEE J. Sel. Top. Quantum Electron. 4, 83–99 doi: 10.1109/2944.669473 (1998).

C.-Y. Chen et al. Negative bias temperature instability in low-temperature polycrystalline silicon thin-film transistors. IEEE Trans. Electron Devices 53, 2993–3000 doi: 10.1109/TED.2006.885543 (2006).

C.-Y. Chen et al. A reliability model for low-temperature polycrystalline silicon thin-film transistors. IEEE Electron Device Lett. 28, 392–394 doi: 10.1109/LED.2007.895454 (2007).

M.-W. Ma et al. Characteristics of PBTI and hot carrier stress for LTPS-TFT with high-k gate dielectric. IEEE Electron Device Lett. 29, 171–173 doi: 10.1109/LED.2007.914091 (2008).

T.-M. Pan et al. High-performance poly-silicon TFTs using a high-k PrTiO3 gate dielectric,. IEEE Electron Device Lett. 30, 39–41 doi: 10.1109/LED.2008.2008449 (2008).

L.-C. Yen et al. Electrical and reliability characteristics of polycrystalline silicon thin-film transistors with high-k Eu2O3 gate dielectrics. Appl. Phys. Lett. 100, 173509 doi: 10.1063/1.4705472 (2012).

C.-W. Chang et al. High-performance poly-Si TFTs with Pr2O3 gate dielectric. IEEE Electron Device lett. 29, 96–99 doi: 10.1109/LED.2007.911614 (2008).

W. Y. Choi, B.-G. Park, J. D. Lee & T.-J. K. Liu . Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28, 743–745 doi: 10.1109/LED.2007.901273 (2007).

M. J. Lee & W. Y. Choi . Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electron. 63, 110–114 doi: 10.1016/j.sse.2011.05.008 (2011).

R. Gandhi et al. Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (<50 mV/decade) at room temperature. IEEE Electron Device Lett. 32, 437–439 doi: 10. 1109/LED.2011.2106757 (2011).

M. T. Björk et al. Silicon nanowire tunneling field-effect transistors, Appl. Phys. Lett. 19, 193504–193506 doi: 10.1063/1.2928227 (2008).

V. V. Zhirnov & R. V. Cavin . Nanoelectronics: negative capacitance to the rescue? Nat. Nanotechnol. 7, 77–78 doi: 10.1038/nnano.2008.18 (2008).

G. A. Salvatore et al. Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor. Appl. Phys. Lett. 100, 163504 doi: 10.1063/1.4704179 (2012).

D. J. R. Appleby et al. Experimental observation of negative capacitance in ferroelectrics at room temperature. Nano Lett. 14, 3864–3868 doi: 10.1021/nl5017255 (2014).

C. M. Krowne et al. Examination of the possibility of negative capacitance using ferroelectric materials in solid-state electronic devices. Nano Lett. 11, 988–882 doi: 10.1021/nl1037215 (2011).

D. Jimenez, E. Miranda & A. Godoy . Potential and drain current in negative capacitance field-effect transistors. IEEE Trans. Electron Devices 57, 2405–2409 doi: 10.1109/TED.2010.2062188 (2010).

Y.-H. Chen et al. Low-temperature polycrystalline silicon tunneling thin-film transistor with MILC. IEEE Electron Device Lett. 34, 1017–1019 doi: 10.1109/LED.2013.2266331 (2013).

M.-H. Jaung, P.-S. Hu & S. L. Jang . Formation of polycrystalline-Si thin-film transistors with tunneling field-effect transistor structure. Thin Solid Films 518, 3978–3981 doi: 10.1016/j.tsf.2009.11.017 (2010).

G. Catalan et al. Ferroelectrics: negative capacitance detected. Nat. Mater. 14, 137–139 doi: 10.1038/nmat4195 (2015).

W. Gao et al. Room-temperature negative capacitance in a ferroelectric-dielectric superlattice heterostructure. Nano Lett. 14, 5814–5819 doi: 10.1021/nl502691u (2014).

K. Shimoyama et al. Epitaxial growth of BaTiO3/SrTiO3 structure on SrTiO3 substrate with automatic feeding oxygen from the substrate. J. Appl. Phys. 92, 4625–4630 doi: 10.1063/1.1506196 (2002).

V. Visinoiu et al. Initial growth stages of epitaxial BaTiO3 films on vicinal SrTiO3 (001) substrate surfaces. J. Appl. Phys. 91, 10157–10162 doi: 10.1063/1.1478800 (2002).

B. D. Qu et al. Dielectric properties of BaTiO3/SrTiO3 multilayered thin-films prepared by pulsed laser deposition. Appl. Phys. Lett. 72, 1394 doi: 10.1063/1.121066 (1998).

D. J. Wouters, J.-P. Colinge & H. E. Maes . Subthreshold Slope in Thin-Film SOI MOSFET’s. IEEE Trans. Electron Devices 37, 2022 doi: 10.1109/16.57165 (1990).

N. R. Parikh, J. T. Stephen, M. L. Swanson & E. R. Myers . Study of diffusion barrier for PZT deposited on Si for non-volatile random-access memory technology. MRS Proc. 200, doi: 10.1557/PROC-200-193 (1990).

J.-H. Park et al. Fabrication of metal/ferroelectric/insulator/semiconductor field effect transistor using Mo/Pb(Zr,Ti)O3/ZrTiO4/poly Si thin film structure. Integr. Ferroel. 49, 13–20, doi: 10.1080/10584580290171720 (2002).

H.-T. Lue, C.-J. Wu & T.-Y. Tseng . Device modeling of ferroelectric memory field-effect transistor (FeMFET). IEEE Trans. Electron Devices 49, 1790–1798 doi: 10.1109/TED.2002.803626 (2002).

J. Sun et al. Interface effects on the characteristics of metal-ferroelectric-insulator-semiconductor field-effect transistor. Semi. Sci. Technol. 26, 095027 doi: 10.1088/0268-1242/26/9/095027 (2011).

T. P. Ma & J.-P. Han . Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron Device Lett. 23, 386–388, doi: 10.1109/LED.2002.1015207 (2002).

V. C. Lo . Simulation of thickness effect in thin film ferroelectric films using Landua-Khalatnikov theory. J. Appl. Phys. 94, 3353 doi: 10.1063/1.1598275 (2003).

E.-K. Tan, J. Osman & D. R., Tilley . Theory of switching in bulk first-order ferroelectric materials. Phys. Stat. Solid. B 228, 765–776 doi: 10.1002/1521-3951 (2001).

A. Picinin et al. Theoretical and experimental investigations of polarization switching in ferroelectric materials. Phys. Rev. B 69, 064117 doi: 10.1103/PhysRevB.69.064117 (2004).

K.-H. Chew, L.-H. Ong & M. Iwata . Switching dynamics in ferroelectric superlattices. Curr. Appl. Phys. 11, 755–761 doi: 10.1016/j.cap.2010.11.058 (2011).

A. I. Khan et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 14, 182–186 (2015) doi: 10.1038/nmat4148 (2015).

N. Ershov et al. Negative capacitance effect in semiconductor devices. IEEE Trans. Electron Devices 45, 2196–2206 doi: 10.1109/16.725254 (1998).

G. A. Salvatore, A. Rusu & A. M. Ionescu . Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor. Appl. Phys. Lett. 100, 163504-1–4 doi: 10.1063/1.4704179 (2012).

S. Salahuddin & S. Datta . Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 doi: 10.1021/nl071804g (2008).

A. I. Khan et al. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl. Phys. Lett. 99, 113501-1–3 doi: 10.1063/1.3634072 (2011).

S. Dasgupta et al. IEEE J. Explor. Solid-State Computat. Devices Circuits 1, 43–48 doi: 10.1109/JXCDC.2015.2448414 (2015).

S. Inoue & T. Shimoda . Investigation of relationship between hot carrier degradation and kink effect in low temperature poly-Si TFTs. SID Int. Symp. Dig. Tec. 30, 452–455 doi: 10.1889/1.1834054 (1999).

M.-C. Lee & M.-K. Han . Poly-Si TFTs with asymmetric dual-gate for kink current reduction. IEEE Electron Device Lett. 25, 25–27 doi: 10.1109/LED.2003.821670 (2004).

M.-K. Kang, K. Uh & H. G. Kim . Invited paper: Advanced technologies based on a-Si ore LTPS (low-temperature poly Si) TFT (thin film transistor) for high performance mobile display. SID Int. Symp. Dig. Tec. 38, 1262–1265 doi: 10.1889/1.2785541 (2007).

Y. Oana . Current and future technology of low-temperature poly-Si TFT-LCDs. SID Journal Soc. Inf. 9, 169–172 doi: 10.1889/1.1828784 (2001).

H. Ohshima & M. Führen . Invited paper: High-performance LTPS technologies for advanced mobile display applications. SID Int. Symp. Dig. Tec. 38, 1482–1485 (2007).

M.-W. Ma et al. Reliability mechanism of LTPS-TFT with HfO2 gate dielectric: PBTI, NBTI and hot-carrier stress. IEEE Trans. Electron Devices. 55, 1153–1160 doi: 10.1109/TED.2008.919710 (2008).

C.-Y. Chen et al. Bias temperature instabilities for low-temperature polycrystalline silicon complementary thin-film transistor. J. Electrochem. Soc. 154, H704–H707 doi: 10.1149/1.2742810 (2007).

D. K. Schroder . Negative bias temperature instability: What do we understand? Microelectron. Rel. 47, 841–852 doi: 10.1016/j.microrel.2006.10.006 (2007).

T. Grasser et al. The paradigm shift in understanding the bias temperature instability: from reaction-diffusion to switching oxide traps. IEEE Trans. Electron Devices 58, 3652–3666 doi: 10.1109/TED.2011.2164543 (2011).

R. A. Sporea, T. Burridge & S. R. P. Silva . Self-heating effects in polysilicon source gate transistors. Sci. Rep. 5, 1–11 doi: 10.1038/srep14058 (2015).

S. Inoue, S. Takenaka & T. Shimoda . Study of degradation phenomenon due to a combination of contamination and self-heating in poly-Si thin film transistors fabricated by a low-temperature process, Jpn. J. Appl. Phys. 42, 4213–4217 doi: 10.1143/JJAP.42.4213 (2003).

K. Takechi et al. Dependence of self-heating effects on operation conditions and device structure for polycrystalline silicon TFTs. IEEE Trans. Electron Devices. 53, 251–257 doi: 10.1109/TED.2005.861729 (2006).

C. L. Wang, W. L. Zhong & P. L. Zhang . The curie temperature of ultra-thin ferroelectric films. J. Phys.: Condens. Matter. 3, 4743–4749 (1992).

S. C. Abrahams., S. K. Kurtz & P. B. Jamieson . Atomic displacement relationship to Curie temperature and spontaneous polarization in displacive ferroelectric. Phys. Rev. 172, 551 doi: 10.1103/PhysRev.172.551 (1968).

B. Wang & C. H. Woo . Curie temperature and critical thickness of ferroelectric thin films. J. Appl. Phys. 97, 084109 doi: 10.1063/1.1861517 (2005).

E. H. Nicollian & A. Goetzberger . The Si-SiO2 interface–Electrical properties as determined by the metal-insulator-silicon conductance technique. Bell System Tech. J. 46, 1055–1133 doi: 10.1002/j.1538-7305.1967.tb01727.x (1967).

N. Lustig & J. Nanicki . Gate dielectric and contact effects in hydrogenated amorphous silicon-silicon nitride thin-film transistors. J. Appl. Phys. 65, 3951 doi: 10.1063/1.343361 (1989).

Z. Jin et al. High-performance polycrystalline SiGe thin-film transistors using Al2O3 gate insulators. IEEE Electron Device Lett. 19, 502–504 doi: 10.1109/55.735760 (1998).

T. M. Pan & C.-J. Chang High-performance poly-silicon TFTs with high-k Y2O3 gate dielectrics. Semi. Sci. Technol. 26, 075004 doi: 10.1088/0268-1242/26/7/075004 (2011).

C.-P. Lin et al. High-performance poly-silicon TFTs using HfO2 gate dielectric. IEEE Electron Device Lett. 27, 360–363 doi: 10.1109/LED.2006.872832 (2006).

J. H. Park et al. High-performance poly-Si thin-film transistor with high-k ZrTiO4 gate dielectric. IEEE Electron Device Lett. 36, 920–922 doi: 10.1109/LED.2015.2462745 (2015).

R. Padmanblan, N. Bhat & S. Mohan . High-performance metal-insulator-metal capacitors using europium oxide as dielectric. IEEE Trans. Electron Devices 59, 1364–1370 doi: 10.1109/TED.2012.2188329 (2012).

H.-S. Kim et al. Leakage current and electrical breakdown in metal-organic chemical vapor deposited TiO2 dielectrics on silicon substrate. Appl. Phys. Lett. 69, 3860 doi: 10.1063/1.117129 (1996).

G. W., Dietz et al. Electrode influence on the charge transport through SrTiO3 thin films. J. Appl. Phys. 78, 6113 doi: 10.1063/1.360553 (1995).

S. S. Kim & C. Park . Leakage current behaviors of acceptor- and donor-doped (Ba0.5Sr0.5)TiO3 thin films. Appl. Phys. Lett. 75, 2554 doi: 10.1063/1.125075 (1999).

C. W. Byun et al. High performance poly-Si thin-film transistor fabricated by novel and simple crystallization method using Ni-silicide seeds. J. Electrochem. Soc. 158, J354–J358 doi: 10.1149/2.049111jes (2012).

M. Miyasaka et al. In situ observation of nickel metal-induced lateral crystallization of amorphous silicon thin films. Appl. Phys. Lett. 80, 944 doi: 10.1063/1.1447014 (2002).

Acknowledgements

The authors would like to thank Dr. Yoonsuk Yoon (LFoundary, Germany) for his valuable discussion. This work was supported by Seoul Nation University, Seoul, Republic of Korea, through the Eui-San Research Center and Research Institute of Advanced Materials (RIAM). In addition, this work was partially supported by Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (Grant. 0417-20150112) and in part by BK21PLUS SNU Materials Division for Educating Creative Global Leaders under (Grant F15SN02D1702). The glass substrate (Eagle XG, 100 × 100 mm2) was provided by Corning Precision Materials Co., Ltd. Republic of Korea.

Author information

Authors and Affiliations

Contributions

J.H.P. and S.K.J. conceived and designed the experiments. J.H.P., G.S.J., K.H.S., H.J.C. and S.K.L. performed the fabrication. J.H.P. analyzed the performance and H.Y.K. analyzed the material characteristics. J.H.P. and S.K.J. interpreted the data and provided fruitful discussion all the coauthors.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Supplementary information

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Park, J., Jang, G., Kim, H. et al. Sub-kT/q Subthreshold-Slope Using Negative Capacitance in Low-Temperature Polycrystalline-Silicon Thin-Film Transistor. Sci Rep 6, 24734 (2016). https://doi.org/10.1038/srep24734

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep24734

This article is cited by

-

Impact of Pocket Layer on Linearity and Analog/RF Performance of InAs-GaSb Vertical Tunnel Field-Effect Transistor

Journal of Electronic Materials (2023)

-

Ferroelectric negative capacitance

Nature Reviews Materials (2019)

-

Epitaxial growth of perovskite (111) 0.65PMN-0.35PT films directly on wurtzite GaN (0002) surface

Applied Physics A (2018)

-

Two-dimensional negative capacitance transistor with polyvinylidene fluoride-based ferroelectric polymer gating

npj 2D Materials and Applications (2017)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.