Abstract

Three-dimensional (3D) stackable memory devices including nano-scaled crossbar array are central for the realization of high-density non-volatile memory electronics. However, an essential sneak path issue affecting device performance in crossbar array remains a bottleneck and a grand challenge. Therefore, a suitable bidirectional selector as a two-way switch is required to facilitate a major breakthrough in the 3D crossbar array memory devices. Here, we show the excellent selectivity of all oxide p-/n-type semiconductor-based p-n-p open-based bipolar junction transistors as selectors in crossbar memory array. We report that bidirectional nonlinear characteristics of oxide p-n-p junctions can be highly enhanced by manipulating p-/n-type oxide semiconductor characteristics. We also propose an associated Zener tunneling mechanism that explains the unique features of our p-n-p selector. Our experimental findings are further extended to confirm the profound functionality of oxide p-n-p selectors integrated with several bipolar resistive switching memory elements working as storage nodes.

Similar content being viewed by others

Introduction

As conventional charge-based memories such as dynamic random access memory (DRAM) and NAND flash memory are rapidly approaching physical limitations, development of non-charge mechanism-based non-volatile memories (NVMs) is of great interest for numerous electronic applications1,2,3,4. Among the various NVMs considered recently, a resistive switching random access memory (ReRAM) is a highly reliable candidate to meet the demand of memory markets due to its high-density integration, long-retention time, small size and fast-switching speed4,5,6,7,8,9. In particular, a simple metal-insulator-metal (MIM) frame employed in the ReRAM is expected to facilitate their use in nano-scalable crossbar arrays with ideal memory cell size (4F2) and multilayer stacking frames suitable for three-dimensional (3D) cells10,11,12,13. The crossbar array is typically composed of alternating bit-lines and word-lines perpendicular to each other with memory elements lying between them. However, as all cells in a row and column are connected to each other by the bottom and top electrode, the selected cell suffers from unintended leakage current arising from parasitic paths around neighboring cells. Therefore, the integration of a selector, such as a diode or transistor has been the focus of immense interest at each node, as illustrated in Fig. 1a12,14,15. In a commercial high-density memory system such as DRAM, a Si-based transistor has been used as a selector. However, the widespread use of three-terminal Si transistors is limited by the need for high processing temperature and difficulty in both scaling and stacking16,17. Therefore much effort has been dedicated towards the development of various suitable selectors, such as p-(n-)type Si-based n-p-n latch-up biristor devices, oxide tunneling based varistor-type devices, mixed-ionic-electronic-conduction devices, complementary resistive switching devices, MIM Schottky diodes, as well as metal-insulator transition and threshold switching devices18,19,20,21,22,23,24. However, several key issues still remain in the improvement of output performance, such as current density, cycling endurance and distribution. Therefore, this work focuses on all oxide semiconductor-based p-n-p junctions as a generic approach for highly distinct bidirectional switches, possibly enabling their use in 3D scalable crossbar arrays including in conventional complementary metal-oxide-semiconductor processes. In particular, p-/n-type oxide semiconductors are one of the most likely sources that can be used at low processing temperatures and they allow easy control of lattice mismatch and dopant impurities in p-n hetero-junctions which are the strong plausibility that such a device based on oxide semiconductors might be easy for the formation of the 3D stacable structures with good uniformity performance due to significant controllability margin in thickenss and doping profiles during growth.

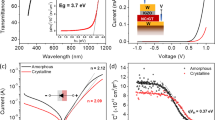

TiN/TaOx resistive switching memory and CoOx/IGZO/CoOx selector device.

(a) Schematic of ideal crossbar array frame using memory and selector devices along with an enlarged view of unit cell. (b) Representative I-V characteristic of the 1S and 1R elements demonstrating the outstanding nonlinearity of over 104 between Vread and Vread/2 (Vread is at 1.6 V) and large memory window of over 102. (c) Typical I-V characteristics of a serially connected selector and memory after completion of electrical connection, where a half voltage method was used. (d) High-resolution EDS (HR-EDS) elemental line profile across a line of the STEM image, where inset indicates a dark-field STEM image of the Pt/CoOx/IGZO/CoOx/Pt frame.

We address the highly distinct electrical features of all oxide semiconductor-based p-CoOx/n-InGaZnOx/p-CoOx open-based bipolar junction transistors for the bidirectional selectors, ensuring outstanding non-linear I-V behavior and promising stability. Systematic electrical analyses of the p-n-p junction selector were conducted by controlling the semiconductor characteristics of each p-(n-) type oxide semiconductor. We further propose a possible explanation of the unique outputs observed in the p-n-p selector based on a Zener tunneling event. Furthermore, we demonstrate the successful operation of a completely series-connected p-n-p selector for the one selector (1S) and bipolar resistive switching memory for the one resistor (1R) acting as a two-terminal 1S1R architecture, contributing to a general framework for advancing 3D crossbar array memory devices.

A detailed discussion of the sample preparation is given in the Methods section. All devices were sputter-deposited on bottom Pt/Ti electrodes on a commercially available SiO2/Si substrate. At first, a CoOx layer serving as p-type oxide semiconductor was sputter-prepared by utilizing a CoO ceramic target in an oxygen and argon gas mixture. Then, an InGaZnOx (IGZO) layer serving as an n-type oxide semiconductor was grown on the above CoOx layer using a sputtering technique. Similarly, a top CoOx layer was also deposited on the IGZO layer under the same growth conditions used for the bottom CoOx layer. Finally, a top Pt electrode was defined using a conventional photolithography and lift-off process for 50 μm × 50 μm cell sizes.

Results

Resistive switching memory and p-n-p selector

Figure 1a shows the ideal schematic crossbar array frame suitable for the most reliable stacking resistive memory elements with proper selectors between the crossbar metal bit and word-line electrodes. Individual I-V responses of typical p-CoOx/n-IGZO/p-CoOx double-hetero-junction selectors (1S) and Pt/TaOx/TiN bipolar resistive switching elements (1R) are shown in Fig. 1b. As seen in this figure, the nonlinearity of the 1S selector is >104 at a half-biased read scheme (Vread = 1.6 V and Vread/2 = 0.8 V). The 1R memory element shows typical bipolar resistive switching behavior representing a larger memory window of 102 at Vread = −0.2 V between a high resistance state (HRS) and low resistance state (LRS). Figure 1c shows the representative I-V curves of the serially connected 1S1R frame, where one electrode of the 1S selector is connected to the bottom TiN electrode of the 1R memory element. A sweeping bias was applied to the top Pt electrode of the 1S selector and was grounded to the top Pt electrode of the 1R memory element. During 1S1R operation, the set and reset voltages of the 1R memory element increased from 1.0 V to 2.3 V and −1.8 V to −3.7 V, respectively, due to the voltage drop across the 1S1R frame. In particular, the write nonlinearity (Kw) of the 1S1R frame is >102 at a half-biased write scheme of Vwrite = 2.3 V and Vwrite/2 = 1.15 V and the memory window of the 1S1R frame is >50 at Vread = −2 V. To determine the distribution of atomic profiles in the 1S selector, a cross-section scanning transmission electron microscopy (STEM) image and high resolution energy dispersive spectroscopy (HR-EDS) elemental line profile were obtained and the results are shown in Fig. 1d. The HR-EDS elemental line profile illustrates clear Co atom distribution at the top and bottom CoOx layers, along with In, Zn and Ga atoms localized at the center of the IGZO layer. Further, a graded atomic composition at the interfaces between the CoOx and IGZO layers of the p-n hetero-junction appears that is attributed to a gradually decreasing Co atom concentration and increasing In, Zn and Ga atoms in the p- and n-oxide regions, respectively. In addition, a cross-sectional HR-EDS elemental mapping identifies noticeable well-grown triple multilayers of a 1S selector, as seen in Supplementary Figure S1. The inset of Fig. 1d provides a dark field STEM image of the 1S selector, confirming the formation of triple oxide layers.

Dependence of p-n-p selector on propertises of n- and p-type oxide semiconductors

To clarify oxide semiconductor-dependent electrical features of a 1S selector, basic features of p-/n-type oxide semiconductors were examined as a function of oxygen content, RF power and film thickness. Physical properties of p-/n-type oxide semiconductors were investigated by using Hall-Effect measurements (Figs 2a and 3a), X-ray diffraction (XRD) analysis (Supplementary Figure S2) and optical transmittance (Supplementary Figure S3). Furthermore, I-V features of each p-/n-type oxide semiconductor and oxide p-n junction were also analyzed in Supplementary Figure S4. Figure 2b,c reveal the resulting I-V features of 1S selectors containing different CoOx layers, where the CoOx layers are deposited under Ar and O2 (at various flow rates) with a fixed IGZO layer. For convenience, the CoOx layer prepared under pure Ar is hereafter designated pure CoOx and the CoOx layers prepared under Ar/O2 flow are referred to as O2-reactive CoOx layers. At first, the 1S selector (dark yellow color) with a pure CoOx layer led to an exponential current increase over seven orders of magnitude for a voltage swing from 0 to ±2 V, providing a low off current (<100 pA) and a low turn-on voltage (~0.3 V). This low turn-on voltage results in a higher current level in the middle voltage region (~1.5 V) and earlier current saturation in the high voltage region (~2 V). This earlier current saturation induces a deteriorated nonlinearity in the 1S selector. The presence of low turn-on voltage and off-current can be described though an insulating characteristic present in a typical MIM selector that will be explained later22. However, the 1S selector containing an O2-reactive CoOx layer reveals a highly nonlinear output with a remarkable difference in the current levels before and after application of a turn-on voltage. One striking feature is that all other selectors containing various O2-reactive CoOx layers show promise in terms of the nonlinearity of the 1S selector. The off-state resistance, turn-on voltage and slope of the double-logarithmic plot after turn-on voltage increase monotonically with increasing O2 flow rates. It is noteworthy that the I-V shape and its nonlinearity are highly affected by the introduction of oxygen gas during CoOx deposition. Therefore, the XRD analysis for the CoOx layer was carried out as a function of Ar and O2 flow rates, as given in Supplementary Figure S2a. In our work, CoO and Co3O4 phases are created in the only Ar and Ar/O2 mixture atmospheres, respectively. As is well-known from previous results reported by other groups, cobalt oxide typically has two stable phases: CoO and Co3O425,26,27. The CoO phase represents a wide optical band gaps of 2.2–2.8 eV with an insulating feature, while the Co3O4 phase corresponds to narrow optical inter-band gaps of 1.4–1.5 eV and 2.18–2.23 eV with a semiconducting feature. Figure 2a shows the carrier concentration, resistivity and optical band gap of CoOx layers prepared at various O2 gas flow rates. Detailed optical band gap results of CoOx layers are given in Supplementary Figure S3. Based on the above XRD analyses, our CoO phase shows insulating properties with a high resistivity of 165 kΩ·cm, a low carrier concentration of 2.8 × 1016 cm−3 and a wide band gap of 2.8 eV, while the Co3O4 phase shows semiconducting behavior with a low resistivity of 52–237 Ω·cm, a high carrier concentration of 6.8 × 1016–1.4 × 1021 cm−3 and a narrow inter band gap of 1.3–1.4 eV. The above findings are consistent with the references for CoO and Co3O425,26,27,28,29. In addition, increasing O2 flow rate reflects enhanced semiconductor characteristics for the CoOx layer including an increased carrier concentration and a decreased optical band gap. Thus, the 1S selector containing a pure CoOx layer is mainly governed by the insulating CoO monoxide phase working as an insulator, not a p-type oxide semiconductor. In contrast, the nonlinear characteristic of the 1S selectors containing an O2-reactive CoOx layer is mainly attributed to the semiconducting Co3O4 sub-oxide phase. It is widely believed that a large carrier concentration in a collector determines the presence of Zener breakdown between the base and collector in a bipolar junction transistor and a small band gap in the p-side of an oxide p-n junction diode causes increased band offset in the reverse bias region30,31,32,33. Thus, the introduction of oxygen during growth in our work positively governs the CoOx semiconducting feature, demonstrating the enhanced nonlinearity of the 1S selector by promoting lower off-current, increased turn-on voltage and exponentially increased turn-on current.

Effects of different p-type oxide semiconductor characteristics on the performance of a CoOx/IGZO/CoOx selector.

(a) Hall carrier concentration, resistivity and optical band gap of CoOx thin films as a function of O2 flow rate. (b) I-V responses of several p-n-p selectors consisting of various CoOx layers at a fixed IGZO layer. (c) Double-logarithmic scale plot taken at positive bias.

I-V characteristics of a CoOx/IGZO/CoOx selector according to various n-type oxide semiconductor characteristics.

(a) Hall carrier concentration, resistivity and optical band gap of IGZO thin films as a function of RF power. The physical features of representative O2 (0.2 sccm) reactive IGZO layer are indicated by filled stars. (b) I-V responses of several p-n-p selectors consisting of various IGZO layers at a fixed CoOx layer. (c) Double-logarithmic scale plot taken at positive bias.

To further access the electrical characteristics of 1S selectors according to various IGZO layers, similar measurements are made by varying RF power and oxygen partial pressure during IGZO growth. All four IGZO layers reveal amorphous phases, as shown in Supplementary Figure S2b. Figure 3a provides the optical band gap and carrier concentration of the IGZO layer as a function of RF power. Decreasing RF power results in decreased optical band gap, electrical conductivity and carrier concentration. These features are well known in the oxide thin film transistor industry34. However, the introduction of oxygen (0.2 sccm O2 flow rate) during IGZO growth increases carrier concentration, resistivity and optical band gap. In general, the resistivity of the n-IGZO layer relies on both mobility and carrier concentration. In our work, the O2-reacitve IGZO layer provides a slightly increased carrier concentration (3 × 1014 → 6 × 1014 cm−3) and a sharp decrease in mobility (0.012 → 0.0034 cm2/V·s, see in Supplementary Figure S5). Thus, the achievement of increased resistivity in an O2-reactive IGZO layer is likely due to a low mobility, resulting in the increased resistivity of a 1S frame suitable for the creation of a low off-current. Figure 3b,c show representative I-V responses of 1S selectors including various IGZO layers. The off-state, on-current and I-V slope after turn-on voltage slightly decrease with decreasing RF power, but the turn-on voltages remain almost unchanged because of a compensation effect between the decreased band gap and carrier concentration on the n-side with increased resistivity. However, when an O2-reactive IGZO layer with an increased carrier concentration, band gap and resistivity is involved in a 1S selector, the 1S selector shows a low off-current and a higher I-V slope after application of a turn-on voltage. We expect that the increase in a carrier concentration of the IGZO layer significantly contributes to the reduction of both the depletion region inside the IGZO and the triangular barrier width in a reversed p-n junction. In addition, an increase in the band gap of IGZO reflects enhanced band offset in the p-n junction. Therefore, both increased height and decreased triangular barrier width in a reversed p-n junction suggest a Zener tunneling event that is directly linked to the enhanced nonlinearity of the 1S selector containing an O2-reactive IGZO layer, as shown in Fig. 3b.

Oxide thickness dependence and switching mechanism

To gain insight into the role of p- or n-type oxide semiconductor thickness on the output of the 1S selector, various n-/p-type oxide thicknesses were also examined, as shown in Fig. 4. The 1S selector is composed of an oxygen reactive (1.0 sccm) CoOx layer and a non-oxygen reactive IGZO layer. Figure 4a show the I-V responses of 1S selectors containing various IGZO thicknesses, suggesting the strong dependence of turn-on voltage and on-currents in the IGZO thickness. However, the 1S selectors with various CoOx thicknesses are not significantly affected, as shown in Fig. 4c. The on/off ratios of 1S selectors with different IGZO and CoOx thicknesses are determined at different read voltages in a half-biased read scheme, as demonstrated in Fig. 4b,d. A decrease in IGZO thickness leads to improved nonlinearity in the 1S selector by allowing a decrease in a maximum read voltage (~1.6 V), as shown in Fig. 4b. However, as seen in Fig. 4d, the highest nonlinearity is achieved for a 10-nm-thick CoOx layer because the nonlinearity of the 1S selector containing a relatively thin CoOx of about 5 nm is saturated at a low read voltage (~1.4 V) and decreases rapidly thereafter. In general, the conductivity in a 1S selector relies on the total resistance of device after turn-on. In our work, a thick CoOx layer provides an increased resistance of 1S, reflecting a slight decrease in on-current without affecting turn-on voltage. In addition, because a higher carrier concentration in a CoOx layer (rather than an IGZO layer) corresponds to a depletion region inside the IGZO layer, most energy band bending and Zener tunneling may occur in the depletion region of the IGZO layer. Consequently, the thickness of the n-type IGZO layer is likely responsible for the resulting electrical key factors, such as turn-on voltage and on current, as confirmed in Fig. 4a.

Oxide semiconductor thickness dependence of a CoOx/IGZO/CoOx selector.

(a) I-V responses of p-n-p selectors containing 5-, 7-, 9- and 11-nm-thick IGZO layer with a 5-nm-thick CoOx p-type oxide semiconductor. (b) On/off ratios of each selector recorded at Vread and Vread/2. (c) I-V features of 5, 10, 15 thick CoOx with a 5-nm-thick IGZO n-type oxide semiconductor. (d) On/off ratio of each selector taken at Vread and Vread/2.

To further identify whether the proposed Zener tunneling is responsible for electrical observations in this work, temperature measurements on our p-n-p selectors were also conducted and the results is shown in Fig. 5a,b. It is well-known that typical junction breakdown events are caused by either Zener tunneling or avalanche multiplication, in which the Zener tunneling breakdown voltage has a negative temperature coefficient whereas the avalanche has a positive temperature coefficient. A gradual decrease in turn-on voltage of p-n-p selector with increasing temperatures was observed, as shown in Fig. 5b. It clearly reflects the occurrence of Zener tunneling event. The inset in Fig. 5a was the I-V plot of 1S frame in a semi-log scale. Based on the above observations and low temperature measurement, we propose a possible model to explain the electrical behavior of bidirectional 1S selectors by means of a reverse breakdown event, as illustrated in Fig. 5c,d. At first, we hypothesize that the bidirectional nonlinear behavior in the p-n-p selector is analogous to the Zener tunneling presented in an open-base n-p-n double hetero-junction bipolar transistors30,31. Figure 5c shows the equilibrium band diagram, suggesting suppressed current flow at zero and low bias voltage since the reversed bias p-n junction exists inherently in a p-n-p selector, regardless of the applied positive or negative bias to the top (or bottom) CoOx layer. In our model for a p-n hetero-junction, the role of any potential well is neglected due to the formation of a graded composition at the IGZO/CoOx interface, as shown in Fig. 1d. However, when a specific voltage is applied to the top (or bottom) CoOx layer, the staggered band lines up between the p-type CoOx valence band edge and n-type IGZO conduction band edge, giving rise to the presence of a narrow effective gap at the reversed p-n junction. Therefore, Zener tunneling is likely to occur at a narrow effective gap, as seen in Fig. 5d. Moreover, since the depletion region is primarily created towards the n-type IGZO side, the turn-on voltage is largely governed by the IGZO thickness. The above findings are correlated with the findings in Fig. 4. If an n-type IGZO layer is thinner than the depletion region, Zener tunneling can appear even at a relatively low bias voltage. Thus, the 1S selector acts as a constant resistor with a higher off-current and a low turn-on voltage. Additional thickness dependence measurements confirmed a linear I-V behavior of a 1S frame with a 2-nm-thick IGZO layer, as plotted in Supplementary Figure S6.

Temperature-dependent I-V features and schematic diagram for a CoOx/IGZO/CoOx selector.

The p-n junctions were described, based on graded composition of hetero-junctions: (a) I-V features recorded from 12 K to 280 K and (b) temperature dependence of turn-on voltage. (c) Schematic diagram in equilibrium and (d) high bias conditions including depletion region width, band diagram and electron flow. The insets in (a) show semi-log temperature dependence I-V curve of CoOx/IGZO/CoOx selector.

Performance of 1S1R integration

To highlight the suitability of the 1S selector developed in this work, the electrical features of 1S1R frames integrated with various 1R memory elements are systematically examined, where the optimized 1S selector consists of O2-reactive 10-nm-thick p-CoOx (1.0 sccm) and 5-nm-thick n-IGZO (0.2 sccm) layers. Figure 6a,b reveal typical I-V responses and a dc endurance test of only the 1S selector, where the endurance test is conducted at a half-bias read voltage scheme (Vread = 1.6 V and −2 V, Vread/2 = 0.8 V and −1 V). The selectors exhibit promising stability at Vread and Vread/2 during 104 consecutive DC sweeps. Figure 6c,d show the representative I-V switching response and pulse endurance results of the 1S1R frame. In a dc bias sweep, the set and reset voltages of 1S1R frame are 2.4 and −3.8 V, respectively, as seen in Fig. 6c. A voltage pulse diagram for the endurance test is shown in Supplementary Figure S7, where the amplitudes of set and reset voltages are 3 and −5.6 V, respectively. The nonlinearity factor (α) in Fig. 6c is defined as the ratio of LRS resistances measured at Vread and Vread/2, demonstrating a value of more than 103, which is comparable to other nonlinear selectors19,22,35. To further estimate the possible array sizes for our 1S1R frames, a normalized read voltage margin (ΔVout/Vpu) is calculated by using a number of word lines, as seen in Fig. 6e. The cell condition assumes the worst read scheme, called a one bit-line pull up scheme36,37,38. For only a 1R memory element, the measurable normalized read voltage margin ΔVout/Vpu rapidly decreases to 10% for the N = 5 array size (N-word line and N-bit line). However, the calculated maximum array size of a 10% read voltage margin is extended to N = 5067 for the 1S1R frame, meaning an array size of more than 10 Mbit is possible. In addition, the endurance tests of 1R and 1S1R frames demonstrate a negligible degradation in the memory window during successive operation of 104 pulses. However, even though a highly uniform dc endurance feature is obtained for a 1S frame, a detectable fluctuation is observed in a pulse endurance test of a 1S1R frame. This is mainly due to the disturbed endurance fluctuations of 1R memory elements, as shown in the inset of Fig. 6d. Therefore, 1S1R device characteristics strongly rely on the electrical features of the 1R memory element, such as distribution of endurance, retention and memory window since the 1S frame is highly stable. In addition, multi-level switching behavior arising from both 1R memory elements is similarly confirmed in 1S1R frames, as seen in Supplementary Figure S8. In particular, to validate the possible use of our 1S selector as a bidirectional switch, the I-V responses of 1S selectors integrated with various memory elements are observed, as seen in Supplementary Figure S9. All devices exhibit good nonlinearities, as expected. As given in Supplementary Figure S9d, the conducting bridge memory (CBM) elements provide a large 1S1R memory window of more than 103, along with the relatively unstable features caused by larger fluctuations frequently present in the CBM 1R memory element. In addition, the 170 nm nano-scaled p-n-p selectors in this work were examined, resulting in the current density of 0.1 MA/cm2 (Supplementary Figure S10). Thus, we expect that there is still a lot of space to be improved after optimization process as a two-way switch for NVMs. Furthermore, we have developed the p-n-p oxide selector by using a semiconductor industry-friendly TiN electrode. However, since the TiN electrode with a reactive characteristic is highly susceptible to reaction with bottom or top CoOx layers, resulting in the degraded electrical performance, a tin-doped indum oxide (ITO) layer was inserted between TiN and bottom CoOx to block the possible reaction of oxide materials with reactive electrode (Supplementary Figure S12).

Characteristics of 1S1R frame.

(a) Typical I-V characteristics of a CoOx/IGZO/CoOx selector and (b) endurance test under 104 consecutive DC sweeps. (c) Typical I-V characteristics of Pt/CoOx/IGZO/CoOx/Pt (1S) integrated with Pt/TaOx/TiN (1R) after completion of electrical connection. (d) Endurance test measured by a 100-ns pulse width signal. (e) Dependence of normalized read margin (ΔVout/Vpu) on the crossbar line number (N) for 1R (red color) and 1S1R (Black color) devices. The insets of (c,d) show I-V curve and endurance characteristics of only 1R.’

In summary, we described the outstanding performance of 1S selectors involving all oxide semiconductor materials as a promising alternative to solve sneak-path issues possibly present in 3D stackable nano-scaled crossbar memory array configurations. We examined the p-/n-type oxide semiconductor material-dependent nonlinearity of a 1S selector, along with a physical model to explain the nonlinear I-V features observed. In particular, the 1S1R frame integrated with various 1R memory elements confirms the possible suppression of the leakage current when compared to that of the 1R memory element, ensuring stable switching endurance up to 104 cycles with a 100-ns pulse width. We anticipate that this approach will become a simple and useful route that offers the possible realization of future 3D stackable crossbar array memory devices.

Methods

Measurement

DC electrical measurement was performed by using a Keithley 4200 semiconductor parameter analyzer (Keithley 4200 SPA, Keithley Instruments, Inc.). Temperature dependent characteristics were recorded using a Helix CTI-Cryogenic 8200 compressor (Helix Technology Corporation) and a Neocera LTC-11 temperature controller under vacuum. Pulse analyses for cycling endurance were carried out with an Agilent 81110A pulse generator (Agilent Technologies, Inc.). Hall Effect measurement was conducted at room temperature by utilizing a standard set-up using the Van der Pauw method with a Lakeshore 662 electromagnet power supply and a Keithley 4200 SPA. The crystalline features of oxide layers were characterized by using an X-ray diffraction system (XRD, Rigaku D/MAX-2500/PC, by Cu Kα radiation). Optical absorption was recorded using a UV-visible spectrometer (Lambda 35: PerkinElmer). Cross-sectional nanostructured observation and atomic distribution analyses of a selector were conducted by using a HR-STEM (JEOL JEM 2100F) with the corresponding EDS mappings. For HR-STEM measurements, across cutting sample was prepared on a copper grid using a focused ion beam (FIB).

Fabrication

Various Pt/TaOx/TiN, Ta/TaOx/Pt and Cu/TaOx/Pt bipolar resistive switching memory device and Pt/CoOx/IGZO/CoOx/Pt bidirectional selector device were fabricated on commercially available SiO2/Si substrates. A 30-nm-thick Ti layer under the Pt bottom electrode was prepared as a buffer layer on the SiO2 by using a sputtering system. The bottom TiN electrode was formed by reactive sputtering of a Ti metal target in a mixture of Ar and N2. All oxide layers were grown by using RF magnetron sputtering with ceramic targets. A 20-nm-thick TaOx oxide layer was chosen as the main active medium suitable for memory elements and then various 50-nm-thick top electrodes (Pt, Ta and Cu) were formed by sputtering of metal targets with a 50 μm × 50 μm cell size defined by photolithography and a lift-off process. Furthermore, a 170 nm-size p-n-p selector were prepared on the TiN nano-pluged wafer (Supplementary Figure S11).

Additional Information

How to cite this article: Bae, Y. C. et al. All oxide semiconductor-based bidirectional vertical p-n-p selectors for 3D stackable crossbar-array electronics. Sci. Rep. 5, 13362; doi: 10.1038/srep13362 (2015).

References

Hamann, H. F., O’Boyle, M., Martin, Y. C., Rooks, M. & Wickramasinghe, H. K. Ultra-high-density phase-change storage and memory. Nat. Mater. 5, 383–387 (2006).

Ikeda, S. et al. A perpendicular-anisotropy CoFeB–MgO magnetic tunnel junction. Nat. Mater. 9, 721–724 (2010).

Ouyang, J., Chu, C. W., Szmanda, C. R., Ma, L. & Yang, Y. Programmable polymer thin film and non-volatile memory device. Nat. Mater. 3, 918–922 (2004).

Lee, M. J. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x/TaO2-x bilayer structures. Nat. Mater. 10, 625–630 (2011).

Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-based resistive switching memories–nanoionic mechanisms, prospects and challenges. Adv. Mater. 21, 2632–2663 (2009).

Borghetti, J. et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Sawa, A. Resistive switching in transition metal oxides. Mater. Today 11, 28–36 (2008).

Yang, J. J., Borghetti, J., Murphy, D., Stewart, D. R. & Williams, R. S. A family of electronically reconfigurable nanodevices. Adv. Mater. 21, 3754–3758 (2009).

Lee, M.-J. et al. Electrical manipulation of nanofilaments in transition-metal oxides for resistance-based memory. Nano. Lett. 9, 1476–1481 (2009).

Yu, L.-E. et al. Structure effects on resistive switching of Al/TiOx/Al devices for RRAM applications. IEEE Elec. Dev. Lett. 29, 331–333 (2008).

Xia, Q. et al. Two- and three-terminal resistive switches: Nanometer-scale memristors and memistors. Adv. Func. Mater. 21, 2660–2665 (2011).

Lee, M.-J. et al. 2-stack 1D-1R cross-point structure with oxide diodes as switch elements for high density resistance RAM application. IEEE Int. Elec. Dev. Meet. Tech. Dig. 771–774 (2007).

Yu, S., Chen, H.-Y., Gao, B., Kang, J. & Wong, H.-S. P. HfOx-based vertical resistive switching random access memory suitable for bit-cost-effective three dimensional cross-point architecture. ACS Nano 3, 2320–2325 (2013).

Liang, J. L. & Wong, H.-S. P. Cross-point memory array without cell selectors-device characteristics and data storage pattern dependencies. IEEE Trans. Elec. Dev. 57, 2531–2538 (2010).

Lee, M.-J. et al. Low-temperature-grown transition metal oxide based storage materials and oxide transistors for high density non-volatile memory. Adv. Func. Mater. 19, 1587–1593 (2009).

Lee, M.-J. et al. A low-temperature-grown oxide diode as a new switch element for high-density, nonvolatile memories. Adv. Mater. 19, 73–76 (2007).

Linn, E., Rosezin, R., Kugeler, C. & Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 9, 403–406 (2010).

Kim, S. et al. Latch-up based bidirectional npn selector for bipolar resistance-change memory. Appl. Phys. Lett. 103, 033505 (2013).

Lee, W. et al. High current density and nonlinearity combination of selection device based on TaOx/TiO2/TaOx structure for one selector-one resistor arrays. ACS Nano 6, 8166–8172 (2012).

Virwani, K. et al. Sub-30nm scaling and high-speed operation of fully-confined access-devices for 3D crosspoint memory based on mixed-ionic-electronic-conduction (MIEC) materials. IEEE Int. Electron Dev. Meet. Tech. Dig. 36–39 (2012).

Bae, Y. C. et al. Oxygen ion drift-induced complementary resistive switching in homo TiOx/TiOy/TiOx and hetero TiOx/TiON/TiOx triple multilayer frameworks. Adv. Func. Mater. 22, 709–716 (2012).

Huang, J. J., Tseng, Y.-M., Hsu, C.-W. & Hou, T.-H. Bipolar nonlinear Ni/TiO2/Ni selector for 1S1R crossbar array applications. IEEE Elec. Dev. Lett. 32, 1427–1429 (2011).

Son, M. et al. Self-selective characteristics of nanoscale VOx devices for high-density ReRAM applications. IEEE Elec. Dev. Lett. 33, 718–720 (2012).

Lee, M.-J. et al. A plasma-treated chalcogenide switch device for stackable scalable 3D nanoscale memory. Nat. Commun. 4, 2629 (2013).

Li, W.-Y., Xu, L.-N. & Chen, J. Co3O4 nanomaterials in lithium-ion batteries and gas sensors. Adv. Func. Mater. 15, 851–857 (2005).

Barreca, D. et al. Composition and microstructure of cobalt oxide thin films obtained from a novel cobalt (II) precursor by chemical vapor deposition. Chem. Mater. 13, 588–593 (2001).

Garcia, H. A., Melo, R. P. Azevedo, A. & Araújo, C. B. Optical and structural characterization of iron oxide and cobalt oxide thin films at 800 nm. Appl. Phys. B 111, 313–321 (2013).

Patil, P. S., Kadam, L. D. & Lokhande, C. D. Preparation and characterization of spray pyrolysed cobalt oxide thin films. Thin Solid Films 272, 29–32 (1996).

Kim, H.-K., Seong, T.-Y., Lim, J.-H., Cho, W. I. & Yoon, Y. S. Electrochemical and structural properties of radio frequency sputtered cobalt oxide electrodes for thin-film supercapacitors. J. Power Sources 102, 167–171 (2001).

Bolognesi, C. R., Watkins, S. P. & Moll, N. Breakdown voltage limitations, impact ionization and interband tunneling in InP/GaAsSb/InP type-II NpN DHBTs. IEEE Int. Elec. Dev. Meet. Tech. Dig. 30.3.1–30.3.4 (2003).

Milovanovic, V., van der Toorn, R., Humphries, P., Vidal, D. P. & Vafanejad, A. Compact model of Zener tunneling current in bipolar transistors featuring a smooth transition to zero forward bias current. IEEE Bipolar/BiCMOS Circ. Tech. Meet. 99–102 (2009).

Kamiya, T. et al. Electrical properties and structure of p-type amorphous oxide semiconductor xZnO∙Rh2O3 . Adv. Func. Mater. 15, 968–974 (2005).

Kang, B. S. et al. High-current-density CuOx/InZnOx thin-film diode for cross-point memory applications. Adv. Mater. 20, 3066–3069 (2008).

Li, Y., Hu, X., Liu, Z. & Ren, J. Power and gas pressure effect on properties of amorphous In-Ga-ZnO films by magnetron sputtering. Jour. Mater. Sci.-Mater. in Elec. 23, 408–412 (2012).

Li,Y., Gong, Q., Li, R. & Jiang, X. A new bipolar RRAM selector based on anti-parallel connected diodes for crossbar applications. Nanotechnology 25, 185201 (2014).

Flocke, A. & Noll, T. G. Fundamental analysis of resistive nano-crossbars for the use in hybrid Nano/CMOS memory. Solid State Circuits Conference, 2007. ESSCIRC 2007. 33rd European. Munich. IEEE. (10.1109/ESSCIRC.2007.4430310) 328–331 (2007, Sept. 11–13).

Liu, Z.-J., Gan, J.-Y. & Yew, T.-R. ZnO-based one diode-one resistor device structure for crossbar memory applications. Appl. Phys. Lett. 100, 153503 (2012).

Lo, C.-L., Hou, T.-H., Chen, M.-C. & Huang, J.-J. Dependence of read margin on pull-up schemes in high-density on selector-one resistor crossbar array. IEEE Tran. Elec. Dev. 60, 420–426 (2013).

Acknowledgements

This work was partially supported by the IT R&D program of MKE/KEIT [KI10039191, Development of Fundamental Technologies for Tera Bit Level 3D ReRAM] and in part supported by a grant from the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2013R1A1A2060350).

Author information

Authors and Affiliations

Contributions

Y.C.B. and J.P.H. designed this work and prepared the manuscript. The experiment and electrical measurements were carried out by Y.C.B., A.R.L., G.H.B. and T.Y.K. All authors discussed the results and implications and commented on the manuscript at all stages.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Bae, Y., Lee, A., Baek, G. et al. All oxide semiconductor-based bidirectional vertical p-n-p selectors for 3D stackable crossbar-array electronics. Sci Rep 5, 13362 (2015). https://doi.org/10.1038/srep13362

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep13362

This article is cited by

-

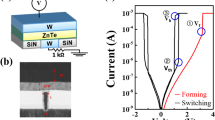

Bidirectional-nonlinear threshold switching behaviors and thermally robust stability of ZnTe selectors by nitrogen annealing

Scientific Reports (2020)

-

Bidirectional Selector Utilizing Hybrid Diodes for PCRAM Applications

Scientific Reports (2019)

-

Resistive random access memory (RRAM) technology: From material, device, selector, 3D integration to bottom-up fabrication

Journal of Electroceramics (2017)

-

Memory window engineering of Ta2O5−x oxide-based resistive switches via incorporation of various insulating frames

Scientific Reports (2016)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.