Abstract

Neuromorphic computing is a promising strategy to overcome fundamental limitations, such as enormous power consumption, by massive parallel data processing, similar to the brain. Here we demonstrate a proof-of-principle implementation of the weighted spin torque nano-oscillator (WSTNO) as a programmable building block for the next-generation neuromorphic computing systems (NCS). The WSTNO is a spintronic circuit composed of two spintronic devices made of magnetic tunnel junctions (MTJs): non-volatile magnetic memories acting as synapses and non-linear spin torque nano-oscillator (STNO) acting as a neuron. The non-linear output based on the weighted sum of the inputs is demonstrated using three MTJs. The STNO shows an output power above 3 µW and frequencies of 240 MHz. Both MTJ types are fabricated from a multifunctional MTJ stack in a single fabrication process, which reduces the footprint, is compatible with monolithic integration on top of CMOS technology and paves ways to fabricate more complex neuromorphic computing systems.

Similar content being viewed by others

Introduction

Von-Neumann based computing is predicted to reach an inevitable limit within 10 years due to fundamental limitations, such as enormous power consumption1. A promising strategy to overcome these barriers is massive parallel data processing, similar to the brain. These NCSs use many parallel processors (neurons) communicating using simple messages (spikes) or continuous interactions (oscillations) mediated by programmable memory units (synapses). The individual input signals are weighted in the synapses and mapped non-linearly into an output signal in the neuron. The close proximity of the processing and memory units and the non-volatile memory are characteristic for this architecture.

NCSs built in conventional CMOS improved in terms of energy efficiency and footprint, but are still far from the energy efficiency and footprint of the brain2,3,4. New hardware implementations of ultra-low energy and non-volatile artificial neurons could fill the performance gap, for example synapses and neurons have been implemented by memristors5,6, photonics7,8, spin Hall oscillators9, and MTJs10,11,12,13,14,15,16,17,18,19,20,21,22,23.

Spin-based computing is the most promising of the mentioned technologies with a small footprint and low power consumption due to the low intrinsic energy needed to manipulate nanomagnets2,24,25,26,27 and non-volatile information storage28. As demonstrated by the commercialization of MRAM technology, MTJ integrated on CMOS have shown to be scalable and robust25. The challenge for application in neuromorphic computing is to integrate the required functionality in a single scalable, energy- and space-efficient system. NCSs consist of multiple layers with each incorporating large numbers of neurons, which are all interconnected by many more synapses. Due to this complexity a reliable monolithic integration between spintronic components and CMOS is fundamental. Implementing synapses and neurons in a single CMOS-compatible process enables the monolithic integration on CMOS and improves the energy efficiency and density of the whole NCS due to a reduction of the footprint and the parasitic losses due to spatial separation.

Different types of devices can be used to implement synapses and neurons29,30. More specifically, neurons have been implemented using a wide range of MTJ micropillars and nanopillars: Using MTJs nanopillars with footprints as low as 0.008 µm2 as rectifiers requires modest RF inputs of 32 µW and results in small DC outputs of 0.2 nW22. By biasing the MTJ nanopillar with an additional DC current, the total input RF and DC input power value can be reduced below 10 µW23. Linearly magnetized spin-torque nano-oscillator (STNO) have an equally small footprint, but require 138 µW in input power and generate RF output powers of 5 nW11. While STNOs with a vortex magnetization state have larger output powers of a few microwatts and require input powers of a few milliwatts20,31. The synchronization of the multiple vortex STNOs can be used as activation of a neuron10,21. Thus, depending on the frequency and power requirements different solutions are preferable.

Here, we propose a spintronic circuit which we call weighted spin torque nano-oscillator (WSTNO) that consists of a resistive network interconnecting multiple MTJ devices with different functional characteristics determined by the MTJ geometry and made out of a single multifunctional MTJ stack. It combines non-volatile magnetic memories (MRAMs) acting as artificial synapses, and non-linear STNO with distinct threshold behavior acting as neurons. The resulting WSTNO is a building block with the required functional features required to implement a NCSs. A distinct feature of the WSTNO presented here compared to previously reported NCSs based on MTJs15,17,19,20 is the implementation of the non-volatility of the weights.

In literature one multifunctional MTJ stack (memory, oscillators, magnetic field sensor) is reported, which is optimized for memory applications (out-of-plane magnetization, thin free layer, low switching energy)32. In contrast, we prioritized the oscillator performance over the memory performance, in order to optimize the performance of the inference phase of neuromorphic applications. In this phase, the weights are written once for each neuromorphic application and the writing is not a fundamental part of the energy efficiency of the system computed over its life-time. We start from a vortex STNO stack31,33,34 (in-plane magnetization, thick free layer), due to the high signal-to-noise ratio, good reproducibility, low magnetic field requirements, large output power and low device to device variation compared to the alternatives, such as linear STNOs11,35,36 or spin Hall nano-oscillators37,38. We emphasize that optimized vortex STNOs are capable of exhibiting RF output powers in the range of 1-10 µW (−30 to −20 dBm) which is above the 1 µW threshold often cited as a minimum for integration of such devices with CMOS circuitry without major amplification requirements39. The magnetic behavior of the free layer is determined by the lateral dimensions of the nanopillars40,41. In nanopillars with a diameter above 300 nm the magnetization of the free layer forms a magnetic vortex state, which can be dynamically excited via spin transfer torque (STT) associated with the tunneling current generating an RF electrical signal of 200 to 400 MHz. Elliptical nanopillars with dimensions around 125 nm will have a uniformly in-plane magnetized free layer with additional shape anisotropy contribution that reinforces a bi-stable magnetization configuration appropriate for memory applications. Although the free layer thickness is optimized for vortex oscillators excited by spin transfer torques, the memory device can be easily switched by local magnetic fields generated by electric current lines.

The material stack of the devices used in this work is 5 Ta / 50 CuN / 5 Ta / 50 CuN / 5 Ta / 5 Ru / 6 Ir0.2Mn0.8 / 2.0 CoFe0.3 / 0.7 Ru / 2.6 Co0.4Fe0.4B0.2 / MgO wedge / 2.0 Co0.4Fe0.4B0.2 / 0.2 Ta / 7 NiFe / 10 Ta / 7 Ru (thicknesses in nm). The deposited MgO thickness was varied in a wedge across the wafer resulting in resistance area product (RxA) values between 3 and 20 Ωµm2 along the wafer. The results reported in this paper concern devices with RxA around 9 Ωµm2, which is typically the sweet spot in terms of maximizing oscillation power35. The nanodevices above this MgO thickness typically show tunnel magnetoresistance (TMR) values between 70 and 200%35,42. The MTJs presented in this work had a TMR of 60–70%.

For a matter of clarity, we demonstrate the concept of the WSTNO in a minimalistic network consisting only of two non-volatile MRAMs and one STNO. Each input is an analog voltage source that is weighted by the resistance state of the memory, which is either in the anti-parallel (AP) high resistance state or the parallel (P) low resistance state. The resulting input currents jointly excite the STNO into oscillation. In such a minimalistic system, only four possible configurations can be encoded in artificial synapses. A scaled up version of this minimalistic WTSNO with 10 MTJs in each synaptic input channel is presented in the Supplementary Note 1.

In conclusion, we present the concept and proof-of-principle of a WSTNO system, which combines different spintronic devices to create a basic programmable computing unit. On this basis, the experimental implementation of an artificial neuron is presented as a network of two MRAMs (synapses) and one STNO (neuron) nanofabricated from the same MTJ stack and only varying in lateral dimension. This allows the fabrication of dense MTJ nanopillar networks and is an advantage compared to artificial neurons consisting of different technologies for neurons and synapses. While the homogeneous integration of devices exploring different physical mechanisms and classes of materials is possible, in general, it requires compromises that are dictated by the compatibility of different materials and process flows that impact the density of integration. That is not the case here. The STNO output power was above 3 µW and frequency around 245 MHz in nanopillars of 300 nm diameter. Due to this high output power and low oscillation frequency, monolithic integration with CMOS technology is less challenging. The required footprint is about 0.017 µm2 per MRAM and 0.09 µm2 per STNO, which is very small compared to CMOS based artificial neurons that can have a footprint of 8 µm², but are usually far above this value4,43. Based on this proof-of-principle of a WSTNO system our long-term vision is to develop a unique platform for next-generation complex NCSs with improved performance compared to existing CMOS computing systems, filling the gap between the capability of current computers and the brain.

Results

The STNO characterization

The MTJ stack that is used in this work is optimized for consistent oscillations with output powers above 3 µW in an in-plane magnetic field of just ±20 Oe. This type of STNOs show a characteristic vortex magnetization state in the free layer. A DC bias current \({I}_{{{{{{\rm{STNO}}}}}}}\) is spin-polarized in the pinned layer and injected into the free layer of the STNO where it interacts through the STT effect, but also through the generated Oersted field and temperature. Above a critical current threshold, the magnetic vortex is excited into auto oscillation were the vortex core performs a gyrotropic motion. The gyration of the vortex core is sustained under the condition that the spin-transfer force is counterbalancing the damping. The micromagnetic behavior of vortex oscillators is well understood qualitatively as described elsewhere31,33,34. This circular orbit in reference to the in-plane magnetized reference layer creates a resistance oscillation due to the TMR effect of the MTJ. Thus, the magnetic state can be probed by measuring the electrical resistance as a function of the external magnetic field, as shown in Fig. 1a. The resulting AC oscillation power is measured using a spectrum analyzer, as shown in Fig. 1b31. A Lorenz fit of the observed oscillation peak is used to determine the integrated power (\({P}_{{{{{{\rm{STNO}}}}}}}\)) and the oscillation frequency shown in Fig. 1c, d. The \({P}_{{{{{{\rm{STNO}}}}}}}\) shows a distinct non-linear threshold behavior as a function of \({I}_{{{{{{\rm{STNO}}}}}}}\). The threshold is called critical current and is the point at which the damping is compensated by the STT effect44. However, the influence of grains can result in deviation from the theory31,33,45. The STNOs used in this work have a critical current of around 4 mA with an almost linear \({P}_{{{{{{\rm{STNO}}}}}}}\) increase above that value up to 3 µW for \({I}_{{{{{{\rm{STNO}}}}}}}=6{{{{{\rm{mA}}}}}}\) and an oscillation frequency around 240 MHz. Typically, the oscillation frequency is increasing as a function of the bias current until it approaches a maximum in these type of oscillators33. This particular STNO shows an almost constant frequency response, but most likely because the oscillation only occurred close to the maximum frequency were the frequency increase is small. The typical behavior measured on a set of seven STNOs of 300 nm diameter at a bias of 5 mA showed a frequency of 245 ± 11 MHz, a power of 1.68 ± 0.80 µW and a linewidth of 0.7 ± 0.5 MHz. These variations are not are not excessively high and should not affect the overall system performance.

a Resistance of the STNO \(({R}_{{{{{{\rm{STNO}}}}}}})\) as a function of an in-plane magnetic field at two bias currents. The arrow indicates the magnetic field conditions and the magnetic vortex state in which the auto oscillations are observed. b Power spectral density (PSD) of a 300 nm vortex STNO at an in-plane magnetic field of −19 Oe. c, d Integrated oscillation power \(({P}_{{{{{{\rm{STNO}}}}}}})\) and resonance frequency obtained from a Lorenz fit of the PSD as a function of the bias current. The sweep was repeated in both directions as indicated by the arrows and shows no hysteretic behavior with the bias current. The insert in d shows the electric circuit of the measurement setup including the spectrum analyzer (SA).

The maximum \({P}_{{{{{{\rm{STNO}}}}}}}\) is about 4 µW before the breakdown of the MgO layer. During the measurement, an external magnetic field of −19 Oe is applied in an in-plane direction with no out-of-plane components in order to obtain oscillations, which is excellent for application as this field strength can be easily obtained by local magnetic fields.

MRAM characterization

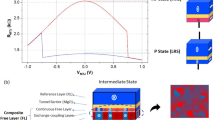

The challenge in fabricating the MRAMs is to obtain a bi-stable resistance state in an MTJ stack that was optimized to have a vortex ground state. This is achieved by introducing shape anisotropy through an elliptical shaped footprint. The MRAMs have a mostly square-like hysteresis loop with defined P and AP resistance states at zero field and two different coercive fields, as shown in Fig. 2a. In the presented samples, this coercive field difference is due to device-to-device variations, but it can be designed by the aspect ratio variation of the elliptical shaped footprint. The difference in the coercive field allows programming the MRAMs into all of the various resistance state combinations (P-P, P-AP, AP-P, and AP-AP) using minor loops of an externally applied magnetic field. To increase the energy efficiency, the individual MRAMs can be programmed through short pulses in independent magnetic field lines 1.0 µm above the devices, which generates a magnetic field of about 0.67 \({{{{{\rm{kOe}}}}}}{{{{{{\rm{A}}}}}}}^{-1}\) (in field lines with a 3 µm width). To study the required energy to program the 100 nm x 200 nm MRAM nanopillar we applied one hundred 1 ns, 2 ns, and 3 ns switching pulse and evaluated the switching probability for each pulse length as a function of the pulse amplitude. A switching probability of 100% is obtained for 1 ns pulses above an amplitude of 350 mV, as shown in Fig. 2b, which corresponds to an energy of 30 pJ. This value is within the typical range of energies cited for comparable field switching MRAM cells, and reasonable considering that this MTJ stack was not optimized for switching efficiency46,47. The average P and AP resistance of 56 elliptical MRAM devices (75 nm × 225 nm) across the 200 mm wafer was 740 ± 277 Ω and 1445 ± 356 Ω, respectively. These variations can be reduced with optimization of the fabrication process as demonstrated for example for STT-MRAM devices48.

a Resistance versus magnetic field transfer curves of elliptical MRAMs (75 nm x 225 nm). The magnetic field (H) was kept at −22 Oe to compensate for the magnetic field offset during the weighted spin torque nano-oscillators characterization. These curves were obtained at a bias current of 10 µA. b Switching probability overview of an elliptical MRAM (100 nm x 200 nm) from parallel to anti-parallel state as a function of the pulse voltage and magnetic field amplitude applied to the field line (VFL and HFL). Each point is the result of 100 switching attempts with a single pulse of a few nanosecond length. A single 30 pJ pulse of 1 ns length is able to switch the MRAM from parallel (P) to anti-parallel (AP) state with a probability of 100%.

WSTNO characterization

The proof-of-principle implementation of the WSTNO with two MRAMs and one STNO, as shown in Fig. 3a. For the WSTNO characterization, the input signals \({V}_{1}\) and \({V}_{2}\) are applied to the two MRAMs and a current source (\({I}_{{{{{{\rm{Bias}}}}}}}\)) is added in parallel, as shown in the electric circuit in Fig. 3b. The total STNO excitation current \(({I}_{{{{{{\rm{STNO}}}}}}})\) is given by (1). The current flowing through each MRAM \(({I}_{i})\) results from the input voltage (\({V}_{i}\)) and the conductance of each MRAM (\({G}_{i}={R}_{i}^{-1}\)), but is slightly reduced by a leak current as expressed in (2). The current flow is determined by the relation of STNO resistance \(({R}_{{{{{{\rm{STNO}}}}}}})\) to the MRAM resistances \(({R}_{{{{{{\rm{MRAM}}}}}}})\). The leakage is minimized in the limit of \({R}_{{{{{{\rm{STNO}}}}}}}\ll {R}_{{{{{{\rm{MRAM}}}}}}}\), which results in the typical artificial neuron output Eq. (3)49. The MRAMs weight and accumulate the inputs, which are then non-linearly converted into the output power \({P}_{{{{{{\rm{STNO}}}}}}}\).

with the resistance of all MTJs in parallel given by \({R}_{{{{{{\rm{parallel}}}}}}}={\left({\sum }_{i}{R}_{i}^{-1}+{R}_{{{{{{\rm{STNO}}}}}}}^{-1}\right)}^{-1}\) and \(f\) being the non-linear transfer function, which is here the \({P}_{{{{{{\rm{STNO}}}}}}}\) behavior. \({P}_{{{{{{\rm{STNO}}}}}}}\) is a function of \({I}_{{{{{{\rm{STNO}}}}}}}\) and resembles the shape of the commonly used leaky ReLU transfer function (see Fig. 1c) with additional step at the critical current50.

a WSTNO consisting of two magnetic memories (MRAM) as weights and a larger nanopillar as a spin torque nano-oscillator (STNO). The MRAMs are the non-volatile weights and the STNO is responsible for the non-linear transfer function of the neuron. b Schematic of the DC circuit used in the demonstration presented here. The input voltages (V1 and V2) are weighted by the MRAMs together with the bias current (IBias) and excite the STNO. The STNO excitation current (ISTNO) is converted non-linearly into an oscillating output power. c Example schematic showing the layout of two layers with each 3 inputs and 3 outputs demonstrating the scaling of the suggested neuromorphic circuit consisting of a crossbar array of MRAMs and STNO elements at the output of each layer. The number of inputs, outputs and layers can be scaled and each should increase the footprint linearly. The peak detector shown here is the interface circuit between layers and could be implemented in CMOS as discussed in the manuscript. d Network representation of the suggested neuromorphic circuit. Shown are the input voltages (Vi), the conductance as the weights (Gik) of the synapses (MRAMs), the neuron (STNO) with output power (Pk), the peak detector and the simplified subsequent layer.

In Fig. 4, we present the integrated \({P}_{{{{{{\rm{STNO}}}}}}}\) of one WSTNO as a function of the two input voltages applied to two MRAMs. The \({P}_{{{{{{\rm{STNO}}}}}}}\) shows a non-linear behavior weighted by the non-volatile input states (P or AP) of each MRAM, shown in the subfigures Fig. 4a–d. The non-linear behavior of \({P}_{{{{{{\rm{STNO}}}}}}}\) is clearly shown for each of the possible input states. The behavior of the artificial neuron is analytically predicted, as shown in Fig. 4e–h, based on Eq. (3) and the experimental characterizations of the individual MRAMs and the STNO, specifically the resistance values of all components and the behavior of \({P}_{{{{{{\rm{STNO}}}}}}}\) as a function of \({I}_{{{{{{\rm{STNO}}}}}}}\). The WSTNO is programmed by minor loops of the applied magnetic field, which sets each MRAM in the respective state. For optimal oscillation conditions during the WSTNO characterization an in-plane magnetic field of −19 Oe and \({I}_{{{{{{\rm{Bias}}}}}}}\) of 3.9 mA are applied to the STNO. A comparable magnetic field of −22 Oe was applied to the MRAM during operation. Thus, a magnetic field of similar magnitude is applied to all spintronic devices during the WSTNO characterization.

a–d Measured oscillation power (P) of the WSTNO as a function of the input voltages (V1 and V2) for each possible combination of the non-volatile states of the MRAMs: parallel (P) and anti-parallel (AP). Each figure represents a computation with two analog inputs and one analog output according to (3). The contour of 1 µW output power is shown in red. e–h Analytical prediction of the WSTNO behavior as a function of the two input voltages for each state combination. This prediction is obtained using formula (3) and the characterizations of the individual MRAMs and the STNO.

Discussion

The measured \({P}_{{{{{{\rm{STNO}}}}}}}\) of the WSTNO follows the predicted behavior reasonably well. There are some deviations in the mixed resistance states (P-AP, AP-P) and a structure along the scan direction (parallel to the y-axis) of the experiment is observed. We believe this is due to heating effects and small irreversible resistance changes of the nanometer-sized MRAMs during the four-hour measurement required to gather the data in Fig. 4 with high resolution. We believe the stability could be improved by reducing the RxA or increasing the lateral size of the MRAM devices. Nevertheless, the results clearly show the ability to program and perform computations through this WSTNO-based implementation of an artificial neuron.

As an example, we can classify the artificial neuron as active above a characteristic threshold power of \({P}_{{{{{{\rm{STNO}}}}}}} > \) 1 µW as marked by the contour in Fig. 4. In the P-P configuration the WSTNO activates above a combined voltage of both inputs (V1 + V2) of 1.35 V, as shown in Fig. 4a. However, programmed to the AP-AP configuration, the WSTNO activates at a combined input (V1 + V2) above 1.46 V, as shown in Fig. 4d. In the mixed states (P-AP, AP-P) one of the inputs will be weighted less and the STNO will show an asymmetric activation behavior, as shown in Fig. 4b, c, f, g. The specific activation range can be shifted using the \({I}_{{{{{{\rm{Bias}}}}}}}\) value.

The non-volatile MRAMs can be programmed by 1 ns current pulses of 30 pJ. Although not directly comparable, this performance looks promising considering that state of the art networks such as Loihi by Intel has a system level consumption of 120 pJ energy per synaptic update, which required 6.1 ns51. Due to the non-volatility the static power consumption of WSTNO is almost zero, while we estimate the required oscillation energy of a single STNO neuron with about 25 pJ in 5 ns operating time (see Table 1 and Supplementary Note 2). Although not directly comparable, this looks promising considering the reported energy consumption of a single neuron in Loihi is 81 pj/52 pJ when it is active/inactive. Compared to vortex STNOs based neuron implementation in literature the footprint, frequencies and input powers are in a comparable range, while the output power is about an order of magnitude larger in the presented devices21. From a fundamental point of view, there is wide room for improvement in terms of footprint and input power particularly by reducing the STNO diameter as suggest in literature20.

Device-to-device variations, as mentioned in the MRAM and STNO characterization, can have an noticeable effect in large networks and the fabrication processes should be further optimized with this in mind. We believe these variations can be partially compensated during the training phase and by the CMOS circuit. For example, lowering the weights or adjusting the bias current can correct a low critical current value. Certainly, the remaining variations might affect the quantized weight resolution of the WSTNO and the final output value.

As an outlook, a future WSTNO system will have multiple distinct weighting levels (resistance states)52, many more inputs (number of input voltages), and multiple detection levels (output power of the STNO). Multiple of these basic elements can compute in parallel in layers and multiple layers follow each other in series (see Fig. 3a–d) to perform more complex operations in a neural network13. To increase the distinct weighting levels, additional MRAMs of varying sizes can be added in series to extend the weighting states to higher binary numbers. First results of this approach are shown in Supplementary Fig. 2. The monolithic integration of WSTNOs on CMOS will be an important step to reach this level of complexity.

The presented WSTNO system receives DC voltages as inputs and converts them to a current depending on the state of the MRAM element. A DC bias current is added, as shown in Fig. 3. The combined current excites the STNO non-linearly into oscillation. This bias current is set below the critical current of the oscillation of a WSTNO. Hence, no current through the MRAMs means no oscillation and negligible output power. By applying the inputs to the MRAMs, for \({I}_{{{{{{\rm{STNO}}}}}}}\) (see Eq. (1)) higher than a threshold current, the corresponding WSTNOs will oscillate which means the corresponding neuron is firing. Then the AC voltage across STNO will be sensed using a peak detector (PD) circuit and will be converted to a binary output. In case there is no oscillation for an STNO, the output of PD will be ‘0’ (no spike), otherwise, it will be ‘1’ (representing a spike). The PD can be a CMOS inverter-based low noise amplifier with a sub-µW power consumption53, which is followed by a comparator with a power consumption lower than 200 µW54. As a result, the whole proposed neural network works similar to a spiking neural network (SNN). To demonstrate the feasibility on a network level we simulated a simple binary network of 10 STNOs with 20 weights each in Cadence Virtuoso with the task of recognizing digits represented by 4 × 5 pixels pictures. The successful results of this simulations are shown in Supplementary Note 3.

Alternatively, an artificial neural network that computes analog output signals can be implemented using an envelope detector instead of the PD at the cost of speed and power. Similarly, the spin diode effect or wide-band diode effects in vortex STNOs can be used as frequency dependent rectifiers55,56,57 considering sufficient amplification by the CMOS circuit. This conversion stage offers an opportunity to tackle the scaling problem by interconnecting subsequent layers through a single wave-guide that interconnects the multiplexed frequency signal of all outputs to all inputs15,20. Another opportunity for optimization is local optical heating for example by integrating vertical-cavity surface-emitting laser (VCSEL) structures for the temporary reduction of the critical currents12,58.

Methods

MTJ stack

The MTJ stack containing two CoFeB layers sandwiching an MgO tunneling barrier was deposited on Si/200 nm SiO2 substrate in a physical vapor deposition system with a base pressure of 10–9 Torr. The top CoFeB is in close proximity to a NiFe layer that creates a magnetic vortex structure. This bilayer acts as the free layer of the MTJ. The bottom CoFeB layer is called pinned layer and is coupled to the synthetic antiferromagnet that forces the magnetization to point uniformly towards the reference direction. If the free layer is aligned with the reference direction the MTJ is in the parallel configuration with low electrical resistance, while in the other extreme it is in the anti-parallel configuration with high resistance. More details on similar devices are found elsewhere59,60.

MTJ nanopillar fabrication

The nanopillar fabrication can be separated in four parts: nanopillar patterning, bottom electrode definition, planarization, and top electrode definition. The electron beam lithography was used to define the nanopillar, otherwise direct write laser lithography was used. The dielectric material that surrounds the nanopillars was SiO2. The top contact was a 450 nm layer of AlSiCu alloy and the field line was an 800 nm layer of AlSiCu alloy. Ion beam etching was used for all the etching purposes. We fabricated and studied not only individual devices of various shapes, sizes and MgO layer thicknesses, but also complete WSTNO systems consisting of two MRAMs and one STNO each. Further details of similar fabrication processes are described elsewhere35,38,42.

WSTNO setup

For the presented WSTNO experiments we used individual 300 nm diameter circular nanopillars as STNOs and two 75 nm × 225 nm elliptical nanopillars as MRAMs. Two interconnected probe stations with multiple micro positioners, three Keithley 2400 source measure units as inputs, a bias-T, and an Agilent E4446a spectrum analyzer to integrate the output power were used. The spectrum analyzer was used with a resolution bandwidth of 39 kHz. In each probestation a separately controlled external in-plane magnetic field was applied. The use of two probestation and individual devices gave us full control of the experimental parameters and allowed us to freely combine different geometries. No further amplification was necessary during the experiments. The oscillation power and frequency values were obtained by a Lorentz fit of the measured spectrum. The stated oscillation power values are as delivered to the 50 Ω load without any mismatch considerations.

Switching probability setup

A 100 nm x 200 nm nanopillar with a so-called field line a few 100 nm above the device was used for the analysis of the switching probability. We used a Keysight M8190A arbitrary waveform generator and a 42 dB amplifier to inject a single pulse into the 4 Ω field line. The pulse shape was monitored on a high input impedance oscilloscope. Pulses down to 1 ns pulse with an around ~0.5 ns rise time were obtained in this setup. The switching experiment was repeated 100 times at each condition to estimate the switching probability. The given pulse amplitudes and powers are measured at the field line, thus, losses due to mismatching of the electric circuit are not included.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Markov, I. L. Limits on fundamental limits to computation. Nature 512, 147–154 (2014).

Kim, J. et al. Spin-based computing: Device concepts, current status, and a case study on a high-performance microprocessor. Proc. IEEE 103, 106–130 (2015).

Poon, C.-S. & Zhou, K. Neuromorphic silicon neurons and large-scale neural networks: Challenges and opportunities. Front Neurosci. 5, 108 (2011).

Sourikopoulos, I. et al. A 4-fJ/spike artificial neuron in 65 nm CMOS technology. Front Neurosci. 11, 123 (2017).

Ambrogio, S., Balatti, S., Nardi, F., Facchinetti, S. & Ielmini, D. Spike-timing dependent plasticity in a transistor-selected resistive switching memory. ACS Sym. Ser. 24, 384012 (2013).

Saïghi, S. et al. Plasticity in memristive devices for spiking neural networks. Front Neurosci. 9, 51 (2015).

Nahmias, M. A., Shastri, B. J., Tait, A. N. & Prucnal, P. R. A leaky integrate-and-fire laser neuron for ultrafast cognitive computing. IEEE J. Select. Topics Quantum Electron. 19, 1–12 (2013).

Romeira, B., Avó, R., Figueiredo, J. M. L., Barland, S. & Javaloyes, J. Regenerative memory in time-delayed neuromorphic photonic resonators. Sci. Rep. 6, 19510 (2016).

Zahedinejad, M. et al. Memristive control of mutual spin Hall nano-oscillator synchronization for neuromorphic computing. Nat. Mater. 21, 81–87 (2021).

Romera, M. et al. Vowel recognition with four coupled spin-torque nano-oscillators. Nature 563, 230–234 (2018).

Tu, H. et al. Spin torque oscillator based on magnetic tunnel junction with MgO cap layer for RF-oriented neuromorphic computing. Chin. Phys. B https://doi.org/10.1088/1674-1056/acb424 (2023).

Farkhani, H. et al. LAO-NCS: Laser assisted spin torque nano oscillator-based neuromorphic computing system. Front Neurosci 13, 1–5 (2020).

Grollier, J., Querlioz, D. & Stiles, M. D. Spintronic nanodevices for bioinspired computing. Proc. IEEE 104, 2024–2039 (2016).

Lequeux, S. et al. A magnetic synapse: multilevel spin-torque memristor with perpendicular anisotropy. Sci. Rep. 6, 31510 (2016).

Leroux, N. et al. Hardware realization of the multiply and accumulate operation on radio-frequency signals with magnetic tunnel junctions. Neuromorphic Comput. Eng. 1, 11001 (2021).

Raymenants, E. et al. Chain of magnetic tunnel junctions as a spintronic memristor. J. Appl. Phys. 124, 152116 (2018).

Riou, M. et al. Neuromorphic computing through time-multiplexing with a spin-torque nano-oscillator. in 2017 IEEE International Electron Devices Meeting (IEDM) (2017). https://doi.org/10.1109/iedm.2017.8268505.

Roy, K., Jaiswal, A. & Panda, P. Towards spike-based machine intelligence with neuromorphic computing. Nature 575, 607–617 (2019).

Torrejon, J. et al. Neuromorphic computing with nanoscale spintronic oscillators. Nature 547, 428–431 (2017).

Leroux, N. et al. Convolutional neural networks with radio-frequency spintronic nano-devices. Neuromorph. Comput. Eng. 2, 34002 (2022).

Romera, M. et al. Binding events through the mutual synchronization of spintronic nano-neurons. Nat. Commun. 13, 883 (2020).

Tu, H. et al. Neural-like population coding based on spin-torque diode. Appl. Phys. Lett. 122, 122402 (2023).

Zhang, L. et al. Ultralow-current density spin-torque diodes with high sensitivity. Appl. Phys. Lett. 122, 92405 (2023).

Grollier, J. et al. Neuromorphic spintronics. Nat. Electr. 3, 360–370 (2020).

Dieny, B. et al. Opportunities and challenges for spintronics in the microelectronics industry. Nat. Electr. 3, 446–459 (2020).

Manipatruni, S. et al. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 565, 35–42 (2018).

Manipatruni, S., Nikonov, D. E. & Young, I. A. Beyond CMOS computing with spin and polarization. Nat. Phys. 14, 338–343 (2018).

Jarollahi, H. et al. A nonvolatile associative memory-based context-driven search engine using 90 nm CMOS/MTJ-hybrid logic-in-memory architecture. IEEE J. Emerg. Sel. 4, 460–474 (2014).

Zhu, J., Zhang, T., Yang, Y. & Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 7, 11312 (2020).

Cai, B. et al. Unconventional computing based on magnetic tunnel junction. Appl. Phys. A 129, 236 (2023).

Dussaux, A. et al. Large microwave generation from current-driven magnetic vortex oscillators in magnetic tunnel junctions. Nat. Commun. 1, 1–6 (2010).

Chavent, A. et al. A multifunctional standardized magnetic tunnel junction stack embedding sensor, memory and oscillator functionality. J. Magn. Magn. Mater. 505, 166647 (2020).

Dussaux, A. et al. Field dependence of spin-transfer-induced vortex dynamics in the nonlinear regime. Phys. Rev. B 86, 014402 (2012).

Pribiag, V. S. et al. Magnetic vortex oscillator driven by d.c. spin-polarized current. Nat. Phys. 3, 498–503 (2007).

Costa, J. D. et al. High power and low critical current density spin transfer torque nano-oscillators using MgO barriers with intermediate thickness. Sci. Rep. 7, 7237 (2017).

Houssameddine, D. et al. Spin transfer induced coherent microwave emission with large power from nanoscale MgO tunnel junctions. Appl. Phys. Lett. 93, 22505 (2008).

Liu, L., Pai, C.-F., Ralph, D. C. & Buhrman, R. A. Magnetic oscillations driven by the spin hall effect in 3-terminal magnetic tunnel junction devices. Phys. Rev. Lett. 109, 186602 (2012).

Tarequzzaman, M. et al. Spin torque nano-oscillator driven by combined spin injection from tunneling and spin Hall current. Commun. Phys. 2, 20 (2019).

Tsunegi, S., Yakushiji, K., Fukushima, A., Yuasa, S. & Kubota, H. Microwave emission power exceeding 10 µW in spin torque vortex oscillator. Appl. Phys. Lett. 109, 252402 (2016).

Jin, W., He, H., Chen, Y. & Liu, Y. Controllable vortex polarity switching by spin polarized current. J. Appl. Phys. 105, 13906 (2009).

Metlov, K. L. & Guslienko, K. Y. Stability of magnetic vortex in soft magnetic nano-sized circular cylinder. J. Magn. Magn. Mater. 242-245, 1015–1017 (2002).

Tarequzzaman, M. et al. Influence of MgO tunnel barrier thickness on the output power of three-terminal spin hall nano-oscillators. IEEE Trans. Magn. 54, 1–4 (2018).

Maranhão, G. & Guimarães, J. G. Low-power hybrid memristor-CMOS spiking neuromorphic STDP learning system. IET Circuits, Devices Syst. 15, 237–250 (2021).

Stiles, M. D. & Miltat, J. Spin-transfer torque and dynamics. in Spin Dynamics in Confined Magnetic Structures III 225–308 (Springer, Berlin, Heidelberg, 2006). https://doi.org/10.1007/10938171_7.

Jenkins, A. S. et al. The impact of local pinning sites in magnetic tunnel junctions with non-homogeneous free layers. Preprint at https://doi.org/10.48550/ARXIV.2304.08228 (2023).

Schumacher, H. W. et al. Phase coherent precessional magnetization reversal in microscopic spin valve elements. Phys. Rev. Lett. 90, 17201 (2003).

Sousa, R. C. & Prejbeanu, I. L. Non-volatile magnetic random access memories (MRAM). C. R. Phys. 6, 1013–1021 (2005).

Song, Y. J. et al. Highly functional and reliable 8Mb STT-MRAM embedded in 28nm logic. in 2016 IEEE International Electron Devices Meeting (IEDM) 27.2.1-27.2.4 (2016). https://doi.org/10.1109/iedm.2016.7838491.

Haykin, S. Neural Networks: A Comprehensive Foundation. 696 (Macmillan, 1994). https://doi.org/10.1017/S0269888998214044.

Maas, A. L., Hannun, A. Y. & Ng, A. Y. Rectifier nonlinearities improve neural network acoustic models. Proc. ICML 30, 3 (2013).

Davies, M. et al. Loihi: A neuromorphic manycore processor with on-chip learning. IEEE Micro 38, 82–99 (2018).

Rzeszut, P. et al. Multi-state MRAM cells for hardware neuromorphic computing. Sci. Rep. 12, 7178, https://doi.org/10.1038/s41598-022-11199-4 (2022).

Parvizi, M., Allidina, K. & El-Gamal, M. N. A sub-mW, ultra-low-voltage, wideband low-noise amplifier design technique. IEEE Trans. Very Large Scale Integr. (VLSI) 23, 1111–1122 (2015).

Siddharth, R. K., Satyanarayana, Y. J., Kumar, Y. B. N., Vasantha, M. H. & Bonizzoni, E. A 1-V, 3-GHz strong-arm latch voltage comparator for high speed applications. IEEE Tran. Circuits Syst. II: Express Briefs 67, 2918–2922 (2020).

Jenkins, A. S. et al. Wideband high-resolution frequency-to-resistance converter based on nonhomogeneous magnetic-state transitions. Phys. Rev. Applied 13, 014046 (2020).

Jenkins, A. S., Alvarez, L. S. E., Freitas, P. P. & Ferreira, R. Digital and analogue modulation and demodulation scheme using vortex-based spin torque nano-oscillators. Sci. Rep. 10, 11181 (2020).

Marković, D. et al. Detection of the microwave emission from a spin-torque oscillator by a spin diode. Phys. Rev. Applied 13, 044050 (2020).

Farkhani, H., Prejbeanu, I. L. & Moradi, F. LAS-NCS: A laser-assisted spintronic neuromorphic computing system. IEEE Trans. Circuits Syst. II: Expr. Briefs 66, 838–842 (2019).

Jenkins, A. S. et al. Phase variation in the locked state of mutually synchronized spin torque nano-oscillators. Appl. Phys. Lett. 118, 172406 (2021).

Martins, L. et al. Non-volatile artificial synapse based on a vortex nano-oscillator. Sci. Rep. 11, 16094 (2021).

Acknowledgements

This work was supported by the project SpinAge, that received funding from the European Union’s Horizon 2020 research and innovation program under grant agreement No 899559.

Author information

Authors and Affiliations

Contributions

T.B. and R.F. conceived the WSTNO concept, which was further developed together with Y.R., A.J., H.F. and F.M. M.C., fabricated the devices in collaboration with L.B. who optimized many of the process steps. T.B. set up the experiments and performed the measurements. Y.R. simulated the neural network. T.B., Y.R., A.J., H.F., F.M., and R.F. contributed to the writing of the manuscript and analyses of the results. R.F. coordinated the activities.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Engineering thanks Fang Bin, Lucian Prejbeanu and the other, anonymous, reviewer for their contribution to the peer review of this work. Primary Handling Editors: Mengying Su.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Böhnert, T., Rezaeiyan, Y., Claro, M.S. et al. Weighted spin torque nano-oscillator system for neuromorphic computing. Commun Eng 2, 65 (2023). https://doi.org/10.1038/s44172-023-00117-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s44172-023-00117-9

This article is cited by

-

Editors’ Choice 2023

Communications Engineering (2023)