Abstract

The co-integration of spin, superconducting, and topological systems is emerging as an exciting pathway for scalable and high-fidelity quantum information technology. High-mobility planar germanium is a front-runner semiconductor for building quantum processors with spin-qubits, but progress with hybrid superconductor-semiconductor devices is hindered by the difficulty in obtaining a superconducting hard gap, that is, a gap free of subgap states. Here, we address this challenge by developing a low-disorder, oxide-free interface between high-mobility planar germanium and a germanosilicide parent superconductor. This superconducting contact is formed by the thermally-activated solid phase reaction between a metal, platinum, and the Ge/SiGe semiconductor heterostructure. Electrical characterization reveals near-unity transparency in Josephson junctions and, importantly, a hard induced superconducting gap in quantum point contacts. Furthermore, we demonstrate phase control of a Josephson junction and study transport in a gated two-dimensional superconductor-semiconductor array towards scalable architectures. These results expand the quantum technology toolbox in germanium and provide new avenues for exploring monolithic superconductor-semiconductor quantum circuits towards scalable quantum information processing.

Similar content being viewed by others

Introduction

The intimate coupling between superconductors and semiconductors in hybrid devices is at the heart of exciting pursuits, including topological qubits with Majorana zero modes1,2, superconducting (Andreev) spin qubits3, and gate-tunable superconducting qubits4. Combining hybrid devices with high-fidelity semiconductor spin qubits in a single material platform may resolve key challenges for scalable quantum information processing. In particular, quantum information transfer between spin and topological qubits5,6,7,8 may enable a universal gate set for topological quantum computation and, conversely, superconductors may be used to coherently couple spin qubits at a distance via crossed Andreev reflection5,9 or topologically protected links10.

The use of epitaxial superconducting Al to induce a hard superconducting gap in III-V semiconductors11,12 stimulated great progress with hybrid devices, leading to experimental reports of topological superconductivity in planar Josephson junctions13 and in electrostatically defined quasi-1D wires14, the demonstration of Andreev spin qubits3, and the realization of a minimal Kitaev chain in coupled quantum dots15. However, spin qubits in III-V semiconductors suffer from the hyperfine interactions with the nuclear spin bath16 that severely deteriorate their quantum coherence17 and challenges their integration with hybrid devices.

On the other hand, spin qubits with quantum dots in Ge18,19,20,21 can achieve long quantum coherence due to the suppressed hyperfine interaction22 and the possibility of isotopic purification into a nuclear spin-free material23. Thanks to the light effective mass24 and high mobility exceeding one million cm2/Vs25, holes in planar Ge/SiGe heterostructures have advanced semiconductors spin qubits to the universal operation on a 2 × 2 qubit array26, and the shared control of a 16 semiconductor quantum dot crossbar array27. Moreover, the ability of holes to make contacts with low Schottky barrier heights to metals28, including superconductors, makes Ge a promising candidate for hybrid devices. Initial work used superconducting Al to contact Ge either via thermal diffusion29,30,31 or by deposition on the sidewalls of etched mesas32,33. However, the key demonstration of a superconducting gap in Ge free of subgap quasiparticle states is lacking, challenged by the difficulty of contacting uniformly a buried quantum well (QW) with a superconductor, whilst maintaining the low disorder at the superconductor-semiconductor interface and in the semiconductor channel.

Here we address these challenges and demonstrate a hard superconducting gap in Ge. We contact the quantum well with a superconducting germanosilicide (PtSiGe), similar to the silicidation process used by the microelectronics industry for low resistance contacts34. The superconductor is formed uniformly within the heterostructure and reaches the buried quantum well via a controlled thermally-activated solid phase reaction between the metal (Pt) and the semiconductor stack (Ge/SiGe). This process is simple, robust, and does not require specialised vacuum conditions or etching because the superconductor-semiconductor interface is buried into the pure semiconducting heterostructure and consequently remains pristine. This represents a conceptually different approach compared to the subtractive nanofabrication processes commonly used for hybrid devices, since our additive process does not deteriorate the active area of the semiconductor. As a result, we demonstrate a suite of reproducible Ge hybrid devices with low disorder and excellent superconducting properties.

Results

Material properties

Our approach to superconductor-semiconductor hybrid devices in Ge is illustrated in Fig. 1a. We use an undoped and compressively-strained Ge quantum well, grown by chemical vapor deposition on a Si(001) wafer35 and separated from the surface by a SiGe barrier (Methods). This heterostructure supports a two-dimensional hole gas (2DHG) with high mobility (~6 × 105 cm2/Vs), long transport scattering time τ (~30 ps), and long mean free path (~7 μm) (Supplementary Fig. 1) and hosts high-performance spin-qubits20. Crucial for the reliable search of topological superconductivity36 and for scaling to large spin-qubit architectures37, the disorder in our buried Ge quantum wells is characterised by an energy level broadening ℏ/2τ of ~0.01 meV, which is more than one order of magnitude smaller than in the other material systems exhibiting a hard superconducting gap (Supplementary Table 1).

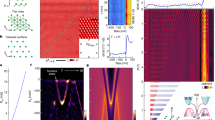

a Schematics of the fabrication process for a superconductor-normal-superconductor quantum point contact (SNS-QPC). First, platinum is deposited on the heterostructure, then thermal annealing at 400 ∘C drives Pt in the heterostructure to form PtSiGe, finally two gate layers are deposited, insulated by Al2O3. b False-color high angle annular dark field scanning transmission electron microscopy (HAADF STEM) image of a cross-section of a SNS-QPC. The PtSiGe contacts are violet, the Ti/Pd constriction gate (CG) operated in depletion mode is yellow, the Ti/Pd accumulation gate (AG), used to populate the quantum well, is green. A scanning electron microscopy top view image of this device is shown in Fig. 2. c Atomic resolution HAADF STEM image of the Ge/PtSiGe interface along with the indexed fast Fourier transforms (FFTs) of the two regions (black squares) within the PtSiGe contacts and a schematics of the PtSiGe orthorhombic unit cell. The corresponding ternary lattice parameters T = aT, bT, cT that define the dimensions of the unit cell can be calculated, in a first approximation, by Vegard’s law: \({T}_{{{{{{{{\rm{PtS{i}}}}}}}_{1-x}G{e}_{x}}}}=x\,{B}_{{{{{{{{\rm{PtGe}}}}}}}}}+(1-x)\,{B}_{{{{{{{{\rm{PtSi}}}}}}}}}\) where B = aB, bB, cB are the lattice parameters of the binary compounds PtSi and PtGe, and x is the relative content of Ge with respect to Si. d Electron energy-loss spectroscopy (EELS) composition maps showing the Pt, Ge, Si and O signals for the central area of the TEM lamella of panel (b), the scale-bar indicates 50 nm. The PtGeSi stoichiometry is extracted by quantitative EELS analysis and reported in Supplementary Fig. 4.

As shown by the schematics in Fig. 1a, we obtain PtSiGe contacts to the quantum well by room-temperature evaporation of a Pt supply layer, metal lift-off, and rapid thermal process at 400 ∘C (Methods). This low-temperature process preserves the structural integrity of the quantum well grown at 500 ∘C, whilst activating the solid phase reaction driving Pt into the heterostructure and Ge and Si into the Pt (Supplementary Fig. 3). As a result, low-resistivity germanosilicide phases are formed38,39 and under these process conditions the obtained PtSiGe films are superconducting with a Tc ≈ 0.5 K and an in-plane critical field of Bc∥ ≈ 400 mT (Supplementary Fig. 2). Finally, we use patterned electrostatic gates, insulated by dielectric films in between, to accumulate charge carriers in the quantum well and to shape the electrostatic confinement potential of the hybrid superconductor-semiconductor devices (Methods). This approach to hybrid devices is different compared to the conventional process with 1D nanowires, where an epitaxial superconductor proximitizes the semiconductor region underneath. Because we do not perform any etch during the nanofabrication of hybrid devices, the low-disorder landscape that determines the 2DHG high mobility is likely to be preserved when further dimensional confinement is achieved by means of electrostatic gates. By contrast, for processes where etching of the superconductor is required, the fabrication of hybrid devices yields to mobility degradation40.

The morphological, structural, and chemical properties of the hybrid devices are inferred by aberration corrected high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) and electron energy-loss spectroscopy (EELS). Figure 1b shows a HAADF-STEM image of a cross-section of a superconductor-normal-superconductor quantum point contact (SNS-QPC) taken off-center to visualise the two gate layers (Fig. 2a shows a top view of the device). We observe a uniform quantum well of high-crystalline quality, with sharp interfaces to the adjacent SiGe and absence of extended defects. As a result of the annealing, Pt diffuses predominantly vertically through the SiGe spacer reaching the quantum well. The sharp lateral interfaces between the two PtSiGe contacts and the QW in between set the length of the channel populated by holes via the top-gates. The PtSiGe film presents poly-crystalline domains with a crystal size up to 50 × 50 nm and orthorhombic phase (PBNM, space group number 62)41. This is inferred from the power spectra or fast Fourier transforms (FFTs) taken from the two PtSiGe domains interfacing with the QW from the left contact, shown in Fig. 1c along with a schematic view of the unit cell of such phase. More detailed studies by atomic-resolution plane HAADF-STEM are required to assess the junction uniformity in the direction parallel to the junction and whether this would impact Majorana experiments. The analysis of EELS elemental concentration profiles across the Ge QW → PtSiGe heterointerface (Supplementary Fig. 4) reveals that the threefold PtSiGe stoichiometry is Ge-rich, with relative composition in the range between Pt0.1Si0.2Ge0.7 and Pt0.1Si0.05Ge0.85 depending locally on the analysed grain. The EELS compositional maps in Fig. 1d show the elemental distribution of Ge, Si, Pt, Al, and O, at the key regions of the device. We observe Pt well confined to the two contacts areas, which also appear Ge-rich. Crucially, O is detected only in the Al2O3 dielectric layer below the gates, pointing to a high-purity quantum well and a pristine superconductor-semiconductor interface.

a False-color scanning electron microscope image of the SNS device. The PtSiGe contacts are violet, the constriction gates (CG) are yellow and the accumulation gate (AG) is green. The channel length between the two superconducting leads is 70 nm and the channel width between the constriction gates is 40 nm. The two constriction gates are separate by design but always shorted together during measurements. b Color map of the voltage drop across the junction V vs source-drain current ISD and constriction-gate voltage VCG at zero magnetic field along with normal-state conductance GN trace vs VCG. GN is calculated as the conductance average where the voltage drop across the device is in the range [500, 650] mV or -[650, 500] mV, that is much higher than the estimated superconducting gap. c Color map of G in units of 2e2/h vs the source-drain voltage VSD and VCG. Bottom panel shows line-cuts of conductance at VCG = [−1.25,−1.4,−1.49]V, red lines are the fit with the coherent scattering model from which transparency τ is extracted. Right inset shows the evolution of the transparency, as extracted from the fitting of conductance curves to the coherent scattering model (Methods), with the constriction gate VCG. d Color map of G vs T and VSD (top panel), and vs B∥ and VSD (bottom panel), where B∥ is the in-plane magnetic field in the direction of transport and T the temperature. The color scale in panel (d) has been saturated to better infer the low conductance limit. The source-drain bias is applied between the PtSiGe contacts, and the voltage drop across the junction is measured with a standard 4-terminal setup. The accumulation voltage for measurements in (b, c and d) was set to −4.5V, where the 2DHG is expected to reach saturation density (see Supplementary Fig. 1) of ≃6 × 1011 cm−2 35. Measurement presented in (b, c) and in panel (d (bottom)), are performed at 15 mK, corresponding to an electron temperature of ~25 mK.

Highly transparent Josephson junction

We perform low-frequency four-terminal current and voltage bias measurements (Methods) on the SNS-QPC device shown in Fig. 2a to infer the properties of the superconductor-semiconductor interface. Accumulation (AG, in green) and constriction (CG, in yellow) gates control transport within the 70 nm long channel between the two PtSiGe leads. We apply a large negative voltage to the accumulation gate to populate the quantum well with holes, and we then control the effective width of the channel by applying a more positive voltage to the constriction gates, thus depleting the underlying quantum well.

The current bias measurements (Fig. 2b) reveal a tunable supercurrent with a plateau when the constriction gate voltage VCG is in the range ≈[−1.75, −1.50] V. This is the same range where we observe the first conductance plateau in the normal-state conductance GN (Fig. 2b, right inset), indicating that the switching current (Isw) plateau observed in the color plot stems form the supercurrent discretization due to the discrete number of modes in the QPC30,42. Supercurrent discretization up to the third conductance plateau is shown in Supplementary Fig. 5 (data are for a different SNS-QPC device with identical design to the one presented here). The discretization of the supercurrent at zero magnetic field, indicates that the quality of the 2DHG is preserved also upon the formation of the superconducting contacts. We use the switching current as a lower bound for the critical current and we estimate an IswRN product of 51 μV, showing an improvement as compared to previous results obtained with pure Al contacts in Ge QWs30,32,33, despite the Al Tc is higher than the PtSiGe Tc. The measured IswRN product is ~0.5 times the theoretical IcRN product calculated for a ballistic short junction using the Ambegaokar-Baratoff formula πΔ*/2e = 110 μV with Ic being the critical current, Δ* the induced superconducting gap and e the electron charge43. This discrepancy has been observed in previous works30,44 and is consistent with a premature switching due to thermal activation45.

By operating the device in voltage-bias configuration and stepping the constriction gates, we observe in the conductance color plot the typical signature of multiple Andreev reflections (MARs) (Fig. 2c). When the applied voltage bias corresponds to an integer fraction of 2Δ*, with Δ* being the induced superconducting gap, we observe differential conductance dI/dV peaks (dips) in the tunneling (open) regime46,47. We measure MARs up to the 5th order, suggesting that the coherence length ξN in the Ge QW is a few times larger than the junction length L, and setting a lower bound to the phase coherence length in the QW lψ > 5L = 350 nm. These observations are consistent with the findings of ref. 33 where a similar Ge/SiGe heterostructure is used. Fitting the differential conductance with the coherent scattering model described in ref. 48 (and used in refs. 44,47,49) reveals single channel transport with gate tunable transparency up to 96%. Such a high transparency confirms the high quality interface between the PtSiGe and the Ge QW. From the MARs fit we estimate an induced superconducting gap Δ* = 70.6 ± 0.9 μeV, which is about half compared to the Δ* = 129 μeV14 and 150 μeV50 for recent InAs-Al devices reporting topological superconductivity.

Further, we characterise the evolution of the induced superconducting gap with temperature and magnetic field. After setting the device in tunneling regime, where sharp coherence peaks are expected at e∣VSD∣ = 2Δ* (Fig. 2d), we observe the induced superconducting gap closing with increasing temperature and magnetic field. By fitting the temperature dependence of the coherence peaks with the empirical formula from ref. 51 we obtain a critical temperature of 0.5 K. The peak close to zero bias emerging at T > 0.2 K can be explained in terms of thermally-activated quasiparticle current49. The in-plane magnetic field in the transport direction quenches the superconductivity at Bc∥ = 0.37 T. The same critical field is found for the in-plane direction perpendicular to the transport direction while for the out of plane direction Bc⊥ = 0.1 T (Supplementary Fig. 6). This in-plane vs out-of-plane anisotropy is expected given the thin-film nature of the PtSiGe superconductor45.

Hard induced superconducting gap

To gain insights into the quality of the Ge/PtSiGe junction we characterise transport through the normal-superconductor quantum point contact (NS-QPC) device shown in Fig. 3a. Importantly, the methodology based on spectroscopy of NS devices alleviates the ambiguity of measuring the amount of quasiparticle states inside the gap with SNS junctions31. On the left side of the QPC there is a PtSiGe superconducting lead and on the right side a normal lead consisting of a 2DHG accumulated in the Ge QW. With the accumulation gate (AG) set at large negative voltages to populate the QW we apply a more positive voltage to the constriction gates (CG), creating a tunable barrier between the superconducting and the normal region. In Fig. 3b we progressively decrease the barrier height (decreasing VCG) going from the tunneling regime, where conductance is strongly suppressed, to a more open regime where conductance approaches the single conductance quantum G0. Line-cuts of the conductance color map are presented in the bottom panel of Fig. 3c. In the tunneling regime, we observe a hard induced superconducting gap, characterised by a two orders of magnitude suppression of the in-gap conductance to the normal-state conductance, and the arising of coherence peaks at e∣VSD∣ ≈ Δ* = 70 μeV. Figure 3b also shows that the induced superconducting gap varies with the constriction gate voltage. This observation brings confidence that we are measuring the induced superconducting gap rather than the parent gap52. A possible explanation is that, upon increasing the density in the semiconductor nearby the junction, the coupling to the parent superconductor might vary, as also observed in other hybrid nanostructures53.

a False-color SEM image of the normal-superconductor quantum point contact device (NS-QPC). The PtSiGe contact is violet, the constriction gate (CG) are yellow and the accumulation gate (AG) is green. The two constriction gates are separate by design but always shorted together during measurements. b Color map of conductance G vs the source-drain voltage VSD and constriction gate VCG, along with line cuts in log-scale of G at the constriction gate voltages VCG = [−733, −710, −695] mV marked by the colored segment in the color-plot. c Color map of G in units of 2e2/h vs the in-plane magnetic field B∥ perpendicular to the transport direction and constriction gate VCG, along with line cuts in log-scale of G at the field strength B∥ = [0.01, 0.1, 0.2, 0.3] T marked by the colored segment in the color-plot. d Conductance traces normalised to the above-gap conductance (G/GN) vs VSD in tunneling regime for 6 different NS-QPC devices D1−D6 processed in the same fabrication run, device D1 is the one reported in Fig. 3a–c, in the remaining devices the constriction gates separation varies (specifications of these devices are provided in Supplementary Fig. 8).

The evolution of the gap as a function of in-plane magnetic field (B∥) shown in Fig. 3c confirms that the gap remains hard for finite magnetic fields up to 0.25 T, ultimately vanishing at B∥ ≈ 0.37 T. The magnetic field evolution of the gap in all three directions matches the behaviour observed in the SNS-QPC (Supplementary Fig. 7).

Finally, Fig. 3d reports the conductance traces in tunneling regime for all the six measured devices (an overview of the geometries of these devices and the respective measurements are available in the Supplementary Fig. 8, the conductance maps for all these devices are shown in Supplementary Fig. 9). For all devices we observe suppression of conductance equal or larger than two orders of magnitude. At a quantitative level, the conductance traces of Fig. 3d are well fitted by the BTK theory54 (Supplementary Fig. 9) consistent with a hard induced superconducting gap free of subgap states11,44. This finding is the signature of a robust process that yields a reproducible high-quality superconductor-semiconductor interface, overcoming a long-standing challenge for hybrid superconductor-semiconductor quantum devices in Ge.

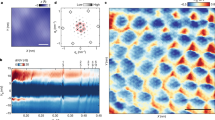

Superconducting quantum interference devices

We use the superconducting quantum interference device (SQUID) in Fig. 4a to demonstrate phase control across a Josephson junction, an important ingredient for achieving topological states at low magnetic field50,55,56,57. The device is composed of two Josephson field-effect transistors (JoFETs) with a width of 2 μm and 1 μm for JoFET1 and JoFET2 respectively, and equal length of 70 nm. The critical current of the junctions Ic1 and Ic2 can be tuned independently by applying the accumulation gate voltages VAG1 and VAG2 to the corresponding gates. We investigate the oscillations of the SQUID switching current as a function of the out-of-plane-magnetic field penetrating the SQUID loop. Namely, we set VAG1 and VAG2, such that both arms support supercurrent and Ic1 ≫ Ic2. This condition provides that the first junction is used as a reference junction and that the phase drop on it is flux independent, while the phase drop over the second junction is therefore modulated by the external flux through the loop. This allows the measurement of the current-phase-relation (CPR) of the second junction. This is demonstrated in Fig. 4b where the shown SQUID oscillations are well fitted by the relation: \({I}_{{{{{{{{\rm{c,SQUID}}}}}}}}}={I}_{{{{{{{{\rm{c}}}}}}}}1}({B}_{\perp }{A}_{1})+{I}_{{{{{{{{\rm{c}}}}}}}}2}({B}_{\perp }{A}_{2})\sin (2\pi {B}_{\perp }{A}_{{{{{{{{\rm{SQUID}}}}}}}}}-L{I}_{{{{{{{{\rm{c}}}}}}}}1}({B}_{\perp }{A}_{1})/{{{\Phi }}}_{0})\) where Ic1,2(BA1,2) are the Fraunhofer dependencies of the critical current obtained from fitting the Fraunhofer pattern of each junction (Supplementary Fig. 10), A1,2 are the junction areas, B⊥ is the out-of-plane magnetic field and Φ0 the flux quantum. From the fit of the data in Fig. 4b (red dashed-line) we extract the effective SQUID loop area ASQUID = 8.9 μm2 (comparable to the 10 μm2 SQUID geometric area) and the self-inductance L = 1.65 pH. In order to confirm for the self-inductance effects, we also fit SQUID oscillations for the opposite direction of the current bias (blue dashed-line) and we get similar values for the effective loop area and self-inductance.

a False-color SEM image of the two JoFET SQUID device. The JoFETs have a channel length of 70 nm and a channel width of 1 μm and 2 μm respectively and can be independently controlled by gates AG1 and AG2. The geometric loop area of the SQUID is of 10 μm2, calculated assuming a rectangle with sides positioned in the center of the PtSiGe loop cross-section. b Color-plot of voltage drop (V) across the SQUID vs current (I) and out-of-plane magnetic field (B⊥). Arrows represent the direction of the current (I) sweep. With the gate voltages set at VAG1 = − 3.5 V and VAG2 = − 1.65 V the superconducting phase drops mainly over the second junction. Upon sweeping the out-of-plane magnetic field B⊥ we observe oscillations of the switching current. Red and blue dashed lines are the fit of the evolution of the critical current with magnetic field. The magnetic field is applied in the out of plane direction as depicted in panel (a).

Scalable junctions

As a first step towards monolithic superconductor-semiconductor quantum circuits in two dimensions, we fabricate and study transport in a macroscopic hybrid device comprising a large array of 510 PtSiGe islands (Fig. 5a) and a global top gate. Each pair of neighbouring islands forms a Josephson junction whose transparency can be tuned by the global accumulation gate. The top panel of Fig. 5b shows a current bias measurement of the junctions array resistance. As the accumulation gate becomes more negative, all the junctions are proximitized and a supercurrent flows through the device. Remarkably, as the source-drain current approaches the junctions critical current the whole array simultaneously switches from superconducting to resistive regime, as shown from the sharp resistance step (Fig. 5b top).

a 3D and top view schematics of an array of 51 × 10 PtSiGe islands. The inset shows an atomic force microscopy image of the PtSiGe islands of the array. The PtSiGe islands are 930 × 930 nm wide and the separation between neighbouring islands is of 70 nm. b Top panel shows a color map of sheet resistance (RS) vs accumulation gate voltage VG and source-drain current ISD. Bottom panels shows a color map of sheet resistance vs out of plane magnetic field B and source-drain current ISD. The measurement is taken at gate voltage VG = − 1.99 V, where we expect carriers in the quantum well to approach a saturation density value of about 6 × 1011 cm−2 and have a mean free path (~7 μm) much longer than the separation between between neighbouring islands. Black arrows denote the magnetic field corresponding to one flux quantum Φ0 per unit cell of the array. Red arrows correspond to one-half flux per unit cell. c Sheet resistance as a function of temperature for gate voltages ranging from −2 V to −1.55 V. Yellow curves correspond to small negative gates, and purple curves to large negative gates.

With this device we also study the evolution of the switching current in a small perpendicular magnetic field. In the bottom panel of Fig. 5b we observe Fraunhofer-like interference, along with the fingerprint of flux commensurability effects associated with the periodicity of the array. At integer numbers of flux quantum per unit area of the periodic array f = B⊥/B0, where B0 = Φ0/A with A the junction area and Φ0 the flux quanta, we observe switching current peaks at ± 1f, 2f, 3f, 4f and 5f, denoted by a black arrow in the plot. We also notice this effect at fractional values of f, most notably at f/2 (red arrow). Flux commensurability effects, due to the pinning and interference of vortices in Josephson junctions arrays, have been previously reported58,59.

The observation of simultaneous switching of super-current and of the Fraunhofer pattern with flux commensurability effects, suggests that all islands effective areas are similar and that the supercurrent through the various junctions is comparable, meaning that all junctions respond synchronously to the applied gate voltage. This is further supported by the observation of sharp switching of super-current and the Fraunhofer pattern of a 1D array of superconducting islands presented in Supplementary Fig. 11.

Finally we present in Fig. 5c the sheet resistance as a function of temperature for different gate voltages. As the gate voltage becomes more negative, the coupling between neighbouring superconducting islands increases and the system transitions from an insulating to a superconducting regime. At low gate voltage the resistance increases with decreasing temperature (yellow curves) indicating the insulating state, while at high gates the resistance drops to zero (purple curves) owing to the global superconducting state. At intermediate gate voltages (−1.95V ≤ VG ≤ −1.93V, orange curves) there is a transition where the resistance shows a weak temperature dependence. It will be interesting to study this regime in detail, in light of the recent claims of an anomalous metallic state between the superconducting and the insulating phases59.

Discussion

In conclusion, we have developed superconducting germanosilicides for contacting Ge quantum wells, which has resulted in excellent superconducting properties imparted to the high-mobility 2DHG. We induced a hard superconducting gap in Ge, a large advancement compared to previous work on Ge hybrid superconductor-semiconductor devices30,31,32,33. We were able to observe a hard gap with 100% yield across all the six measured devices, pointing to a robust and reproducible fabrication process. Next to this central result, we further demonstrate phase control across a Josephson junction and take advantage of the planar geometry to scale these devices in 2D arrays.

While we focused on the poly-crystalline superconducting PtSiGe compound, we anticipate two strategies to further increase the size of the induced superconducting gap, which sets a relevant energy scale for hybrid devices. Firstly, following the approach in ref. 33 a superconducting layer with a larger gap, such as Al or Nb, may be deposited on top of the superconducting PtSiGe. Secondly, other ternary superconducting germanosilicides with a higher critical temperature may be explored, starting from the deposition and thermal anneal of other platinoid metals such as Rh and Ir60.

Based on our findings, we foresee the following use cases for superconductor-semiconductor hybrids in high mobility planar Ge. Although a hard gap is necessary but not sufficient on its own for achieving a topologically protected system, this work positions planar Ge as a promising platform to explore Majorana bound states in phased-biased Josephson junctions13,61,62. Calculations with experimentally realistic material parameters57 show that accessing the topological phase is feasible by careful design of Ge planar Josephson junctions geometries that relaxes magnetic field and spin-orbit constrains. More advanced future experiments should build on our current results to fully assess the readiness of Ge for Majorana bound states experiments, such as increasing the induced superconducting gap and measuring it by non local spectroscopy in multi-terminal devices and demonstrate the two-electron charging effect in hybrid Ge/PtSiGe islands, a pre-requisite for their use in topological quantum computation.

Crucially, the realization of a hard superconducting gap positions planar Ge as a unique material platform to pursue the coherent coupling of high fidelity spin qubits using crossed Andreev reflection to enable two-qubit gates over micrometer distances5,9. Remote coupling of spin qubits in Ge may also be achieved by coupling spin qubits via superconducting quantum dots5,6, potentially offering a topological protection10. Coupling on an even longer distance may be obtained via superconducting resonators63. In such a scenario, a capacitive interaction may suffice, but connecting the resonator to a superconducting ohmic, such as PtSiGe, could result in a larger lever arm and therefore boost the coupling, while a direct tunnel coupling would give further directions to explore. The ability to couple qubits over different length scales is highly relevant and a critical component in network-based quantum computing37.

Furthermore, the demonstration of a hard gap in Ge motivates the investigation of alternative spin qubits systems, such as Andreev spin qubits (ASQ)64,65, that may be coupled with gatemons66 or superconductors67. Similar to semiconductor spin qubits, the use of isotopically purified Ge23 may overcome the strong decoherence from the nuclear environment currently limiting progress with ASQs in III-V materials3,66.

All together, these findings represent a major step in the Ge quantum information route, aiming to co-integrate spin, superconducting, and topological systems for scalable and high-fidelity quantum information processing on a silicon wafer.

Methods

Ge/SiGe heterostructure growth

The Ge/SiGe heterostructure of this study is grown on a 100-mm n-type Si(001) substrate using an Epsilon 2000 (ASMI) reduced pressure chemical vapor deposition reactor. The layer sequence comprises a Si0.2Ge0.8 virtual substrate obtained by reverse grading, a 16 nm thick Ge quantum well, a 22 nm-thick Si0.2Ge0.8 barrier, and a thin sacrificial Si cap35. Detailed electrical characterisation of heterostructure field effect transistors from these heterostructures are presented in ref. 35.

Device fabrication

The fabrication of the devices presented in this paper entails the following steps. Wet etching of the sacrificial Si-cap in buffer oxide etch for 10 s. Deposition of the Pt contacts via e-gun evaporation of 15 nm of Pt at pressure of 3 × 10−6 mbar at the rate of 0.5 Å/s. Rapid thermal anneal of Pt contacts at 400 ∘C for 15 min in a halogen lamps heated chamber in argon atmosphere. Atomic layer deposition of 10 nm of Al2O3 at 300 ∘C. Deposition of the first gate layer via e-gun evaporation of 3 nm of Ti and 17 nm of Pd. For the devices with a second gate layer the last two steps are repeated, 27 nm of Pd are deposited for the second gate layer to guarantee film continuity where overlapping with first gate layer.

Transport measurements

Electrical transport measurements of the SNS-QPC, NS-QPC, and SQUID devices are carried out in a dry dilution refrigerators at a base temperature of 15 mK, corresponding to an electron temperature of ≈25 mK measured with a metallic N-S tunnel junction thermometer. This refrigerator is equipped with a 3-axis vector magnet. Measurements of the junctions array are carried out in a wet dilution refrigerator with base temperature of 50 mK and z-axis magnet.

Measurements are performed using a standard 4-terminals low-frequency lock-in technique at the frequency of 17 Hz. Voltage bias measurements are performed with an excitation voltage VAC < 4 μV. By measuring in a four-terminal setup, additional data processing to subtract series resistances of various circuit components is avoided. For the measurements in Fig. 2b−d and Fig. 5b the (maximum) gate voltage is tuned to be just below the threshold for hysteresis, caused by trapped charges in the surface states at the semiconductor/dielectric. In these electrostatic conditions the valence band edge at the semiconductor/dielectric interface and the Fermi level align and the density in the buried channel is expected to approach a saturation density of about 6 × 1011 cm−2 35.

Simulations and fitting of MARs

The experimentally measured conductance Gexp(V) of an SNS junction is assumed to be superposition of N single-mode contributions47:

where \({G}^{({\tau }_{i},{{\Delta }})}\) is the simulated conductance for the Ni modes with transparency τi. We allow for M different transparencies, but all Ni modes have the same superconducting gap Δ. The simulations of conductance were implemented in Python using a modified version of the code presented in ref. 68.

The theoretically computed conductance Gtheory(V) is fitted to Gexp(V) using a nonlinear least-squares procedure: \(\chi =\int{[{G}_{exp}(V)-{G}_{theory}(V)]}^{2}dV\) is minimised for the fitting parameters Δ, Ni, τi with i ∈ 1, . . . , M. The fitting is performed for increasing M, provided that all Ni and τi are nonzero. We note that we assume a coherent 1D system. When the MAR contribution is significant, this assumption leads to an overestimation of the sharpness and amplitude of the peaks. Nonetheless, overall we find a good agreement between the data and the model.

Data availability

All data included in this work are openly available at 4TU research data repository https://doi.org/10.4121/19940174. All other relevant data are available from the corresponding author upon reasonable request.

References

Lutchyn, R. M. et al. Majorana zero modes in superconductor-semiconductor heterostructures. Nat. Rev. Mater. 3, 52–68 (2018).

Flensberg, K., von Oppen, F. & Stern, A. Engineered platforms for topological superconductivity and Majorana zero modes. Nat. Rev. Mater. 6, 944–958 (2021).

Hays, M. et al. Coherent manipulation of an Andreev spin qubit. Science 373, 430–433 (2021).

Casparis, L. et al. Superconducting gatemon qubit based on a proximitized two-dimensional electron gas. Nat. Nanotechnol. 13, 915–919 (2018).

Choi, M.-S., Bruder, C. & Loss, D. Spin-dependent Josephson current through double quantum dots and measurement of entangled electron states. Phys. Rev. B 62, 13569–13572 (2000).

Leijnse, M. & Flensberg, K. Quantum information transfer between topological and spin qubit systems. Phys. Rev. Letters 107, 210502 (2011).

Leijnse, M. & Flensberg, K. Hybrid topological-spin qubit systems for two-qubit-spin gates. Phys. Rev. B 86, 104511 (2012).

Hoffman, S., Schrade, C., Klinovaja, J. & Loss, D. Universal quantum computation with hybrid spin-Majorana qubits. Phys. Rev. B 94, 045316 (2016).

Leijnse, M. & Flensberg, K. Coupling spin qubits via superconductors. Phys. Rev. Letters 111, 060501 (2013).

Kitaev, A. Y. Unpaired Majorana fermions in quantum wires. Phys. Uspekhi 44, 131–136 (2001).

Chang, W. et al. Hard gap in epitaxial semiconductor-superconductor nanowires. Nat. Nanotechnol. 10, 232–236 (2015).

Kjaergaard, M. et al. Quantized conductance doubling and hard gap in a two-dimensional semiconductor-superconductor heterostructure. Nat. Commun. 7, 1–6 (2016).

Fornieri, A. et al. Evidence of topological superconductivity in planar Josephson junctions. Nature 569, 89–92 (2019).

Aghaee, M. et al. InAs-Al hybrid devices passing the topological gap protocol. Preprint at http://arxiv.org/abs/2207.02472 (2022).

Dvir, T. et al. Realization of a minimal Kitaev chain in coupled quantum dots. Nature 614, 445–450 (2023).

Cywiński, L., Witzel, W. M. & Das Sarma, S. Electron spin dephasing due to hyperfine interactions with a nuclear spin bath. Phys. Rev. Letters 102, 1–4 (2009).

Stano, P. & Loss, D. Review of performance metrics of spin qubits in gated semiconducting nanostructures. Nat. Rev. Phys. 4, 672–688 (2022).

Scappucci, G. et al. The germanium quantum information route. Nat. Rev. Mater. 6, 926–943 (2020).

Watzinger, H. et al. A germanium hole spin qubit. Nat. Commun. 9, 1–6 (2018).

Hendrickx, N. W., Franke, D. P., Sammak, A., Scappucci, G. & Veldhorst, M. Fast two-qubit logic with holes in germanium. Nature 577, 487–491 (2020).

Jirovec, D. et al. A singlet-triplet hole spin qubit in planar Ge. Nat. Mater. 20, 1106–1112 (2021).

Prechtel, J. H. et al. Decoupling a hole spin qubit from the nuclear spins. Nat. Mater. 15, 981–986 (2016).

Itoh, K. M. & Watanabe, H. Isotope engineering of silicon and diamond for quantum computing and sensing applications. MRS Commun. 4, 143–157 (2014).

Lodari, M. et al. Light effective hole mass in undoped Ge/SiGe quantum wells. Phys. Rev. B 100, 041304(R) (2019).

Lodari, M. et al. Lightly strained germanium quantum wells with hole mobility exceeding one million. Appl. Phys. Letters 120, 122104 (2022).

Hendrickx, N. W. et al. A four-qubit germanium quantum processor. Nature 591, 580–585 (2021).

Borsoi, F. et al. Shared control of a 16 semiconductor quantum dot crossbar array. Preprint at https://doi.org/10.48550/arXiv.2209.06609 (2022).

Dimoulas, A., Tsipas, P., Sotiropoulos, A. & Evangelou, E. K. Fermi-level pinning and charge neutrality level in germanium. Appl. Phys. Letters 89, 252110 (2006).

Hendrickx, N. W. et al. Gate-controlled quantum dots and superconductivity in planar germanium. Nat. Commun. 9, 2835 (2018).

Hendrickx, N. W. et al. Ballistic supercurrent discretization and micrometer-long Josephson coupling in germanium. Phys. Rev. B 99, 7–9 (2019).

Ridderbos, J. et al. Hard superconducting gap and diffusion-induced superconductors in Ge-Si nanowires. Nano Letters 20, 122–130 (2020).

Vigneau, F. et al. Germanium quantum-well Josephson field-effect transistors and interferometers. Nano Letters 19, 1023–1027 (2019).

Aggarwal, K. et al. Enhancement of proximity-induced superconductivity in a planar Ge hole gas. Phys. Rev. Res. 3, 022005 (2021).

Kittl, J. A. et al. Silicides and germanides for nano-CMOS applications. Mater. Sci. Eng. B 154, 144–154 (2008).

Sammak, A. et al. Shallow and undoped germanium quantum wells: a playground for spin and hybrid quantum technology. Adv. Funct. Mater. 29, 1807613 (2019).

Ahn, S., Pan, H., Woods, B., Stanescu, T. D. & Sarma, S. D. Estimating disorder and its adverse effects in semiconductor Majorana nanowires. Phys. Rev. Mater. 5, 124602 (2021).

Vandersypen, L. M. K. et al. Interfacing spin qubits in quantum dots and donors - hot, dense, and coherent. npj Quantum Inf 3, 34 https://doi.org/10.1038/s41534-017-0038-y (2017).

Gaudet, S., Detavernier, C., Kellock, A. J., Desjardins, P. & Lavoie, C. Thin film reaction of transition metals with germanium. J. Vacuum Sci. Technol. A Vacuum, Surf. Films 24, 474–485 (2006).

Raub, C. J., Zachariasen, W. H., Geballe, T. H. & Matthias, B. T. Superconductivity of some new Pt-metal compounds. J. Phys. Chem. Solids 24, 1093–1100 (1963).

Shabani, J. et al. Two-dimensional epitaxial superconductor-semiconductor heterostructures: a platform for topological superconducting networks. Phys. Rev. B 93, 1–6 (2016).

Alptekin, E., Kirkpatrick, C. J., Misra, V. & Ozturk, M. C. Platinum germanosilicide contacts formed on strained and relaxed Si1-xGex layers. IEEE Transact. Electron Devices 56, 1220–1227 (2009).

Irie, H., Harada, Y., Sugiyama, H. & Akazaki, T. Josephson coupling through one-dimensional ballistic channel in semiconductor-superconductor hybrid quantum point contacts. Phys. Rev. B 89, 1–6 (2014).

Ambegaokar, V. & Baratoff, A. Tunneling between superconductors. Phys. Rev. Letters 10, 486 (1963).

Heedt, S. et al. Shadow-wall lithography of ballistic superconductor-semiconductor quantum devices. Nat. Commun. 12, 1–9 (2021).

Tinkham, M. Introduction to Superconductivity, 2nd ed edn. Dover Publications, Mineola, N.Y. (2004). OCLC: 853663851

Octavio, M., Tinkham, M., Blonder, G. E. & Klapwijk, T. M. Subharmonic energy-gap structure in superconducting constrictions. Phys. Rev. B 27, 6739–6746 (1983).

Kjaergaard, M. et al. Transparent semiconductor-superconductor interface and induced gap in an epitaxial heterostructure Josephson junction. Phys. Rev. Appl. 7, 034029 (2017).

Averin, D. & Bardas, A. ac Josephson effect in a single quantum channel. Phys. Rev. Letters 75, 1831–1834 (1995).

Borsoi, F. et al. Single shot fabrication of semiconducting-superconducting nanowire devices. Adv. Funct. Mater. 31, 2102388 (2021).

Fornieri, A. et al. Evidence of topological superconductivity in planar Josephson junctions. Nature 569, 89–92 (2019).

Nilsson, H. A., Samuelsson, P., Caroff, P. & Xu, H. Q. Supercurrent and multiple andreev reflections in an InSb nanowire Josephson junction. Nano Lett 12, 233 (2012).

van Loo, N. et al. Electrostatic control of the proximity effect in the bulk of semiconductor-superconductor hybrids. Preprint at https://doi.org/10.48550/arXiv.2211.06709 (2022).

De Moor, M. W. A. et al. Electric field tunable superconductor-semiconductor coupling in Majorana nanowires. New J. Phys. 20, 103049 (2018).

Blonder, G. E., Tinkham, M. & Klapwijk, T. M. Transition from metallic to tunneling regimes in superconducting microconstrictions: excess current, charge imbalance, and supercurrent conversion. Phys. Rev. B 25, 4515–4532 (1982).

Pientka, F. et al. Topological superconductivity in a planar Josephson junction. Phys. Rev. X 7, 1–17 (2017).

Ren, H. et al. Topological superconductivity in a phase-controlled Josephson junction. Nature 569, 93–98 (2019).

Luethi, M., Laubscher, K., Bosco, S., Loss, D. & Klinovaja, J. Planar Josephson junctions in germanium: effect of cubic spin-orbit interaction. Phys. Rev. B 107, 035435 (2023).

Poccia, N. et al. Critical behavior at a dynamic vortex insulator-to-metal transition. Science 349, 1202–1205 (2015).

Bøttcher, C. G. L. et al. Superconducting, insulating and anomalous metallic regimes in a gated two-dimensional semiconductor-superconductor array. Nat. Phy. 14, 1138–1144 (2018).

Matthias, B. T., Geballe, T. H. & Compton, V. B. Superconductivity. Rev. Mod. Phys 35, 1–22 (1963).

Hell, M., Leijnse, M. & Flensberg, K. Two-dimensional platform for networks of Majorana bound states. Phys. Rev. Letters 118, 107701 (2017).

Pientka, F. et al. Topological superconductivity in a planar Josephson junction. Phys. Rev. X 7, 021032 (2017).

Burkard, G., Gullans, M. J., Mi, X. & Petta, J. R. Superconductor-semiconductor hybrid-circuit quantum electrodynamics. Nat. Rev. Phys. 2, 129–140 (2020).

Chtchelkatchev, N. M. & Nazarov, Y. V. Andreev quantum dots for spin manipulation. Phys. Rev. Letters 90, 226806 (2003).

Padurariu, C. & Nazarov, Y. V. Theoretical proposal for superconducting spin qubits. Phys. Rev. B 81, 144519 (2010).

Pita-Vidal, M. et al. Direct manipulation of a superconducting spin qubit strongly coupled to a transmon qubit. Preprint at https://doi.org/10.48550/arXiv.2208.10094 (2022).

Spethmann, M., Zhang, X.-P., Klinovaja, J. & Loss, D. Coupled superconducting spin qubits with spin-orbit interaction. Phys. Rev. B 106, 115411 (2022).

Nowak, M. P., Wimmer, M. & Akhmerov, A. R. Supercurrent carried by nonequilibrium quasiparticles in a multiterminal Josephson junction. Phys. Rev. B 99, 075416 (2019).

Acknowledgements

We thank L. Kouwenhoven for fruitful discussions and S.V. Amitonov for nanofabrication support. A.T. and G.S acknowledges support through a projectruimte associated with the Netherlands Organization of Scientific Research (NWO). M. V. acknowledges support through an ERC Starting Grant (Grant agreement No. 850641).ICN2 acknowledges funding from Generalitat de Catalunya 2021SGR327. ICN2 is supported by the Severo Ochoa program from Spanish MCIN/AEI (Grant No. CEX2021-001214-S) and is funded by the CERCA Programme/Generalitat de Catalunya and ERDF funds from EU. Part of the present work has been performed in the framework of Universitat Autònoma de Barcelona Materials Science PhD program. Authors acknowledge the use of instrumentation as well as the technical advice provided by the National Facility ELECMI ICTS, node “Laboratorio de Microscopias Avanzadas” at University of Zaragoza. M.B. acknowledges support from SUR Generalitat de Catalunya and the EU Social Fund; project ref. 2020 FI 00103. We acknowledge support from CSIC Interdisciplinary Thematic Platform (PTI+) on Quantum Technologies (PTI-QTEP+).

Author information

Authors and Affiliations

Contributions

A.S. grew the Ge/SiGe heterostructures. A.T. fabricated the devices. C.N.B., M.B, S.M., J.A. performed transmission electron microscopy characterisation. A.T. with C.B. measured Josephson junction devices, SNS-QPCs, and 2D arrays in wet dilution refrigerators, analysed the data and performed numerical simulation of the MARs processes. V. L. and A.T. measured SNS-QPC, NS-QPC devices and SQUIDs in dry dilution refrigerators and analyzed the data with the supervision of J.W. and input from F.B. and M.V. A.T wrote the manuscript with input from all authors. G.S. conceived and supervised the project.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Materials thanks the anonymous reviewers for their contribution to the peer review of this work. Primary Handling Editor: Aldo Isidori. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tosato, A., Levajac, V., Wang, JY. et al. Hard superconducting gap in germanium. Commun Mater 4, 23 (2023). https://doi.org/10.1038/s43246-023-00351-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s43246-023-00351-w

This article is cited by

-

Shared control of a 16 semiconductor quantum dot crossbar array

Nature Nanotechnology (2024)

-

Parity-conserving Cooper-pair transport and ideal superconducting diode in planar germanium

Nature Communications (2024)

-

Direct manipulation of a superconducting spin qubit strongly coupled to a transmon qubit

Nature Physics (2023)

-

Hole-type superconducting gatemon qubit based on Ge/Si core/shell nanowires

npj Quantum Information (2023)