Abstract

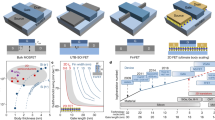

Two-dimensional transition metal dichalcogenides could potentially be used to create transistors that are scaled beyond the capabilities of silicon devices. However, despite progress on the single-transistor level, the development of high-frequency integrated circuits remains a challenge and the operating frequency of integrated circuits based on transition metal dichalcogenides has so far been limited to the megahertz regime; this is well below the silicon complementary metal–oxide–semiconductor technology, as well as emerging technologies such as carbon nanotubes. Here we report two-dimensional semiconductor integrated circuits—five-stage ring oscillators—that operate in the gigahertz regime (up to 2.65 GHz) and are developed using a design-technology co-optimization process. The circuits are based on monolayer molybdenum disulfide field-effect transistors that have an air-gap structure, which leads to doping-free ohmic contacts and low parasitic capacitance. Technology computer-aided design simulations also suggest that our air-gap structure can potentially be scaled to the 1 nm technology node and could reach the targets set out in the IEEE International Roadmap for Devices and Systems for 2031.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding authors on reasonable request.

References

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Wang, S. et al. Two-dimensional devices and integration towards the silicon lines. Nat. Mater. 21, 1225–1239 (2022).

Sathaiya, D. et al. Comprehensive physics based TCAD model for 2D MX2 channel transistors. In 2022 IEEE International Electron Devices Meeting 28.4.1–28.4.4 (IEEE, 2022).

Ahmed, Z. et al. Introducing 2D-FETs in device scaling roadmap using DTCO. In 2020 IEEE International Electron Devices Meeting 22.5.1–22.5.4 (IEEE, 2020).

Shen, Y., Tian, H. & Ren, T. Simulation of MoS2 stacked nanosheet field effect transistor. J. Semicond. 43, 082002 (2022).

International Roadmap for Devices and Systems (IRDS, 2021); https://irds.ieee.org/

Polyushkin, D. K. et al. Analogue two-dimensional semiconductor electronics. Nat. Electron. 3, 486–491 (2020).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Brien, K. P. O. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In 2021 IEEE International Electron Devices Meeting 7.1.1–7.1.4 (IEEE, 2021).

Xiong, X. et al. Top-gate CVD WSe2 pFETs with record-high Id~594 μA/μm, Gm~244 μS/μm and WSe2/MoS2 CFET based half-adder circuit using monolithic 3D integration. In 2022 IEEE International Electron Devices Meeting 20.6.1–20.6.4 (IEEE, 2022).

Chung, Y.-Y. et al. First demonstration of GAA monolayer-MoS2 nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm gate length. In 2022 IEEE International Electron Devices Meeting 34.5.1–34.5.4 (IEEE, 2022).

Smets, Q. et al. Scaling of double-gated WS2 FETs to sub-5nm physical gate length fabricated in a 300mm FAB. In 2021 IEEE International Electron Devices Meeting 34.2.1–34.2.4 (IEEE, 2021).

Hao, Y. et al. Recent progress of integrated circuits and optoelectronic chips. Sci. China Inf. Sci. 64, 201401 (2021).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Su, S. K. et al. Perspective on low-dimensional channel materials for extremely scaled CMOS. In 2022 IEEE Symposium on VLSI Technology and Circuits 403–404 (IEEE, 2022).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Chen, X. et al. Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning. Nat. Commun. 12, 5953 (2021).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Zhong, D. et al. Gigahertz integrated circuits based on carbon nanotube films. Nat. Electron. 1, 40–45 (2017).

Liu, L. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 368, 850–856 (2020).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42nm contact pitch and 250µA/µm drain current. In 2019 IEEE International Electron Devices Meeting 23.2.1–23.2.4 (IEEE, 2019).

Lanza, M., Smets, Q., Huyghebaert, C. & Li, L. J. Yield, variability, reliability, and stability of two-dimensional materials based solid-state electronic devices. Nat. Commun. 11, 5689 (2020).

Bazizi, E. M. et al. Materials to systems co-optimization platform for rapid technology development targeting future generation CMOS nodes. IEEE Trans. Electron Devices 68, 5358–5363 (2021).

Chen, L. et al. Gigahertz integrated circuits based on complementary black phosphorus transistors. Adv. Electron. Mater. 4, 1800274 (2018).

Guerriero, E. et al. Gigahertz integrated graphene ring oscillators. ACS Nano 7, 5588–5594 (2013).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948–14953 (2017).

Togo, M., Tanabe, A., Furukawa, A., Tokunaga, K. & Hashimoto, T. A gate-side air-gap structure (GAS) to reduce the parasitic capacitance in MOSFETs. In 1996 IEEE Symposium on VLSI Technology and Circuits 38–39 (IEEE, 1996).

Park, J. & Hu, C. Air spacer MOSFET technology for 20nm node and beyond. In 2008 9th International Conference on Solid-State and Integrated-Circuit Technology 53–56 (IEEE, 2008).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In 2021 IEEE International Electron Devices Meeting 7.2.1–7.2.4 (IEEE, 2021).

Wang, J. et al. Integration of high-κ oxide on MoS2 by using ozone pretreatment for high-performance MoS2 top-gated transistor with thickness-dependent carrier scattering investigation. Small 11, 5932–5938 (2015).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Sanne, A. et al. Radio frequency transistors and circuits based on CVD MoS2. Nano Lett. 15, 5039–5045 (2015).

Xu, K. et al. Sub-10 nm nanopattern architecture for 2D material field-effect transistors. Nano Lett. 17, 1065–1070 (2017).

Yang, L., Lee, R. T. P., Rao, S. S. P., Tsai, W. & Ye, P. D. 10 nm nominal channel length MoS2 FETs with EOT 2.5 nm and 0.52 mA/µm drain current. In 2015 73rd Annual Device Research Conference 237–238 (IEEE, 2015).

Wu, X. et al. Dual gate synthetic MoS2 MOSFETs with 4.56µF/cm2 channel capacitance, 320µS/µm Gm and 420 µA/µm Id at 1V Vd/100nm Lg. In 2021 IEEE International Electron Devices Meeting 7.4.1–7.4.4 (IEEE, 2021).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Zou, X. et al. Interface engineering for high-performance top-gated MoS2 field-effect transistors. Adv. Mater. 26, 6255–6261 (2014).

Waltl, M. et al. Perspective of 2D integrated electronic circuits: scientific pipe dream or disruptive technology? Adv. Mater. 34, e2201082 (2022).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Smithe, K. K. H., Suryavanshi, S. V., Munoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Xu, H. et al. High-performance wafer-scale MoS2 transistors toward practical application. Small 14, e1803465 (2018).

Yu, L. et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Cheng, K. et al. Improved air spacer co-integrated with self-aligned contact (SAC) and contact over active gate (COAG) for highly scaled CMOS technology. In 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020).

Frougier, J., Xie, R., Cheng, K. & Park, C. Gate-all-around field effect transistors with robust inner spacers and methods. US patent 10,692,991 (2021).

Jiang, J., Xu, L., Qiu, C. & Peng, L. M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

English, C. D., Smithe, K. K., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS2 transistors with self-aligned 10 nm top gates. In 2016 IEEE International Electron Devices Meeting 5.6.1–5.6.4 (IEEE, 2016).

Verreck, D. et al. The role of nonidealities in the scaling of MoS2 FETs. IEEE Trans. Electron Devices 65, 4635–4640 (2018).

Lin, D. et al. Dual gate synthetic WS2 MOSFETs with 120μS/μm Gm 2.7μF/cm2 capacitance and ambipolar channel. In 2020 IEEE International Electron Devices Meeting 3.6.1–3.6.4 (IEEE, 2020).

Sun, J. et al. ZnO thin-film transistor ring oscillators with 31-ns propagation delay. IEEE Electron Device Lett. 29, 721–723 (2008).

Myny, K. & Steudel, S. Flexible thin-film NFC transponder chip exhibiting data rates compatible to ISO NFC standards using self-aligned metal-oxide TFTs. In 2016 IEEE International Solid-State Circuits Conference 298–299 (IEEE, 2016).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Li, S., Gu, C., Li, X., Huang, R. & Wu, Y. 10-nm channel length indium-tin-oxide transistors with Ion = 1860 μA/μm, Gm = 1050 μS/μm at Vds = 1 V with BEOL compatibility. In 2020 IEEE International Electron Devices Meeting 40.5.1–40.5.4 (IEEE, 2020).

Han, S. J. et al. High-speed logic integrated circuits with solution-processed self-assembled carbon nanotubes. Nat. Nanotechnol. 12, 861–865 (2017).

Chen, Z. et al. An integrated logic circuit assembled on a single carbon nanotube. Science 311, 1735–1735 (2006).

Acknowledgements

This work was supported by the National Key R&D Program of China (grant nos. 2022YFB4400100, 2021YFA0715600, 2021YFA1202903, 2022YFA1402504 and 2023YFF1500500); the National Natural Science Foundation of China (grant nos. T2221003, T2322014, 61927808, 62204113, 62204124, 62304101, 62322408 and 61861166001); the National Natural Science Fund for Excellent Young Scholars (Overseas); the Leading-Edge Technology Program of Jiangsu Natural Science Foundation (grant no. BK20202005); the China Postdoctoral Science Foundation (grant nos. 2022M711549 and 2022T15036); Jiangsu Funding Program for Excellent Postdoctoral Talent (grant no. 20220ZB63); the Natural Science Foundation of Jiangsu Province (grant no. BK20220773); Jiangsu Province Key R&D Program (grant no. BE2023009-3); the Excellent Youth Natural Science Foundation of Jiangsu Province (grant no. BK20200060); the Strategic Priority Research Program of the Chinese Academy of Sciences (grant no. XDB30000000); the Key Laboratory of Advanced Photonic and Electronic Materials, Collaborative Innovation Center of Solid-State Lighting and Energy-Saving Electronics; and the Fundamental Research Funds for the Central Universities, China. X.W. acknowledges the support by the New Cornerstone Science Foundation through the XPLORER PRIZE. W. L. acknowledges the support from Xiaomi foundation. The funders had no role in the study design, data collection and analysis, decision to publish or preparation of the manuscript.

Author information

Authors and Affiliations

Contributions

X.W. conceived and supervised the project with H.Q., D.F., W.L., Y.X., Y.S., M.L. and X.T. contributed to the transistor fabrication, measurements and data analysis. S.G., F.H. and P.W. performed the transmission electron microscopy and data analysis. L.L. and T.L. performed the CVD growth of MoS2. H.Q., D.F., and X.W. co-wrote the manuscript with input from other authors. All authors contributed to discussions.

Corresponding authors

Ethics declarations

Competing interests

The authors declare the following competing interest: China patent application no. 2023101731215.

Peer review

Peer review information

Nature Electronics thanks Jiadi Zhu, Zhiyong Zhang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–16, Notes 1–3 and Tables 1 and 2.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Fan, D., Li, W., Qiu, H. et al. Two-dimensional semiconductor integrated circuits operating at gigahertz frequencies. Nat Electron 6, 879–887 (2023). https://doi.org/10.1038/s41928-023-01052-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-01052-5

This article is cited by

-

Design–technology co-optimization for 2D electronics

Nature Electronics (2023)