Abstract

Cryogenic data storage technology is of use in superconducting single-flux quantum electronics and quantum computing. However, the lack of compatible cryogenic memory technology, which can operate at temperatures of 4 K (or lower), hinders the development of practical and scalable systems. Here we examine the development of cryogenic memory technologies. We explore three areas of memory technology: cryogenic non-superconducting memories (including those based on charge and resistance), superconducting memories (including those based on Josephson junctions, superconducting quantum interference devices and superconducting memristors) and hybrid memories (which use both superconducting and non-superconducting technologies). We consider the key challenges involved in the integration of such memories with single-flux quantum circuits and quantum computers. We also provide a comparison of the capabilities of the different technologies in the context of the requirements of superconducting electronics and quantum computing.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper are available from the corresponding author on reasonable request.

References

Mujtaba, H. Cerebras wafer scale engine is a massive AI chip featuring 2.6 trillion transistors & nearly 1 million cores. wccftech https://wccftech.com/cerebras-unveils-7nm-wafe-scale-engine-2-largest-ai-chip-ever-built/ (2021).

Masanet, E., Shehabi, A., Lei, N., Smith, S. & Koomey, J. Recalibrating global data center energy-use estimates. Science 367, 984–986 (2020).

Likharev, K. K. & Lukens, J. Dynamics of Josephson junctions and circuits. Phys. Today 41, 122 (1988).

Mukhanov, O. A. et al. Superconductor digital-RF receiver systems. IEICE Trans. Electron. 91, 306–317 (2008).

Vernik, I. V. et al. Cryocooled wideband digital channelizing radio-frequency receiver based on low-pass ADC. Supercond. Sci. Technol. 20, S323 (2007).

Superconducting Technology Assessment (National Security Agency Office of Corporate Assessments, 2005).

Hastings, M. B., Wecker, D., Bauer, B. & Troyer, M. Improving quantum algorithms for quantum chemistry. Quantum Inf. Comput. 15, 1–21 (2015).

Shor, P. W. Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer. SIAM J. Comput. 26, 1484–1509 (1997).

Feynman, R. P. Quantum mechanical computers. Found. Phys. 16, 507–531 (1986).

Tannu, S. S., Carmean, D. M. & Qureshi, M. K. Cryogenic-DRAM based memory system for scalable quantum computers: a feasibility study. ACM Int. Conf. Proc. Ser. Oct. 2017, 189–195 (2017). This paper discusses the importance of cryogenic memory for scalable quantum computers and studies the feasibility of using DRAMs as a cryogenic memory candidate.

Filippov, T. V. et al. 20 GHz operation of an asynchronous wave-pipelined RSFQ arithmetic-logic unit. Phys. Proc. 36, 59–65 (2012).

Ware, F. et al. Do superconducting processors really need cryogenic memories? The case for cold DRAM. ACM Int. Conf. Proc. Ser. Oct. 2017, 183–188 (2017).

Patra, B. et al. Cryo-CMOS circuits and systems for quantum computing applications. IEEE J. Solid -State Circuits 53, 309–321 (2018).

Veldhorst, M. et al. An addressable quantum dot qubit with fault-tolerant control-fidelity. Nat. Nanotechnol. 9, 981–985 (2014).

Veldhorst, M. et al. A two-qubit logic gate in silicon. Nature 526, 410–414 (2015).

Chow, J. M. et al. Implementing a strand of a scalable fault-tolerant quantum computing fabric. Nat. Commun. 5, 4015 (2014).

Dicarlo, L. et al. Demonstration of two-qubit algorithms with a superconducting quantum processor. Nature 460, 240–244 (2009).

Kawakami, E. et al. Electrical control of a long-lived spin qubit in a Si/SiGe quantum dot. Nat. Nanotechnol. 9, 666–670 (2014).

Likharev, K. K. Superconductor digital electronics. Physica C 482, 6–18 (2012).

Hornibrook, J. M. et al. Cryogenic control architecture for large-scale quantum computing. Phys. Rev. Appl. 3, 024010 (2015).

Tannu, S. S., Myers, Z. A., Nair, P. J., Carmean, D. M. & Qureshi, M. K. Taming the instruction bandwidth of quantum computers via hardware-managed error correction. In Proc. 50th Annual IEEE/ACM International Symposium on Microarchitecture 679–691 (ACM, 2017); https://doi.org/10.1145/3123939

Tuckerman, D. B. et al. Flexible superconducting Nb transmission lines on thin film polyimide for quantum computing applications. Supercond. Sci. Technol. 29, 084007 (2016).

Yoshikawa, N. et al. Characterization of 4 K CMOS devices and circuits for hybrid Josephson-CMOS systems. IEEE Trans. Appl. Supercond. 15, 267–271 (2005).

Henkels, W. H. et al. A low temperature 12 ns DRAM. In International Symposium on VLSI Technology, Systems and Applications 32–35 (IEEE, 1989); https://doi.org/10.1109/VTSA.1989.68576. This paper characterized room-temperature CMOS memory at cryogenic temperatures.

Henkels, W. H. et al. Low temperature SER and noise in a high speed DRAM. In Proc. Workshop on Low Temperature Semiconductor Electronics 5–9 (IEEE, 1989); https://doi.org/10.1109/ltse.1989.50171

Mohler, R. L. et al. A 4-Mb low-temperature DRAM. IEEE J. Solid State Circuits 26, 1519–1529 (1991).

Vogelsang, T. Understanding the energy consumption of dynamic random access memories. In Proc. 43rd Annual IEEE/ACM International Symposium on Microarchitecture 363–374 (IEEE, 2010); https://doi.org/10.1109/MICRO.2010.42

Mitchell, C., McCartney, C. L., Hunt, M. & Ho, F. D. Characteristics of a three-transistor DRAM circuit utilizing a ferroelectric transistor. Integr. Ferroelectr. 157, 31–38 (2014).

Tack, M. R., Gao, M., Claeys, C. L. & Declerck, G. J. The multistable charge-controlled memory effect in SOI MOS transistors at low temperatures. IEEE Trans. Electron Devices 37, 1373–1382 (1990).

Morishita, F. et al. Leakage mechanism due to floating body and countermeasure on dynamic retention mode of SOI-DRAM. Symposium on VLSI Technology, Digest of Technical Papers 141–142 (IEEE, 1995); https://doi.org/10.1109/vlsit.1995.520897

Ohsawa, T. et al. A memory using one-transistor gain cell on SOI(FBC) with performance suitable for embedded DRAM’s. In Symposium on VLSI Circuits, Digest of Technical Papers 93–96 (IEEE, 2003); https://doi.org/10.1109/vlsic.2003.1221171

Collaert, N. et al. A low-voltage biasing scheme for aggressively scaled bulk FinFET 1T-DRAM featuring 10s retention at 85 °C. In Symposium on VLSI Technology, Digest of Technical Papers 161–162 (IEEE, 2010); https://doi.org/10.1109/VLSIT.2010.5556211

Park, K. H., Park, C. M., Kong, S. H. & Lee, J. H. Novel double-gate 1T-DRAM cell using nonvolatile memory functionality for high-performance and highly scalable embedded DRAMs. IEEE Trans. Electron Devices 57, 614–619 (2010).

Bae, J. H. et al. Characterization of a capacitorless DRAM cell for cryogenic memory applications. IEEE Electron Device Lett. 40, 1614–1617 (2019).

Song, Y. J., Jeong, G., Baek, I. G. & Choi, J. What lies ahead for resistance-based memory technologies? Computer 46, 30–36 (2013).

Lee, H. Y. et al. Evidence and solution of over-RESET problem for HfOx based resistive memory with sub-ns switching speed and high endurance. In International Electron Devices Meeting 19.7.1–19.7.4 (IEEE, 2010); https://doi.org/10.1109/IEDM.2010.5703395

Govoreanu, B. et al. 10×10nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. In International Electron Devices Meeting 31.6.1–31.6.4 (IEEE, 2011); https://doi.org/10.1109/IEDM.2011.6131652

Ielmini, D. et al. Scaling analysis of submicrometer nickel-oxide-based resistive switching memory devices. J. Appl. Phys. 109, 034506 (2011).

Kügeler, C., Zhang, J., Hoffmann-Eifert, S., Kim, S. K. & Waser, R. Nanostructured resistive memory cells based on 8-nm-thin TiO2 films deposited by atomic layer deposition. J. Vac. Sci. Technol. B 29, 01AD01 (2011).

Walczyk, C. et al. On the role of Ti adlayers for resistive switching in HfO2-based metal–insulator–metal structures: top versus bottom electrode integration. J. Vac. Sci. Technol. B 29, 01AD02 (2011).

Hirose, S., Nakayama, A., Niimi, H., Kageyama, K. & Takagi, H. Resistance switching and retention behaviors in polycrystalline La-doped SrTiO3 ceramics chip devices. J. Appl. Phys. 104, 053712 (2008).

Yao, J., Sun, Z., Zhong, L., Natelson, D. & Tour, J. M. Resistive switches and memories from silicon oxide. Nano Lett. 10, 4105–4110 (2010).

Lörtscher, E., Ciszek, J. W., Tour, J. & Riel, H. Reversible and controllable switching of a single-molecule junction. Small 2, 973–977 (2006).

Walczyk, C. et al. Impact of temperature on the resistive switching behavior of embedded HfO2-based RRAM devices. IEEE Trans. Electron Devices 58, 3124–3131 (2011).

Ahn, C. et al. Temperature-dependent studies of the electrical properties and the conduction mechanism of HfOx-based RRAM. In Proc. Technical Program—2014 International Symposium on VLSI Technology, Systems and Application 1–2 (IEEE, 2014); https://doi.org/10.1109/VLSI-TSA.2014.6839685

Shang, J. et al. Thermally stable transparent resistive random access memory based on all-oxide heterostructures. Adv. Funct. Mater. 24, 2171–2179 (2014).

Fang, R., Chen, W., Gao, L., Yu, W. & Yu, S. Low-temperature characteristics of HfO. IEEE Electron Device Lett. 36, 567–569 (2015).

Blonkowski, S. & Cabout, T. Bipolar resistive switching from liquid helium to room temperature. J. Phys. D 48, 345101 (2015).

Takashima, D. Overview of FeRAMs: trends and perspectives. In Proc. 11th Annual Non-Volatile Memory Technology Symposium 36–41 (IEEE, 2011); https://doi.org/10.1109/NVMTS.2011.6137107

Trentzsch, M. et al. A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs. In International Electron Devices Meeting 11.5.1–11.5.4 (IEEE, 2017); https://doi.org/10.1109/IEDM.2016.7838397

Dünkel, S. et al. A FeFET based super-low-power ultra-fast embedded NVM technology for 22nm FDSOI and beyond. In International Electron Devices Meeting 19.7.1–19.7.4 (IEEE, 2018); https://doi.org/10.1109/IEDM.2017.8268425

Chatterjee, K. et al. Self-aligned, gate last, FDSOI, ferroelectric gate memory device with 5.5-nm Hf0.8Zr0.2O2, high endurance and breakdown recovery. IEEE Electron Device Lett. 38, 1379–1382 (2017).

Florent, K. et al. Vertical Ferroelectric HfO2 FET based on 3-D NAND architecture: towards dense low-power memory. In International Electron Devices Meeting 2.5.1–2.5.4 (IEEE, 2019); https://doi.org/10.1109/IEDM.2018.8614710

Rowley, S. E. et al. Ferroelectric quantum criticality. Nat. Phys. 10, 367–372 (2014).

Meng, X. J. et al. Temperature dependence of ferroelectric and dielectric properties of PbZr0.5Ti0.5O3 thin film based capacitors. Appl. Phys. Lett. 81, 4035–4037 (2002).

Wang, Z. et al. Cryogenic characterization of antiferroelectric zirconia down to 50 mK. In Device Research Conference 85–85 (IEEE, 2019); https://doi.org/10.1109/DRC46940.2019.9046475

Wang, Z. et al. Cryogenic characterization of a ferroelectric field-effect-transistor. Appl. Phys. Lett. 116, 042902 (2020).

Na, T., Kang, S. H. & Jung, S. O. STT-MRAM sensing: a review. IEEE Trans. Circuits Syst. II 68, 12–18 (2021).

Lang, L. et al. A low temperature functioning CoFeB/MgO-based perpendicular magnetic tunnel junction for cryogenic nonvolatile random access memory. Appl. Phys. Lett. 116, 022409 (2020).

Rowlands, G. E. et al. A cryogenic spin-torque memory element with precessional magnetization dynamics. Sci. Rep. 9, 803 (2019).

Yau, J. B., Fung, Y. K. K. & Gibson, G. W. Hybrid cryogenic memory cells for superconducting computing applications. In Proc. International Conference on Rebooting Computing 1–3 (IEEE, 2017); https://doi.org/10.1109/ICRC.2017.8123684

Alam, S., Hossain, M. S. & Aziz, A. A non-volatile cryogenic random-access memory based on the quantum anomalous Hall effect. Sci. Rep. 11, 7892 (2021). This paper developed a cryogenic memory system using topological properties of materials.

Serlin, M. et al. Intrinsic quantized anomalous Hall effect in a moiré heterostructure. Science 367, 900–903 (2020).

Ovshinsky, S. R. Reversible electrical switching phenomena in disordered structures. Phys. Rev. Lett. 21, 1450–1453 (1968).

Lai, S. Current status of the phase change memory and its future. In International Electron Devices Meeting 255–258 (IEEE, 2003); https://doi.org/10.1109/iedm.2003.1269271

Yi, H. T., Choi, T. & Cheong, S. W. Reversible colossal resistance switching in (La,Pr,Ca) MnO3: cryogenic nonvolatile memories. Appl. Phys. Lett. 95, 063509 (2009).

Tahara, S., Ishida, I., Ajisawa, Y. & Wada, Y. Experimental vortex transitional nondestructive read-out Josephson memory cell. J. Appl. Phys. 65, 851–856 (1989). This paper proposed and demonstrated a superconducting memory for cryogenic applications.

Tahara, S. et al. 4-Kbit Josephson nondestructive readout ram operated at 580 psec and 6.7 mW. IEEE Trans. Magn. 27, 2626–2633 (1991).

Nagasawa, S., Numata, H., Hashimoto, Y. & Tahara, S. High-frequency clock operation of Josephson 256-word × 16-bit rams. IEEE Trans. Appl. Supercond. 9, 3708–3713 (1999).

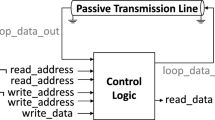

Nagasawa, S., Hinode, K., Satoh, T., Kitagawa, Y. & Hidaka, M. Design of all-dc-powered high-speed single flux quantum random access memory based on a pipeline structure for memory cell arrays. Supercond. Sci. Technol. 19, S325 (2006).

Nagasawa, S., Hashimoto, Y., Numata, H. & Tahara, S. A 380 ps, 9.5 mW Josephson 4-Kbit RAM operated at a high bit yield. IEEE Trans. Appl. Supercond. 5, 2447–2452 (1995).

Kirichenko, A. F., Mukhanov, O. A. & Brock, D. K. A single flux quantum cryogenic random access memory rapid single flux quantum digital electronics. In 7th International Superconductive Electronics Conference 124–127 (ISEC, 1999).

Kirichenko, A. F., Sarwana, S., Brock, D. K. & Radpavar, M. Pipelined DC-powered SFQ RAM. IEEE Trans. Appl. Supercond. 11, 537–540 (2001).

Yuh, P. F. A buffered nondestructive-readout Josephson memory cell with three gates. IEEE Trans. Magn. 27, 2876–2878 (1991).

Yuh, P. F. A 2-kbit superconducting memory chip. IEEE Trans. Appl. Supercond. 3, 3013–3021 (1993).

Polonsky, S. V., Kirichenko, A. F., Semenov, V. K. & Likharev, K. K. Rapid single flux quantum random access memory. IEEE Trans. Appl. Supercond. 5, 3000–3005 (1995).

Alam, S., Jahangir, M. A. & Aziz, A. A compact model for superconductor–insulator–superconductor (SIS) Josephson junctions. IEEE Electron Device Lett. 41, 1249–1252 (2020).

Polyakov, Y., Narayana, S. & Semenov, V. K. Flux trapping in superconducting circuits. IEEE Trans. Appl. Supercond. 17, 520–525 (2007).

Narayana, S., Polyakov, Y. A. & Semenov, V. K. Evaluation of flux trapping in superconducting circuits. IEEE Trans. Appl. Supercond. 19, 640–643 (2009).

Jackman, K. & Fourie, C. J. Flux trapping analysis in superconducting circuits. IEEE Trans. Appl. Supercond. 27, 1–5 (2017).

Holmes, D. S., Ripple, A. L. & Manheimer, M. A. Energy-efficient superconducting computing—power budgets and requirements. IEEE Trans. Appl. Supercond. 23, 1701610–1701610 (2013).

Manheimer, M. A. Cryogenic computing complexity program: phase 1 introduction. IEEE Trans. Appl. Supercond. 25, 1–4 (2015).

Tolpygo, S. K. Superconductor digital electronics: Scalability and energy efficiency issues. Low. Temp. Phys. 42, 361–379 (2016).

Tolpygo, S. K. et al. Inductance of circuit structures for MIT LL superconductor electronics fabrication process with 8 niobium layers. IEEE Trans. Appl. Supercond. 25, 1–5 (2015).

Braiman, Y., Nair, N., Rezac, J. & Imam, N. Memory cell operation based on small Josephson junctions arrays. Supercond. Sci. Technol. 29, 124003 (2016).

Braiman, Y., Neschke, B., Nair, N., Imam, N. & Glowinski, R. Memory states in small arrays of Josephson junctions. Phys. Rev. E 94, 052223 (2016).

Nair, N., Jafari-Salim, A., D’Addario, A., Imam, N. & Braiman, Y. Experimental demonstration of a Josephson cryogenic memory cell based on coupled Josephson junction arrays. Supercond. Sci. Technol. 32, 115012 (2019).

Nair, N. & Braiman, Y. A ternary memory cell using small Josephson junction arrays. Supercond. Sci. Technol. 31, 115012 (2018).

Miloshevsky, A., Nair, N., Imam, N. & Braiman, Y. High-Tc superconducting memory cell. J. Supercond. Nov. Magn. 35, 373–382 (2022).

Hilgenkamp, H. Josephson memories. J. Supercond. Nov. Magn. 34, 1621–1625 (2020).

Wada, Y. Josephson memory technology. Proc. IEEE 77, 1194–1207 (1989).

Hidaka, Y. Superconductor magnetic memory using magnetic films. US patent 5,039,656 (1991).

Ryazanov, V. V. et al. Magnetic Josephson junction technology for digital and memory applications. Phys. Procedia 36, 35–41 (2012). This paper proposed an alternative superconducting memory technology to improve the limited capacity of SIS JJ-based memories.

Oboznov, V. A., Bol’ginov, V. V., Feofanov, A. K., Ryazanov, V. V. & Buzdin, A. I. Thickness dependence of the Josephson ground states of superconductor–ferromagnet–superconductor junctions. Phys. Rev. Lett. 96, 197003 (2006).

Shelukhin, V. et al. Observation of periodic π-phase shifts in ferromagnet-superconductor multilayers. Phys. Rev. B 73, 174506 (2006).

Robinson, J. W. A., Piano, S., Burnell, G., Bell, C. & Blamire, M. G. Critical current oscillations in strong ferromagnetic π junctions. Phys. Rev. Lett. 97, 177003 (2006).

Niedzielski, B. M., Gingrich, E. C., Loloee, R., Pratt, W. P. & Birge, N. O. S/F/S Josephson junctions with single-domain ferromagnets for memory applications. Supercond. Sci. Technol. 28, 085012 (2015).

Bol’ginov, V. V., Stolyarov, V. S., Sobanin, D. S., Karpovich, A. L. & Ryazanov, V. V. Magnetic switches based on Nb–PdFe–Nb Josephson junctions with a magnetically soft ferromagnetic interlayer. J. Exp. Theor. Phys. Lett. 95, 366–371 (2012).

Glick, J. A., Loloee, R., Pratt, W. P. & Birge, N. O. Critical current oscillations of Josephson junctions containing PdFe manomagnets. IEEE Trans. Appl. Supercond. 27, 1–5 (2017).

Dayton, I. M. et al. Experimental demonstration of a Josephson magnetic memory cell with a programmable φ-junction. IEEE Magn. Lett. 9, 1–5 (2018).

Ryazanov, V. V. et al. Coupling of two superconductors through a ferromagnet: evidence for a π junction. Phys. Rev. Lett. 86, 2427–2430 (2001).

Bannykh, A. A. et al. Josephson tunnel junctions with a strong ferromagnetic interlayer. Phys. Rev. B 79, 054501 (2009).

Vernik, I. V. et al. Magnetic Josephson junctions with superconducting interlayer for cryogenic memory. IEEE Trans. Appl. Supercond. 23, 1701208–1701208 (2013).

Larkin, T. I. et al. Ferromagnetic Josephson switching device with high characteristic voltage. Appl. Phys. Lett. 100, 222601 (2012). This paper incorporated an additional superconducting layer to the MJJ structure to make the switching speed compatible with SFQ circuits.

Bakurskiy et al. Theoretical model of superconducting spintronic SIsFS devices. Appl. Phys. Lett. 102, 192603 (2013).

Bergeret, F. S., Volkov, A. F. & Efetov, K. B. Enhancement of the Josephson current by an exchange field in superconductor–ferromagnet structures. Phys. Rev. Lett. 86, 3140–3143 (2001).

Krivoruchko, V. N. & Koshina, E. A. From inversion to enhancement of the dc Josephson current in (formula presented) tunnel structures. Phys. Rev. B 64, 172511 (2001).

Golubov, A. A., Kupriyanov, M. Y. & Fominov, Y. V. Critical current in SFIFS junctions. J. Exp. Theor. Phys. Lett. 75, 190–194 (2002).

Barash, Y. S., Bobkova, I. V. & Kopp, T. Josephson current in S-FIF-S junctions: nonmonotonic dependence on misorientation angle. Phys. Rev. B 66, 140503 (2002).

Bell, C. et al. Controllable Josephson current through a pseudospin-valve structure. Appl. Phys. Lett. 84, 1153–1155 (2004).

Kontos, T. et al. Josephson junction through a thin ferromagnetic layer: negative coupling. Phys. Rev. Lett. 89, 137007 (2002).

Blum, Y., Tsukernik, A., Karpovski, M. & Palevski, A. Oscillations of the superconducting critical current in Nb–Cu–Ni–Cu–Nb junctions. Phys. Rev. Lett. 89, 187004 (2002).

Glick, J. A. et al. Critical current oscillations of elliptical Josephson junctions with single-domain ferromagnetic layers. J. Appl. Phys. 122, 133906 (2017).

Baek, B., Rippard, W. H., Benz, S. P., Russek, S. E. & Dresselhaus, P. D. Hybrid superconducting-magnetic memory device using competing order parameters. Nat. Commun. 5, 3888 (2014).

Golod, T., Iovan, A. & Krasnov, V. M. Single Abrikosov vortices as quantized information bits. Nat. Commun. 6, 8628 (2015).

Stoner, E. C. & Wohlfarth, E. P. A mechanism of magnetic hysteresis in heterogeneous alloys. IEEE Trans. Magn. 27, 3475–3518 (1991).

Goldobin, E. et al. Memory cell based on a φ Josephson junction. Appl. Phys. Lett. 102, 242602 (2013).

Peotta, S. & Di Ventra, M. Superconducting memristors. Phys. Rev. Appl. 2, 034011 (2014).

Alam, S., Hossain, M. S. & Aziz, A. A cryogenic memory array based on superconducting memristors. Appl. Phys. Lett. 119, 082602 (2021).

Stewart, W. C. Current–voltage characteristics of Josephson junctions. Appl. Phys. Lett. 12, 277–280 (1968).

McCumber, D. E. Effect of ac impedance on dc voltage–current characteristics of superconductor weak-link junctions. J. Appl. Phys. 39, 3113–3118 (1968).

Ingold, G. L., Grabert, H. & Eberhardt, U. Cooper-pair current through ultrasmall Josephson junctions. Phys. Rev. B 50, 395 (1994).

Van Den Brink, A. M., Schön, G. & Geerligs, L. J. Combined single-electron and coherent-Cooper-pair tunneling in voltage-biased Josephson junctions. Phys. Rev. Lett. 67, 3030 (1991).

McCaughan, A. N. & Berggren, K. K. A superconducting-nanowire three-terminal electrothermal device. Nano Lett. 14, 5748–5753 (2014).

Suleiman, M., Sarott, M. F., Trassin, M., Badarne, M. & Ivry, Y. Nonvolatile voltage-tunable ferroelectric-superconducting quantum interference memory devices. Appl. Phys. Lett. 119, 112601 (2021).

Alam, S. et al. Cryogenic memory array based on ferroelectric SQUID and heater cryotron. In Device Research Conference 1–2 (IEEE, 2022); https://doi.org/10.1109/DRC55272.2022.9855813

Ghoshal, U., Kroger, H. & Van Duzer, T. Superconductor–semiconductor memories. IEEE Trans. Appl. Supercond. 3, 2315–2318 (1993). This paper coined the concept of hybrid superconductor–semiconductor memories.

Feng, Y. J. et al. Josephson–CMOS hybrid memory with ultra-high-speed interface circuit. IEEE Trans. Appl. Supercond. 13, 467–470 (2003).

Van Duzer, T., Liu, Q., Meng, X., Whiteley, S. & Yoshikawa, N. High-speed interface amplifiers for SFQ-to-CMOS signal conversion. In International Superconductive Electronics Conference (ISEC, 2003).

Liu, Q. et al. Simulation and measurements on a 64-kbit hybrid Josephson–CMOS memory. IEEE Trans. Appl. Supercond. 15, 415–418 (2005).

Liu, Q. et al. Latency and power measurements on a 64-kb hybrid Josephson–CMOS memory. IEEE Trans. Appl. Supercond. 17, 526–529 (2007).

Kuwabara, K., Jin, H., Yamanashi, Y. & Yoshikawa, N. Design and implementation of 64-kb CMOS static RAMs for Josephson–CMOS hybrid memories. IEEE Trans. Appl. Supercond. 23, 1700704–1700704 (2013).

Tanaka, M. et al. Josephson-CMOS hybrid memory with nanocryotrons. IEEE Trans. Appl. Supercond. 27, 1–4 (2017).

Aziz, A. et al. Single-ended and differential MRAMs based on spin hall effect: a layout-aware design perspective. In Proc. IEEE Computer Society Annual Symposium on VLSI 333–338 (IEEE, 2015); https://doi.org/10.1109/ISVLSI.2015.52

Nguyen, M. H. et al. Cryogenic memory architecture integrating spin Hall effect based magnetic memory and superconductive cryotron devices. Sci. Rep. 10, 248 (2020).

Mukhanov, O. A., Kirichenko, A. F., Filippov, T. V. & Sarwana, S. Hybrid semiconductor–superconductor fast-readout memory for digital RF receivers. IEEE Trans. Appl. Supercond. 21, 797–800 (2011).

Suzuki, H., Inoue, A., Imamura, T. & Hasuo, S. Josephson driver to interface Josephson junctions to semiconductor transistors. In International Electron Devices Meeting 290–293 (IEEE, 1988); https://doi.org/10.1109/iedm.1988.32814

Ghoshal, U., Kishore, S., Feldman, A., Huynh, L. & Van Duzer, T. CMOS amplifier designs for Josephson–CMOS interface circuits. IEEE Trans. Appl. Supercond. 5, 2640–2643 (1995).

Author information

Authors and Affiliations

Contributions

All authors conceived the idea of this Review. S.A. performed the literature analysis and collected data. All authors took part in writing the paper, discussed the data and contributed to the final paper. A.A. supervised the project.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Swamit Tannu and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Alam, S., Hossain, M.S., Srinivasa, S.R. et al. Cryogenic memory technologies. Nat Electron 6, 185–198 (2023). https://doi.org/10.1038/s41928-023-00930-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-00930-2