Abstract

Nanowire-based devices can potentially be of use in a variety of electronic applications, from ultrascaled digital circuits to 5G communication networks. However, the devices are typically restricted to low-power applications due to the relatively low electrical conductivity and limited voltage capability of the nanowires. Here, we show that wide-band-gap AlGaN/GaN nanowires containing multiple two-dimensional electron gas channels can be used to create high-electron-mobility tri-gate transistors for power-conversion applications. The multiple channels lead to improved conductivity in the nanowires, and a three-dimensional field-plate design is used to manage the high electric field. Power devices made with 15-nm-wide nanowires are shown to exhibit low specific on resistances of 0.46 mΩ cm−2, enhancement-mode operation, improved dynamic behaviour and breakdown voltages as high as 1,300 V.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

Vardi, A. & Del Alamo, J. A. Sub-10-nm fin-width self-aligned InGaAs FinFETs. IEEE Electron Device Lett. 37, 1104–1107 (2016).

Singh, J. et al. 14-nm FinFET technology for analog and RF applications. IEEE Trans. Electron Devices 65, 31–37 (2018).

Baliga, B. J. Fundamentals of Power Semiconductor Devices (Springer, 2008).

Baliga, B. J. Gallium nitride devices for power electronic applications. Semicond. Sci. Technol. 28, 074011 (2013).

Ma, J., Erine, C., Xiang, P., Cheng, K. & Matioli, E. Multi-channel tri-gate normally-on/off AlGaN/GaN MOSHEMTs on Si substrate with high breakdown voltage and low ON-resistance. Appl. Phys. Lett. 113, 242102 (2018).

Ma, J. et al. 1200 V multi-channel power devices with 2.8 Ω·mm ON-resistance. In 2019 IEEE International Electron Devices Meeting (IEDM) 4.1.1–4.1.4 (IEEE, 2019).

Ma, J. & Matioli, E. Slanted tri-gates for high-voltage GaN power devices. IEEE Electron Device Lett. 38, 1305–1308 (2017).

Ma, J. & Matioli, E. 2 kV slanted tri-gate GaN-on-Si Schottky barrier diodes with ultra-low leakage current. Appl. Phys. Lett. 112, 060401 (2018).

Sheng, N. H., Lee, C. P., Chen, R. T. & Miller, S. J. Multiple-channel GaAs/AlGaAs high electron mobility transistors. Electron Device Lett. 6, 307–310 (1985).

Cao, Y. et al. MBE growth of high conductivity single and multiple AlN/GaN heterojunctions. J. Cryst. Growth 323, 529–533 (2011).

Shinohara, K. et al. GaN-based multi-channel transistors with lateral gate for linear and efficient millimeter-wave power amplifiers. In IEEE MTT-S International Microwave Symposium (IMS) 1133–1135 (IEEE, 2019).

Lei, J. et al. 650-V double-channel lateral Schottky barrier diode with dual-recess gated anode. IEEE Electron Device Lett. 39, 260–263 (2018).

Raj, A. et al. Demonstration of a GaN/AlGaN superlattice-based p-channel FinFET with high ON-current. IEEE Electron Device Lett. 41, 220–223 (2020).

Heikman, S., Keller, S., Green, D. S., DenBaars, S. P. & Mishra, U. K. High conductivity modulation doped AlGaN/GaN multiple channel heterostructures. J. Appl. Phys. 94, 5321–5325 (2003).

Palacios, T. et al. Use of double-channel heterostructures to improve the access resistance and linearity in GaN-based HEMTs. IEEE Trans. Electron Devices 53, 562–565 (2006).

Erine, C., Ma, J., Santoruvo, G. & Matioli, E. Multi-channel AlGaN/GaN in-plane-gate field-effect transistors. IEEE Electron Device Lett. 41, 321–324 (2020).

Lu, B., Matioli, E. & Palacios, T. Tri-gate normally-off GaN power MISFET. IEEE Electron Device Lett. 33, 360–362 (2012).

Ma, J. & Matioli, E. High performance tri-gate GaN power MOSHEMTs on silicon substrate. IEEE Electron Device Lett. 38, 367–370 (2017).

Amano, H. The 2018 GaN power electronics roadmap. J. Phys. D 51, 163001 (2018).

Wong, K. Y. R. et al. A next generation CMOS-compatible GaN-on-Si transistors for high efficiency energy systems. In International Electron Devices Meeting (IEDM) 9.5.1–9.5.4 (IEEE, 2015).

Kwan, M. H. et al. CMOS-compatible GaN-on-Si field-effect transistors for high voltage power applications. Int. Electron Devices Meet. IEDM 17.6.1–17.6.4 (IEEE, 2015).

Wong, R. K. Y. et al. High performance GaN-on-Si power devices with ultralow specific on-resistance using novel strain method fabricated on 200 mm CMOS-compatible process platform. In 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD) 67–70 (IEEE, 2019).

Thathachary, A. V., Liu, L. & Datta, S. Impact of fin width scaling on carrier transport in III–V FinFETs. In 71st Device Research Conference 17–18 (IEEE, 2013).

Cao, X. A. et al. Electrical effects of plasma damage in p-GaN. Appl. Phys. Lett. 75, 2569–2571 (1999).

Liu, Z., Ma, J., Huang, T., Liu, C. & May Lau, K. Selective epitaxial growth of monolithically integrated GaN-based light emitting diodes with AlGaN/GaN driving transistors. Appl. Phys. Lett. 104, 091103 (2014).

Howell, R. S. et al. The super-lattice castellated field effect transistor (SLCFET): a novel high performance transistor topology ideal for RF switching. In 2014 International Electron Devices Meeting (IEDM) 11.5.1–11.5.4 (IEEE, 2014).

Nela, L., Zhu, M., Ma, J. & Matioli, E. High-performance nanowire-based E-mode power GaN MOSHEMTs with large work-function gate metal. IEEE Electron Device Lett. 40, 439–442 (2019).

Astre, G., Tartarin J. G. & Lambert, B. Trapping related degradation effects in AlGaN/GaN HEMT. In Fifth European Microwave Integrated Circuits Conference 298–301 (IEEE, 2010).

Nela, L. et al. Conformal passivation of multi-channel GaN power transistors for reduced current collapse. IEEE Electron Device Lett. 42, 86–89 (2020).

Ma, J., Kampitsis, G., Xiang, P., Cheng, K. & Matioli, E. Multi-channel tri-gate GaN power Schottky diodes with low ON-resistance. IEEE Electron Device Lett. 40, 275–278 (2018).

Chang, J. et al. The super-lattice castellated field-effect transistor: a high-power, high-performance RF amplifier. IEEE Electron Device Lett. 40, 1048–1051 (2019).

Elehed, A. et al. Demonstration of β-(AlxGa1 − x)2O3–β-Ga2O3 modulation doped field-effect transistors with Ge as dopant grown via plasma-assisted molecular beam epitaxy. Appl. Phys. Express 10, 071101 (2017).

Krishnamoorthy, S. et al. Modulation-doped β-(Al0.2Ga0.8)2O3–Ga2O3 field-effect transistor. Appl. Phys. Lett. 111, 023502 (2017).

Li, W. et al. 2.44 kV Ga2O3 vertical trench Schottky barrier diodes with very low reverse leakage current. In 2018 IEEE International Electron Devices Meeting (IEDM) 8.5.1–8.5.4 (IEEE, 2019).

Del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Tang, Z. et al. 600-V normally off SiNx/AlGaN/GaN MIS-HEMT with large gate swing and low current collapse. IEEE Electron Device Lett. 34, 1373–1375 (2013).

Hsieh, T. E. et al. Gate recessed quasi-normally off Al2O3/AlGaN/GaN MIS-HEMT with low threshold voltage hysteresis using PEALD AlN interfacial passivation layer. IEEE Electron Device Lett. 35, 732–734 (2014).

He, L. et al. High threshold voltage uniformity and low hysteresis recessed gate Al2O3/AlN/GaN MISFET by selective area growth. IEEE Trans. Electron Devices 64, 1554–1560 (2017).

Huang, S. et al. High uniformity normally-OFF GaN MIS-HEMTs fabricated on ultra-thin-barrier AlGaN/GaN heterostructure. IEEE Electron Device Lett. 37, 1617–1620 (2016).

Wang, H. et al. 823-mA/mm drain current density and 945-MW/cm2 Baliga’s figure-of-merit enhancement-mode GaN MISFETs with a novel PEALD-AlN/LPCVD-Si3N4 dual-gate dielectric. IEEE Electron Device Lett. 39, 1888–1891 (2018).

Wei, J. et al. Low on-resistance normally-off GaN double-channel metal–oxide–semiconductor. IEEE Electron Device Lett. 36, 1287–1290 (2015).

Zhu, M., Ma, J., Nela, L., Erine, C. & Matioli, E. High-voltage normally-off recessed tri-gate GaN power MOSFETs with low on-resistance. Electron Device Lett. 40, 1289–1292 (2019).

Zhong, Y. et al. Normally-off HEMTs with regrown p-GaN gate and low-pressure chemical vapor deposition SiNx passivation by using an AlN pre-layer. IEEE Electron Device Lett. 40, 1495–1498 (2019).

Lu, B., Piner, E. L. & Palacios, T. Schottky-drain technology for AlGaN/GaN high-electron mobility transistors. IEEE Electron Device Lett. 31, 302–304 (2010).

Tang, Z. et al. High-voltage (600-V) low-leakage low-current-collapse AlGaN/GaN HEMTs with AlN/SiNx passivation. Electron Device Lett. 34, 366–368 (2013).

Arulkumaran, S., Vicknesh, S., Ing, N. G., Selvaraj, S. L. & Egawa, T. Improved power device figure-of-merit (4.0×108 V2 Ω−1 cm−2) in AlGaN/GaN high-electron-mobility transistors on high-resistivity 4-in. Si. Appl. Phys. Express 4, 084101 (2011).

Krishna, S. et al. Over 550 V breakdown voltage of InAlN/GaN HEMT on Si. Physica Status Solidi C 10, 824–826 (2013).

Lo, C.- F. et al. High-power AlGaN/GaN heterostructure field-effect transistors on 200mm Si substrates. ECS Transactions 66, 191–199 (2015).

Zhou, Q., Chen, B., Jin, Y., Huang, S. & Wei, K. High-performance enhancement-mode Al2O3/AlGaN/GaN-on-Si MISFETs with 626 MW/cm2 figure of merit. IEEE Trans. Electron Devices 62, 776–781 (2015).

Sun, M., Lee, H.-S., Lu, B., Piedra, D. & Palacios, T. Comparative breakdown study of mesa- and ion-implantation-isolated AlGaN/GaN high-electron-mobility transistors on Si substrate. Appl. Phys. Express 5, 074202 (2012).

Herbecq, N. et al. Above 2000 V breakdown voltage on ultrathin barrier AlN/GaN-on-silicon transistors. In CS MANTECH 2015 Int. Conf. Compound Semicond. Manuf. Technol. 305–307 (2015).

Herbecq, N. et al. GaN-on-silicon high electron mobility transistors with blocking voltage of 3 kV. Electron. Lett. 51, 1532–1534 (2015).

Dogmus, E., Zegaoui, M. & Medjdoub, F. GaN-on-silicon high-electron-mobility transistor technology with ultra-low leakage up to 3000 V using local substrate removal and AlN ultra-wide bandgap. Appl. Phys. Express 11, 034102 (2018).

Ikeda, N. et al. High-power AlGaN/GaN MIS-HFETs with field-plates on Si substrates. In Int. Symp. Power Semicond. Devices IC’s 251–254 (IEEE, 2009).

Hwang, I. et al. 1.6kV, 2.9 mΩ cm2 normally-off p-GaN HEMT device. In Int. Symp. Power Semicond. Devices ICs 41–44 (IEEE, 2012).

Selvaraj, S. L., Watanabe, A., Wakejima, A. & Egawa, T. 1.4-kV breakdown voltage for AlGaN/GaN high-electron-mobility transistors on silicon substrate. IEEE Electron Device Lett. 33, 1375–1377 (2012).

Egawa, T. Heteroepitaxial growth and power electronics using AlGaN/GaN HEMT on Si. In Tech. Dig. Int. Electron Devices Meeting IEDM 613–616 (IEEE, 2012).

Ishida, M., Ueda, T., Tanaka, T., & Ueda, D. GaN on Si technologies for power switching devices. IEEE Trans. Electron Devices 60, 3053–3059 (2013).

Zhang, Z. et al. Studies on high-voltage GaN-on-Si MIS-HEMTs using LPCVD Si3N4 as gate dielectric and passivation layer. IEEE Trans. Electron Devices 63, 731–738 (2016).

Freedsman, J. J., Kubo, T. & Egawa, T. High drain current density E-mode Al2O3/AlGaN/GaN MOS-HEMT on Si with enhanced power device figure-of-merit (4×108 V2 Ω−1 cm−2). IEEE Trans. Devices 60, 3079–3083 (2013).

Christy, D. et al. Uniform growth of AlGaN/GaN high electron mobility transistors on 200 mm silicon (111) substrate. Appl. Phys. Express 6, 026501 (2013).

Liu, X. et al. AlGaN/GaN-on-silicon metal–oxide–semiconductor high-electron-mobility transistor with breakdown voltage of 800 V and on-state resistance of 3 mΩ·cm2 using a complementary metal–oxide–semiconductor compatible gold-free process. Appl. Phys. Express 5, 066501 (2012).

Lu, B. & Palacios, T. High breakdown (>1500 V) AlGaN/GaN HEMTs by substrate-transfer technology. IEEE Electron Device Lett. 31, 951–953 (2010).

Acknowledgements

We thank R. Soleimanzadeh and G. Santoruvo for their assistance in electrothermal and Hall measurements, and the staff in the CMi and ICMP cleanrooms at EPFL for their technical support. This work was supported in part by the European Research Council (ERC) under the European Union’s H2020 programme/ERC Grant Agreement 679425, in part by the Swiss National Science Foundation (SNSF) under Assistant Professor (AP) Energy Grants PYAPP2_166901 and 200021_169362 and in part by the ECSEL Joint Undertaking (JU) under Grant Agreement 826392. The JU receives support from the European Union’s Horizon 2020 research and innovation programme and from Austria, Belgium, Germany, Italy, Norway, Slovakia, Spain, Sweden and Switzerland.

Author information

Authors and Affiliations

Contributions

E.M., L.N. and J.M. conceived the project. L.N., J.M. and C.E. fabricated the devices and performed and analysed the electrical measurements. K.C., P.X. and J.M. grew the epitaxy structures. V.T., T.-H.S. and T.W. performed and analysed the STEM measurements. E.M., L.N. and J.M. wrote the paper, and all authors approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Electronics thanks Kevin Chen and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

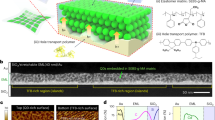

Extended Data Fig. 1 Electron transport in multi-channel nanowires.

a, Electron mobility in multi-channel nanowires measured by gated hall bar at different gate voltages (VG) and nanowire width (wNW). The mobility peak depends on the nanowire width and shifts to higher VG as wNW decreases. b, Peak mobility as a function of wNW, extracted from figure (a). 20 nm-wide nanowires still present a high mobility value of 1200 cm2/Vs. This is of great importance as it demonstrates excellent electron conduction despite the small nanowire dimensions and the sidewalls scattering contributions. The excellent mobility results in a very low sheet resistance Rs of 150 Ω/sq for 20 nm e-mode nanowires c. Such value is half of the typical sheet resistance of conventional planar single-channel heterostructures. d, TEM cross-section showing the interface between the multi-channel nanowire and the ALD SiO2 gate oxide. A smooth surface with no evident roughness above ~ 1 nm can be observed.

Extended Data Fig. 2 Threshold voltage in multi-channel nanowires.

a, The minimum nanowire width to achieve e-mode operation was extracted by employing the conductance method. The I-V characteristics of Fat-FET with different nanowire width (wNW) was measured, from which the nanowire conductance (GNW) was extracted. By linear fit of the GNW versus wNW plot, a nanowire sidewalls depletion (wDepl) of 16.5 nm was calculated for gate voltage (VG) of 0 V. As VG increased, wDepl decreased showing the effective gate control over the nanowire. b, The depletion width indicates the minimum nanowire width to achieve e-mode operation since for wNW < 2wDepl the depletion regions from the two sidewalls merge in the center and eliminate the 2DEG. c, It should be noted that while in general a much higher gate voltage is required to turn off a multi-channel nanowire with respect to a single-channel one due to its larger carrier density, for small nanowire widths such difference becomes smaller and multi-channel devices show very similar VTH with respect to single-channel counterpart for wNW below 50 nm, despite the much larger Ns. This is due to the predominant side gate control and to the strong sidewalls depletion at such narrow widths, which is similar for multi- and single-channel nanowires. d, The evaluation of the sidewalls depletion width is consistent with the device transfer curves, which indicate 30 nm as the minimum nanowire width to achieve positive VTH. To further shift VTH to positive values, the conventional Ni-Au gate metal stack was replaced by a Pt-Au gate metal, which resulted in a threshold voltage increase of about 0.5 V. Such improvement, which is consistent for different wNW, derives from the higher work-function of Pt with respect to Ni and allows to increase VTH without any degradation of the channel, resulting in large VTH of 0.85 V for 15 nm-wide nanowires.

Extended Data Fig. 3 Threshold voltage stability.

a, Schematics of the gate lag measurement employed to determine the device VTH stability. First, the device is stressed for a time toff = 5 ms during which a quiescent gate voltage VG,q is applied to cause trapping in the gate stack. The quiescent drain voltage VD,q is 0 V to avoid any drain lag contribution or device heating. Then the gate voltage VG is set to 7 V and the drain voltage VD to 1 V for a short time ton = 5 μs, during which the drain current (ID) is measured. Trapping in the gate stack and instability of the device VTH result in a variation of the measured ID depending on the value of the applied VG,q. b, Gate lag measurement as a function of VG,q for the presented multi-channel devices, and for a reference single-channel device having similar VTH. The measured ID has been normalized to the value obtained at VG,q = 7 V, that is when the gate voltage is kept constant and thus no stress is applied. A negligible gate lag effect is observed for the multi-channel devices with a current reduction of less than 4 % in the whole measurement range, which proves their excellent VTH stability. Moreover, multi-channel devices show much-reduced gate lag with respect to the single-channel references, which instead present a current decrease of 20 % at VG,q of −3 V. Such behavior is due to the multi-channel larger carrier concentration which results in a weaker influence of the traps in the gate dielectric on the device VTH. c, VTH as a function of temperature (T) for the presented multi-channel devices. A very constant VTH behavior can be observed in the whole measurement range up to 150 °C with the device maintaining full E-mode operation and showing only a minor VTH shift of 50 mV.

Extended Data Fig. 4 Current collapse in multi-channel tri-gate HEMTs.

a, Schematics of the double pulse measurement employed to determine the device current collapse. The device is first stressed in the off-state for a time toff = 5 ms at a large quiescent drain bias VD,q, and then it is suddenly turned on for a short time ton = 50 μs during which its on-resistance is measured. b, Normalized RON,dyn as a function of VD,q for the multi-channel devices and for two different single-channel reference devices, cofabricated in the same batch, with (1) gate termination in the nanowire region and same design with respect to the multi-channel case (2) gate termination on the planar region as for conventional single-channel device architectures. All devices present a low-pressure chemical vapor deposition (LPCVD) Si3N4 passivation layer. Single-channel devices with the gate termination in the nanowire region show a highly degraded RON,dyn as a consequence of the increased surface area at the nanowire sidewalls, which result in more severe electron trapping during the off-state stress. This is not the case, instead, for multi-channel devices, whose much larger carrier density (Ns) and 3D structure considerably reduce the virtual gate effect due to sidewalls traps. Most importantly, multi-channel devices show very similar performance with respect to conventional single-channel devices with gate termination on the planar region, which represents the optimal architecture for such single-channel heterostructures. This demonstrates that multi-channel devices can be effectively passivated despite their 3D architecture and can provide not only outstanding DC performance but also excellent dynamic behavior.

Supplementary information

Supplementary Information

Supplementary Figs. 1–3 and Tables 1–4.

Rights and permissions

About this article

Cite this article

Nela, L., Ma, J., Erine, C. et al. Multi-channel nanowire devices for efficient power conversion. Nat Electron 4, 284–290 (2021). https://doi.org/10.1038/s41928-021-00550-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-021-00550-8

This article is cited by

-

Lattice-mismatch-free construction of III-V/chalcogenide core-shell heterostructure nanowires

Nature Communications (2023)

-

An avalanche-and-surge robust ultrawide-bandgap heterojunction for power electronics

Nature Communications (2023)

-

Boosted high-temperature electrical characteristics of AlGaN/GaN HEMTs with rationally designed compositionally graded AlGaN back barriers

Science China Information Sciences (2023)

-

Ultra-wide bandgap semiconductor Ga2O3 power diodes

Nature Communications (2022)

-

Observation of polarity-switchable photoconductivity in III-nitride/MoSx core-shell nanowires

Light: Science & Applications (2022)