Abstract

Inspired by massive parallelism, an increase in internet-of-things devices, robust computation, and Big-data, the upsurge research in building multi-bit mem-transistors is ever-augmenting with different materials, mechanisms, and state-of-the-art architectures. Herein, we demonstrate monolayer WS2-based functional mem-transistor devices which address nonvolatility and synaptic operations at high temperature. The ionotronic memory devices based on WS2 exhibit reverse hysteresis with memory windows larger than 25 V, and extinction ratio greater than 106. The mem-transistors show stable retention and endurance greater than 100 sweep cycles and 400 pulse cycles in addition to 6-bit (64 distinct nonvolatile storage levels) pulse-programmable memory features ranging over six orders of current magnitudes (10−12–10−6 A). The origin of the multi-bit states is attributed to the carrier dynamics under electrostatic doping fluctuations induced by mobile ions, which is illustrated by employing a fingerprint mechanism including band-bending pictures. The credibility of all the storage states is confirmed by obtaining reliable signal-to-noise ratios. We also demonstrate key neuromorphic behaviors, such as synaptic plasticity, near linear potentiation, and depression, rendering it suitable for successful implementation in high temperature neuromorphic computing. Furthermore, artificial neural network simulations based on the conductance weight update characteristics of the proposed ionotronic mem-transistors are performed to explore the potency for accurate image recognition. Our findings showcase a different class of thermally aided memories based on 2D semiconductors unlocking promising avenues for high temperature memory applications in demanding electronics and forthcoming neuromorphic computing technologies.

Similar content being viewed by others

Introduction

The amount of digital data generated by humans, which can be quantified in terms of the number of bits produced yearly, is continuously expanding and is projected to exceed 100 zettabytes by 2023. To effectively manage the massive amount of data and global memory requirements, the upcoming nonvolatile memory (NVM) technologies must furnish multi-bit ultra-high-density storage capacity with a significant extinction ratio, endurance, retention, and low energy consumption1. Two-dimensional (2D) layered materials, consisting of atomically thin layers, possess a plethora of exotic properties and have emerged as the leading contenders for the upcoming generation of electronic devices2. Specific attention given to the layered transition metal di-chalcogenides (TMDCs)3, has created numerous prospects for developing low-power electronics, cutting-edge memory device arrays4,5 and smart computing architectures6 with desirable miniaturization. Recently, there has been an intensive exploration of NVMs based on 2D materials and their heterostructures7. These NVMs utilize revolutionary device architecture and unusual mechanisms to overcome the limitations of conventional flash memory based on silicon. Opto-electronically controlled floating gate (FG) and charge trap based devices can produce high operation speed, and low power memory characteristics8,9,10,11,12,13,14,15,16,17. Nevertheless, it is difficult to develop high-capacity multi-bit generation that can work at elevated temperatures. Recent report by Li et al. propose MoS2/hBN/MoS2/GDYO/WSe2 heterostructure as an active layer to generate 8 memory states18 whereas, Lai et al. use top FGM with stacked MoS/hBN/2D-RPP to produce 22 distinct memory states19. Furthermore, the production of such memory devices necessitates cumbersome state-of-the-art methodologies, which require accurate deposition of various semiconductor layers, and multiple lithography processes, culminating in intricate mem-transistors with numerous floating metals and oxide layers. As the yearning for energy conservation is more prevalent than ever, advancing the scale-down of circuits beyond Moore’s law will mandate the exploration of 2D materials based architectures20.

On the contrary, the electrolyte-gated transistors show analog switching performance with superior storage capacity benefited from their ion-gating mechanism over electrostatic charge trap phenomena, making them viable candidates for brain-inspired computation and logic-in-memory applications21,22,23,24,25. Post stimulation, the diffusive dynamics of mobile ions (such as Li+, Na+) possess linear and symmetric weight updates of the discrete multilevel states, making them more effective than FGM-based arrays in processing artificial neural networks (ANNs)26,27,28. Despite the recent development of synaptic ion-gated transistors, multi-bit memory based on ion gating mechanisms is still lacking. With the increasing spatial density of FET arrays on a solitary wafer, integrated circuits (ICs) of superior performance can attain an operating temperature as high as 450 K29. Therefore, understanding and leveraging the properties of 2D materials-based devices is crucial for their high-temperature potential applications in harsh environments such as aerospace industries, military, automotives, sensors, well logging, oil refinery etc30. However, no consensus has been reported to address stable multilevel memory switching at elevated temperatures. Unfortunately, the use of liquid electrolytes severely demarcates the integration density of devices and limits their applicability to high-temperature environments22,24. As a result, it is imperative to introduce multi-level memories with eccentric synaptic functionalities that can enable simpler device architectures, thermally-stable reliable switching, and enhanced throughput.

In this context, we have proposed and demonstrated monolayer (ML) WS2 mem-transistor with robust device architecture and reduced dimensionality for multi-bit nonvolatile memory applications at high temperatures (~425 K). The WS2 based mem-transistor manifests endurance properties greater than 100 sweep and 400 pulse cycles, high switching ratios, non-volatility with stable retention and efficient conductance modulation. The memory behavior is attributed to the interfacial electrostatic doping effect of channel material through active cation migration under the applied gate field. Furthermore, the three-terminal device exhibits more than 64 distinct memory states, making it a potential candidate for 6-bit memory operations. The multi-bit memory operations in our device show exceptional pulse control of charge injection and release, providing a complete yet straightforward strategy to achieve large-scale data storage capabilities in WS2 mem-transistors. Moreover, key synaptic behaviors such as excitatory post-synaptic current (EPSC), long-term potentiation/depression (LTP/LTD) are demonstrated at elevated temperatures using various pulse schemes. We further utilize ionotronic non-volatile conductance weights to establish excellent pattern recognition accuracy approaching software limit of ~98% during ANN training of MNIST datasets. Our results showcase a different class of thermally-driven memories based on 2D semiconductors, representing a leap forward for developing high density memories and future neuromorphic computing technologies operating at high-temperatures.

Results and discussion

Fabrication of ion-gated WS2 transistors

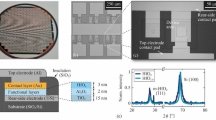

The ML WS2 is synthesized via a salt-assisted chemical vapor deposition (CVD) technique31, wherein the synthesis parameters are fine-tuned to achieve large-scale triangular domain growth with high crystallinity, as shown in Supplementary Fig. 2 and facilitate the diffusion of mobile ions (Na+) into the SiO2 gate dielectric (for detailed information, refer to “Methods”). As-grown samples are characterized with Raman spectroscopy at room temperature, utilizing a 532 nm excitation wavelength. The WS2 exhibits two prominent Raman active modes, namely E12g and A1g, as illustrated in Fig. 1a, corresponding to the in-plane vibration of W and S atoms and the out-of-plane vibrations of the S atoms, respectively. The frequency difference (\(\Delta \omega \le 61{{cm}}^{-1}\)) between them indicates the ML nature of the as-grown WS2 samples32. Figure 1b displays the photoluminescence (PL) spectrum with a very sharp and intense luminescence at 1.96 eV, which further confirms the high optical grade quality of salt-assisted CVD-grown ML WS233. The inset shows the optical micrograph (top view) of a WS2 transistor with silver (Ag) metal as drain/source electrodes (for details, see Supplementary Fig. 2). Figure 1c depicts the schematics of the device architecture with necessary electrical contacts where the back gate is facilitated by heavily doped silicon (Si++). The WS2/SiO2 interface is portrayed in a separate magnified cross-sectional cartoon where Na+ ions are shown to be diffused inside the SiO2 near the interface region. Recently, Kaushik et al. report the adsorption of lighter impurities such as Na+ ions, on the SiO2 surface during NaCl-aided CVD growth34. These Na+ ions get diffused inside the SiO2 upon high-temperature annealing which can be employed to realize a solid-state ion-gated medium in our case, similar to electrolyte/ionic liquid-gated transistors22,23.

a Room temperature Raman spectrum of as-grown ML WS2 supported by SiO2 (285 nm)/Si substrate. b The photoluminescence spectrum confirms the monolayer nature of WS2. Inset shows the optical micrograph (top view) of a WS2 transistor with silver (Ag) metal as drain/source electrodes (Scale bar is 10 \(\mu m\)). c Schematic representation of the ML WS2-based device model with necessary electrical contacts. The magnified cross-sectional view at the WS2/SiO2 interface illustrates the diffusion of Na+ ions inside SiO2.

Thermally-driven hysteresis evolution

The temperature-dependent dual sweep transfer characteristics are conducted under high vacuum (10−6 mbar) after annealing the device at 200 °C for 36 h. Annealing is found to be crucial to reduce contact resistances without degrading the device performance, as reported earlier35. Figure 2a, b depicts the evolution of hysteresis curves for temperatures ranging from 275 to 425 K during a gate voltage sweep range of \(\pm 50\) V. The black and red arrows represent forward and backward sweep directions and the threshold voltage differences between them indicate the memory window (\(\Delta {V}_{{th}}\)). Initially at 275 K, the nature of the hysteresis is found to be clockwise (CW), while at room temperature, the forward and backward sweeps overlap with each other collapsing the hysteresis completely. Interestingly, upon increasing the temperature to 350 K, an anti-clockwise (ACW) hysteresis loop is evolved which inflates further with elevated temperatures. It is worth to mention that, at 425 K the memory window is increased to as high as 25 V with extinction ratio (IBS/IFS) rises to the orders of 105 at zero gate bias. The hysteresis curves at 325 and 375 K along with temperature dependent mobility variations are shown in Supplementary Fig. 3, which are consistent with the thermally-driven hysteresis evolution in our case. Moreover, in Fig. 2b, we demonstrate the potential application of thermally-assisted reverse hysteresis in nonvolatile memory operations. The memory characteristics can be obtained by utilizing specific regions of the transfer curves to define the PROGRAM, ERASE, and READ operations. During the forward sweep, the ERASE operation can be executed by applying a gate voltage of −50 V, followed by a low conductive READ operation at Vbg = 0 V. Similarly, by applying a high positive gate voltage of 50 V, we can PROGRAM our memory device to achieve a higher conductance state, which can be subsequently READ at Vbg = 0 V during backward sweep. Recently, the temperature dependent hysteresis crossover/inversion has been reported in ML and few-layer MoS236,37. However, the nature and origin of the hysteresis loops and their proposed mechanisms are very different from the results we observed in our case. For example, in the article by He et al.36, the hysteresis loop contains two different regions, i.e., anti-clockwise loop below Vbg = 0 V and clockwise loop above Vbg = 0 V, which also limits the extinction ratio to ~102. Also, the origin of such hysteresis is attributed to carrier injection from Si into SiO2 with minimal role of channel MoS2. However, in our case, the device attains a single large anticlockwise hysteresis with extinction ratio of ~106 and the memory is governed by the dielectric/channel interfacial physics. Figure 2c represents the progression of memory windows and extinction ratios as a function of temperature. Both the parameters show systematic and significant enhancements when compared with their respective room temperature values. Here we want to emphasize that our recent findings on CVD (without NaCl) grown ML MoS2 shows a high temperature clockwise hysteresis behavior owing to the accelerated charge trapping/detrapping, however, the anticlockwise hysteresis is only observed in NaCl-assisted CVD grown MoS238. This further confirms the Na+ driven ion-gating induced large reverse hysteresis in our NaCl-assisted CVD grown WS2 based transistors. For the sake of completeness, we also perform the output characteristics for different gate voltages in our devices which are shown in Supplementary Fig. 4.

a The dual sweep transfer characteristics at temperatures ranging from 275 to 400 K. The black and red arrows represent forward and backward sweep direction, respectively and nature of the hysteresis loop. b Dual sweep reverse hysteretic transfer curves with memory window of 25 V and extinction ratio of ~105 is demonstrated at 425 K for gate voltage sweep range of \(\pm 50\) V. The PROGRAM, ERASE, and READ operation regime are also demonstrated. c The relation between memory window (\(\triangle {V}_{{th}}\)) and current switching ratios (IBS/IFS) with temperature at zero gate voltages during dual sweep measurements.

Operation mechanism of Ionotronic memory

In conventional WS2 transistors, a relatively high surface-to-volume ratio necessitates an inescapable exposure of the atomically thin channel to the oxide trap/defect states, which induce clockwise hysteresis and high threshold voltage instabilities, leading to reliability issues39. Nonetheless, the substantial hysteresis generated during the dual sweep and pulsed gate operations in most 2D transistor devices has been meticulously utilized for nonvolatile (which encompass 2D flash memory, magnetic random access memory, resistive random access memory) and volatile (such as dynamic random access memory, semi-floating gate transistor) memory applications1. However, in our case, temperature modulated hysteresis collapse and switch from clockwise to anti-clockwise hysteresis indicates ion-gating induced charge transfer and charge storage25. The increased kinetic energy of Na+ inside SiO2 at high temperatures generates an efficient ion gating over conventional dielectric gating for transistor applications28. To shed light on the effect of Na+ ions on hysteresis, we propose a fingerprint mechanism as depicted in Fig. 3a–d, that adequately illustrates the evolution of hysteresis with temperature, providing the possibilities to attain thermally stable nonvolatile memory states in ML WS2. The upper and lower panel shows the cross-sectional schematic view of the WS2/Na+ diffused SiO2 interface and energy band diagram of source-channel-drain, respectively during various programming operations. Applying a positive gate-source voltage induces a drift of mobile Na+ ions, causing them to move towards the WS2 channel. This accumulation beneath the interface, illustrated in Fig. 3a, results in the buildup of spatial charges near the interface. This accumulation has the effect of further electrostatically doping the WS2 channel, an operation referred as ‘PROGRAM’. The added n-doping of WS2 reduces its energy band below the Fermi level of Ag, creating an easily accessible pathway for conduction electrons to tunnel through.

The cross-sectional schematic view of the WS2 mem-transistor (upper panel), Energy band diagram of source-channel-drain (lower panel) for a PROGRAM, b High Conductive Read, c ERASE, and d Low Conductive Read operations. For Read operations, the bias voltage Vds is fixed at a finite voltage (in our case, 2 V) to measure the drain current values after PROGRAM/ERASE. The PROGRAM operation is facilitated by the Na+ accumulation at the WS2/SiO2 interface, whereas in the ERASE operation, the depletion of the ion layer reduces the effective electrostatic doping resetting the device to the original state. The green arrows in the energy band diagrams indicate the direction of the flow of currents through the channel. Effect of e Positive (+50 V) and f Negative (−50 V) stress under different stress times of ML WS2 mem-transistor. g Mobilities extracted from forward and backward transfer curves vs. stress time, at Vds = 2 V.

Figure 3b illustrates the schematic for the “High Conductive Read” operation with a bias voltage (Vds) of 2 V at Vbg = 0 V. Following the “PROGRAM” operation, the collected Na+ ions progressively enhance the drain current, reaching around ~10−6 A even in the absence of gate voltage during the backward sweep. The corresponding band diagram highlights the increased carrier concentration within the WS2 channel under the conditions of the “High Conductive Read” state. The Na+ ions accumulated at the interface exhibit high retention due to their low probability of returning to their original state, even after removing the external electric field, resulting in band lowering and hence high conductance of the WS2 channel. Thus it can only be depleted by employing a highly negative Vbg, an “ERASE” operation. In such cases, the Na+ ions migrate away from the interface and towards the opposite direction, facilitated by the electrostatic polarization effect. The “ERASE” operation increases the barrier width at the Schottky junction, as displayed in Fig. 3c. A further “Read” operation can furnish low current values up to ~10−12 A, akin to the case of an undoped WS2 channel. The schematic representation of Fig. 3d illustrates low carrier channel densities with corresponding band bending in the “Low Conductive Read” operation. Hence, by administering a positive or negative gate voltage of approximately ±50 V, the doping concentration of the WS2 channel can be tuned, resulting in a subsequent modification of its resistivity.

Considering the intricate dynamics of Na+ ions during gating, it is imperative to scrutinize the impact of gate bias stress in our ML WS2 mem-transistors. Specifically, to induce positive (negative) gate bias stress, a uniform gate voltage of 50 V (-50 V) was applied for a defined duration before measuring the transfer characteristics. As demonstrated in Fig. 3e, the transfer curve gradually shifts upwards with prolonged positive gate bias stress durations. The maximum output current (Idsmax) with different hold times is also charted in Supplementary Fig. 5 to elucidate the gate bias stress on our memory devices. It can also be noted that the maximum current augments linearly with increasing stress durations. Interestingly, the transfer curves remain unaltered for mounting negative gate bias stress durations as shown in Fig. 3f. Considering the fact that the Na+ are mobile in few nm range inside the diffused SiO2 region, the ions cannot be pushed away to the gate/dielectric interface, unlike the case of single ion conductor40. Therefore, we expect the formation of a weaker negatively charged depletion layer at the channel/dielectric interface on the application of negative gate voltage which will have a negligible impact on the device performance. The values of mobilities obtained from multiple transfer curves with various positive and negative stress durations are determined and presented in a graph against the duration of stress in Fig. 3g. It is observed that the positively stressed mobility values vary linearly with increasing stress durations, unlike the case for negatively stressed mobility values. We have also estimated the carrier doping densities of ~1012 cm−2 for different stress time durations. It may also be noted that the doping concentrations in our WS2 mem-transistors increases with increasing positive stress times as shown in Supplementary Fig. 5.

The existence of hysteresis in the transistor current suggests a dynamic characteristic, which we investigate in Supplementary Fig. 6 by measuring transfer curves with varying sweep rate and range. It may be deduced that since this is an analog memory, changing the voltage sweep range and step size will have an impact on the extinction ratio and hysteresis window because the effective program time will change drastically. We observe an interesting trend by varying the sweep rate from 2 V/s to 0.1 V/s and the range from ±20 V to ±50 V. As the sweep range (rate) is increased (decreased), the current jump observed in the forward sweep becomes more significant. However, a considerable increase in the overall current level is observed toward a lower sweep rate in the backward sweep case, indicating the existence of distinct time scales for different segments of the hysteresis curve. To further probe the dynamics, we terminate the backward sweep at an intermediate gate voltage (Vbghold) and closely observe the time-dependent fluctuations of Ids over a specific time interval prior to recommencing the sweep as shown in Fig. 4a–d when we hold at 20 V, the drain current increases by approximately ~102, whereas holding at 10 V for 20,000 s can elevate the current level to the order of ~10. In contrast, holding at negative Vbghold can decrease the current level. Furthermore, Fig. 4e displays the temporal evolution of the current achieved at distinct Vbghold levels. Upon halting at a positive Vbghold, a gradual increase in the drain current is witnessed over a prolonged time period. However, holding at Vbghold = 0 V, we observe no significant alterations in drain current values after the holding period, indicating zero gate bias as an ideal condition for READ voltage. For the negative Vbghold, the current exhibits a remarkably rapid decrease in a time frame that is several orders of magnitude shorter. These findings are in sharp contrast to the transient analysis reported earlier, where no current rises were observed for any Vbghold cases36. Additionally, we showcase an alternative trial by altering the Vbg sweep amplitudes to accomplish discrete PROGRAM states. As depicted in Fig. 4f, a rise in the positive Vbg from 10 V to 50 V leads to an increase in the hysteresis window and extinction ratios, with the expectation of achieving diverse PROGRAM states. While conducting a dual sweep, we execute retention measurements at Vbg = 0 V to observe the loss of carriers over time. However, the satisfactory retention behavior of over 104 for various PROGRAM states, as demonstrated in Supplementary Fig. 7, exemplifies the exceptional dynamic behavior of charge injection and release of our ion-gated WS2 mem-transistor.

The effect of hold voltage on the hysteretic behavior is demonstrated. Initially, the gate voltage is swept from the negative to positive voltage range, and during the backward sweep, it is halted at a specific intermediate voltage called Vbghold: a 20 V, b 10 V, c 0 V, and d −10 V. Then, the current progression is recorded over a period exceeding 20,000 s. After the hold, the sweep is resumed, and the gate voltage returns to the negative range. The hysteresis curve is indicated in green color before the hold and is represented by orange after the delay. e The Ids vs. time measured during the hold phase of the experiments demonstrated in (a–d). f Dual sweep transfer curves leading to distinct PROGRAM states by varying Vbg amplitudes.

Robustness of nonvolatile memory in ion-gated transistors

The WS2-based mem-transistors are subjected to endurance tests, wherein more than 100 hysteresis cycles with varying sweep rates are performed. As shown in Fig. 5a, the tests reveal that our memory device sustains high on/off ratios without significant decay, demonstrating its superior memory capacity and reliability. In addition, we have extracted the forward and backward mobilities and the threshold voltage shifts (∆Vth), of the WS2 channel from the transfer curves acquired at a sweep rate of 0.5 V/s, which have been briefly summarized in Supplementary Fig. 8. The mobilities and ∆V values of 100 hysteresis cycles demonstrate the reliability of these memory devices, with minimal fluctuation bands. Transfer curves have been obtained for eight different devices to establish stability amidst device-to-device variations. The extracted parameters, encompassing extinction ratios and memory windows (∆V) of different devices, are depicted in Fig. 5b. The large extinction ratios observed in these ionotronic memory devices concur with the previous reports based on the floating gate and electrolyte-gated mem-transistors13,19,25. An additional performance index of a durable memory device is its retention behavior over an extended duration. In this particular case, the retention characteristics following PROGRAM (a pulse of +50 V, 4 s) and ERASE (a pulse of −50 V, 4 s) operations have been illustrated in Fig. 5c. Our device exhibits an stable extinction ratio exceeding 106 after 2000 s at elevated temperatures, thereby opening up opportunities for practical device applications in innovative nonvolatile memories. Building memory devices that can operate at high temperatures offers numerous challenges, including the shortened data retention time resulting from increased thermal screening41. Additionally, an augmented carrier trapping and de-trapping leads to significant off-state currents, which results in lower on/off ratios30. To our knowledge, no report on such high-temperature retention characteristics with a larger extinction ratio is available. Furthermore, we investigate the programmable cyclic endurance of the device by applying alternating positive and negative pulses. The applied periodic waveform includes a PROGRAM (5 V, 1 s) pulse, followed by a READ (0 V, 1 s) pulse, and then an ERASE (–40 V, 1 s) pulse followed by another similar READ pulse, as shown in Fig. 5d. The high/low conductive READ currents remain nearly invariant even after subjecting the devices to 400 periodic cycles, indicating the exceptional endurance properties of these memory devices. Here, the mechanism involved in the 2D WS2 nonvolatile memory devices opens up broader possibilities to use 2D semiconductors for robust data storage applications.

a The endurance tests of 100 dual sweep hysteresis cycles for varied sweep rates. The gate voltages are swept from −50 V to +50 V and back to again −50 V. Transfer curves (black) of faster sweep rates introduce a stable extinction ratio of 102, whereas the Transfer curves (black) of slower sweep rates provide a stable Ion/Ioff ratio of 104. b Extracted parameters, i.e., Ion/Ioff ratios (orange) and memory windows (∆V) (green) of transfer curves from 8 different devices illustrating device-to-device variations (the error bars represent the standard error of the mean). c Retention characteristics of the device after PROGRAM (pulse of +50 V, 4 s) and ERASE (pulse of −50 V, 4 s) operations for 2000 s. d The ionotronic memory device over 400 cycles of operations showing endurance characteristics of the programmable waveforms at (0 V, 1 s) READ pulse (orange) succeeded by a (5 V, 1 s) PROGRAM pulse. After that, an ERASE pulse of (–40 V, 1 s) is supplied, and another READ pulse (green) for 1 s is followed. The orange (green) triangles represent High (low) conductive READ currents in each cycle.

Dynamic response and paradigm of multibit storage

Multibit memories, featuring the capacity to stockpile over a solitary bit of data within a single device, have been widely acknowledged as an effective mechanism to amplify the data retention ability in forthcoming miniaturized electronics. To examine the dynamic response of our memory device, we alter the Vbg pulses in a programmable operation, fluctuating between ±40 V for a duration of 1 s, as depicted in Fig. 6a. The switching process between READ states subsequent to each PROGRAM/ERASE cycle is accomplished via the attrition of Na+ ions in the vicinity of the WS2/SiO2 interface. At the same time, the drain is grounded, and the source is biased at 1 V. The device is first set to the OFF state (~10−10 A) by implementing a high negative gate voltage (Vbg = −40 V) pulse. To activate the device, a positive voltage pulse of 40 V for 1 s causes attrition of charges in the WS2 channel, signified by the ∼10−6 A current surge. Upon resetting the gate voltage to 0 V, the device persists in a high conductive READ level with a steady OFF current of ~10−8 A. The imposition of a similar negative pulse of -40V for 1 s restores the initial OFF state (~10−10 A), also called a low conductive READ state. To attain a storage capacity of n-bits, a mem-transistor must comprise no less than 2n distinct storage levels42. These devices can be exploited for a 2-bit storage potential that mandates 4 data levels. Figure 6b depicts four Vbg operations implemented to configure our mem-transistor into 4 data states (“00,” “10,” “01,” “11”). The Vbg pulses denoted by “00” and “11” correspond to the pulses employed to establish the device into binary “ERASE” and “PROGRAM” states, respectively. However, the Vbg pulses for collecting the “01” and “10” state are combinational, consisting two successive pulses of (-40 V, 1 s) and (40 V, 1 s) and vice versa. These operations generate two additional intermediate PROGRAM states with stable READ currents traversing four orders of current magnitudes across the spectrum. The conservation of the corresponding READ states is additionally probed for 2000 s at a steady drain-source bias of 2 V, as depicted in Fig. 6b. By scrutinizing their time-dependent behavior, it can be inferred that ion-gated transistors based on 2D materials can cater to the pressing need for high-temperature multi-level storage devices.

a Switching between PROGRAM (P, high current, device ON, red circles) and ERASE (E, low current, device OFF, green triangles) states (lower panel) induced by the application of alternating Vbg pulses (\(\pm\)40 V,1 s), upper panel. The READ (R) operations are performed by using Vbg = 0 V. The high (low) conductive READs are blue triangles (black squares). b Vbg pulses used for programming the mem-transistor into 4 distinguishable storage states (“00,” “01,” “10,” “11”), i.e., a 2-bit memory device. Retention characteristics of 4 states are also shown for 2000 s at Vbg = 0 V and Vds = 1 V. c Transient drain current memory operations by using a combinational gate pulse of various amplitudes, i.e., 5 V, 10 V, 30 V, 40 V, and 50 V, displaying over 64 distinct current levels. d The retention of 64 conductance states for more than 1000 s, taken at Vbg = 0 V, Vds = 2 V.

The extinction ratios and retention capabilities of these ionotronic WS2 mem-transistors signify the potential of multibit memory with exceptional storage capacities. Although floating-gate multibit memories based on 2D materials, such as MoS2, manifest high switching ratios exceeding 106, the ungovernable laws of the charge trapping mechanism lead to a restricted storage capability with less than 16 storage levels (4 bits)17,18. Nevertheless, the electrolyte-gated transistors exhibit enhanced conductance modulation due to their ion-gating mechanism compared to the electrostatic charge trap phenomena, rendering them suitable contenders for high storage densities43,44. We execute several voltage operations to demonstrate the multibit storage potential of our solid-state ion-gated WS2 mem-transistors. Initially, the device is subjected to repetitive stimulation by a gate pulse of (5 V, 1 s) duration. The phenomenon observed is the gradual increase in storage current with increasing the number of pulses indicating the persistent accumulation of charge carriers in WS2. Furthermore, we utilize combinational gate pulses of various amplitudes, including 5 V, 10 V, 30 V, 40 V, and 50 V, as depicted in Fig. 6c. This approach yielded 65 distinct storage currents, spanning over six orders of magnitude of current levels, thereby revealing the potential for 6-bit data storage capabilities in our ion-gated WS2 mem-transistors compared to existing literature11,12,13,14,15,16,17. Our results, combined with recent studies on multibit memory that use two- and three-terminal device configurations on 2D materials and heterostructures, have been consolidated in Table 1. The table highlights various memory parameters such as retention, extinction ratios, and thermal stabilities.

Notably, our study presents, the capability of achieving such high data storage states (>6 bits) with intriguing memory characteristics at high temperatures (425 K) using NaCl-assisted CVD-grown ML WS2. Figure 6d depicts the stable nonvolatile retention characteristics of 64 storage states, even after 1000 s of programming using combinational gate pulses. We explicitly observe 64 levels spread across six orders of current, with discernible gaps between consecutive levels. To further confirm the credibility of all the storage states, we calculated the signal-to-noise ratio (SNR) as illustrated in Supplementary Fig. 9. All the computed ratios surpass the critical limit of SNR = 1, anticipating the validity of the 6-bit ionotronic memory in the present study. Furthermore we have estimated a low energy consumption of <1 pJ in case of our WS2 mem-transistors by modulating several conductance states at pA range. The operation speed can be further improved by using lighter ions such as Li+ and the programming voltage range can be reduced with a top gate architecture. The device’s unwavering dependability and thermal stability can be attributed to the highly effective conductance modulation through ion-gating. Such reliable multi-bit data storage is highly desirable in high performance neuromorphic computing applications45.

Neuromorphic adaptation with proposed WS2 based mem-transistors

The robust multi-bit storage of our proposed WS2 mem-transistors, provides an upper hand in achieving reliable neuromorphic computing at high temperatures, as most previous literatures on ion-gated synaptic transistors are based on room temperature neuromorphic performances7,22,23,24,25,26,27. The proposed WS2 mem-transistor operating at 425 K can be treated as an artificial synapse, and the structural analogy with a biological synapse is illustrated in Fig. 7a. In biological synapses, the information transmits between presynaptic and postsynaptic neurons by sending neurotransmitters across the synapse to dock with receptors on the postsynaptic neuron. If enough neurotransmitters dock with the receptors, a signal is sent down that neuron to generate excitatory post-synaptic current (EPSC). Similarly, in the case of our artificial synaptic device, the gate acts as the presynapse to input modulatory signals through Na+ diffused SiO2, while the drain electrode serves as the postsynapse to measure the EPSC from the WS2 channel.

a Schematic illustration of human and artificial brain synaptic elements. (left: biological synapse operation by pre-synaptic and post-synaptic neurons and right: artificial synapse operation by using the proposed ion-gated WS2-based mem-transistors). b Excitatory postsynaptic current (EPSC) stimulated by gate voltages with an amplitude of 40 V and different duration times (0.1–15 s) showing long-term plasticity. c Emulating long-term potentiation (LTP) and depression (LTD) with consecutive identical pulses of (10 V, 1 s), and (-20 V, 1 s), respectively.

To probe the high-temperature neuromorphic characteristics of WS2 mem-transistors, sequential voltage pulses of equivalent magnitudes (40 V) and diverse time scales (from 0.1 to 15 s) are exerted on the gate electrode as an external action potential at 425 K. The corresponding excitatory postsynaptic current (EPSC) is measured at a fixed Vds of 2 V. As shown in Fig. 7b, positive voltages applied to the gate terminal significantly increase synaptic weights due to the accumulation of Na+ ions at the SiO2/WS2 interface. The EPSCs exhibit an incremental peak value as the duration of the voltage pulses increases in a manner similar to that of biological excitatory synapses6. Moreover, a linear correlation is observed between the duration of the pulse width and the EPSC response, as depicted in Supplementary Fig. 10. Furthermore, we observe negligible decay in post-stimulated read currents attributed to the robust non-volatile EPSC response at 425 K from these ion-gated WS2 mem-transistors. Long-term potentiation (LTP) and depression (LTD), essential for implementations of ANNs in neuromorphic learning, are also emulated at high temperatures by tuning the conductance states of our ionotronic memory devices with repetitive presynaptic stimulation pulses. As depicted in Fig. 7c, the potentiation triggered using successive voltage pulses of 10 V exhibits near linear synaptic weight changes even at elevated temperatures, which entails the robust ion-gating mechanism in our case. Similarly, a depression characteristic is emulated by employing a series of voltage pulses of −20 V, illustrating an inhibitory post-synaptic current behavior. In this process, we anticipate decumulations of Na+ back to the original state under negative gate bias.

On the basis of excellent memory capabilities with key synaptic performances, we explore the potency of our WS2 based memory devices for accurate image recognition by conducting ANN simulations using the open-source Pytorch package46. In this approach, a three-layer neural network is constructed to train and test the hand-written MNIST data sets, as shown in Fig. 8a47. The input, hidden, and output layers are fully connected through 784\(\times\)512\(\times\)10 synaptic weights. The 784 input neurons correspond to the 28\(\times\)28 pixels input MNIST image, whereas the 10 output neurons correspond to the digit ranging from “0” to “9.” Moreover, The multi-bit memory states of our ionotronic device are treated as synaptic weights during the training of 60,000 data sets. Figure 8b shows the nonlinearity factors of LTP and LTD characteristics which are extracted using the following equation48

where \({G}_{{Max}}\) and \({G}_{{Min}}\) represent maximum and minimum conductances, \(\omega\) is an internal variable and \({{\rm{\alpha }}}_{{\rm{p}}},{{\rm{\alpha }}}_{{\rm{d}}}\) are nonlinearity coefficients of potentiation and depression, respectively. In our case, the nonlinearity coefficients obtained from the fitted LTP and LTD curves are 0.63 and 0.1 for potentiation and depression, respectively, consistent with near-ideal device cases (\(\alpha =1\)). These values are key metrics for evaluating the high classification accuracy rate in neural network simulations. The backpropagation algorithm updates the synaptic weights in our ANN module with cross-entropy loss as the cost function at zero bias condition. A nonlinear rectified linear unit (ReLU) activation function is during information propagation from one layer to another. Each training session is repeated 5 times for 70 epochs, and the mean accuracy is plotted against the number of epochs. As displayed in Fig. 8c, the validation accuracy reached over 90% after training for 20 epochs establishing an excellent recognition rate using our proposed memory devices. Moreover, the maximum accuracy approaches the computational limit of ~98%, which delineates excellent neuromorphic adaptation with superior near-ideal synaptic characteristics in our case, which are also consistent with previous reports49,50. The inset shows the improvement of test accuracy with an increasing number of neurons in hidden layers at a specific epoch. Similar trends are also observed in previous literatures stating the early convergence of our test results with increasing hidden neurons49. To further support the high accuracy obtained in our pattern recognition task, we have computed the confusion matrices shown in Fig. 8d. The resulting confusion matrix can be used to evaluate the performance of our ANN model in terms of output class separability. The diagonal elements denote the normalized ANN model predictions that match the true labels in the test data. The observed high diagonal and low off-diagonal values clearly indicate the class separation capability of our device-based ANN implementation. The proposed ion-gated WS2 mem-transistors in this work offer potential avenues for employing other 2D materials in high-temperature multifunctional nonvolatile memories with extensive storage capacities and future neuromorphic computing applications.

a The schematic of a three-layer ANN structure consisting of the input layer (784 nodes), hidden layer (512 nodes), and output layer (10 nodes) for recognition of MNIST images. b The nonlinearity factors (\({{\rm{\alpha }}}_{{\rm{p}}}\) \({\rm{and}}\) \({{\rm{\alpha }}}_{{\rm{d}}}\)) are extracted from LTP and LTD characteristics. c The recognition accuracy of our synaptic device with respect to training epoch. Software limit is shown for comparison. Inset shows the relation between accuracy with increasing nodes in hidden layers. d Confusion matrix showing the digit classification results for hand-written MNIST training datasets. The diagonal form represents most of the digits are correctly classified.

In summary, we demonstrate a mem-transistor device based on ML WS2 that addresses more than 64 storage states (6 bits) and synaptic operations, emulating biomimetic plasticity. The direct salt-assisted synthesis of ML WS2 on SiO2/Si++ substrate using a cost-effective CVD method has the potential for scalability. In addition, it is advantageous to directly fabricate three-terminal 2D memory devices with robust ion-gating mechanisms and device functionalities. The Na+ diffused SiO2 can be treated as an ionic gating medium instead of dielectric gating at high temperatures due to the thermal activation of mobile Na+ ions. Using band-bending characteristics, we employ a fingerprint mechanism to address the carrier dynamics under electrostatic doping fluctuations induced by local ion movements. The WS2-based ionotronic memory is equipped with endurance tests (>400 pulse cycles), 105 extinction ratio with stable retention, low device-to-device variations, and 64 distinct nonvolatile storage levels with reliable signal-to-noise ratios using combinational pulses. It also leverages the high-temperature potential memory applications in harsh electronics as demanded in aerospace, military, and automotive industries. We also demonstrate the excitatory postsynaptic current with varying time scales, near linear potentiation, and depression for successful implementation in ANNs. We anticipate that the simple and cost-effective synthesis and fabrication methods presented in this work would substantially enhance the distinctive attributes of WS2 and other emerging layered 2D materials, thus representing potential for their advancement as scalable memory solutions. The associated bio-inspired synaptic capability delineates a viable path to constructing next-generation 2D mem-transistors towards advanced computing platforms at high temperatures.

Methods

Growth of ML WS2

The ML WS2 is synthesized using a salt-assisted CVD technique in a single-zone tube furnace (Carbolite 1200) with a 2-inch diameter quartz tube, as shown in Supplementary Fig. 1. In this specific experiment, high purity NaCl (99%, SRL) and WO3 (99.998%, Alfa Aesar) powders are used as metal precursors and sulfur (99.995%, Alfa Aesar) powder is used as a chalcogen source. These precursors are placed in separate alumina boats. The SiO2 (285 nm)/Si (1 × 1 cm2) substrate is cleaned using the ultrasonication method with acetone, isopropyl alcohol, and de-ionized (DI) water, followed by drying with pressurized dry N2 (99.999%) to eliminate any moisture. Before placing the cleaned substrate face down on the boat with the precursors, the precursor (WO3+NaCl) height is adjusted to minimize the distance between the precursor and growth substrate to 3 mm, to channelize the sulfur feeding during the growth period. The boat containing the growth substrate and precursors is then moved to the center of the furnace, while the boat containing sulfur is placed upstream. The tube is initially pumped down to 0.2 mbar, and then purged three times with 500 sccm of high-purity Ar (99.999%) to eliminate any oxygen contaminants inside the tube. The system is heated to 900 °C at a ramp speed of 30 °C/min using Ar (75 sccm) as the carrier gas. The pressure inside the tube is maintained at 500 mbar throughout the 10 min growth time. Finally, the system is cooled down rapidly to ambient temperature by partially opening the furnace.

Raman and PL spectroscopy

The Raman spectra are collected with a confocal micro-Raman spectrometer (Renishaw Invia) using a laser excitation wavelength of 532 nm in a backscattering configuration employing an ~100x (NA = 0.8) objective. The laser power on the sample was kept low to avoid local heating. The laser exposure time on the sample is kept fixed for 10 s with 2 accumulations. However, to obtain PL spectra, the exposure time is reduced to 1 s to avoid local heating during the spectral acquisition.

Device fabrication

The ML WS2 based mem-transistors are fabricated by using a photolithography (Heidelberg μPG 101) system. Initially, the salt-assisted CVD grown WS2 samples on SiO2/Si substrate are coated with a positive photoresist (ma-p-1205) by a spin coater (SUSS Microtech) and then baked at 80 °C for 1 min. Under the inspection of a high-resolution microscope, the contact patterns of several channel lengths are exposed on the ML WS2 flakes with a 405 nm laser in photolithography. The exposed patterns are developed with an alkaline solution (1:4, NaOH:DI water) for 1 min. The sample is then mounted on a thermal evaporation chamber for the deposition of the silver (Ag) electrode followed by dissolution of residual resists in acetone for 10 min, known as lift-off process. The heavily p-doped silicon functioned as the gate electrode and 285 nm SiO2 functioned as the gate dielectric. Before taking all the electrical measurements for this work, the devices are annealed at 200 °C for 36 h in a high vacuum (~10−6 mbar) condition.

Electrical characterization

The fabricated device is mounted on a cryogenic four-probe station (Lake Shore) to probe the top and bottom electrodes. The chamber is maintained at a high vacuum of ~10−6 mbar during all the measurements. For electrical characterization, a semiconductor parameter analyzer system (Keithley 4200A-SCS) is used. A high-speed pulse generator module 4220-PGU and measurement unit 4225-PMU integrated within Keithley 4200 system are used for electrical pulse characterization. In order to prevent photo-excitation of charge carriers, all experiments are performed in dark conditions.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Hou, X., Chen, H., Zhang, Z., Wang, S. & Zhou, P. 2D atomic crystals: a promising solution for next-generation data storage. Adv. Electron. Mater. 5, 1800944 (2019).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Migliato Marega, G. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

Xue, F. et al. Integrated memory devices based on 2D materials. Adv. Mater. 34, 2201880 (2022).

Sahu, M. C., Sahoo, S., Mallik, S. K., Jena, A. K. & Sahoo, S. Multifunctional 2D MoS2 optoelectronic artificial synapse with integrated arithmetic and reconfigurable logic operations for in-memory neuromorphic computing applications. Adv. Mater. Technol. 8, 2201125 (2023).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Lee, D. et al. Multibit MoS2 photoelectronic memory with ultrahigh sensitivity. Adv. Mater. 28, 9196–9202 (2016).

Lee, J. et al. Monolayer optical memory cells based on artificial trap-mediated charge storage and release. Nat. Commun. 8, 1–8 (2017).

Wang, Q. et al. Nonvolatile infrared memory in MoS2/PbS van der Waals heterostructures. Sci. Adv. 4, eaap7916 (2018).

Yang, Z. et al. High-performance photoinduced memory with ultrafast charge transfer based on MoS2/SWCNTs network van der Waals heterostructure. Small 15, 1804661 (2019).

Tran, M. D. et al. Two-terminal multibit optical memory via van der Waals heterostructure. Adv. Mater. 31, 1807075 (2019).

Huang, W. et al. Multibit optoelectronic memory in top-floating-gated van der Waals heterostructures. Adv. Funct. Mater. 29, 1902890 (2019).

Gao, F. et al. Low optical writing energy multibit optoelectronic memory based on SnS2/h-BN/graphene heterostructure. Small 17, 2104459 (2021).

Liu, C. et al. Polarization-resolved broadband MoS2/black phosphorus/MoS2 optoelectronic memory with ultralong retention time and ultrahigh switching ratio. Adv. Funct. Mater. 31, 2100781 (2021).

Wen, J. et al. Direct charge trapping multilevel memory with graphdiyne/MoS2 van der Waals heterostructure. Adv. Sci. 8, 2101417 (2021).

Zhang, Z. C. et al. An ultrafast nonvolatile memory with low operation voltage for high-speed and low-power applications. Adv. Funct. Mater. 31, 2102571 (2021).

Li, Y. et al. Low-voltage ultrafast nonvolatile memory via direct charge injection through a threshold resistive-switching layer. Nat. Commun. 13, 1–9 (2022).

Lai, H. et al. Photoinduced multi-bit nonvolatile memory based on a van der waals heterostructure with a 2D-perovskite floating gate. Adv. Mater. 34, 2110278 (2022).

Zhu, K. et al. Hybrid 2D/CMOS microchips for memristive applications. Nature 618, 57–62 (2023).

Yang, C. Sen et al. A synaptic transistor based on quasi-2D molybdenum oxide. Adv. Mater. 29, 1700906 (2017).

Jiang, J. et al. 2D MoS2 neuromorphic devices for brain-like computational systems. Small 13, 1700933 (2017).

Yang, C. Sen et al. All-solid-state synaptic transistor with ultralow conductance for neuromorphic computing. Adv. Funct. Mater. 28, 1804170 (2018).

Zhu, J. et al. Ion gated synaptic transistors based on 2D van der Waals crystals with tunable diffusive dynamics. Adv. Mater. 30, 1800195 (2018).

Yao, B. W. et al. Non-volatile electrolyte-gated transistors based on graphdiyne/MoS2 with robust stability for low-power neuromorphic computing and logic-in-memory. Adv. Funct. Mater. 31, 2100069 (2021).

Park, B. et al. Robust 2D MoS2 artificial synapse device based on a lithium silicate solid electrolyte for high-precision analogue neuromorphic computing. ACS Appl. Mater. Interfaces 14, 53038–53047 (2022).

Li, Y. et al. Electrolyte-gated transistors with good retention for neuromorphic computing. Appl. Phys. Lett. 120, e2003018 (2022).

Wang, B. et al. Monolayer MoS2 synaptic transistors for high-temperature neuromorphic applications. Nano Lett. 21, 10400–10408 (2021).

Schroder, D. K. & Babcock, J. A. Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing. J. Appl. Phys. 94, 1 (2003).

Watson, J. & Castro, G. A review of high-temperature electronics technology and applications. J. Mater. Sci. Mater. Electron. 26, 9226–9235 (2015).

Mallik, S. K. et al. Salt-assisted growth of monolayer MoS2 for high-performance hysteresis-free field-effect transistor. J. Appl. Phys. 129, 145106 (2021).

Huang, X. et al. Quantitative analysis of temperature dependence of Raman shift of monolayer WS2. Sci. Rep. 6, 1–8 (2016).

McCreary, K. M. et al. The effect of preparation conditions on Raman and photoluminescence of monolayer WS2. Sci. Rep. 6, 1–10 (2016).

Kaushik, V. et al. Charge transport in 2D MoS2, WS2, and MoS2-WS2 heterojunction-based field-effect transistors: role of ambipolarity. J. Phys. Chem. C 124, 23368–23379 (2020).

Abraham, M. & Mohney, S. E. Annealed Ag contacts to MoS2 field-effect transistors. J. Appl. Phys. 122, 115306 (2017).

He, G. et al. Thermally assisted nonvolatile memory in monolayer MoS2 transistors. Nano Lett. 16, 6445–6451 (2016).

Kaushik, N. et al. Reversible hysteresis inversion in MoS2 field effect transistors. npj 2D Mater. Appl 1, 1–9 (2017).

Mallik, S. K. et al. Thermally driven multilevel non-volatile memory with monolayer MoS2 for brain-inspired artificial learning. ACS Appl. Mater. Interfaces 15, 36527–36538 (2023).

Lan, C. et al. The origin of gate bias stress instability and hysteresis in monolayer WS2 transistors. Nano Res. 13, 3278–3285 (2020).

Xu, K. et al. Electric double-layer gating of two-dimensional field-effect transistors using a single-ion conductor. ACS Appl Mater. Interfaces 11, 35879–35887 (2019).

Li, Y. et al. Filament-free bulk resistive memory enables deterministic analogue switching. Adv. Mater. 32, 2003984 (2020).

Chen, M. et al. Multibit data storage states formed in plasma-treated MoS2 transistors. ACS Nano 8, 4023–4032 (2014).

Bisri, S. Z., Shimizu, S., Nakano, M. & Iwasa, Y. Endeavor of iontronics: from fundamentals to applications of ion-controlled electronics. Adv. Mater. 29, 1607054 (2017).

Lee, S. J. et al. Programmable devices based on reversible solid-state doping of two-dimensional semiconductors with superionic silver iodide. Nat. Electron. 3, 630–637 (2020).

Li, D., Ryu, B. & Liang, X. A study on MoS2-based multilevel transistor memories for neuromorphic computing. Appl. Phys. Lett. 117, 213102 (2020).

Paszke, A. et al. PyTorch: an imperative style, high-performance deep learning library. Adv. Neural Inf. Process. Syst. 32, 8026–8037 (2019).

Deng, L. The MNIST database of handwritten digit images for machine learning research. IEEE Signal Process. Mag. 29, 141–142 (2012).

Hao, S. et al. Monolayer MoS2/WO3 heterostructures with sulfur anion reservoirs as electronic synapses for neuromorphic computing. ACS Appl. Nano Mater. 4, 1766–1775 (2021).

Jena, A. K. et al. Bipolar resistive switching in TiO2 artificial synapse mimicking Pavlov’s associative learning. ACS Appl. Mater. Interfaces 15, 3585 (2022).

Seo, S. et al. The gate injection-based field-effect synapse transistor with linear conductance update for online training. Nat. Commun. 13, 1–10 (2022).

Gwon, O. H. et al. Systematic design and demonstration of multi-bit generation in layered materials heterostructures floating-gate memory. Adv. Funct. Mater. 31, 2105472 (2021).

Jia, M. et al. Multibit tribotronic nonvolatile memory based on van der Waals heterostructures. Nano Energy 83, 105785 (2021).

Wang, M. et al. Robust memristors based on layered two-dimensional materials. Nat. Electron. 1, 130–136 (2018).

Acknowledgements

S.S., G.K.P., and R.P. thank the Science and Engineering Research Board for partial financial support (CRG/2020/006190). The authors acknowledge the use of the Micro-Raman facility at the central research facility (CRF) of KIIT Deemed to be University, Bhubaneswar.

Author information

Authors and Affiliations

Contributions

The project was conceptualized by S.S. and S.K.M. and S.S. supervised the project. S.K.M. and R.P. carried out the CVD growth, device fabrications. S.K.M. performed Raman and PL experiments. S.K.M. and R.P. carried out temperature-dependent transport measurements. S.K.M. and M.C.S. analyzed the experimental data. S.K.M., G.K.P., P.K.S., S.P.D., and S.S. carried out formal analysis and scientific discussions. S.K.M. wrote the manuscript with input from all the authors. The final manuscript was reviewed by all the authors.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mallik, S.K., Padhan, R., Sahu, M.C. et al. Ionotronic WS2 memtransistors for 6-bit storage and neuromorphic adaptation at high temperature. npj 2D Mater Appl 7, 63 (2023). https://doi.org/10.1038/s41699-023-00427-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-023-00427-8