Abstract

The ability to couple the in-plane (IP) and out-of-plane (OOP) dipole polarizations in ferroelectric In2Se3 makes it a promising material for multimodal memory and optoelectronic applications. Herein, we experimentally demonstrate the cross-field optoelectronic modulation in In2Se3 based field-effect devices. Surface potential measurements of In2Se3 based devices directly reveal the bidirectional dipole locking following high gate voltage pulses. The experimental evidence of hysteretic change in the IP electrical field facilitating a nonvolatile memory switch, was further explored by performing photocurrent measurements. Fabricated photodetectors presented multilevel photocurrent characteristics showing promise for nonvolatile memory and electro-optical applications.

Similar content being viewed by others

Introduction

Since the successful isolation of graphene1 and subsequent discovery of its exceptional mechanical, thermal, and electrical properties, substantial research interest has been enthroned on various two-dimensional (2D) materials2,3 placing them in the forefront of modern science. Among the properties under scrutiny is room temperature ferroelectricity, due to its potential application in a wide range of fields such as nonvolatile phase change memory4,5, energy harvesting6, strain tuned electronics7, artificial brain8, neuromorphic sensors9, etc. Although the traditional ferroelectric materials, e.g., BaTiO310, BiFeO311, and PbTiO312 have been used for decades, the presence of surface dangling bonds, high leakage current in thinner form, and their complex fabrication process limit their potential integration for nanoelectronics. This emphasizes the need for 2D counterparts that are free from such constraints along with having superior ferroelectric properties to realize sub-10-nm ferroelectric devices, applicable for high-density storage and low power consumption. The list of 2D ferroelectric materials that were isolated so far includes 1T-MoS213, (M)Mo,WTe214,15, CuInP2S616, SnTe17, and 2H α-In2Se318. Among these, 2H α-In2Se3 exhibits stable ferroelectricity at room temperature, which is essential for practical ferroelectric-based devices19. Although the current levels in typical In2Se3 based electronic devices are relatively low (~nA), recently In2Se3 based electronic devices have utilized ferroelectric effect to replicate neuromorphic devices by realizing artificial synapse20. Moreover, its predicted21 stable intercoupled in-plane (IP) and out-of-plane (OOP) ferroelectricity paves the way for controlling the device functionality in nonconventional ways. α-In2Se3 is a III–VI compound semiconductor comprising of five atomic layers of Se-In-Se-In-Se with a direct bandgap of ~1.4 eV22, making it a prime candidate for low-power electronics. Among all the polytypes of In2Se3 (α, β, γ, δ, and κ), the α-phase is recognized to have the most stable crystal structure at room temperature along with prominent ferroelectricity23. The emergence of the ferroelectricity in α-phase arises from the different interatomic layer spacing between the central Se layer and the adjacent In layers resulting in the centrosymmetry breaking21. Recently, researchers have reported experimental evidence of both IP24 and OOP18 ferroelectricity in α-In2Se3 using piezoelectric force microscopy (PFM). Although the existence of intercoupled IP and OOP ferroelectricity has been reported by few groups25,26 for α-In2Se3 nanoflakes, many open questions regarding the nature of the dipole switching, dipole locking after removal of an external field, and their influence in modulating the optoelectronic properties in this material still remain unanswered.

Recently, Kelvin probe force microscopy (KPFM) has come to the forefront for 2D materials characterization and has been widely used to accurately determine mobility27, dopant distribution28,29,30, evaluation of charge carrier distribution31, etc. Several groups have used KPFM to resolve pinch-off formation32 and determine potential profiles across semiconductor channels in field-effect transistors (FETs)27,33. Its capability to probe the local surface potential and to provide quantitative information about the remnant polarization in ferroelectric thin films34,35 open the door towards the exploration of intercoupled ferroelectric behavior in 2D semiconductors.

In this study, we demonstrate the cross-field optoelectronic modulation of ferroelectric In2Se3 based FET devices. IP variations of the electric field along the device channel were realized by gate electrode actuation of the OOP electric field at room temperature. Our observations based on detailed surface potential measurements using KPFM shed light on the dynamics of the intercoupled dipole modulation. Moreover, at higher OOP field strengths, the modulated dipoles maintained the state even after the withdrawal of bias voltage, essentially leading to dipole locking. Nonvolatile multilevel photoresponse of α-In2Se3 based phototransistors was demonstrated following different withdrawn gate voltages, which correspond to different OOP fields. Remarkably, the photocurrent showed significant modulation ranging from 19.38 ± 0.32 nA for an unpoled device to that of 10.84 ± 0.31 and 28.15 ± 0.62 nA for poled devices (negative and positive gate pulses, respectively). The herein presented electronic dipole coupling and its modulation can be utilized to fabricate functional multimodal memory devices based on FET architectures with far-reaching potential for logic, memory, and optoelectronic applications.

Results and discussions

Material characterization

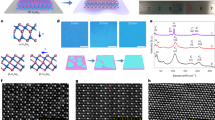

Few layers of In2Se3 flakes were exfoliated onto a conductive- Si wafer covered by 300 nm thermal oxide (Supplementary Fig. 1). Figure 1a shows the AFM topography of a typical flake comprising a height of ~ 40 nm and lateral dimensions of ~ 10 µm (inset of Fig. 1b). Additional AFM topography images for other measured flakes (Supplementary Fig. 2a, b) in addition to optical images (Supplementary Fig. 2c) and Raman maps (Supplementary Fig. 2d–f) show no significant unevenness or contamination on the surface. Figure 1b presents the Raman spectrum of the In2Se3 flake exhibiting prominent peaks at 89, 104, 178, and 192 cm−1, which are the signature peaks for the α phase26,36,37. The characteristic peak at 104 cm−1 can be attributed to A1(LO + TO) phonon modes and the peaks at 178 and 192 cm−1 can be attributed to A1(LO) and A1(TO) phonon modes, respectively. In addition, the peak at 89 cm−1 confirms it to be 2H α-In2Se3 with hexagonal symmetry38. The presence of the A1(LO) and A1(TO) modes at 178 and 192 cm−1 caused by the LO − TO splitting indicates a lack of inversion symmetry in the structure, thus proving the material to be ferroelectric. The emergence of the intercoupled IP and OOP polarizations25 is a consequence of the lack of centrosymmetry in the quintuple layered van der Waals structure. Insets in Fig. 1c, d show the 2D structure of α-In2Se3 crystal arrangement with In atom as blue circles and Se atom as red circles. The relative displacement of the central Se atom, marked by a dotted black circle, with respect to the In atoms, breaks the centrosymmetry providing two energetically degenerate states with opposite OOP electric polarization and IP asymmetry with reverse second-order nonlinear polarization39.

a top—AFM topography of α-In2Se3 flake on a Si/SiO2 substrate with Cr/Au electrodes deposited by e-beam lithography, bottom—Height profile of the flake along the red dotted line shows the height to be ~40 nm, b Raman spectra of α-In2Se3 flake with prominent peaks at 89, 104, 178, and 192 cm−1; inset shows the optical image of the flake and the red dot denotes the point of the Raman measurement. Scale bar is 10 µm. Schematic of the KPFM experimental setup for positive (c) and negative (d) applied back gate voltage bias with source and drain grounded. The insets illustrate the respective crystal structures for the alternating bias conditions with intercoupled IP and OOP polarizations in the sample (the directions of which are marked by the red arrows). Measured surface potential along the α-In2Se3 channel for (e) positive and (f) negative applied gate bias.

Surface potential properties of electronically polarized α-In2Se3

For device testing, back gated FETs were fabricated based on exfoliated α-In2Se3 flakes on SiO2/Si substrate (see Methods). The surface potential measurement of an individual FET device, marked as D1, is schematically shown in Fig. 1c, d. Figure 1e, f present the measured surface potential across the device channel for positive and negative gate polarities, respectively. Both source and drain contacts were grounded throughout the measurement. The nonequivalence of the drain potentials in the figure can be attributed to a convolution effect33 that the metal electrode of ~1 µm in width footprint encounters. Such a strong effect was previously demonstrated for silicon nanowire-based field-effect devices31,33. Thus, even though the real drain potential should be similar to the source electrode, its measured potential eventually increases. In addition, the metal contact height ~50 nm, can potentially result in an incomplete screening of the potential below the electrodes40 which might strongly arise due to induced dipoles below the metal. The distinct alternating slopes of the surface potential manifest the modulation of the IP dipoles as a result of different polarities of the OOP gate-induced electrical fields35,41. Figure 2a, b present the surface potential distributions of α-In2Se3 FET marked as D2 for various selected applied back gate voltages and the individual cross-sectional potential profiles across the device channel, respectively. We note that the potential variations across the channel for different applied gate potentials in Fig. 2a are vertically shifted to fall within the range of 0.1–0.4 V for better visualization. The corresponding electric fields across the device channel E(x) are extracted by taking the potential slope -\(\frac{{d({\mathrm{Surface}}\,{\mathrm{Potential}})}}{{dx}}\) for each back-gate voltage, where x is the distance along the semiconductor channel (Fig. 2c). The observed potential variations at the metal-semiconductor interface are attributed to the Schottky barrier formation at the interface27. Due to the distinct Schottky barrier at the metal-semiconductor interface, only the surface potential away from the junctions (marked with a semitransparent red box in Fig. 2b) is taken into consideration to have an accurate estimation of the electric field in the channel independent of the effect of metal contacts. We note, that while for most measured devices the potential across the channel was virtually zero for zero applied back-gate voltage, few devices showed an asymmetric potential dependence with an initial nonzero potential slope. The emergence of a distinct slope of the surface potential due to variable OOP gate voltages is indicative of an induced electric field in the IP direction. We observed a gradual increase in E(x) arising from the increasing OOP applied bias, which eventually modulates the IP dipoles. For an ideal monolayer system, when a positive (negative) voltage is applied on the gate, the central Se atoms in the van der Waals structure are attracted (repelled) towards the bottom (top) In atom, leading to the crystal configuration in the inset of Fig. 1c, (d). This creates a net dipole in the system with effective negative (positive) charges accumulating near the interface of α-In2Se3/SiO2 and results in an OOP dipole polarization, the directions of which are exhibited in the inset of Fig. 1c, (d). Due to the intercoupled IP and OOP dipoles nature25, the IP dipoles are also reconfigured (Supplementary Fig. 3). Although our system contains tens of layers, the same phenomenon stands true for all individual layers giving rise to similar modifications generating a significant net dipole moment.

a Surface potential maps across the α-In2Se3 channel for different gate bias conditions. b Surface potential profiles across the channel for various gate biases ranging from VG = −7 V to VG = 20 V. The semi-transparent blue boxes indicate the source and the drain positions. c Effective IP electric field calculated from a section of the line profiles away from electrodes (marked by semi-transparent red quadrilateral) in Fig. 2b as a function of applied gate voltage. The orientation of the electric field is attributed to the orientation of the IP dipoles (indicated by the inset images).

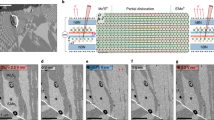

In order to establish a framework for the interpretation of the experimental results and to relate it to polarization, TCAD Sentaurus modeling has been used to solve the potential variations as a consequence of the induced polarization in the In2Se3 field-effect device. The model (details in supplementary) is based on transforming the strain-field distribution of α-In2Se3 to polarization as a function of the applied field on the basis of the symmetry group of α-In2Se3, which has an important role on the intercoupling piezoelectric response. The intercorrelation between IP and OOP polarization under different applied back gate potentials and the corresponding surface potential across the In2Se3 channel has been simulated for different piezoelectric coefficient values of e13 and e33, all of which are shown in Supplementary Fig. 12. The simulated surface potentials are in excellent agreement with our experimental results. To test the bidirectional hysteretic modulation and repeatability of the phenomenon, surface potentials following high gate pulses of alternating polarities were measured in another α-In2Se3 FET marked as D3. Figure 3a shows two potential profiles measured at zero gate voltage following VG = 100 V and VG = −100 V pulses marked with gray and red colors, respectively. Due to experimental limitations, surface potentials at live gate voltages were limited to ~ ±20 V. Repeated switching of the gate bias demonstrated the repeatability of the induced electric fields across the device (Fig. 3b). The average IP field strength following applied gate bias of +100 V was found to be ~ 32 mV/µm, while that for −100 V gate bias was ~ −42 mV/µm (dotted blue lines mark the average field). The consistent IP field modulation profoundly establishes both bidirectionality and repeatability of the dipoles switching using applied gate bias and is attributed to polarization locking imposed by the unique covalent bond configuration of α-In2Se3 crystal39. Most studied ferroelectrics usually show very low ionic conductivity at room temperature42, however, the observed IP dipole locking rules out any contribution of ionic conductivity in α-In2Se343. Therefore, the observed cross-field electronic switching can be attributed to the intercoupled polarizability of α-In2Se3. To support our study, PFM measurements were performed on both pristine and field-effect devices based on In2Se3 to demonstrate the polarization change as a consequence of the applied gate potential (Supplementary Figs. 8 and 9). To study the dipole variations as a function of applied IP electrical field, a voltage was applied to the source and drain electrodes one at a time respectively, while keeping the back-gate contact grounded. Figure 3c, d show the induced IP electrical field measured at zero source-drain voltage after the removal of a bias voltage of +50 V (black squares) and −50 V (red squares), at the source and the drain electrodes, respectively. It is evident from the figures that although an IP field is induced in the material, its magnitude is lower compared to the values for OOP applied voltages. This can be attributed to the significantly stronger IP polarization in α-In2Se3 with respect to its OOP polarization25. Moreover, the IP field due to a lateral bias (VDS) is spread out across the ~ µm length of the semiconductor, whereas, for the OOP direction, the bias potential (VG) falls across the height of the In2Se3 flake, which is typically ~50 nm for our experiments. Since, we apply a similar range of bias voltages for both the gate and drain terminals, the effective electric field in IP and OOP directions is effectively different. The opposite trends of the IP lateral electric fields for bias on each electrode rules out any instrument-based error of the measured surface potential.

a Potential profiles across α-In2Se3 channel following withdrawn +100 V (gray) and −100 V (red) gate potential. Inset shows the pulse profile of the applied electrical bias, with the arrows denoting the point of measurement after withdrawal of pulse (pulse duration was 6 s). b Extracted IP electric field across the channel following four cycles of applying alternating gate bias of +100 V (black squares) and −100 V (red square). c Extracted IP electric field across the channel following four cycles of applying a bias of +50 V (black squares) and −50 V (red squares) on the left electrode (Source) with all other terminals grounded. d Extracted IP electric field across the channel following four cycles of applying a bias of +50 V (black squares) and −50 V (red squares) on the right electrode (Drain) with all other terminals grounded. Error bars comprise the standard deviation (STD) analyzed from the full measured profile.

To further understand the hysteretic nature of the gate induced dipole modulation, the IP electric field across the channel in a device marked as D4 was measured as a function of withdrawn gate voltage cyclically from 0 to −100 V (connected black dots), −80 to 100 V (connected red dots), and 80 to −100 V (connected green dots) (Fig. 4a). The results clearly indicate a significant hysteresis effect following higher withdrawn gate voltages. The hysteresis of the IP field generated by varying the gate strongly adheres to the phenomenon of ferroelectricity44. For lower gate pulses, the dipoles did present IP modulation but relaxed upon withdrawal of the gate bias (Supplementary Fig. 4). Figure 4b shows the temporal variations of the IP field after the withdrawal of gate bias of +100 V (black squares) and −100 V (red squares); the blue dotted lines act as a guide to the eye to display the average trend of the evolution of the IP field with time. It is evident from the figure that the remanence of induced electric fields following the withdrawal of gate voltage for both polarities remain almost constant during the test. In addition, to verify the OOP ferroelectric property, surface potential values after withdrawal of different gate voltages were measured and the results are shown in Supplementary Fig. 7. The hysteretic nature of the resultant plot is indicative of the remnant OOP ferroelectric polarization in the material.

a IP electric field across the α-In2Se3 channel as a function of withdrawn gate voltage. The connected black dots denote electric fields for withdrawn gate voltage from 0 to −100 V, the connected red dots denote electric fields for withdrawn gate voltage from −80 to 100 V and the connected green dots indicate electric fields for withdrawn gate voltage from 80 to −100 V. The direction of the arrows indicates the direction of progression of the scan. b Temporal remanence of the IP electric field after the withdrawal of gate bias. The dotted blue lines show the general trend of the evolution of the electric field with time.

Electronic transport and photoresponse

Following the KPFM measurements, the electrical transport characteristics were examined for the fabricated FET. The output characteristics of the fabricated back-gated FET under dark and illumination are shown in Supplementary Fig. 5a. The output characteristics for varying gate voltages are shown in the supplementary section (Supplementary Fig. 5b). The transfer characteristics of the same device when subjected to different gate sweep voltages show a clockwise hysteresis. Similar clockwise hysteresis has been reported45 as a manifestation of dipole switching in ferroelectric semiconductor field-effect transistors. Interestingly, the hysteresis visibly increases with a greater gate sweep range as can be seen in Supplementary Fig. 5c, which is commensurate with our findings from Kelvin probe measurements. The fact that α-In2Se3 exhibits both semiconducting and insulating ferroelectric properties simultaneously, have already been shown before, which is supported by I-V from one side and surface probe measurements from the other side19,26,46. A possible reason for this could be that the I-V, which acts as an indication to its n-type semiconducting nature is affected significantly by the charge accumulation at the interface between the SiO2 dielectric and the α-In2Se3 channel, whereas, scanning probe measurements are conducted away from this interface i.e., on the surface of the α-In2Se3 which is more insulating.

Next, we employ the gate-based electronic control over the IP and OOP to modulate the photoelectrical characteristics of α-In2Se3. Photoresponse of the fabricated FET was measured immediately after withdrawal of various gate biases ranging from +90 V to −90 V with an interval of 30 V. Figure 5a shows the current through the FET with and without white light illumination (details in the Methods section) before and after withdrawal of various gate voltages. A distinct change in photocurrent was observed following negative and positive gate pulses (Fig. 5b). The photocurrent gradually increases (decreases) for positive (negative) gate pulses due to partial modulation of dipoles. Schematic illustrations explaining the origin of the photoresponse modulations for different conditions following the withdrawal of gate bias are shown in Fig. 5c, d. Under illumination with energy higher than that of the bandgap, generated e–h pairs are separated by the applied drain voltage of −2 V. For the 0 V gate bias condition under illumination, the applied potential across the channel leads to drift of the photogenerated electrons and holes towards opposite electrodes resulting in a net increase in the output current, which accounts for a photocurrent of 19.38 ± 0.32 nA. For illumination following the withdrawal of high gate bias of +90 V and −90 V, as demonstrated previously, the dipoles are locked in a particular orientation with respect to the polarity of the applied bias depending on the intercoupling of the IP and OOP polarizations. Thus, following the withdrawal of +90 V gate bias, IP dipoles line up such that they add an effective electric field between the source and drain electrodes. This facilitates an improved charge collection, resulting in a higher magnitude of photocurrent with respect to the dark current and accounts for a photocurrent of 28.15 ± 0.62 nA. In contrary, for the scenario following the withdrawal of −90 V gate bias, the dipoles align in such a way to reduce the effective field between the electrodes and result in a reduced photocurrent of 10.84 ± 0.31 nA. The rise and fall times of the phototransistor are calculated and shown in Supplementary Fig. 6. Additionally, simulations of photocurrent variations following different gate pulses were carried out using TCAD Sentaurus, the results of which are shown in Supplementary Fig. 12. The change in photocurrent post withdrawal of different gate pulses is in accordance with the results achieved experimentally. Although the photocurrent modulation may be attributed to the photovoltaic effect, in particular since there is an effective field due to dipole modulation, our experiments do not exhibit any switch in the sign of photocurrent with the reversal of polarization as seen in other asymmetric systems47. Thus, the presence of a significant photovoltaic effect that can potentially influence the experiment can be ruled out.

a Temporal response of photocurrent in α-In2Se3 for various gate pulses. Gate pulses were applied for 30 s after which the gate was withdrawn. The measurements were performed with zero applied gate potential and drain voltage of −2 V thereafter. b Photorecurrent as a function of the withdrawn gate voltage pulse. Error bars comprise the standard deviation (STD) for each current level measured over time of light exposure. c, d Schematic illustrations describing the origin for the variable photoresponsivity following the application of negative and positive gate bias, respectively.

In summary, we demonstrated the bidirectional cross-field electronic switching of IP and OOP dipole polarizations in α-In2Se3. Surface potential and piezoelectric force measurements of α-In2Se3 based FET devices directly reveal the dipole modulation and the bidirectional dipole locking following high gate voltages. Furthermore, multilevel photoresponse characteristics are effectively realized by the intrinsic IP field showing great promise for nonvolatile memory and electro-optical applications.

Methods

Sample preparation

α-In2Se3 crystals with 4–6 mm diameter (2D Semiconductors, 99.9999% purity) were used as the source material for mechanical exfoliation. The first few layers of the bulk crystal were mechanically cleaved to eradicate any native oxide layers on the surface. The pristine α-In2Se3 bulk was consequently cleaved again to exfoliate flakes, which were then transferred onto a pre-patterned degenerately p-doped silicon substrate encapsulated with 300 nm Si oxide.

Device fabrication

Standard e-beam lithography [Raith-eLine] followed by electron beam evaporation [Evatec BAK 501 A] were used to fabricate the contact electrodes of 5 nm of Cr and 50 nm of Au. Before metal deposition, the sample was subjected to a mild oxygen plasma [Low-Pressure Plasma System—Diener PCCE] for ~5 s to remove unwanted resist residues. The deposition rate was minimized to ~0.5 Å/s for Cr and ~1 Å/s for Au at the base pressure of ~7 × 10−7 torr to facilitate proper adhesion.

Surface and electrical characterization

Atomic force microscopy (AFM) was conducted to study topography and flake thickness in an N2 filled glovebox (H2O and O2 content <1 ppm) in tapping mode (Dimension-Scanassist, Bruker Inc.). KPFM was conducted in amplitude modulation (AM-KPFM) mode in a two-pass procedure, where surface topography was obtained by standard tapping mode AFM in the first pass followed by an interleaved surface potential measurement in the second pass in the same system. Conductive Pt/Ir-coated cantilever [PPP-EFM-50, NANOSENSORSTM] with ~25 nm tip radius was used for KPFM measurements. Prior to KPFM, the devices were mounted onto a chip carrier and wire bonded to a prototype PCB board. For the gate-dependent KPFM studies, bias was applied (Keysight B1500A) through back-side conducting (p++) Si and the 300-nm-thick SiO2 layer served as the gate dielectric. PFM measurements were conducted on Dimension-Scanassist, Bruker Inc. system in near-contact resonance mode (frequency of ~400 kHz) with conductive Pt/Ir-coated cantilever [PPP-EFM-50, NANOSENSORSTM] tips. For mapping of pristine α-In2Se3, flakes were exfoliated onto a conducting substrate (5 nm Cr/50 nm Au on Si/SiO2) to eliminate electrical charging effects. For mapping devices, the chips were mounted onto a prototype PCB board similar to the process mentioned for KPFM. The electrical measurements of FET devices were carried out using a semiconductor parameter analyzer (Keysight B1500A) and a probe station equipped with an optical microscope. Photoresponse measurements were carried out by illumination with a broadband white light source of spectral range 420–720 nm and an intensity of ~332 µW/cm2.

Spectroscopic characterization

Raman spectroscopy was used to characterize the flakes and identify the phase of the material. The spectra were recorded using a WITec Alpha300R Raman Microscope in confocal mode comprising of 532 nm laser. A 100x objective (NA = 0.9; Δλ ~360 nm) was used to focus the laser beam, while keeping the laser power typically at ~1 mW to avoid degradation of the material.

Sentaurus modeling

Sentaurus TCAD, which is a general-purpose finite element numerical device simulation tool, was used to simulate the surface potential and the corresponding photoresponse variations as a consequence of the induced polarization in the In2Se3 field-effect device across the semiconductor channel.

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films supplementary. Science 5, 1–12 (2004).

Mukherjee, S., Maiti, R., Katiyar, A. K., Das, S. & Ray, S. K. Novel colloidal MoS2 quantum dot heterojunctions on silicon platforms for multifunctional optoelectronic devices. Sci. Rep. 6, 1–11 (2016).

Mukherjee, S., Maiti, R., Midya, A., Das, S. & Ray, S. K. Tunable direct bandgap optical transitions in MoS2 nanocrystals for photonic devices. ACS Photonics 2, 760–768 (2015).

Guo, R. et al. Non-volatile memory based on the ferroelectric. Nat. Commun. 4, 2–6 (2013).

Lee, H., Kang, D. H. & Tran, L. Indium selenide (In2Se3) thin film for phase-change memory. Mater. Sci. Eng. B 119, 196–201 (2005).

Kang, W. & Huber, J. E. Prospects for energy harvesting using ferroelectric/ferroelastic switching. Smart Mater. Struct. 28, 024002 (2019).

Matzen, S. et al. Tuning ultrafast photoinduced strain in ferroelectric-based devices. Adv. Electron. Mater. 5, 1–6 (2019).

Tian, B. et al. A robust artificial synapse based on organic ferroelectric polymer. Adv. Electron. Mater. 5, 1–8 (2019).

Oh, S., Hwang, H. & Yoo, I. K. Ferroelectric materials for neuromorphic computing. APL Mater. 7, 091109 (2019).

Shen, Z., Wang, X., Luo, B. & Li, L. BaTiO3-BiYbO3 perovskite materials for energy storage applications. J. Mater. Chem. A 3, 18146–18153 (2015).

Ren, X., Fan, H., Zhao, Y. & Liu, Z. Flexible lead-Free BiFeO3/PDMS-based nanogenerator as piezoelectric energy harvester. ACS Appl. Mater. Interfaces 8, 26190–26197 (2016).

Lee, H. J., Zhang, S., Luo, J., Li, F. & Shrout, T. R. Thickness-dependent properties of relaxor-PbTiO3 ferroelectrics for ultrasonic transducers. Adv. Funct. Mater. 20, 3154–3162 (2010).

Shirodkar, S. N. & Waghmare, U. V. Emergence of ferroelectricity at a metal-semiconductor transition in a 1T monolayer of MoS2. Phys. Rev. Lett. 112, 1–5 (2014).

Yuan, S. et al. Room-temperature ferroelectricity in MoTe 2 down to the atomic monolayer limit. Nat. Commun. 10, 2–7 (2019).

Fei, Z. et al. Ferroelectric switching of a two-dimensional metal. Nature 560, 336–339 (2018).

Liu, F. et al. Room-temperature ferroelectricity in CuInP 2S 6 ultrathin flakes. Nat. Commun. 7, 1–6 (2016).

Chang, K. et al. Discovery of robust in-plane ferroelectricity in atomic-thick SnTe. Science 353, 274–278 (2016).

Zhou, Y. et al. Out-of-plane piezoelectricity and ferroelectricity in layered α-In2Se3 nanoflakes. Nano Lett. 17, 5508–5513 (2017).

Mukherjee, S. et al. Scalable integration of coplanar heterojunction monolithic devices on two-dimensional In2Se3. ACS Nano 14, 17543–17553 (2020).

Gao, J. et al. Intrinsic polarization coupling in 2D α-In 2 Se 3 toward artificial synapse with multimode operations. SmartMat 2, 88–98 (2021).

Ding, W. et al. Prediction of intrinsic two-dimensional ferroelectrics in In 2 Se 3 and other III 2 -VI 3 van der Waals materials. Nat. Commun. 8, 1–8 (2017).

Quereda, J. et al. Strong quantum confinement effect in the optical properties of ultrathin α-In2Se3. Adv. Optical Mater. 4, 1939–1943 (2016).

Rasmussen, A. M., Teklemichael, S. T., Mafi, E., Gu, Y. & McCluskey, M. D. Pressure-induced phase transformation of In2Se3. App. Phys. Lett. 102, 062105 (2013).

Xue, F. et al. Gate-tunable and multidirection-switchable memristive phenomena in a van der Waals ferroelectric. Adv. Mater. 31, 1–9 (2019).

Cui, C. et al. Intercorrelated in-plane and out-of-plane ferroelectricity in ultrathin two-dimensional layered semiconductor In2Se3. Nano Lett. 18, 1253–1258 (2018).

Xue, F. et al. Room-temperature ferroelectricity in hexagonally layered α-In2Se3 nanoflakes down to the monolayer limit. Adv. Funct. Mater. 28, 1–7 (2018).

Dagan, R., Vaknin, Y., Weisman, D., Amit, I. & Rosenwaks, Y. Accurate method to determine the mobility of transition-metal dichalcogenides with incomplete gate screening. Appl. Mater. Interfaces 11, 44406–44412 (2019).

Koren, E., Rosenwaks, Y., Allen, J. E., Hemesath, E. R. & Lauhon, L. J. Nonuniform doping distribution along silicon nanowires measured by Kelvin probe force microscopy and scanning photocurrent microscopy. Appl. Phys. Lett. 95, 21–24 (2009).

Koren, E., Berkovitch, N. & Rosenwaks, Y. Measurement of active dopant distribution and diffusion in individual silicon nanowires. Nano Lett. 10, 1163–1167 (2010).

Koren, E. et al. Obtaining uniform dopant distributions in VLS-grown Si nanowires. Nano Lett. 11, 183–187 (2011).

Koren, E. et al. Direct measurement of individual deep traps in single silicon nanowires. Nano Lett. 11, 2499–2502 (2011).

Vaknin, Y., Dagan, R. & Rosenwaks, Y. Pinch-off formation in monolayer and multilayers MoS2 field-effect transistors. Nanomater 9, 882 (2019).

Koren, E. et al. Direct measurement of nanowire Schottky junction depletion region. Appl. Phys. Lett. 99, 1–4 (2011).

Cuniot-Ponsard, M. Kelvin probe force microscopy and electrostatic force microscopy responses to the polarization in a ferroelectric thin film: theoretical and experimental investigations. J. Appl. Phys. 114, 014302 (2013).

Popescu, D. G. et al. Spectro-microscopic photoemission evidence of charge uncompensated areas in Pb(Zr,Ti)O3(001) layers. Phys. Chem. Chem. Phys. 1, 509–520 (2015).

Lewandowska, R., Bacewicz, R., Filipowicz, J. & Paszkowicz, W. Raman scattering in alpha-In2Se3 crystals. Mater. Res. Bull. 36, 2577–2583 (2001).

Igo, J., Gabel, M., Yu, Z. G., Yang, L. & Gu, Y. Photodefined in-plane heterostructures in two-dimensional In2Se3 nanolayers for ultrathin photodiodes. ACS Appl. Nano Mater. 2, 6774–6782 (2019).

Xue, F. et al. Multidirection piezoelectricity in mono- and multilayered hexagonal α-In2Se3. ACS Nano 12, 4976–4983 (2018).

Xiao, J. et al. Intrinsic two-dimensional ferroelectricity with dipole locking. Phys. Rev. Lett. 120, 227601 (2018).

Ge, C. et al. Numerical investigation into the switchable diode effect in metal-ferroelectric-metal structures. Appl. Phys. Lett. 99, 98–101 (2011).

Sai, N., Kolpak, A. M. & Rappe, A. M. Ferroelectricity in ultrathin perovskite films. Phys. Rev. B Condens. Matter Mater. Phys. 72, 1–4 (2005).

Goodenough, J. B. Oxide-ion conductors by design. Nature 404, 821–823 (2000).

Zhou, S. et al. Anomalous polarization switching and permanent retention in a ferroelectric ionic conductor. Mater. Horiz. 7, 263–274 (2020).

Wong, C. K. & Shin, F. G. A simplified treatment of the Landau theory of phase transitions for thin ferroelectric films. Am. J. Phys. 76, 31–38 (2008).

Si, M. et al. A ferroelectric semiconductor field-effect transistor. Nat. Electron. 2, 580–586 (2019).

Wang, S. et al. Two-dimensional ferroelectric channel transistors integrating ultra-fast memory and neural computing. Nat. Commun. 12, 1–9 (2021).

Wang, F., Young, S. M., Zheng, F., Grinberg, I. & Rappe, A. M. Substantial bulk photovoltaic effect enhancement via nanolayering. Nat. Commun. 7, 1–7 (2016).

Acknowledgements

D.D. gratefully acknowledges the support of The Miriam and Aaron Gutwirth Memorial Fellowship. S.M. gratefully acknowledges the support of the Technion by the Aly Kaufman Fellowship. E.K. gratefully acknowledges the Israel Science Foundation (ISF) grant 1567/18 for financial assistance and the RBNI for the nanofabrication facilities. E.K. thanks the Taub fellowship for leadership in science and technology, supported by the Taub Foundation and the Alon fellowship.

Author information

Authors and Affiliations

Contributions

D.D. performed the experimental work, S.M. provided experimental support, M.U. performed numerical modeling, E.K. supervised the work. All authors participated in manuscript writing.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Dutta, D., Mukherjee, S., Uzhansky, M. et al. Cross-field optoelectronic modulation via inter-coupled ferroelectricity in 2D In2Se3. npj 2D Mater Appl 5, 81 (2021). https://doi.org/10.1038/s41699-021-00261-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-021-00261-w

This article is cited by

-

Laterally gated ferroelectric field effect transistor (LG-FeFET) using α-In2Se3 for stacked in-memory computing array

Nature Communications (2023)

-

Ferroelectric order in van der Waals layered materials

Nature Reviews Materials (2022)

-

Monolithic In2Se3–In2O3 heterojunction for multibit non-volatile memory and logic operations using optoelectronic inputs

npj 2D Materials and Applications (2022)