Abstract

Two-dimensional (2D) transition metal dichalcogenides (TMDs)-based van der Waals (vdW) PN junctions have been used for heterojunction diodes, which basically utilize out-of-plane current across the junction interface. In fact, the same vdW PN junction structure can be utilized for another important device application, junction field effect transistors (JFETs), where in-plane current is possible along with 2D–2D heterojunction interface. Moreover, the 2D TMD-based JFET can use both p- and n-channel for low voltage operation, which might be its unique feature. Here we report vdW JFETs as an in-plane current device with heterojunction between semiconducting p- and n-TMDs. Since this vdW JFET would have low-density traps at the vdW interface unlike 2D TMD-based metal insulator semiconductor field effect transistors (MISFETs), little hysteresis of 0.0–0.1 V and best subthreshold swing of ~100 mV/dec were achieved. Easy saturation was observed either from n-channel or p-channel JFET as another advantage over 2D MISFETs, exhibiting early pinch-off at ~1 V. Operational gate voltage for threshold was near 0 V and our highest mobility reaches to ~>500 cm2/V·s for n-channel JFET with MoS2 channel. For 1 V JFET operation, our best ON/OFF current ratio was observed to be ~104.

Similar content being viewed by others

Introduction

Two-dimensional (2D) transition metal dichalcogenides (TMDs) have been extensively studied in both aspects of materials and devices for the past decade, since those are regarded to have great potentials for future nanoelectronics.1,2,3,4,5,6,7,8,9,10,11 Main focus has been on 2D TMD semiconductor devices, which are probably the most important for existing or future technologies.3,8,9,10,11,12 Many of metal insulator semiconductor field effect transistors (MISFETs) using 2D TMD channels have thus been reported,8,10,13,14,15,16,17,18,19,20,21,22 along with their use for complementary metal-oxide-semiconductor transistor inverters.23,24,25,26,27,28 Heterojunction 2D TMD p–n (PN) diodes with van der Waals (vdW) interface have also received much attention from researchers.29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44 These vdW PN junction interfaces basically experience out-of-plane or vertical current across the junction during device operation. In fact, the same vdW PN junction structure can be utilized for another important device application, junction field effect transistors (JFETs), where in-plane current is possible along with 2D–2D heterojunction interface. However, the vdW JFET application seems not reported yet, although some possibilities have just been casted in black phosphorous/ZnO nanowire junction systems.45

In the present work, we have fabricated vdW JFETs as an in-plane current device with heterojunction between semiconducting p-MoTe2 (or p-WSe2) and n-MoS2 TMDs. Since this vdW JFET would have low-density traps at the heterojunction interface when p-type material plays as a gate for n-channel and vice versa, little hysteresis of 0.05–0.1 V and good subthreshold swing (SS) of ~100 mV/dec were achieved. In addition, vdW JFET always exhibited easy saturation at a low drain voltage of ~1 V and reproducibly showed low operational gate voltages for threshold near 0 V (+0.2 V for p-JFET and −0.2 V for n-JFET). Above-mentioned properties have rarely been realized all together from general vdW 2D MISFETs.20,22 The highest mobility reaches to ~>500 cm2/V·s for n-channel JFET with MoS2 channel while p-channel JFET with MoTe2 appears much lower by more than an order of magnitude (~13 cm2/V·s). These values are comparable or approaches to previous results from 2D FETs.12,25,46 For our low-voltage JFET devices, ON/OFF current ratios were observed to be ~>104. The operation of both channel JFETs with ultrathin vdW 2D TMDs is regarded unique and different from that of general three-dimensional (3D) JFETs and MISFETs, and in principle two opposite (p and n) channels can be used as gate for each other. We again confirmed the principle through another p-TMD/n-TMD JFET (p-WSe2/n-MoS2 junction).

Results and Discussion

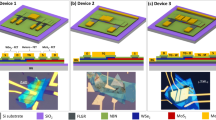

Figure 1a displays an optical microscopic (OM) image of our p-MoTe2/n-MoS2 channel JFET device fabricated on 285-nm-thick SiO2/p-Si wafer. Pt and Au are used as source/drain ohmic electrodes, respectively, for MoTe2 and MoS2 channel. As shown in a 3D schematic device view in Fig. 1c, hexagonal 2H-MoS2 channel overlies on 2H-MoTe2 when the two channels cross each other. The two semiconducting TMDs are simultaneously and clearly identified by micro Raman spectroscopy as shown in Fig. 1b, for which a central spot of the overlapped region is probed (see the red spot in Fig. 1a). Since the p- and n-channel materials are crossing, four different PN diodes are possibly formed using Pt and Au electrode and such diode behavior was confirmed (see supporting information in Figure S1). In addition, from the same structure, p- and n-type MISFET behavior was also confirmed along with large hysteresis in the transfer curve characteristics (Figure S2a).

Materials characteristics and device schematic views. a Optical microscopic (OM) image of our JFET device fabricated on 285-nm-thick SiO2/p-Si wafer. Red and blue dashed lines outline MoS2 and MoTe2 flake area, respectively. Scale bar = 5 μm. b Raman spectra obtained from red dot point of the overlapped region. c 3D schematic view of our MoS2 and MoTe2 junction device. Four heterojunction PN diode pairs can basically be formed (supporting information, Fig. S1) d 3D cross sectional views of p-MoTe2 channel (n-MoS2 gate) and n-MoS2 channel (p-MoTe2 gate) JFET devices

Following the OM for the JFET structure (Figs. 1a and 2a inset), atomic force microscopy (AFM; Fig. 2a, b) and scanning kelvin probe microscopy (SKPM, Fig. 2c) were conducted probing a rectangular region of the same device, which contains four respective surfaces as shown in Fig. 2a: SiO2 substrate, MoTe2, MoS2, and overlay MoS2 on MoTe2. According to AFM results (image contrast), the thickness of MoTe2 and MoS2 channel appears to be ~16 and 6 nm, respectively. According to SKPM results, the work functions of individual MoTe2 and MoS2 are quite the same, to be 4.54 eV, while that of MoS2 overlay on MoTe2 is slightly higher to be 4.56 eV. Slightly higher value is probably because MoS2 on MoTe2 is exempted from the effects of trap charges on SiO2 surface47,48 and also because of some electron charge transfer between the two TMDs. Based on SKPM data, we could expect and construct the band diagrams of MoTe2/MoS2 PN junction, MoS2 n-channel, and MoTe2 p-channel as seen in Fig. 2d–f, respectively. The PN junction should contain ~0.3 nm vdW gap between MoTe2 and MoS2. Without gate bias, channel has almost no energy barrier but built-in potential energy (qΦi = 0.02 eV for n-channel). When a reverse bias is applied to the p-type gate of n-channel, the MoS2 channel should have energy barrier at the p-gated (overlapped) region (Fig. 2e), where the Fermi energy becomes located in the middle of the band gap indicating charge carrier depletion (for OFF state). Similarly, the MoTe2 channel has the energy barrier at the n-gate region (Fig. 2f) under a reverse bias applied on p-channel. Without drain bias voltage, the band diagram with the barrier must be symmetric; however, it should become asymmetric under drain bias.

Device band diagram by AFM and SKPM. a 2D and b 3D AFM images of the JFET structure. Scale bar = 1 μm. c SKPM image of the JFET. White dashed box in the inset of a indicates the scanning region for AFM and SKPM (a–c). Energy band diagrams of d MoTe2/MoS2, e MoS2 n-channel, and f MoTe2 p-channel, respectively. VGn and VGp means the gate biases, respectively, applied on n- and p-channels

As expected from the in-plane direction band diagram (Fig. 2e, f), n-channel JFET was experimentally demonstrated in Fig. 3a–f. Figure 3a shows an OM image of another JFET that is different from that of Fig. 1a but has a comparable channel thickness dimension: ~12 and 7 nm, respectively, for MoS2 and MoTe2 channels. Output characteristics (drain current–drain voltage; ID–VDS) of the device in Fig. 3d display three stages for typical transistors: linear (i), pinch-off (ii), and saturation-to-early effect (iii). Those three stages are well explained with schematic JFET cross-sections under, respectively, different VDS in Fig. 3c, while each material component of the device is identified by color in the schematic 3D view of Fig. 3b. Cross-section (i) in Fig. 3c shows a conducting channel under small VDS for linear regime ID. As VDS increases toward more positive voltage, drain side experiences reverse bias with respect to the p-gate and asymmetric channel depletion (crosshatched area) takes place while source side maintains forward bias and channel opening. As VDS increases further, the n-channel reaches to pinch-off state (ii) and even channel length (L) modulation (iii). Such channel length modulation causes shorter length (L′) and elevated current (deviated from saturation; early effect). This channel modulation was quite general in our JFET devices as observed from another JFET (supporting information Figure S3a). Figure 3e shows transfer characteristics (drain current–gate voltage; ID–VGS), where a good ON/OFF ID ratio of 5 × 104 and SS of ~100 mV/dec were observed. The gate leakage current (IG) appears to increase with applied gate voltage (VGS) in Fig. 3e, and it is certainly understandable as forward bias-induced leakage that originates from the PN junction between n-MoS2 and p-MoTe2.

n-channel of p-MoTe2/n-MoS2 JFET. a OM image of n-channel JFET. Scale bar = 10 μm. b Simple 3D schematic of our n-channel JFET. c 2D cross-section device views according to (i) small, (ii) pinch-off, and (iii) large VDS as sectioned along with the white dashed line in b of our n-channel device. d ID–VDS output characteristics of n-channel JFET. e ID–VGS transfer characteristics of n-channel JFET. f Mobility of our n-channel JFET. Red and orange lines indicate the saturation mobility and black stars indicate the linear mobility at different VGS (0.2, 0.4, 0.6, 0.8 V, respectively)

The saturation mobility of our JFET is also extracted from the same figure. Threshold voltage and peak saturation mobility appear to be −0.2 V and 500–600 cm2/V·s, respectively, according to Fig. 3e, f. The saturation mobility was driven from the following Eq. (1), which needs the information on carrier concentration, Nd, and transconductance, gm, in MoS2 n-channel. We extract gm plots from transfer curves as a function of VGS in Fig. 3e.

So the mobility can be calculated as follows,

where Nd is carrier density as number per cm3; q is an electronic charge; and t, W, and L are the thickness, width, and length of the channel, respectively. Linear mobility can also be extracted out of the output characteristics at different VGS in Fig. 3d, using the following simple Eq. (3) at small VDS.

The maximum linear mobility appears quite comparable to that of saturation regime.

For both estimations of saturation and linear mobilities, Nd value would be the most important information. In order to obtain Nd value at room temperature, we have actually attempted four-point van der Pauw Hall measurements with Au-contacting 16-nm-thin MoS2 and Pt-contacting 7-nm-thin MoTe2. Figure 4a, b show two OM images of our samples on SiO2/p-Si substrate, while each thickness of the samples was measured by AFM scan as shown with the results of Fig. 4c. Although the sample shapes were not ideal symmetric in Fig. 4a, b, MoTe2 and MoS2 samples displayed positive and negative slopes, respectively, under magnetic field (H) sweep for relative magnetic resistance [RH(H)–RH(0)] vs. H field plot in Fig. 4d. Those slopes clearly identify or distinguish p- and n-type conduction. According to the slope, hole and electron concentrations (Na and Nd) were calculated to be 2.43 × 1017 and 2.5 × 1016/cm3 at 300 K, respectively. Calculation details are in supporting information section.

Hall measurement of MoS2 and MoTe2. OM image of a n-MoS2 and b p-MoTe2 for four-probe Hall measurement. c Flake thickness profiles of MoS2 (red) and MoTe2 (blue) as obtained from AFM scanning, and d RH(H)–RH(0) data under the magnetic field (H) for MoS2 (top negative slopes) and MoTe2 (positive slope). Scale bar of a, b = 10 μm

All of our JFET devices displayed only a little hysteresis unlike MISFET (Figure S2a) because of small density charge traps at the vdW PN junction interface. Mobility plots in Fig. 3f and transfer curves of Figure S2b exhibit a small hysteresis of 0.05–0.1 V whether the device is n- or p-channel JFET (which is actually a single device working with both channels). Figure 5a shows our third JFET with p-channel, and in fact, this JFET has similar channel thickness of ~10 nm, which is comparable to that of n-channel JFET in Fig. 3a. Output curve characteristics in Fig. 5d show the three ID regimes: linear (i), pinch-off (ii), and saturation (iii). At first glance, the p-channel ID output curves are comparable to those of n-channel ones in Fig. 3d; however, it is recognized on detail observation that pinch-off stage appears slower in MoTe2 p-channel; saturation voltages (VSAT = −1.5 V for VGS = −1 V) of p-channel are larger than those of MoS2 n-channel (VSAT = ~0.8 V for VGS = 1 V). It is related to the hole carrier density of p-channel, which is an order of magnitude larger than that of n-channel; the charge depletion of p-channel is more difficult under the same VGD (VGS−VDS) than that of n-channel. Figure 5b, c present schematic 3D and cross-section views of the p-channel JFET. As shown in Fig. 5c, under a positive VGD MoS2 gate (reverse bias) is more readily depleted than MoTe2 p-channel, which needs further VDS for reaching to pinch-off. In Fig. 5e, our p-channel JFET shows an order of magnitude lower ID than that of n-channel one, along with inferior SS (200 mV/dec) and ON/OFF ID ratio (5 × 103) to those of n-channel device. Difficult channel depletion or channel closing might be closely related to such inferiorities. According to Fig. 5f, the saturation (13–14 cm2/V·s as the peak mobility) and linear mobilities (4 cm2/V·s) of p-channel JFET appear comparable to the previous reports from p-MoTe2 MISFETs25 but much inferior to the values from MoS2 JFET. Impurity scattering due to an order of magnitude higher carrier concentration in the p-channel would be a main reason for the low mobility along with the intrinsic band structure of MoTe2.49,50 Besides, we could also suspect the many traps at the MoTe2 channel/SiO2 interface as another reason of such low mobility in respect of device geometry.

p-channel of p-MoTe2/n-MoS2 JFET. a OM image of p-channel JFET. Scale bar = 10 μm. b Simple 3D schematic of our p-channel JFET. c 2D cross-section device views according to (i) small, (ii) pinch-off, and (iii) large VDS as sectioned along with the white dashed line in b of our p-channel device. d ID–VDS output characteristics of p-channel JFET. e ID–VGS transfer characteristics of p-channel JFET. f Mobility of our p-channel JFET. Blue and skyblue lines indicate the saturation mobility and black stars indicate the linear mobility at different VGS (−0.2, −0.4, −0.6, −0.8 V, respectively)

As our final device, p-WSe2/n-MoS2 JFET was fabricated on purpose to confirm that any p-TMD/n-TMD JFET generally works in principle; p-TMD works as gate for n-TMD channel while n-TMD does as gate for p-TMD channel. Figure 6a, b, respectively, show the OM and schematic 3D view of the JFET, where Au contact was used in common for both p-WSe2 and n-MoS2 channel FETs. Figure 6c displays Raman spectra from both flakes as obtained at once by probing the overlaid position (red dot in Fig. 6a). According to output curve characteristics of Fig. 6d, p- and n-channel JFETs operate well again, although the contact resistance between Au and p-WSe2 appears serious. Owing to such shortcoming in contact resistance, p-WSe2 JFET shows its inferior I–V characteristics with a few nA of ON state, and the inferior conductance of p-channel WSe2 results in its insufficient gating for n-MoS2 JFET. Hence, n-MoS2 JFET in p-WSe2/n-MoS2 system displays an order of magnitude lower ON state ID than that of p-MoTe2/n-MoS2 JFET case, as seen in the output and transfer characteristics of Fig. 6d, e. However, this demonstration of p-WSe2/n-MoS2 JFET device still supports that any p-TMD/n-TMD JFET generally works in principle using both channels. (Figure S4 shows AFM thickness profile of p-WSe2 and n-MoS2 flakes in JFET.)

p-WSe2/n-MoS2 JFET. a OM image of p-WSe2/n-MoS2 JFET on SiO2/p-Si. Scale bar = 10 μm. b 3D schematic cross-sections of p-WSe2 and n-MoS2 channel JFET. Au was used as contact metal for both channels. c Raman spectra of WSe2 and MoS2 as obtained by probing the red spot in a. d ID–VDS output characteristics of p-WSe2 and n-MoS2 channel JFET. e ID–VGS transfer characteristics of p-WSe2 and n-MoS2 channel JFET

In summary, we have fabricated vdW JFETs as an in-plane current device with heterojunction between semiconducting p-MoTe2 and n-MoS2 TMDs. Since this vdW JFET would have low-density traps at the vdW interface when p-type material plays as a gate for n-channel and vice versa, little hysteresis of 0.05–0.1 V and good SS of ~100 mV/dec were achieved. Easy saturation was observed as another advantage over 2D MISFETs, exhibiting early pinch-off at ~1 V. Operational gate voltage for threshold was near 0 V and the highest mobility reaches to ~>500 cm2/V·s for n-channel JFET with MoS2 channel while p-channel JFET with MoTe2 appears much lower by more than an order of magnitude (~13 cm2/V·s). For 1 V JFET operation, our highest ON/OFF current ratio was observed to be ~104. The operation of both channel JFETs with ultrathin vdW 2D TMDs is regarded unique and different from that of general 3D JFETs and MISFETs in the principle that two opposite (p- and n-) channels can be used as gate for each other. We again confirmed the principle through another p-TMD/n-TMD JFET (p-WSe2/n-MoS2 junction). We thus conclude that our 2D-like ultrathin channel JFET is fresh enough in its operating principle, structure, and fabrication simplicity to influence the future of 2D semiconductor-based nanoelectronics.

Methods

Device fabrication

SiO2/p-Si wafer (285-nm thick) was chosen as JFET device substrate. The substrates were cleaned in acetone and methyl alcohol by ultrasonicator. For p-MoTe2/n-MoS2 JFETs, α-MoTe2 nanosheet (mechanically exfoliated from bulk crystals using polydimethylsiloxane) was transferred onto the substrate. Fifty-nm (Pt) ohmic electrodes for MoTe2 were patterned by photolithography process and deposited by direct current (DC) magnetron sputtering system. In the next step, MoS2 nanoflake was transferred onto the MoTe2 flake forming vdW junction. Fifty-nm (Au) ohmic electrodes for MoS2 were also patterned in the same way. For p-WSe2/n-MoS2 JFETs, WSe2 nanosheet was transferred onto the substrate and then MoS2 nanoflake was crossed over contacting WSe2 flake. Au ohmic electrodes for both WSe2 and MoS2 were patterned by photolithography process and DC magnetron sputter deposition.

Characterization

All nanoflakes were measured for thickness information with AFM (Nanowizard I, JPK Instrument). SKPM measurements were performed using Park Systems XE7 with non-contact mode. In SKPM imaging, we applied an alternating current (AC) bias voltage of 1.5 V with a frequency of 17 kHz to Au-coated tip (PPP-NCSTAu, nanosensors). Device electrical characteristics (I–V curve of diodes and transfer and output characteristics of transistors) were performed in the dark at room temperature using a semiconductor parameter analyzer (HP4155C, Agilent Technologies). The Hall measurement for carrier density estimation of MoS2 and MoTe2 nanoflakes on SiO2/p+-Si substrate were conducted by applying an AC current of 0.4 Hz and 0.1 mA as input signal frequency and amplitude, respectively, under the magnetic field (H) sweep from −9 to 9 T using physical property measurement system.

Data availability

The authors confirm that the data supporting the findings of this study are available within the article and its supplementary materials.

References

Zhou, L. et al. Large-area synthesis of high-quality uniform few-layer MoTe2. J. Am. Chem. Soc. 137, 11892–11895 (2015).

Keum, D. H. et al. Bandgap opening in few-layered monoclinic MoTe2. Nat. Phys. 11, 482–486 (2015).

Fathipour, S. et al. Exfoliated multilayer MoTe2 field-effect transistors. Appl. Phys. Lett. 105, 2014–2017 (2014).

Chhowalla, M. et al. The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets. Nat. Chem. 5, 263–275 (2013).

Qi, Y. et al. Superconductivity in Weyl semimetal candidate MoTe2. Nat. Commun. 7, 11038 (2016).

Ruppert, C., Aslan, O. B. & Heinz, T. F. Optical properties and band gap of single- and few-layer MoTe2 crystals. Nano Lett. 14, 6231–6236 (2014).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Lee, H. S. et al. MoS2 nanosheet phototransistors with thickness-modulated optical energy gap. Nano Lett. 12, 3695–3700 (2012).

Choi, K. et al. Direct imprinting of MoS2 flakes on a patterned gate for nanosheet transistors. J. Mater. Chem. C 1, 7803 (2013).

Lezama, I. G. et al. Indirect-to-direct band gap crossover in few-layer MoTe2. Nano Lett. 15, 2336–2342 (2015).

Lee, H. S. et al. Metal semiconductor field-effect transistor with MoS2/conducting NiOX van der Waals Schottky interface for intrinsic high mobility and photoswitching speed. ACS Nano 9, 8312–8320 (2015).

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Yin, Z. et al. Single-layer MoS2 phototransistors. ACS Nano 6, 74–80 (2012).

Fang, H. et al. High-performance single layered WSe2 P-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotechnol. 8, 497–501 (2013).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934–9938 (2011).

Di Bartolomeo, A. et al. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 5, 015014 (2017).

Li, C. et al. Low sub-threshold swing realization with contacts of graphene/h-BN/MoS2 heterostructures in MoS2 transistors. Appl. Phys. Lett. 111, 193502 (2017).

Liu, N. et al. Improving the stability of high-performance multilayer MoS2 field-effect transistors. ACS Appl. Mater. Interfaces 9, 42943–42950 (2017).

Lim, J. Y. et al. Homogeneous 2D MoTe2 P-N junctions and CMOS inverters formed by atomic-layer-deposition-induced doping. Adv. Mater. 29, 1701798 (2017).

Jin, Y. et al. Van der Waals homojunction: ideal p-n diode behavior in MoSe2. Adv. Mater. 27, 5534–5540 (2015).

Pezeshki, A. et al. Static and dynamic performance of complementary inverters based on nanosheet α-MoTe2 p-channel and MoS2 n-channel transistors. ACS Nano 10, 1118–1125 (2016).

Tosun, M. et al. High-gain inverters based on WSe2 complementary field-effect transistors. ACS Nano 8, 4948–4953 (2014).

Yu, L. et al. High-performance WSe2 complementary metal oxide semiconductor technology and integrated circuits. Nano Lett. 15, 4928–4934 (2015).

Das, S., Dubey, M. & Roelofs, A. High gain, low noise, fully complementary logic inverter based on bi-layer WSe2 field effect transistors. Appl. Phys. Lett. 105, 1–6 (2014).

Lee, C.-H. et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol. 9, 676–681 (2014).

Zhang, K. et al. Interlayer transition and infrared photodetection in atomically thin type-II MoTe2/MoS2 van der Waals heterostructures. ACS Nano 10, 3852–3858 (2016).

Wang, B. et al. Enhanced current rectification and self-powered photoresponse in multilayer p-MoTe2 /n-MoS2 van der Waals Heterojunctions. Nanoscale 9, 10733–10740 (2017).

Wang, F. et al. Tunable GaTe-MoS2 van der Waals p−n junctions with novel optoelectronic performance. Nano Lett. 15, 7558–7566 (2015).

Doan, M.-H. et al. Charge transport in MoS2/WSe2 van der Waals heterostructure with tunable inversion layer. ACS Nano 11, 3832–3840 (2017).

Cho, A. J. et al. Electric and photovoltaic characteristics of a multi-layer ReS2/ReSe2 heterostructure. Nano Lett. 14, 5590–5597 (2014).

Cheng, R. et al. Electroluminescence and photocurrent generation from atomically sharp WSe2/MoS2 heterojunction p−n diodes. Nano Lett. 14, 5590 (2014).

Ahn, J. et al. Transition metal dichalcogenide heterojunction PN diode toward ultimate photovoltaic benefits. 2D Mater. 3, 045011 (2016).

Ross, J. S. et al. Interlayer exciton optoelectronics in a 2D heterostructure p−n junction. Nano Lett. 17, 638–643 (2017).

Jariwala, D. et al. Large-area, low-voltage, antiambipolar heterojunctions from solution-processed semiconductors. Nano Lett. 15, 416–421 (2015).

Jariwala, D. et al. Gate-tunable carbon nanotube–MoS2 heterojunction p-n diode. Proc. Natl. Acad. Sci. 110, 18076–18080 (2013).

Jariwala, D. et al. Hybrid, gate-tunable, van der Waals p−n heterojunctions from pentacene and MoS2. Nano Lett. 16, 497–503 (2016).

Furchi, M. M., Pospischil, A., Libisch, F., Burgdörfer, J. & Mueller, T. Photovoltaic effect in an electrically tunable van der Waals heterojunction. Nano Lett. 14, 4785–4791 (2014).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Kim, J., Mastro, M. A., Tadjer, M. J. & Kim, J. Heterostructure WSe2−Ga2O3 junction field-effect transistor for low-dimensional high-power electronics. ACS Appl. Mater. Interfaces 10, 29724–29729 (2018).

Cheng, R. et al. High-performance, multifunctional devices based on asymmetric van der Waals heterostructure. Nat. Electo. 1, 356–361 (2018).

Jeon, P. J. et al. Black phosphorus–zinc oxide nanomaterial heterojunction for p–n diode and junction field-effect transistor. Nano Lett. 16, 1293–1298 (2016).

Shin, H. G. et al. Vertical and in-plane current devices using NbS2/n-MoS2 van der Waals Schottky junction and graphene contact. Nano Lett. 18, 1937–1945 (2018).

Li, Y., Xu, C. Y. & Zhen, L. Surface potential and interlayer screening effects of few-layer MoS2 nanoflakes. Appl. Phys. Lett. 102, 3–7 (2013).

Castellanos-Gomez, A. et al. Electric-field screening in atomically thin layers of MoS2: the role of interlayer coupling. Adv. Mater. 25, 899–903 (2013).

Lezama, I. G. et al. Surface transport and band gap structure of exfoliated 2H-MoTe2 crystals. 2D Mater. 1, 21002 (2014).

Muller, R. S., Kamins, T. I. & Chan, M. Device Electronics for Integrated Circuits (John Wiley & Sons, Inc., New York, NY, 2003).

Acknowledgements

The authors acknowledge the financial support from NRF (NRL program: Grant No. 2017R1A2A1A05001278, SRC program: Grant No.2017R1A5A1014862, vdWMRC center). J.Y.L. acknowledges the tuition support from the Hyundai Motor Chung Mong-Koo Foundation.

Author information

Authors and Affiliations

Contributions

J.Y.L. conducted all the experiments and analysis; M.K., Y.Y., and T.K. supported the SKPM measurement; Y.J. and H.G.S. helped device fabrications; K.R.K., J.Y.M., and Y.J.C. helped Hall measurement; S.Y. helped with 3D figure scheme techniques; S.I. designed whole-device experiments.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lim, J.Y., Kim, M., Jeong, Y. et al. Van der Waals junction field effect transistors with both n- and p-channel transition metal dichalcogenides. npj 2D Mater Appl 2, 37 (2018). https://doi.org/10.1038/s41699-018-0082-2

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-018-0082-2

This article is cited by

-

Longitudinal and latitudinal split-gate field-effect transistors for NAND and NOR logic circuit applications

npj 2D Materials and Applications (2022)

-

High-performance MoS2/p+-Si heterojunction field-effect transistors by interface modulation

Nano Research (2022)

-

Investigation of optical and electrical properties of graphene oxide/silicon nanowires heterojunction

Journal of Materials Science: Materials in Electronics (2022)

-

Controllable potential barrier for multiple negative-differential-transconductance and its application to multi-valued logic computing

npj 2D Materials and Applications (2021)

-

High-performance lateral MoS2-MoO3 heterojunction phototransistor enabled by in-situ chemical-oxidation

Science China Materials (2020)