Abstract

This paper is an attempt to provide a dual-source inverter, an intelligent inverter topology that links two isolated DC sources to a single three-phase output through single-stage conversion. The converter is designed to be utilized in hybrid photovoltaic fuel cell systems, among other renewable energy applications. The proposed dual-source inverter employs a single DC-AC converter, as opposed to conventional dual-source hybrid inverters which make use of several input DC-DC modules to obtain the voltage formed across the inverter’s input DC-link. In the proposed topology, the semiconductor count is low, which leads to improved efficiency, cost, complexity, and reliability. The proposed topology makes use of two impedance networks connected by transformers, diodes, and capacitors. The regulation of the electrical power generated by primary sources and the independence of the converter on key factors like voltage and frequency are essential parameters in multi-input converters. This feature becomes highly prominent when the control algorithm is implemented by conventional processors. Viewed from this perspective, the control method described in this paper is worthy of consideration. The research work describes a 220-W/50 Hz prototype that employs Simple Boost-SPWM. Experimental results verify the analyses and corroborate the satisfactory performance of the suggested converter.

Similar content being viewed by others

Introduction

Some renewable energy resources such as solar cells and wind turbines are widely available around the world and are good choices for energy storage systems. The intermittent nature of these energy sources requires them to be used alongside batteries or fuel cells. Energy generated by one of these renewable energy resources causes low reliability in supplying power to the grid system1,2,3. Photovoltaic panels and fuel cells generate not only low, but also unstable DC voltage. To overcome this shortcoming, power electronic boost converters should be used1,2. The terminal voltage could increase if additional photovoltaic cells are connected in series. Even using the second solution cannot compensate for the effect of partial shading1,2.

In hybrid energy systems with DC voltage sources, it is possible to use a separate DC-DC converter for each power source and then connect their outputs to a single DC bus. This solution, however, leads to higher costs, complexity, volume, and so on. The other proposed solution involves using multi-input converters1,2,4,5. These converters are powered by sources with different power and voltage levels, producing a fixed output of voltage and frequency1,2,6,7. In hybrid energy systems that take DC voltage as input and produce AC voltage as output, two technical approaches are available for conversion: single-stage and dual-stage1. Power electronic converters with a single or multiple input can be used to achieve these tasks. In dual-stage conversion structures, you need DC-DC converters. Some of these topologies are introduced in Refs.3,4,6,7,8. Somehow Multi-input converters must be used with single-stage conversion structures1. In this regard, some single-phase topologies are introduced in Refs.9,10,11,12,13, while three-phase topologies are discussed in Refs.1,2,14,15,16,17,18,19,20. Using a multi-input DC-AC converter for the implementation of single-stage energy conversion reduces the costs, weight, and volume1. Thus, the present research introduces a multi-input single-output DC-AC converter which belong to the category of single-stage conversion systems.

The topologies discussed in Refs.17,18 require three DC sources to generate a three-phase output. The topology discussed in Ref.18 needs three extra switches. Reference19 describes the development of a high-reliability multi-port inverter using five extra switches and no additional passive elements. The topologies proposed in Refs.16,20,21 are appropriate structures, especially for high-power applications. In this research study, the converters used are implemented using twelve additional switches. The impedance source inverter, initially covered in Ref.22, uses single-stage conversion by utilizing the "shoot-through" concept23,24. The Shoot-Through State (STS) in such structures increases the value of DC-link voltage. This new concept has recently been used to propose new designs for multi-input inverters1,2,14,15,17.

The topologies presented in Refs.25,26,27,28,29,30,31,32,33 are dual-stage multi-input inverters. These topologies are unique in several ways, including their low number of semiconductors and absence of low-frequency transformers. These features make them well-suited for photovoltaic and grid-connected applications. However, these systems do have some drawbacks, such as low voltage gain. Various types of inverters, such as multilevel, modified Z-source, and high step-up three-phase inverters, were discussed in Refs.34,35,36,37,38,39,40,41. These inverters have notable features such as being short-circuit risk-free, not requiring connection to the AC grid for stable output voltage, minimizing voltage and current stress, having higher voltage gain, continuous input current, and excellent power-sharing capabilities. The single-stage dual-input inverter design covered in Ref.42 carries a risk of short-circuit. Additionally, this inverter may need to be connected to the AC grid to maintain a consistent output voltage.

The new multi-port impedance source inverters introduced by Refs.14,15 form the basis of the z-source inverter presented in Ref.22. Reference14 describes a dual-input dual-output inverter with nine switches, allowing each source to supply a separate load. In the topology presented in Ref.15, the input sources cannot have random voltage or current levels. Two dual-input single-output three-phase inverters are discussed in Refs.1,2. In the topology developed by Ref.2, replacing the two inductors of the classic impedance source inverter with two transformers forms a new multi-port inverter. In this inverter, the DC-link voltage is a three-level signal with a specific switching frequency. Hence, a new modulation method is required to overcome the THD problem considering the classic modulation methods generating high THD at output. A multi-input inverter is proposed in Ref.1 using a z-source inverter22. This inverter uses a single-stage power conversion. The traditional z-source structure forms the basis of this topology22. This structure and the proposed topology use artificial intelligence for preventing negative bias of the capacitors placed in DC-Link bus. This topology has more components with respect to the proposed inverter in this paper.

The connections in the proposed inverter are such that when the DC-link capacitors (C5 and C6) start to charge up with a negative voltage, the diodes paralleled with these capacitors will start conducting. Therefore, the negative charge of the capacitors would be discharged into the other energy storage elements placed in Z1 through these diodes. So, this hardware-based approach will eliminate the need for excessive detection and protection mechanisms by humans or other additional hardware Infrastructure. This is a hardware-based artificial intelligence because human attention and protection do not play a role in the process. In this paper, "artificial intelligence" refers to machine intelligence. As it is known the machine intelligence is a sub-branch of artificial intelligence which implicates substituting human with machine hardware for taking human-based tasks and procedures. This approach uses high-capacity polarized electrolytic capacitors in the converter’s structure, reducing voltage ripple of the DC link section used in the inverters structure.

In this paper, a new single-stage multi-port inverter is proposed by removing the third windings of the transformers and some active and passive elements from the topology introduced in Ref.1. This inverter shows higher efficiency and an equal gain in real-life conditions. Improvements in cost, weight, volume, and other aspects have also been observed. The hardware-based artificial intelligence used in manufacturing DC-link capacitors does not receive negative voltage. However, other advantages of the topology presented in Ref.1 are observable in the suggested structure. This function is performed using microcomputers and low-power embedded systems.

In this topology, two impedance networks are linked through diodes, capacitors, and the winding of transformers, which mechanism has replaced inductors. As impedance networks and STS are utilized, the proposed inverter serves as a voltage booster. Due to using capacitors in series with the transformers, there are no voltage spikes over the semiconductors caused by the leakage inductances. Therefore, in this topology, using snubbers is not a necessity.

In this paper, there are two dependent and two independent variables. The DC-link voltage and the ratio of the power generated by the sources are considered dependent variables. One feature of the proposed inverter is that it allows individual control of the two dependent variables. Otherwise, each dependent variable is only controlled by one independent variable, and changes in one cannot bring about any changes in the other. Also, Simple Boost-SPWM, first presented in Ref.22, is used as the modulation method. Following the above introduction, section “Presenting and analyzing the proposed inverter” presents the operating modes of the suggested inverter and more. Section “An analysis of steady state relations and power-sharing” provides a more detailed analysis of power-sharing and mathematical relationships. Finally, the outcomes of the simulation and experiments are discussed and assessed in the concluding section “Reliability assessment”.

Presenting and analyzing the proposed inverter

Figure 1 shows the inverter proposed in this paper. The inverter consists of two impedance networks (Z1 and Z2), two DC sources (Vi1 and Vi2), and a six-switch inverter. In Z1, two high-frequency transformers (T1 and T2) are used instead of two inductors, with their inductors (L1 and L2) taking the place of the removed inductors. Z1 enters the STS if S1 is turned on, and if S1 is turned off, Z1 enters the NSTS (Non-Shoot-Through State). If at least one leg of the six-switch inverter is shorted, Z2 enters the STS; otherwise, it enters the NSTS. The Vi1 power is transferred to the load via T1, T2, C5, C6, and the six-switch inverter. The control of power generated by Vi1 and Vi2 is done by adjusting the shoot-through duty cycles of both Z1 and Z2.

Reference22 explains how Z1 works and discusses the relation between the average values of the voltages as follow:

In (1) and (2), \({\text{D}}_{{\text{st}}{1}}\) is equal to the duty cycle of S1. Other variables are shown in Fig. 1. According to the circuit symmetry, it is possible to say that \({\text{V}}_{{\text{C}}{1}} = {\text{V}}_{{\text{C}}{2}}.\)

Considering that all inductors of the inverter of Fig. 1 work in CCM, and as both Z1 and Z2 have two operation modes (STS and the NSTS), four operation modes can be defined for the proposed inverter: Mode A, Mode B, Mode C, Mode D as is shown in Fig. 2. Table 1 details each mode. What inductors or capacitors charge or discharge are displayed in Fig. 2. Once Z1 enters in the STS because S1 is a short circuit (according to Fig. 2a and b), the inductors of Z1, C5, and C6 are charged by the capacitors of Z1. When Z1 enters in the NSTS, the capacitors of Z1 are charged, and the inductors of Z1, C5, and C6 are discharged (according to Fig. 2c and d). In this case, the branch containing S1 is an open circuit.

When Z2 enters in the STS (Cf. Fig. 2a and c), at least one of the legs of the six-switch inverter is a short circuit. At this time, similar to the Z1 operation, the capacitors of Z2 charge the inductors of Z2 and discharge themselves. When Z2 enters in the NSTS (according to Fig. 2b and d), the capacitors of Z2 are charged and the inductors of Z2 are discharged. At this time, the six-switch inverter connects the load to the other parts of the circuit, and the load current and the six-switch inverter's current become equal. The power is transferred from Vi1 to the other parts of the circuit only if Z1 is in the NSTS, and the power is transferred from Vi2 to the other parts of the circuit only if Z2 is in the NSTS.

In this topology, the components C5, D3 and secondary winding of T1 and also C6, D4 and secondary winding of T2 have the responsibility to transfer power from Vi1 to the load. It is obvious that this portion of power is delivered to the load through an interconnection between the Z2 and load. Therefore, there is a need for a low ripple voltage in the C5 and C6 to reduce the load voltage and current ripple. This requires high-capacity capacitors, mainly found in the class of polarized electrolytic capacitors. So, it is possible to achieve this goal by using high-capacity electrolytic capacitors for C5 and C6.

Additionally, supposing that Z1 does not supply the C5 and C6, it can be said that C5 and C6, after some switching periods, will be charged with negative voltage by Z2. When this happens, the power will not be transferred to the load and the system will be inefficient.

Also, because C5 and C6 are polarized electrolytic capacitors, the negative voltage causes both an explosion and a lack of transfer of power to the load. Therefore, it can be said that the presence of C5 and C6 in DC-link, executed for power-sharing proposes, can cause a lack of supplying the load, if Z1 and the windings of T1 and T2 are unable to discharge the negative voltage of C5 and C6. One solution to overcome the above problem is using some sensing and relay circuits in parallel with C5 and C6. The solution requires several sensors, which increases the cost and foundation preparations. Also, the aging of the relays due to the moving elements requires to additional attentions. A better solution to the problem is using machine intelligence which is a sub-branch of artificial intelligence. Using machine intelligence for overcoming this problem can be performed by using controllers or hardware-based methods. The inverter proposed here makes use of machine intelligence as a hardware-based artificial intelligence so that if C5 and C6 are charged by a negative voltage, Z1, D3, D4, and the secondary windings of T1 and T2 will start to discharge them to C1, C2, L1, and L2. The energy stored in C1, C2, L1, and L2 in this way, thus, will be discharged to C5 and C6 to charge with positive voltage.

Furthermore, the capacitors C5 and C6 may be charged with negative voltage if \({\text{V}}_{{\text{i}}{1}} = {0}\). if this happens, the problem mentioned in the previous paragraphs will accrue. Therefore, in such cases also, some relay circuits or human monitoring are required to stop that from happening. The interesting point to note is that Z1 will cause discharge of C5 and C6, if they start to charge with a negative voltage. Also, machine intelligence is in operation in such situations.

The switching frequencies chosen for Z1 and Z2 in the suggested inverter might not be equal. This precludes the need for any additional consideration and the inverter works according to what was explained in this section. This research paper employs Simple Boost-SPWM introduced in Ref.22 as switching method for Z2.

An analysis of steady state relations and power-sharing

For the suggested inverter illustrated in Fig. 1, if Z1 enters in the STS, C5 and C6 will be charged, and if Z1 enters in the NSTS, C5 and C6 will be discharged. Once Z1 enters in the STS, the voltage of C1 and C2 will drop across the primary windings of T1 and T2, respectively, multiplied by \(\frac{{\text{N}}_{2}}{{\text{N}}_{1}}\) and dropped across C5 and C6. Considering these explanations and (1), it can be said that:

According to the circuit symmetry, \({\text{V}}_{{\text{C}}{5}} = {\text{V}}_{{\text{C}}{6}}\) and \({\text{V}}_{{\text{C}}{3}} = {\text{V}}_{{\text{C}}{4}}\). Appling volt-second law for L3 yields:

In (4), \({D}_{st2}\) is equal to the shoot-through duty cycle of Z2. Considering (1), (3), and (4), the following results:

Using the same analysis, DC-link voltage (\({\text{V}}_{{\text{O}}{2}}\))–when Z2 is in the NSTS – can yield as is shown in the following:

The suggested inverter is a voltage booster, as demonstrated by Eq. (6), making it a good fit for some such applications as hybrid photovoltaic-fuel cell systems. The suggested inverter's comparison with comparable structures presented in 1,14,17, from a voltage gain viewpoint, is performed in the following part.

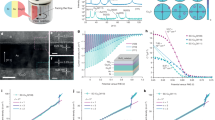

To have a fair comparison, some such assumptions as \({\text{V}}_{{\text{i}}{1}} = {\text{V}}_{{\text{i}}{2}}\) for Refs.1,14,17, \(\frac{{\text{N}}_{2}}{{\text{N}}_{1}} = {1}\) for the proposed converter, and \(\frac{{\text{N}}_{3}}{{\text{N}}_{1}} = \frac{{\text{N}}_{2}}{{\text{N}}_{1}} = {1}\) for Ref.1 are taken into account. The results are illustrated in Fig. 3. According to the results displayed in Fig. 3, it can be stated that the voltage gain of the proposed inverter is higher than the topologies of Refs.14,17 for all values of \({\text{D}}_{{\text{st}}{1}}\). But the topology of Ref.1 shows a higher gain than the proposed inverter in the same value of \({\text{D}}_{{\text{st}}{1}}\) and \({\text{D}}_{{\text{st}}{2}}\). For instance, when \({\text{D}}_{{\text{st}}{1}} = {\text{D}}_{{\text{st}}{2}} = {0.2}\), the voltage gain of the suggested inverter is 9.9, 6.11, 1.67, and 1.43, according to the topology of Refs,1,14,17. The gain of the suggested inverter will be greater than that of the inverters suggested in Refs.14,17 and will be lower than the inverter suggested in Ref.1 due to the increase in transformer turns ratio. This comparison is performed under ideal conditions where parasitic elements of the converters are not taken into account and the efficiency of all converters is assumed to be %100. As will be explained in Part IV, in real-life conditions, where parasitic elements of topologies are considered, the efficiency of the proposed inverter is higher than the topology of Ref.1. Also, the voltage gain of the proposed inverter is almost equal to that of the topology of Ref.1 in high-power applications.

The act of controlling the power produced by each source is crucial for multi-input converters1. In this paper, the role of each source in providing the load is represented by the index \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\). Furthermore, \({\text{V}}_{{\text{O}}{2}}\) is an additional index that has to be under control. In the suggested system, the independent variables are \({\text{D}}_{{\text{st}}{1}}\) and \({\text{D}}_{{\text{st}}{2}}\). Therefore, there are two dependent variables (\({\text{V}}_{{\text{O}}{2}}\) and \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\)) that have to be controlled by \({\text{D}}_{{\text{st}}{1}}\) and \({\text{D}}_{{\text{st}}{2}}\). Equation (6) depicts the relation between \({\text{V}}_{{\text{O}}{2}}\), \({\text{D}}_{{\text{st}}{1}}\), and \({\text{D}}_{{\text{st}}{2}}\). So, another variable is required to show the relation between \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\),\({\text{D}}_{{\text{st}}{1}}\), and \({\text{D}}_{{\text{st}}{2}}\). When Z2 is in the STS, it can be said that:

where the average value of \({\text{i}}_{\text{DC-link}}\) during shoot-through time is represented by \({\text{I}}_{\text{DC-link}}^{\text{st}}\). Again, when Z2 is in the NSTS, this can be stated as:

where the average values of \({\text{i}}_{\text{DC-link}}\) and load current in non-shoot-through time are denoted by \({\text{I}}_{\text{DC-link}}^{\text{non st}}\) and \({\text{I}}_{\text{Load}}\), respectively. Simultaneously taking into account (7) and (8), the average value of \({\text{i}}_{\text{DC-link}}\) in a single switching period can be obtained as Eq. (9).

As regards \({\text{I}}_{\rm{DC-link}} = {\rm{I}}_{{\text{L}}{3}}\) and \({\text{I}}_{{\text{L}}{3}} = {\text{I}}_{{\text{i}}{2}}\), (9) can be simplified as follow:

Therefore, the load's absorption of active power is:

The active power generated by source 2 is:

Considering (10), (11), and (12) simultaneously yields:

Also, the generated active power by source 1 is:

Substituting (13) in (14) simplifies (14) as follow:

The division of (15) by (13) yields the generated power ratio by the sources as follows:

Substituting (6) in (16) results:

Equation (17) shows that the control of \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) is performed by adjusting \({\text{D}}_{{\text{st}}{1}}\), and whatever changes in \({\text{D}}_{{\text{st}}{2}}\) cannot bring about any changes in \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\). The reason is that in a real system, the control of the variable is performed by controllers, and the controller needs programming. Hence, simple control relations mean both easier implementation and faster execution. With these explanations, one can say that, as (17) only depends on \({\text{D}}_{{\text{st}}{1}}\), implementing (17) in the controller proves simple and the execution is affected in a speedy manner. By replacing (17) in (6), the following is obtained:

Equation (18) well indicates that controlling \({\text{V}}_{{\text{O}}{2}}\) only depends on \({\text{D}}_{{\text{st}}{2}}\) and is independent of \({\text{D}}_{{\text{st}}{1}}\) if \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) is already determined. Thus, by changing the values of \({\text{D}}_{{\text{st}}{1}}\) and \({\text{D}}_{{\text{st}}{2}}\), respectively, the values of \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) and \({\text{V}}_{{\text{O}}{2}}\) can both be controlled. Correspondingly, (17) and (18) determine \({\text{D}}_{{\text{st}}{1}}\) and \({\text{D}}_{{\text{st}}{2}}\).

Considering (17), the curves of \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) are drawn in terms of different values of \({\text{V}}_{{\text{i}}{1}}\), \({\text{V}}_{{\text{i}}{2}}\), and \(n\) illustrated in Fig. 4. This figure clearly shows that in the proposed inverter, regardless of the parameter values, the controller can manage \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) in a wider range of cases by changing \({\text{D}}_{{\text{st}}{1}}\).

Curves of \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) with respect to \({\text{D}}_{{\text{st}}{1}}\) for different values of \({\text{V}}_{{\text{i}}{1}}\), \({\text{V}}_{{\text{i}}{2}}\), and \(n\). (a) for \(\frac{{\text{V}}_{{\text{i}}{1}}}{{\text{V}}_{{\text{i}}{2}}} = {2}\), (b) for \(\frac{{\text{V}}_{{\text{i}}{1}}}{{\text{V}}_{{\text{i}}{2}}} = {1}\), (c) for \(\frac{{\text{V}}_{{\text{i}}{1}}}{{\text{V}}_{{\text{i}}{2}}} = {1/2}\).

In order to compare the voltage and current stresses of the MOSFETs used in this paper with those in reference 1, the relevant relations are listed in Table 2.

As shown in Table 2, the current and voltage stress of S1 and the current stress of S2 to S7 are parametrically the same in both cases. However, the voltage stress of S2 to S7 in both cases are not equal. The voltage stress of these switches is coupled to the transformers turn ratio with the definition of n \( = \frac{{\text{N}}_{3}}{{\text{N}}_{1}} = \frac{{\text{N}}_{2}}{{\text{N}}_{1}}\). Therefore, in order to have a fairly comparison, the value of turns ratio is assumed to be unity. After applying this assumption and doing simplification for the voltage stress terms, it can be inferred that the voltage stress of S2 to S7 is smaller than the voltage stress of S2 to S7 in the topology presented in Ref.1 by a factor of \(({1}-{\text{D}}_{{\text{st}}{1}})\).

Reliability assessment

This section provided an assessment of the proposed system, focusing on estimating the reliability of the semiconductor switches, such as MOSFETs and diodes and so the whole converter. As previously mentioned, the system's machine intelligence feature ensures that not all semiconductor switches equally impact system operations. Specifically, the system's operation is critically dependent only on H-bridge MOSFETs (S2 to S7), as the system's operation and power transfer from Vi2 to the load is maintained in the failure occurrence for other semiconductor switches. The power transmission from Vi2 to the load becomes faulty when switches S2 to S7 fail. Therefore, only switches S2 to S7 affect the reliability estimation of the system. According to references43,44, the reliability of the H-bridge switches can be calculated using the following equation:

where \({\text{R}}\left({\text{t}}\right)\) is the reliability of the entire system, \({\lambda }_{\text{t}}\) is the total failure rate of the MOSFETs used in the H-bridge, and \({\text{t}}\) is the period over which the reliability is calculated. This paper evaluates the reliability of H-bridge MOSFETs by calculating the failure rate using the modern prediction standard IEC-TR-6238045,46,47,48. According to the IEC-TR-62380 standard, a mission profile is needed to calculate the failure rate based on the system's operating and environmental conditions. The mission profile table contains various parameters necessary for calculating the reliability of a system or component, taking into account all the conditions encountered during its operational lifespan. This includes environmental conditions, usage, and other factors that can impact the performance and reliability of the system or component. Table 3 presents the mission profile well-suited for the system studied in this paper. As can be seen in this table, \({\left({\text{t}}_{\text{ae}}\right)}_{\text{i}}\) is the average outside ambient temperature surrounding the equipment, during the ith phase of the mission profile, \({\left({\text{t}}_{\text{ac}}\right)}_{\text{i}}\) represents the average ambient temperature of the printed circuit board (PCB) near the components, where the temperature gradient is cancelled, \({\tau }_{\text{i}}\) is the ith working time ratio of the transistor for the ith junction temperature of the mission profile, \({\tau }_{\text{on}}\) is the total working time ratio of the transistor, \({\tau }_{\text{off}}\) is the time ratio for the transistor being in storage (or dormant) mode, and \({\text{n}}_{\text{i}}\) is the Annual number of cycles.

After determining the appropriate mission profile, it is important to calculate the total power loss for each MOSFET in order to estimate the junction temperature of each switch which is used in failure rate calculation. The total power loss for each MOSFET includes switching loss and conduction loss, which need to be calculated first47. The factors required for estimating power loss of MOSFETs are illustrated in Table 4. As can be seen in this table, the values of trise, tfall and Ron are respectively the rise time, fall time and the on-state resistance of the MOSFETs which are extracted from the datasheet. Additionally, Iswitch,max, Iswitch,rms and \({\text{V}}_{\text{DS,applied}}\) are respectively the maximum value of drain current, RMS value of the drain current and the maximum value of drain-source voltage impinged to the MOSFET. Also, FF and Fsw are the fundamental frequency of the load current and the switching frequency of the MOSFETs respectively.

Therefore, the total power loss for each MOSFET is calculated by Eq. (20) as follows:

In (20), \({\text{P}}_{\text{Loss-MOSFET}}\) is the total power loss for each MOSFET, \({\text{P}}_{\text{sw}}\) represents the switching loss for each MOSFET, and \({\text{P}}_{\text{cond}}\) is the conduction loss for each MOSFET. The conduction loss of the MOSFET is calculated by Eq. (21) as follows:

Therefore, by substituting the required values from Table 4, the conduction loss for each MOSFET is equal to \({\text{P}}_{\text{cond}}\; = 0.583 \text{W}\). Since the load absorbs a sinusoidal current from the H-Bridge, because a Three-Phase filter with a constant fundamental frequency of 50 Hz was utilizes, any change in the load current will only affect the peak value of the load current. So, A correction factor called K is needed to calculate the average of the maximum variable value of the drain current. Therefore, the switching loss for each MOSFET is calculated using the following equation47,48.

where the correction factor is calculated as \(\text{K} = \sum_{\rm{n} = {1}}^{\text{Q}}{\rm{sin}}\left(\frac{{2}\pi }{\text{Q}}{\rm{n}}\right)= 50.9\) in which Q is called frequency ratio in which can be calculated as \(\text{Q= }\frac{{\text{f}}_{\text{sw}}}{\text{FF}} = 80\). By substituting the value of correction factor and other essential factors from Table 4 in (22), the switching loss value would be equal to \({\text{P}}_{\text{sw}} = 0.052 \text{W}\). Therefore, the total power loss for each MOSFET is equal to \({\text{P}}_{\text{Loss-MOSFET}} = 0.635 \text{W}\).

Based on IEC-TR-62380 standard, the general formula for calculating the MOSFET failure rate can be expressed as follows:

In Eq. (23), \({\pi }_{\text{S}}\) is charge factor, \({\lambda }_{0}\) represents the base failure rate of the MOSFET, \({{\text{(}\pi }_{\text{t}}\text{)}}_{\text{i}}\) is the ith temperature factor related to the ith junction temperature of the MOSFET mission profile, \({{\text{(}\pi }_{\text{n}}\text{)}}_{\text{i}}\) is the ith influence factor related to the annual cycles of thermal variations experienced by the MOSFETs package, \({\Delta {\text{T}}}_{\text{i}}\) is the ith thermal amplitude variation of the mission profile, \({\lambda }_{\text{B}}\) is base failure rate of the MOSFET package, \({\pi }_{\text{I}}\) is the influence factor related to the use of the MOSFETs body diode, and \({\lambda }_{\text{EOS}}\) is failure rate related to the electrical overstress in the considered application. Table 5 shows the mathematical expressions and parameter values used in Eq. (23).

Ultimately, substituting the required values from Table 5 into Eq. (23) the failure rate for a single MOSFET in the proposed inverter is calculated as \({\lambda }_{\text{MOSFET}} = 12.95 \text{ (FIT)}\). So, the failure rate for six MOSFETs used in H-bridge structure will be equal to \({\lambda }_{\text{6-MOSFET}}\text{ } = { \, {6}\times \lambda }_{\text{MOSFET}} = \text{77.74 (FIT)}\). Eventually by substituting the \({\lambda }_{\text{6-MOSFET}}\) in (19) for operating period of one year \(\left(\text{t } = {365}\times {24}\right)\) the reliability of the system would be equal to \({\text{R}}\left({\text{t}}\right) = {99.93 \%}\). As it is known switches such as MOSFETs are very sensitive to the increase in their operating voltage and temperature. In these conditions, voltage and thermal accelerations cause aging chemical reactions to speed up the failure process and increase the failure rate of the MOSFET. Also, as it is known power electronic converters are designed for long life spans in order to be efficient, cost effective and to have acceptable performance in this period. Therefore, the reliability of the proposed inverter was calculated for 1 and 15 years of operation considering three different voltage stresses of 72, 94,116 and a switching frequency range of 1KHZ to 100KHZ for the MOSFETs. In this procedure different voltage stresses and switching frequencies were chosen in order to analyze their impact on the overall system's reliability. The Fig. 5a and b show how the reliability varies at different frequencies for three different voltage stresses for the MOSFETs S2 to S7 at two different time periods.

As can be seen in Fig. 5a the reliability of the system for all voltage stresses and switching frequencies is above 99.8% which is a good number that ensures a well performance for the system in aone-year period. Also, as can be seen in Fig. 5b the reliability of the system for all voltage stresses and switching frequencies is above 97.5% which is also a fairly good number that ensures the well performance for the system in the period of fifteen-years.

Simulation and experimental results

A 220-W prototype was built and tested to assess the performance of the suggested inverter in actual operating circumstances. In the tests, the input sources were connected to the proposed inverter via LC filters so that the input currents were placed nearer to the DC component. The system parameters are shown in Table 6. As can be seen in this table, the duty cycle is set to a low value in order to reduce both the input current harmonics and the load voltage harmonics. that brings the prominent advantage of producing high voltages in low duty cycle conditions for the proposed system. To demonstrate and validate the suggested inverter's capability to operate at two distinct frequencies simultaneously for Z1 and Z2, the switching frequencies for Z1 and Z2 were chosen unevenly. In order to ensure comparability between the simulation and test results, the values of the system parameters were incorporated into the simulation model. The simulation was performed using MATLAB Simulink. The simulation and experimental results are illustrated in Figs. 6, 7, 8 and 9.

Experimental results (Time/div: for (a) is 10 \(\mu\) s, for (b,c,e–g) is 50 \(\mu\) s, for (d) and (h) is 10 ms.), (\({\text{T}}_{{\text{Z}}{1}}\) and \({\text{T}}_{{\text{Z}}{2}}\) are switching period of Z1 and Z2, respectively), (Volt/div and Ampere/div for each carve are added in each part with specific colors).

The average values for the currents absorbed from input sources 1 and 2 in simulation and test results are 4.6, 2.9, 4.7, and 2.6 Amperes, respectively, as shown in Figs. 6a,b, and 9a. Additionally, the voltage of the independent sources connected to the converters inputs are shown in Fig. 8a and b. As can be seen in these figures the proposed converter is capable of supplying the load with one or both of Vi1 and Vi2 Since there are portions of times in which one or both of VO1 or VO2 have non-zero voltages simultaneously. Also, Fig. 8d and the test results (Fig. 9c) show that the value of DC-link voltage (\({\text{V}}_{{\text{O}}{2}}\)) in the NSTS in simulation and test results to be 92 and 94 Volts, respectively. The transformer's primary winding current in the NSTS essentially needs to be equal to the current of the magnetizing inductors for the system function properly (iL1 and iL2). And since at this time, the magnetizing inductors of the transformers are discharged, their currents need to be reduced. Also, at the same time, the currents of the secondary windings have to be zero. With these explanations and by referring to Figs. 6f and h and 9b and f, it can be seen that the primary and secondary windings currents are in line with the expected outcomes. In the shoot-through time, however, both primary and secondary windings are conducting. The primary winding currents, minus their magnetizing currents, are multiplied by the turn ratio (\(\text{n} = \frac{{\text{N}}_{1}}{{\text{N}}_{2}}\)) and flow in the secondary windings, given that the turn ratio of the transformers in the proposed system is 2. In this regard, it is also observed that in Figs. 6f and h and 9b and f, in the shoot-through time, if the magnetizing current (which is approximately equal to the amount that flows through the primary windings in the NSTS) is subtracted from the primary windings current and then multiplied by 2 (turn ratio), the secondary windings current is obtained. In this regard, it is also noticed that, in terms of quantity, the curves of the transformers' windings currents in simulation studies and experiments with good accuracy are equal. As regards such other variables as inductors voltage and current, capacitors voltage, and so on, it can be seen that the simulation results (Figs. 6 and 7) verify the experimental results presented in Fig. 9. A few differences between the experimental and simulation results are due to the simulations using specific prototype parasitic elements and a lack of PCB modeling.

To calculate the efficiency of the proposed inverter in the fundamental frequency (50 Hz), the input and output active powers are to be computed. Figure 9a shows that the active power generated by the sources is:\({\text{V}}_{{\text{i}}{1}}\times {\text{I}}_{{\text{i}}{1}}+{\text{V}}_{{\text{i}}{2}}\times {\text{I}}_{{\text{i}}{2}} = {30}\times \text{4.7}+{30}\times {2.6} = {219}\) watt; and Fig. 9h shows the active power absorbed by the load is:\({3}\times {\text{R}}\times {\text{I}}_{\text{rms-phase-}{50}{\text{Hz}}}^{2} = {3}\times {45}\times ({\frac{1.7}{\sqrt{2}})}^{2} = {199.1}\) watt. Therefore, the efficiency of the system is determined at about 91%.

Some high-frequency noises, observable in Fig. 9h, are related to non-ideal and parasitic elements of the output filter. This causes some high-frequency current components to pass through the output filter.

For evaluating the contribution of the sources in supplying the load, the value of \(\frac{{P}_{i1}}{{P}_{i2}}\) needs to be calculated. Figure 4 (b) shows if \(\frac{{\text{V}}_{{\text{i}}{1}}}{{\text{V}}_{{\text{i}}{2}}} = {1}\text{; n=}\frac{1}{{2}}\), \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) is equal to 1.6. If \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) is calculated according to the experimental results (Fig. 9a), \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) is equal to 1.8. Some differences between Figs. 4b and 9a in calculations of \(\frac{{\text{P}}_{{\text{i}}{1}}}{{\text{P}}_{{\text{i}}{2}}}\) are related to the ideal system consideration in section “An analysis of steady state relations and power-sharing”.

Figures 7d–f, 8d and 9c,d show the leakage inductors of the transformers used in the suggested inverter do not cause voltage spikes on DC-link and line-line voltages. Therefore, using the inverter in high-power applications requires no such considerations as protection and control of the switches and their switching losses.

Figure 10a and b show that if parasitic elements of the system and the topology of Ref.1 are considered, the proposed inverter has higher efficiency (more than 10%) while the voltage gain of the proposed inverter at powers higher than 1700 watts is almost equal to that of the topology in Ref.1. Therefore, eliminating some active and passive components from the topology of Ref.1 brings about improvements in cost, weight, volume, and efficiency in high-power applications.

Efficiency is one of the most crucial factors in the performance evaluation of an inverter. A comparison was made between the proposed inverter and some of the references mentioned in the literature. The efficiencies of the proposed inverter and those in previous works have been shown in Table 7. In this comparison, it should be considered that the proposed inverter is a single-stage, high voltage gain, microcontroller-based inverter which takes advantage from machine intelligence in its protection procedure. Therefore, this inverter should be compared with other works that have similar features. The inverters presented in Refs.9,10,11,32,34,35,38,39,40,41,42 are all single-stage non-microcontroller-based inverters that have a low voltage gain. Also, these inverters don’t take advantage from machine intelligence in their structure. The inverter described in reference37 is a single-stage, microcontroller-based inverter with a low voltage gain that does not benefit from machine intelligence in its structure. The inverter described in Ref.24 is a single-stage, microcontroller-based inverter with a high voltage gain, but it does not incorporate machine intelligence into its design. At the end, only the inverter presented in Ref.1 has all the same features mentioned for the proposed inverter in this paper. Based on the efficiency values of Table 7 it can be concluded that the proposed inverter has a higher efficiency in addition to having a lower semiconductor count with respect to the inverter presented in Ref.1.

Conclusion

The present research paper sets forth a multi-port three-phase inverter. This structure is based on single-stage conversion, and besides employing six switches of the classic single-input inverter, it only uses one extra switch. This structure suits such applications as hybrid renewable energy systems as it boosts voltage. Artificial intelligence based on hardware design is exploited in the proposed inverter, precluding the need for human intervention or circuit protection by DC-link electrolytic capacitors. Also presented in this paper are explanations related to the operation of the proposed inverter together with relations governing the system and the curves explaining power-sharing and voltage gains. The possibility to individually control the power ratio absorbed from the input sources and the DC-link voltage is demonstrated. The proposed inverter is further shown to exhibit higher efficiency in high-power applications. The operation of the prototype has been verified through simulation studies using prototype parameters.

Data availability

Data and codes for simulation-based items can be furnished on demand from the corresponding author.

Change history

20 February 2024

A Correction to this paper has been published: https://doi.org/10.1038/s41598-024-54747-w

References

Varzaneh, M. G., Rajaei, A., Jolfaei, A. & Khosravi, M. R. A high step-up dual-source three-phase inverter topology with decoupled and reliable control algorithm. IEEE Trans. Ind. Appl. 56, 4501–4509 (2019).

Ghani Varzaneh, M., Rajaei, A. & Mardaneh, M. Dual-source inverter for hybrid PV–FC application. SN Appl. Sci. 1, 1470 (2019).

Ghavidel, B. Z., Babaei, E. & Hosseini, S. H. An Improved Three-Input DC-DC Boost Converter for Hybrid PV/FC/Battery and Bidirectional Load as Backup System for Smart Home. in 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC). 533–538 (2019).

Mohseni, P., Hosseini, S. H., Sabahi, M., Jalilzadeh, T. & Maalandish, M. A new high step-up multi-input multi-output DC–DC converter. IEEE Trans. Ind. Electron. 66, 5197–5208 (2018).

Zeng, J., Yu, Z., Liu, J. & Liu, F. Triple-compound-full-bridge-based multi-input converter with wide zero-voltage switching range and wide conversion gain. IEEE Trans. Ind. Electron. 67, 9260–9272 (2019).

Jabbari, M. & Dorcheh, M. S. Resonant Multi-input/Multi-output/Bidirectional ZCS Step-Down DC–DC Converter With Systematic Synthesis for Point-to-Point Power Routing. IEEE Trans. Ind. Electron. 33, 6024–6032 (2017).

Reddi, N. K., Ramteke, M. R., Suryawanshi, H. M., Kothapalli, K. & Gawande, S. P. An isolated multi-input ZCS DC–DC front-end-converter based multilevel inverter for the integration of renewable energy sources. IEEE Trans. Ind. Appl. 54, 494–504 (2017).

Kardan, F., Alizadeh, R. & Banaei, M. R. A new three input DC/DC converter for hybrid PV/FC/battery applications. IEEE J. Emerg. Sel. Top. Power Electron. 5, 1771–1778 (2017).

Yang, F., Ge, H., Yang, J., Dang, R. & Wu, H. A family of dual-buck inverters with an extended low-voltage DC-input port for efficiency improvement based on dual-input pulsating voltage-source cells. IEEE Trans. Ind. Electron. 33, 3115–3128 (2017).

Yang, F., Ge, H., Yang, J., Dang, R. & Wu, H. An asymmetrical multi-level dual-input dual-buck inverter for multi-source interface applications. in IEEE Applied Power Electronics Conference and Exposition (APEC). 2228–2233 (2017).

Zhu, L., Wu, H., Mu, T., Yang, F. & Ma, X. An asymmetrical three-level dual-input bidirectional DC/AC converter with improved conversion efficiency for vehicle-to-grid application. in IEEE Applied Power Electronics Conference and Exposition (APEC). 2062–2067 (2017).

Mu, T., Zhu, L., Wu, H. & Jiang, W. A semi-two-stage DC-AC power conversion system with improved efficiency based on a dual-input inverter. in IEEE Energy conversion congress and exposition (ECCE). 1–6 (2016).

Zhang, N., Sutanto, D. & Muttaqi, K. M. Design and control of a boost inverter based multi-input converter. in IEEE International Conference on Smart Grid Communications (SmartGridComm). 588–593 (2016).

Dehghan, S. M., Mohamadian, M., Yazdian, A. & Ashrafzadeh, F. A dual-input–dual-output Z-source inverter. IEEE Trans. Ind. Electron. 25, 360–368 (2009).

Li, D., Gao, F., Loh, P. C., Zhu, M. & Blaabjerg, F. Hybrid-source impedance networks: Layouts and generalized cascading concepts. IEEE Trans. Ind. Electron. 26, 2028–2040 (2010).

Yan, C., Zou, S. & Xu, D. Power control for dual-input DC/AC inverter. in IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG). 1–8 (2015).

Jiang, S. & Peng, F. Z. Modular single-phase trans-Z-source inverter for multi-input renewable energy system. in Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC). 2107–2114 (2012).

Azizi, M., Mohamadian, M. & Beiranvand, R. A new family of multi-input converters based on three switches leg. IEEE Trans. Ind. Electron. 63, 6812–6822 (2016).

Chemali, E. & Emadi, A. On the concept of a novel Reconfigurable Multi-Source Inverter. in IEEE Transportation Electrification Conference and Expo (ITEC). 707–713 (2017).

Dorn-Gomba, L., Magne, P., Danen, B. & Emadi, A. On the concept of the multi-source inverter for hybrid electric vehicle powertrains. IEEE Trans. Ind. Electron. 33, 7376–7386 (2017).

Dorn-Gomba, L., Magne, P., Barthelmebs, C. & Emadi, A. On the concept of the multi-source inverter. in IEEE Applied Power Electronics Conference and Exposition (APEC). 453–459 (2016).

Peng, F. Z. Z-source inverter. IEEE Trans. Ind. Appl. 39, 504–510 (2003).

Ellabban, O. & Abu-Rub, H. Z-source inverter: Topology improvements review. IEEE Ind. Electron. Mag. 10, 6–24 (2016).

Varzaneh, M. G., Rajaei, A., Forouzesh, M., Siwakoti, Y. P. & Blaabjerg, F. A single-stage multi-port buck-boost inverter. IEEE Trans. Ind. Electron. 36, 7769–7782 (2020).

Das, M. & Agarwal, V. Novel high-performance stand-alone solar PV system with high-gain high-efficiency DC–DC converter power stages. IEEE Trans. Ind. Appl. 51, 4718–4728 (2015).

Debnath, D. & Chatterjee, K. Solar photovoltaic-based stand-alone scheme incorporating a new boost inverter. IET Power. Electron. 9, 621–630 (2016).

Dutta, S. & Chatterjee, K. A buck and boost-based grid connected PV inverter maximizing power yield from two PV arrays in mismatched environmental conditions. IEEE Trans. Ind. Electron. 65, 5561–5571 (2017).

Kwon, J.-M., Kwon, B.-H. & Nam, K.-H. Grid-connected photovoltaic multistring PCS with PV current variation reduction control. IEEE Trans. Ind. Electron. 56, 4381–4388 (2008).

Liao, Y.-H. & Lai, C.-M. Newly-constructed simplified single-phase multistring multilevel inverter topology for distributed energy resources. IEEE Trans. Power. Electron. 26, 2386–2392 (2011).

Rahim, N. A. & Selvaraj, J. Multistring five-level inverter with novel PWM control scheme for PV application. IEEE Trans. Ind. Electron. 57, 2111–2123 (2009).

Jain, S. & Agarwal, V. An integrated hybrid power supply for distributed generation applications fed by nonconventional energy sources. IEEE Trans. Energy Conv. 23, 622–631 (2008).

Serban, E., Paz, F. & Ordonez, M. Improved PV inverter operating range using a Miniboost. IEEE Trans. Power. Electron. 32, 8470–8485 (2016).

Wang, Y. & Wang, F. Novel three-phase three-level-stacked neutral point clamped grid-tied solar inverter with a split phase controller. IEEE Trans. Power. Electron. 28, 2856–2866 (2012).

Kumar, N., Saha, T. K. & Dey, J. Control, implementation, and analysis of a dual two-level photovoltaic inverter based on modified proportional–resonant controller. IET Renew. Power. Gener. 12, 598–604 (2018).

Kumar, N., Saha, T. K. & Dey, J. Multilevel inverter (MLI)-based stand-alone photovoltaic system: Modeling, analysis, and control. IEEE Systems. J. 14, 909–915 (2019).

Thang, T., Thao, N., Jang, J.-H. & Park, J.-H. Analysis and design of grid-connected photovoltaic systems with multiple-integrated converters and a pseudo-dc-link inverter. IEEE Trans. Ind. Appl. 61, 3377–3386 (2013).

Haddadi, A. M., Farhangi, S. & Blaabjerg, F. A reliable three-phase single-stage multiport inverter for grid-connected photovoltaic applications. IEEE J. Emerg. Sel. Top. Power Electron. 7, 2384–2393 (2018).

Keyhani, H. & Toliyat, H. A. Single-stage multistring PV inverter with an isolated high-frequency link and soft-switching operation. IEEE Trans. Power. Electron. 29, 3919–3929 (2013).

Keyhani, H., Toliyat, H. A. & Alexander, W. C. A single-stage multi-string quasi-resonant inverter for grid-tied photovoltaic systems. in IEEE Energy Conversion Congress and Exposition (ECCE). 1925–1932 (2013).

Bilakanti, N., Zheng, L., Kandula, P., Kandasamy, K. & Divan, D. Single stage soft-switching tri-port converter for integrating renewable source and storage with grid through galvanic isolation. in IEEE 19th European Conference on Power Electronics and Applications (ECPEA). P.1-P.10 (2017).

Singh, S. A., Carli, G., Azeez, N. A. & Williamson, S. S. Modeling, design, control, and implementation of a modified Z-source integrated PV/grid/EV DC charger/inverter. IEEE Trans. Ind. Electron. 65, 5213–5220 (2017).

Amirabadi, M., Toliyat, H. A. & Alexander, W. C. A multiport AC link PV inverter with reduced size and weight for stand-alone application. IEEE Trans. Ind. Appl. 49, 2217–2228 (2013).

Kales, P. Reliability: for technology, engineering, and management. Englewood Cliffs, NJ: Prentice-Hall. Ch. 1 (1998).

Yang, Y., Wang, H., Sangwongwanich, A. & Blaabjerg, F. Design for reliability of power electronic systems. In Elsevier Power electronics handbook. 1423–1440 (2018).

Committee, I. T. Reliability data handbook-universal model for reliability prediction of electronics components, PCBs and equipment, 1st ed. IEC TR 62380. (2004).

Butnicu, D., Neacsu, D. O. & Cracan, A. A study of switching frequency impact on reliability of DC-DC PoL converters with discrete transistors. IEEE Trans. Ind. Appl. 59, 6373–6383 (2023).

De León-Aldaco, S. E., Calleja, H., Chan, F. & Jiménez-Grajales, H. R. Effect of the mission profile on the reliability of a power converter aimed at photovoltaic applications—A case study. IEEE Trans. Power. Electron. 28, 2998–3007 (2012).

Babaei, A., Najafizadeh, A., Kaffashan, I. & Rezaei, H. A Corrected method for Calculation of Failure Rate Based on IEC-TR-62380. in IEEE International Power System Conference (PSC). 417–422 (2019).

Vishay Siliconix, https://www.vishay.com/docs/91237/91237.pdf , IRFP460 Power MOSFET datasheet, (2023)

Author information

Authors and Affiliations

Contributions

M.G.V. provided the main idea, wrote the initial text with A.R., and did the experimental tests. N.K.-O. and A.S.-P. did the simulations. M.K. edited the final text.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The original online version of this Article was revised: In the original version of this Article Mohamadreza Khosravi and Ali Shams-Panah were incorrectly affiliated. Full information regarding the corrections made can be found in the correction for this Article.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ghani Varzaneh, M., Rajaei, A., Kamali-Omidi, N. et al. A single-stage dual-source inverter using low-power components and microcomputers. Sci Rep 14, 1804 (2024). https://doi.org/10.1038/s41598-024-51513-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-51513-w

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.