Abstract

To address the rising demand for high-speed wireless data links, communication systems operating at frequencies beyond \({100}\,\hbox {GHz}\) are being targeted. A key enabling technology in the development of these wireless systems is the phased antenna array. Yet, the design and implementation of such steerable antenna arrays at frequencies over \({100}\,\hbox {GHz}\) comes with a multitude of challenges. In particular, the cointegration of active electronics at each antenna element poses a major hurdle due to the inherent space constraints in the array. This article proposes a novel scalable concept for opto-electronic phased antenna arrays operating at 140 GHz. It details the system architecture of a transmitter that enables the implementation of large scale, wideband, 2D steerable phased antenna arrays and presents the design and measurement of a compact SiGe power amplifier (PA) chip to be used as one of its key building blocks. The amplifier achieves a gain of 20 dB at 135 GHz, features a \(P_{1dB}\) of 14.6 dBm and can support data rates up to 45 Gbps in a limited footprint of only 540μm × 550μm. This makes it one of the fastest, most powerful D-band power amplifiers in literature with a footprint compatible with \(\frac{\lambda }{2}\)-spaced phased array integration.

Similar content being viewed by others

Introduction

High-speed wireless communication has seen a significant increase in demand over the past few years. The development and subsequent rollout of 5G networks has a significant contribution to this. In order to support the increasing demand for wireless communication bandwidth, higher millimeter-wave (mmWave) and sub-THz carrier frequencies are under investigation1,2,3. Currently, the D-band (110 GHz – 170 GHz) is an attractive candidate, not only for high-speed wireless communication4 but also for applications like high-resolution radar front ends5,6 or spectroscopy7. This can be attributed to the very large aggregated available and unlicensed bandwidth. However, the realisation of such wireless D-band systems comes with many challenges. In particular, path loss experienced by the signal is a severely limiting factor in the performance of these mmWave systems, increasing by approximately 15 dB when moving from 5G mmWave at approximately 30 GHz to the D-band at 140 GHz. As such, to fully exploit the potential of wireless D-band communication links, technologies used in the 5G mobile communication network will need to evolve further, incorporating novel advancements and innovations to further enhance spectral efficiency, energy efficiency, and reliability. One key enabling technology that will be indispensable for these D-band systems are steerable or phased antenna arrays. These antenna arrays significantly increase link budget compared to a single antenna element, up to \(20log_{10}(N)\) dB8, with N being the number of elements in the array. Note that this is only the case if every antenna is equipped with its own dedicated power amplifier, thereby also upscaling the transmitter’s power consumption. The total array gain can be further increased to \(30log_{10}(N)\) if a similar array is used at the receiver side. This allows the signal to overcome the extreme propagation loss at D-band frequencies. However, this compensation requires a large amount of antennas, raising the need for an efficient, highly scalable solution. For instance, commercial mmWave antenna arrays typically use between 16 and 64 antennas for 5G wireless networks around 30 GHz9,10 and up to 256 antenna elements for 60 GHz fixed wireless access networks11. If this trend continues, it is safe to assume that commercially viable D-band arrays will use hundreds, if not thousands of antenna elements. Their steerability is not only a crucial feature in mobile systems with fast-moving users, but also for alignment purposes in fixed-beam use cases due to the narrow beamwidth of large-scale antenna arrays12.

The implementation of very large (phased) antenna arrays raises a number of challenges itself. First, there is the signal distribution problem. If we assume the case of purely passive splitting and routing, the maximum number of elements in the array is limited by the feeding losses. Expanding the array beyond a certain size has an adverse effect because the increase in array gain is negated by additional feeding losses. It is possible to overcome this limitation using additional amplification hardware as shown in13. Unfortunately, this significantly increases the complexity and power consumption of the circuit and is difficult to implement at such high frequencies. As such, an efficient signal distribution network is imperative to be able to support large antenna arrays. The steerability requirement of the array also raises the question of how to handle beamsteering. Traditional electronic beamsteering is implemented by controlling the phase shift between the different array elements. This narrowband approximation of a delay introduces beam squint, where the array’s beam is steered in different directions depending on the frequency of the signal14. Evidently, this can have drastic effects on performance when steering broadband signals over a large scanning range using an array with a very narrow beamwidth. Shifting to a time delay-based approach avoids this issue but is difficult to achieve electronically over wide delay spreads15. These particular challenges can be overcome by leveraging optical techniques. The inclusion of optical components is already prevalent in existing radio systems in the form of radio-over-fiber (RoF). Here, optical fiber infrastructure is used to distribute radio signals from a central office (CO) to remote radio units (RRUs)16,17,18. Moving to such a partially optical system allows us to leverage the wide gamut of optical components and techniques such as extremely low-loss signal distribution, true-time delay (TTD) beamforming or even on-chip optical modulation to overcome the issues faced in an all-electrical approach19,20,21.

Lastly, one of the most restricting issues in the design of steerable D-band arrays lies with the cointegration of active electronics with each individual antenna element. As shown by Sadhu et al.12, the unit elements in antenna arrays and their respective spacing shrink as the array’s frequency of operation increases. However, the active electronics driving each individual antenna element don’t shrink at nearly the same rate as the antennas do. In the past, this issue was much less prevalent since even at 30 GHz, a \(\frac{\lambda }{2}\)-spaced array still has an area of 25mm2 per antenna element to accomodate integrated circuits (ICs) for amplification, beamforming, digital control etc. The importance of this issue becomes clear when reviewing the current state-of-the-art on sub-THz phased antenna arrays in literature. Kim et al.22 and Gomez-Torrent et al.23 present the implementation of very large-scale, 2D arrays. While these achieve very good bandwidth and gain, they do not support beamsteering or integration of other active electronics due to their multilayer waveguide feeding network. Laminen et al.24 show a 4×4 D-band antenna array with a fractional bandwidth of 14%, although no beamsteering electronics are integrated and the high microstrip feedline losses limit scaling to larger antenna arrays. Other implementations are steerable, yet achieve this through varying the center frequency, giving rise to beam squint25,26. This imposes a significant data rate limit on the system. Abu-Surra et al.15 present a phased array with a substantial steering range, although this can only be done in one dimension over a limited 2 GHz bandwidth. Finally, Dong et al.27, Elkhouly et al.28 and Ahmed et al.29 all show very impressive implementations and demonstrations for steerable Tx/Rx arrays, with Ahmed et al. showing actual beamsteering measurement results. It should be noted however that scaling in all of these solutions is limited as they rely on extra tunable gain elements to compensate for high-frequency transmission line feeding losses. In summary, despite the impressive strides made in this research area in these past few years, the authors of this work currently have no knowledge of a solution that enables the implementation of very large-scale, wideband, 2D-steerable antenna arrays.

This work presents a novel, scalable concept for opto-electronic active phased antenna arrays operating in the D-band. The proposed system will provide a solution to the aforementioned issues currently plaguing the design of sub-THz phased antenna arrays. Most importantly, this work details the design and verification of a D-band power amplifier IC that suitable for integration into the aforementioned system. First, the Opto-Electronic Transmitter System Architecture section will discuss the proposed opto-electronic transmitter system architecture, briefly elaborate on the function of each component and derive specifications for the required power amplifier. Next, the Power Amplifier Design & Measurements section elaborates on the development of this power amplifier IC, including both the design procedure and measurement results. Lastly, the Conclusion section summarizes the main findings of this manuscript.

Opto-electronic transmitter system architecture

The introductory section already touched on some of the most significant challenges to be addressed in the development of D-band phased antenna arrays. These include low-loss signal distribution, broadband and beam squint-free beamsteering and finally, the cointegration of the array with active electronics.

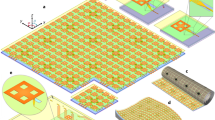

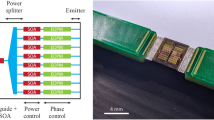

To tackle these problems, we propose a novel concept for a D-band phased array transmitter. The block diagram of the proposed system architecture for this multi-antenna system, shown in Figure 1, represents the implementation of an exemplary 2×2 array. To alleviate the drawbacks of conventional all-electronic approaches, an opto-electronic architecture is adopted. The transmitter is implemented as an array of active opto-electronic antenna elements supported by an optical front-end module. The active antenna element implements opto-electric conversion, amplification and radiation. The optical front-end, which is implemented on a silicon-photonics (Si-Ph) PIC, handles the signal distribution and beamforming. Notice that, using this architecture, the system is not limited to a 4-element configuration and can be scaled up further to hundreds of antennas according to the specific application. The next paragraph explains the function and specifications of each component in more detail.

At 140 GHz, antenna elements suited for phased array integration are ideally around 1 mm × 1 mm (half of the free-space wavelength) in size with a spacing between 1 mm and 1.3 mm to ensure a grating lobe-free steering range of 180° down to 60° respectively30. This yields an integration density of approximately 100 antennas per cm2. To facilitate the broadband feeding of such a high number of densely packed antennas while enabling two-dimensional beamsteering, we propose integrating these antenna elements into the backside of the substrate of a photonic IC as is shown in Figure 1. This PIC itself is used as a platform for signal distribution as well as beamforming. By employing an analog radio-over-fiber (ARoF) scheme where the 140 GHz signal is directly modulated onto an optical carrier, the signal can be distributed over the array through ultra low loss optical waveguides. The loss of these waveguides can be as low as 3 dB/m31, compared to a loss of approximately 1 dB/cm for state-of-the-art electrical waveguides at these frequencies32. Because of this low loss, the PIC can easily be reused to implement an optical beamforming network (OBFN)33,34 through a network of switchable delay lines which act as true-time delay (TTD) cells. As these apply a different phase to each frequency of the signal, the issue of beam squint is negated. While the optical waveguides on the PIC offer low-loss interconnects to each of the antennas, these optical signals should still be converted into an electrical current with a high-speed photodiode (PD). At D-band frequencies, PDs can typically only supply a maximum of a few milliwatts of power35. Hence, a dedicated D-band power amplifier is required at each antenna element to provide amplification of the signal up to a level suitable for transmission. As mentioned in the introductory paragraph, the small spacing between the antenna elements severely restricts the footprint of the electronics that are integrated together with each antenna element. In turn, this has serious implications on the performance of the PA. Its footprint has to be limited to a fraction of the wavelength that corresponds to the highest frequency of operation, meaning that a system-level bandwidth specification should be derived. When considering a system-level point of view, a throughput of at least 100 Gbps is targeted to enable next-generation high-throughput applications. If we assume relatively simple modulation schemes such as 16-QAM or 32-QAM, a bandwidth of \({20}\,\hbox {GHz}\) to \({25}\,\hbox {GHz}\) is required. This is also in line with the current state-of-the-art for power amplifiers at this frequency8,36,37. If we consider a realistic steering range of [\({-45}^\circ ,{45}^\circ\)], the inter-element spacing cannot exceed \(0.59\lambda _{min}\) × \(0.59\lambda _{min}\) where \(\lambda _{min}\) is the wavelength corresponding to the array’s highest frequency of operation30. Combined with a 20 GHz bandwidth centered around 140 GHz, the PA’s dimensions can certainly not exceed \({1.18}\,\hbox {mm}\) × \({1.18}\,\hbox {mm}\). However, considering that space should be left to accomodate PD integration and DC routing, a more stringent \({0.8}\,\hbox {mm}\) \(\times\) \({0.8}\,\hbox {mm}\) footprint restriction will be imposed. This limits both the output power and the gain of the PA as both power combining techniques and the cascading of many amplifier stages are off the table.

Power amplifier design & measurements

In this section, we will describe the design and validation of a compact D-band power amplifier. Because of the very high frequency of operation, a high-performance semiconductor process is a necessity to achieve acceptable gain and output linearity. If RF performance is the only concern, an InP or other III/V technology would be an obvious choice as these devices feature very high \(f_{T}/f_{max}\) and good voltage handling, making them very attractive options for the development of sub-THz power amplifiers38. However, their larger size, restrictive back-end-of-line (BEOL) and lack of support for logic or control circuitry makes them less favorable than eg BiCMOS technologies37,39,40. In this work, a SiGe BiCMOS technology with \(f_{T}/f_{max}\) of \(350/{450}\,\hbox {GHz}\) and a copper BEOL was used. The latter is crucial as it enables low-loss interconnections and passives. The following paragraphs elaborate further on both the design and measurement results of this power amplifier chip.

Circuit implementation

The schematic of the proposed power amplifier is shown in Figure 2. The circuit consists of a driver stage and a power stage which are both biased in class A to maintain high gain and linearity. Both stages feature a similar pseudo-differential cascode topology. Using a cascode circuit has multiple advantages. First, a higher gain can be achieved than with common emitter (CE) or common base (CB) configurations. Co-simulating the schematic-level transistor model provided by the foundry combined with the EM-simulated layout of basic interconnection metallization, both the CE and CB configurations yield a maximum available gain (MAG) of around 8 dB. However, when looking at Figure 3, which showcases the MAG and the input/output reflection coefficients of the cascode circuit, we see that its performance is significantly higher, achieving a MAG of over 18 dB at \({140}\,\hbox {GHz}\). Note that the right part of the MAG curve depicts the maximum stable gain (MSG) as opposed to the MAG since the amplifier is not unconditionally stable. The loss required to stabilize the amplifier is handled through the inherently lossy matching circuits. This is in stark contrast with the simple CE and CB configurations which would need very low-loss matching networks to produce a useful amount of gain in this technology. The higher gain per stage also reduces the required number of stages to reach a suitable gain specification. Combined with the compactness of the topology, this significantly reduces the footprint of the final IC. In order to boost the gain of the cascode amplifier, an internal matching network is sometimes implemented in between the two transistors. Such a matching network can reduce the impedance mismatch between the output of the bottom CE transistor and the input of the top cascode transistor, essentially a CB amplifier, increasing the MAG. Using a tool such as the S-Parameter Probe component in Keysight ADS, the internal impedance levels at this node when looking into either side of the circuit can be obtained without disturbing its function. This indeed shows a discrepancy between both quantities. However, even when both are conjugately matched to eachother using a matching circuit, the increase in MAG is negligible considering the space needed for the implementation of such a matching circuit.

The second major advantage of the cascode topology is its increased supply voltage as the voltage swing at the output of the amplifier is now divided over 2 devices, although not equally. The higher supply voltage allows for an in increased voltage swing at the amplifier’s output, which in turn yields a higher maximum output power. Lastly, the pseudo-differential character of the circuit signifies that while the core circuit operates differentially, the interfacing with the IC is done in a single-ended way. In this case, the single-ended to differential conversion is achieved through integrated input and output transformers operating as baluns, indicated as \(TF_{in}\) and \(TF_{out}\) on the schematic in Figure 2. Having a single-ended interface with the IC significantly simplifies measurements and also facilitates integration with other components. In this case, these baluns also operate as matching networks. However, a problem arises when trying to match the input of the driver or power stage to an inductive impedance such as a transformer. As shown in Figure 3, their input impedance is inductive due to the high frequency of operation, making it impossible to attain a good power match without additional components. The series capacitors \(C_{in, MN}\) and \(C_{inter, MN}\) are therefore added to the circuit to shift the input impedance back to the capacitive half-plane of the Smith chart. This impedance transformation is illustrated using the input matching network of the driver stage on the Smith chart in Figure 4.

In terms of sizing, we use 20-emitter devices in the power stage to obtain as much output power as possible while maintaining a realisable optimal load impedance. The driver stage is a scaled down version of the power stage, both in bias current and in the size of devices as the gain of the power stage lowers the output power requirement of any previous stages. Simulations were performed using the completed output stage to verify the impact of the driver stage output power on the complete amplifier’s compression point. This yielded that a driver stage with a scaling factor of 2 was sufficient to minimize its influence, giving rise to 10-emitter devices in the driver stage.

Layout implementation

Arguably the most critical step in a sub-THz RFIC design is translating the circuit to a layout as careless implementation will have a detrimental effect on the performance of the IC. When designing circuits operating at frequencies > 100 GHz, EM simulations of the entire RF core are an absolute necessity in the iterative design and optimization process but also as a means of verification. Figure 5 shows the layout of the PA’s output stage. Note the high degree of symmetry to ensure good differential operation and compact integration to minimize parasitics. As mentioned before, each transistor from the schematic in Figure 2 is implemented as 2 10-emitter devices to support higher output power.

Since this amplifier relies on a cascode topology operating at very high frequencies, great care needs to be taken to adequately decouple the base of every cascode transistor as it is well known that any parasitic inductance at this node can destabilize the amplifier41. Here, this potential issue is avoided by adding multiple decoupling stages to the relevant base nodes. First, high frequency decoupling is provided very close to the base of all cascode transistors using high-Q, high self-resonance frequency (SRF), low-capacitance MIM capacitors, indicated by \(C_{casc}\) on the schematic in Figure 2 and the layout in Figure 5. A \({100}\,\Omega\) series resistor \(R_{casc}\) is then added to dampen potential oscillations. This component also diminishes the influence of hard to model external components such as bondwires and DC sources on the impedance level seen at these base nodes, thereby increasing the predictability of the circuit. Finally, low-Q, high capacitance decoupling cells further away from the devices are added. This ensures an impedance that is low at high frequencies and well-modeled for lower frequencies at every potentially problematic node.

Taking this into account, an EM/circuit co-simulation of the PA stage’s core was carried out using Cadence EMX. This model was then used in a load-pull simulation to determine the PA’s optimum load impedance \(Z_{L,opt}\). This yielded an optimum load impedance of \(3.8 + 14j \Omega\). Notice that the resistive part of \(Z_{L,opt}\) is rather small; this is a consequence of the high number of parallel devices in the output stage, meaning that the size of this stage is close to the upper limit for this technology at this frequency. The small resistive part of \(Z_{L,opt}\) also implies that little parasitic resistance can be tolerated in the output matching network.

The design of the output matching network, a transformer in this case, is handled different from a classic matching network. Since the impedance transformation realized by the balun is fairly complex at these frequencies, it will be considered as a normal 2-port device that will be optimized for input/output matching as well as transmission. This means that during the design procedure, we consider the transformer’s simultaneously matched source and load reflection coefficients (\(\Gamma _{S/L,SM}\)) as well as its MAG, signifying the transformer’s inherent loss. The goal now becomes to design a transformer with \(\Gamma _{S,SM} \leftrightarrow Z_{L,opt}^{*}\), \(\Gamma _{L,SM} \leftrightarrow 50 \Omega\) and a MAG that is as high as possible. To achieve the low resistive impedance part at the input, the primary winding of the output balun is comprised of multiple, thick metal layers to minimize parasitic resistance. The output matching requirement initially poses a problem as a transformer is inherently an inductive device, meaning that \(\Gamma _{L,SM}\) will always have a capacitive component unless the transformer is used exactly at its SRF, which would require a very large transformer. However, this issue can easily solved by adding a capacitor in parallel with the secondary windings, resonating out the inductive part. In practice, this capacitor can be absorbed in the output transmission line by slightly lowering its characteristic impedance. In order to increase matching between simulation and measurements, the transformer was encased with metallic sidewalls that are connected to the chip’s groundplane. Note that no ground shield underneath the transformer was used as the coupling to it increases the total loss by over a dB. The transformer was designed and optimized using Cadence EMX. Its S-parameters with respect to \(Z_{L,opt}^{*}\) at the input and \(50 \Omega\) at the output are presented in Figure 6. The transformer achieves a transmission of -1.1 dB and a return loss of more than 20 dB at both input and output.

Measurement results

The power amplifier IC is fabricated using the IHP SG13G2Cu process. Its micrograph is shown in Figure 7. The amplifier’s total area is 540×550 μm2, while the RF core only takes up 250 × 540μm2. The amplifier is first characterized in small-signal as well as in large-signal regime. Small-signal measurements are obtained via range extender-based S-parameter measurements and large-signal performance is assessed by performing a power sweep at the input of the amplifier and measuring transmission to the output. This allows us to extract the PA’s 1-dB compression point and its saturated output power. All of these measurements were performed via on-wafer probing using an MPI TS200-THZ Probing System and FormFactor Infinity waveguide probes. This measurement setup is shown in Figure 8. The waveguide probes are directly connected to VDI WR6.5 VNAX TxRx range extender modules which in turn are connected to a Keysight N5247B PNA-X. Using a GSG calibration susbtrate, an S-parameter calibration was performed up to the probe tips.

Small-signal measurements

Figure 9 depicts the S-parameter measurement data. The amplifier exhibits a peak gain of approximately 20 dB with a 3 dB bandwidth of 25 GHz between 120 and 145 GHz. Additionally, the amplifier’s input reflection coefficient shows a -10dB bandwidth that encompasses almost the complete measurement range aside from a small peak around 135 GHz.

Large-signal measurements

In order to perform large-signal/output power measurements, a source/receiver power calibration was performed up to the probe tips. Afterwards, the source power was swept and the output power and \(S_{21}\) are measured at different frequencies from \({120}\,\hbox {GHz}\) to \({145}\,\hbox {GHz}\). Figure 10 depicts \(P_{1dB}\) and \(P_{sat}\) over frequency as well the AM-AM and AM-PM distortion at \({125}\,\hbox {GHz}\). The 1dB output compression point of the power amplifier peaks at \({125}\,\hbox {GHz}\) at 14.6 dBm while the highest measured output power is 15 dBm. It should be noted that due to the limitations of the measurement equipment, the PA could not be completely saturated. This results in a 6.5% power-added efficiency (PAE) at 1dB compression and a maximum PAE of 7%. Note that the low PAE is a direct consequence of not being able to saturate the PA as it is essentially still operating under backoff. It is also worthy to note that the thermal dissipation of these PAs will not be negligible when assembled into an array as any D-band PA’s low efficiency will give rise to a thermal power density of close to \({0.5}\,\hbox {W}/\hbox {mm}^{2}\). However, due to the system architecture’s design, this thermal power can easily be dissipated without disturbing the antenna elements.

Table 1 gives an overview of D-band power amplifiers in literature. Here we can see that this IC achieves state-of-the-art performance when compared to other SiGe implementations. Important to note is that many chips that achieve higher output power exploit power combining, which drastically increases IC size. This makes these chips unsuitable for application in \(\frac{\lambda }{2}\)-spaced phased arrays. Consequently, our implementation is currently the most compact implementation of a D-band power amplifier to achieve this level of output power with the closest contender only including the RF core footprint of 323 μm× 790 μm while exploiting a process technology that is not yet commercially available.

Modulation measurements

Finally, time domain measurements were performed on the PA through the transmission of modulated waveforms. This directly illustrates the PA’s performance for its intended use case. The modulated signal transmission setup is shown in Figure 11. All components are mounted on an MPI TS-150 THZ probe station to allow for interfacing with the device-under-test (DUT). Using a Keysight M8196A arbitrary waveform generator (AWG), a data signal is generated on an IF carrier at 15 GHz. This IF signal is then applied to a VDI WR6.5SHM sub-harmonic waveguide mixer. The LO signal is provided by a Rohde & Schwarz SMA100B signal generator. The upconverted RF signal is injected into the DUT through a GGB PICOPROBE Model 170 WR-6 waveguide probe. Using a similar probe at the output of the DUT, the amplified signal is transferred into a Flann Microwave WR-6 variable waveguide attenuator to reduce the signal power to a safe input level for the second VDI subharmonic downconversion mixer. This second mixer uses an LO signal provided by an Anritsu MG3697C signal generator that has been locked to the first LO source. The downconverted IF signal is then analyzed and demodulated by a Teledyne LeCroy 10-65-Zi-A real-time oscilloscope (RTO) using its vector signal analysis (VSA) software. Note that no pre-distortion or equalization is applied to the signal. The resulting constellation diagrams can be seen in Figure 12. This shows that the PA is able to transmit highly complex constellations such as 64-QAM or 128-QAM while maintaining a very high SNR. Moreover, a maximum data rate of 45 Gbps is achieved using a 9 GBaud, 32-QAM format, all while maintaining an SNR larger than 20 dB.

Conclusion

This paper proposed a novel concept for wideband, 2D steerable, opto-electronic phased antenna arrays operating at 140 GHz. It presented the envisioned system architecture and its advantage over the current state-of-the-art, leveraging optical components to implement both low-loss signal distribution and TTD beamforming while using compact active opto-electronic antenna modules to perform optical-electric conversion, amplification and radiation. Moreover, the design, development, and characterization of a compact power amplifier chip in SiGe technology is presented, a key component for the realization of such photonic-enabled transmitter modules. The power amplifier IC features a gain of 20 dB over a bandwidth of \({25}\,\hbox {GHz}\) between \({120}\,\hbox {GHz}\) and \({145}\,\hbox {GHz}\) and shows a 1dB output power of 14.6 dBm with a saturated output power of 15 dBm. On top of this, modulated signal measurements show that the IC is able to transmit data at speeds up to 45 Gbps. All of this is achieved in a footprint of 540 μm × 550 μm , making it one of the fastest and most powerful D-band power amplifiers for its footprint, thereby paving the way for wideband, fully 2D-steerable opto-electronic antenna arrays.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

References

Vaigandla, K., Bolla, S. & Karne, R. A Survey on Future Generation Wireless Communications-6G: Requirements, Technologies, Challenges and Applications. Int. J. Adv. Trends Comput. Sci. Eng. 10, 3067–3076. https://doi.org/10.30534/ijatcse/2021/211052021 (2021).

Jornet, J. M., Knightly, E. W. & Mittleman, D. M. Wireless communications sensing and security above 100 GHz. Nat. Commun. 14, 841. https://doi.org/10.1038/s41467-023-36621-x (2023).

Habibpour, O., He, Z. S., Strupinski, W., Rorsman, N. & Zirath, H. Wafer scale millimeter-wave integrated circuits based on epitaxial graphene in high data rate communication. Sci. Rep. 7, 41828. https://doi.org/10.1038/srep41828 (2017).

Doré, J.-B. et al. Technology roadmap for beyond 5G wireless connectivity in D-band. In 2020 2nd 6G Wireless Summit (6G SUMMIT), 1–5 (2020) https://doi.org/10.1109/6GSUMMIT49458.2020.9083890.

Ahmad, W. A. et al. Multimode W-Band and D-Band MIMO Scalable Radar Platform. IEEE Trans. Microw. Theory Tech. 69, 1036–1047. https://doi.org/10.1109/TMTT.2020.3038532 (2021).

Ng, H. J., Kucharski, M., Ahmad, W. & Kissinger, D. Multi-purpose fully differential 61- and 122-GHz radar transceivers for scalable MIMO sensor platforms. IEEE J. Solid State Circ. 52, 2242–2255. https://doi.org/10.1109/JSSC.2017.2704602 (2017).

Schmalz, K. et al. Gas Spectroscopy System for Breath Analysis at mm-wave/THz Using SiGe BiCMOS Circuits. IEEE Trans. Microw. Theory Tech. 65, 1807–1818. https://doi.org/10.1109/TMTT.2017.2650915 (2017).

Tang, X., Nguyen, J., Mangraviti, G., Zong, Z. & Wambacq, P. Design and Analysis of a 140-GHz T/R Front-End Module in 22-nm FD-SOI CMOS. IEEE J. Solid State Circ. 57, 1300–1313. https://doi.org/10.1109/JSSC.2021.3139359 (2022).

N.V., N. S. 5G mmWave. Accessed = 2023-5-15.

Manufacturing, M. Millimeter Wave RF Modules Type 1QT 28GHz RF Antenna Module. Accessed = 2023-5-15.

Manufacturing, M. Pharrowtech Boosts Millimeter-Wave Fixed Wireless Access Coverage (2018). Accessed = 2023-5-15.

Sadhu, B., Gu, X. & Valdes-Garcia, A. The more (Antennas), the merrier: A survey of silicon-based mm-wave phased arrays using multi-IC scaling. IEEE Microw. Mag. 20, 32–50. https://doi.org/10.1109/MMM.2019.2941632 (2019).

Khalaf, K. et al. A 60-GHz 8-way phased-array front-end with T/R switching and calibration-free beamsteering in 28-nm CMOS. IEEE J. Solid State Circ. 53, 2001–2011. https://doi.org/10.1109/JSSC.2018.2822676 (2018).

Optical Receivers, chap. 4, 128–181 (John Wiley & Sons, Ltd, 2011). https://onlinelibrary.wiley.com/doi/pdf/10.1002/9780470918524.ch4.

Abu-Surra, S. et al. End-to-end 140 GHz wireless link demonstration with fully-digital beamformed system. In 2021 IEEE International Conf. on Communications Workshops (ICC Workshops), 1–6, https://doi.org/10.1109/ICCWorkshops50388.2021.9473600 (2021).

Wu, C.-Y. et al. Distributed antenna system using sigma-delta intermediate-frequency-over-fiber for frequency bands above 24 GHz. J. Lightw. Technol. 38, 2765–2773. https://doi.org/10.1109/JLT.2020.2976605 (2020).

Giannoulis, G. et al. Analog radio-over-fiber solutions for 5G communications in the beyond-CPRI era. In 2018 20th International Conf. on Transparent Optical Networks (ICTON), 1–5, https://doi.org/10.1109/ICTON.2018.8473886 (2018).

Singh, N. et al. 60 GHz analog radio-over-fiber single sideband transmitter chipset with 55 nm SiGe BiCMOS driver RFIC and silicon photonics modulator PIC. J. Lightw. Technol. 23, 1–7. https://doi.org/10.1109/JLT.2023.3262124 (2023).

Liu, Y. et al. 93-GHz signal beam steering with true time delayed integrated optical beamforming network. In 2019 Optical Fiber Communications Conference and Exhibition (OFC), 1–3 (2019).

McKenna, T. P., Nanzer, J. A. & Clark, T. R. Photonic beamsteering of a millimeter-wave array with 10-Gb/s data transmission. IEEE Photon. Technol. Lett. 26, 1407–1410 (2014).

Haddad, T. et al. Photonic-assisted 2-D terahertz beam steering enabled by a LWA array monolithically integrated with a BFN. Opt. Express 30, 38596–38612. https://doi.org/10.1364/OE.468200 (2022).

Kim, D., Hirokawa, J., Ando, M., Takeuchi, J. & Hirata, A. 64 × 64-element and 32 × 32-element slot array antennas using double-layer hollow-waveguide corporate-feed in the 120 GHz Band. IEEE Trans. Antennas Propag 62, 1507–1512. https://doi.org/10.1109/TAP.2013.2296318 (2014).

Gomez-Torrent, A. et al. A 38 dB gain, low-loss, flat array antenna for 320–400 GHz enabled by silicon-on-insulator micromachining. IEEE Trans. Antennas Propag. 68, 4450–4458. https://doi.org/10.1109/TAP.2020.2969753 (2020).

Lamminen, A., Säily, J., Ala-Laurinaho, J., de Cos, J. & Ermolov, V. Patch antenna and antenna array on multilayer high-frequency PCB for D-band. IEEE Open J. Antennas Propag. 1, 396–403. https://doi.org/10.1109/OJAP.2020.3004533 (2020).

Gomez-Torrent, A. et al. A low-profile and high-gain frequency beam steering subterahertz antenna enabled by silicon micromachining. IEEE Trans. Antennas Propag. 68, 672–682. https://doi.org/10.1109/TAP.2019.2943328 (2020).

Yao, S. S., Cheng, Y. J., Wu, Y. F. & Yang, H. N. THz 2-D frequency scanning planar integrated array antenna with improved efficiency. IEEE Antennas Wirel. Propag. Lett. 20, 983–987. https://doi.org/10.1109/LAWP.2021.3068773 (2021).

Dong, S. et al. A 140ghz rf beamforming phased-array receiver supporting >20db irr with 8ghz channel bandwidth at low if in 22nm fdsoi cmos. In 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 293–296 (2023) https://doi.org/10.1109/RFIC54547.2023.10186204.

Elkhouly, M. et al. Fully integrated 2d scalable tx/rx chipset for d-band phased-array-on-glass modules. In 2022 IEEE International Solid- State Circuits Conference (ISSCC), vol. 65, 76–78, https://doi.org/10.1109/ISSCC42614.2022.9731626 (2022).

Ahmed, A., Li, L., Jung, M. & Rebeiz, G.M. A 140 ghz scalable on-grid 8 \(\times\) 8-element transmit-receive phased-array with up/down converters and 64qam/24 gbps data rates. In 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 93–96 (2023) https://doi.org/10.1109/RFIC54547.2023.10186155.

Ren, C., Xiao-mo, W., Zheng-hui, X. & Jiang-ling, L. Investigation on grating lobe suppression of uniform antenna array. In 2011 IEEE International Conf. on Microwave Technology & Computational Electromagnetics, 285–288 (2011) https://doi.org/10.1109/ICMTCE.2011.5915513.

Dirani, H. E. et al. Ultralow-loss tightly confining Si3N4 waveguides and high-Q microresonators. Opt. Express 27, 30726–30740. https://doi.org/10.1364/OE.27.030726 (2019).

Sinha, S., Trischler, H., Ocket, I. & Schaffler, E. D -band air-filled substrate integrated waveguide (AFSIW) and broadband stripline to AFSIW launcher embedded in multi-layer PCBs. IEEE Microw. Wirel. Technol. Lett. 12, 1–4. https://doi.org/10.1109/LMWT.2023.3267769 (2023).

Bogaert, L. et al. A 5-bit, 1.6ps resolution true time delay optical beamforming network for 4-element antenna arrays. In 2021 International Topical Meeting on Microwave Photonics (MWP), 1–4 (2021) https://doi.org/10.1109/MWP53341.2021.9639408.

Andrianopoulos, E. et al. Optical generation and transmission of mmWave signals in 5G ERA: Experimental evaluation paradigm. IEEE Photonics Technol. Lett. 34, 1011–1014. https://doi.org/10.1109/LPT.2022.3196632 (2022).

Chao, E. et al. D-band MUTC photodiodes with flat frequency response. IEEE J. Sel. Top. Quantum Electr. 28, 1–8. https://doi.org/10.1109/JSTQE.2021.3115488 (2022).

Petricli, I., Riccardi, D. & Mazzanti, A. D-Band SiGe BiCMOS Power Amplifier with 16.8dBm PdB and 17.1

Wang, X., Li, Y., Yu, W. & Lv, X. A Compact 4-way 4-stage 130-160GHz D-band Power Amplifier in 0.5\(\mu\)m InP DHBT. 2022 IEEE MTT-S International Wireless Symposium, IWS 2022 - Proc.https://doi.org/10.1109/IWS55252.2022.9977535 (2022).

Cahoon, N., Srinivasan, P. & Guarin, F. 6G roadmap for semiconductor technologies: Challenges and advances. In 2022 IEEE International Reliability Physics Symposium (IRPS), 11B.1–1–11B.1–9, https://doi.org/10.1109/IRPS48227.2022.9764582 (2022).

Griffith, Z., Urteaga, M. & Rowell, P. A 140-GHz 0.25-W PA and a 55-135 GHz 115-135 mW PA, high-gain, broadband power amplifier MMICs in 250-nm InP HBT. IEEE MTT-S International Microwave Symposium Digest 2019-June, 1245–1248 (2019) https://doi.org/10.1109/MWSYM.2019.8701019.

Urteaga, M. et al. InP HBT technologies for sub-THz communications. In 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 122–123 (2022) https://doi.org/10.1109/VLSITechnologyandCir46769.2022.9830311.

Schmid, R. L., Coen, C. T., Shankar, S. & Cressler, J. D. Best practices to ensure the stability of sige HBT cascode low noise amplifiers. In 2012 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), 1–4, https://doi.org/10.1109/BCTM.2012.6352657 (2012).

Rao, S. G. & Cressler, J. D. A D-band SiGe power amplifier using a four-way coupled-Line wilkinson combiner. IEEE Microw. Wirel. Compon. Lett. 31, 1239–1242. https://doi.org/10.1109/LMWC.2021.3097017 (2021).

Li, S. & Rebeiz, G. M. High Efficiency D-Band Multiway Power Combined Amplifiers with 17.5-19-dBm Psat and 14.2-12.1

Simic, D. & Reynaert, P. A 14.8 dBm 20.3 dB power amplifier for D-band applications in 40 nm CMOS. In 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 232–235 (2018) https://doi.org/10.1109/RFIC.2018.8428981.

Acknowledgements

This research was funded through a PhD fellowship by the Research Foundation Flanders, the ERC Advanced Grant ATTO Project as well as the Horizon Europe PATTERN project. The authors wish to extend their gratitude toward Luc Pauwels and Nele Van Hoovels for their support on the measurements of the power amplifier IC.

Author information

Authors and Affiliations

Contributions

G.T. and S.L. worked out the system architecture. R.B. designed the PA chip with input from N.S., M.V.O and G.T., prepared the manuscript with input from S.L. and G.T.; J.V.K. helped with the assembly of the PA on the test PCB. R.B. and N.S. performed the measurements. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Broucke, R., Singh, N., Van Osta, M. et al. A compact SiGe D-band power amplifier for scalable photonic-enabled phased antenna arrays. Sci Rep 13, 20560 (2023). https://doi.org/10.1038/s41598-023-47908-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-47908-w

This article is cited by

-

Dual-band dual-polarized sub-6 GHz phased array antenna with suppressed higher order modes

Scientific Reports (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.