Abstract

Amorphous oxide semiconductor (AOS) field-effect transistors (FETs) have been integrated with complementary metal-oxide-semiconductor (CMOS) circuitry in the back end of line (BEOL) CMOS process; they are promising devices creating new and various functionalities. Therefore, it is urgent to understand the physics determining their scalability and establish a physics-based model for a robust device design of AOS BEOL FETs. However, the advantage emphasized to date has been mainly an ultralow leakage current of these devices. A device modeling that comprehensively optimizes the threshold voltage (VT), the short-channel effect (SCE), the subthreshold swing (SS), and the field-effect mobility (µFE) of short-channel AOS FETs has been rarely reported. In this study, the device modeling of two-steps oxygen anneal-based submicron indium-gallium-zinc-oxide (IGZO) BEOL FET enabling short-channel effects suppression is proposed and experimentally demonstrated. Both the process parameters determining the SCE and the device physics related to the SCE are elucidated through our modeling and a technology computer-aided design (TCAD) simulation. In addition, the procedure of extracting the model parameters is concretely supplied. Noticeably, the proposed device model and simulation framework reproduce all of the measured current–voltage (I–V), VT roll-off, and drain-induced barrier lowering (DIBL) characteristics according to the changes in the oxygen (O) partial pressure during the deposition of IGZO film, device structure, and channel length. Moreover, the results of an analysis based on the proposed model and the extracted parameters indicate that the SCE of submicron AOS FETs is effectively suppressed when the locally high oxygen-concentration region is used. Applying the two-step oxygen annealing to the double-gate (DG) FET can form this region, the beneficial effect of which is also proven through experimental results; the immunity to SCE is improved as the O-content controlled according to the partial O pressure during oxygen annealing increases. Furthermore, it is found that the essential factors in the device optimization are the subgap density of states (DOS), the oxygen content-dependent diffusion length of either the oxygen vacancy (VO) or O, and the separation between the top-gate edge and the source-drain contact hole. Our modeling and simulation results make it feasible to comprehensively optimize the device characteristic parameters, such as VT, SCE, SS, and µFE, of the submicron AOS BEOL FETs by independently controlling the lateral profile of the concentrations of VO and O in two-step oxygen anneal process.

Similar content being viewed by others

Introduction

Amorphous oxide semiconductor (AOS) field-effect transistors (FETs) are successfully utilized in the backplane panels of commercial display products, such as organic light-emitting diode displays and liquid–crystal displays1,2. Their advantages include higher mobility than amorphous Si, good large-area uniformity, and a low process temperature. Furthermore, AOS FETs are promising candidates for the back end of line (BEOL) FETs; their advantages include a low-temperature process, ultralow leakage current3, scalability, stability, endurance, low mask count, compatibility with complementary metal-oxide-semiconductor (CMOS) technology4, high thermal tolerance5, and threshold voltage (VT) controllability6.

Various new and promising applications have recently been demonstrated based on AOS BEOL FETs (e.g., 2T1C gain-cell memory4, monolithic three-dimensional (3D) 2T-dynamic random access memory7,8, W doping-based high-performance memory9, high-density and low-power memory using the incorporation into ferroelectric FET structures10, and the low standby power normally-off microcontroller11). In these applications, electrical properties of AOS FETs are mostly controlled via modulating the concentration of carrier donors, i.e., oxygen vacancy (VO) or hydrogen species, which are employed during the deposition of AOS active thin films or by combining the depositions of active film and gate insulator (GI) (especially in the case of the self-aligned top-gate coplanar structure12,13,14,15,16,17,18). However, these methods are not actually suitable for the BEOL process owing to their complexity and high cost. More BEOL-compatible AOS FET technology is required.

On the other hand, in these applications, whether the degree of integration density of AOS FETs is comparable to CMOSFETs determines the performance, power consumption, and cost. In particular, from the viewpoint of power consumption, AOS FET’s advantage of very low leakage current may be diluted unless the integration density is significantly improved. Therefore, an AOS FET technology, which is compatible with the BEOL process and facilitates FET scaling-down, should be developed.

Meanwhile, as the AOS FETs are integrated with the CMOSFETs in the BEOL process and attract more attention as promising devices that create new and various functionalities, the understanding of the effect of process/structure condition on the short-channel effect (SCE) is urgent. Up to now, the device modeling and simulation have rarely demonstrated a comprehensive optimization of VT, SCE, subthreshold swing (SS), and field-effect mobility (µFE) of short-channel AOS FETs, particularly in terms of the effect of process/structure condition on SCE.

This study demonstrates the device modeling of submicron amorphous InGaZnO (a-IGZO) FETs, based on experimentally extracted parameters. Both the subgap density of states (DOS), which is extracted through the photo-response of the current–voltage (I–V) characteristics, and the lateral profile of donor doping concentration are considered in the proposed model. In addition, the model parameters are incorporated into the technology computer-aided design (TCAD) simulation framework. Through the device simulation, the effects of oxygen (O) partial pressure and device structure on the device parameters are quantitatively investigated, and the feasibility of comprehensive optimization of the device performance parameters, such as VT, SCE, SS, and µFE, is proved in the bottom-gate (BG) and double-gate (DG) IGZO FETs fabricated with a two-step O annealing. The range of the channel length (L) of used device is L = 0.245–20.2 µm. In particular, which role the lateral profile of VO and O concentrations can play in suppressing either the L-dependency of VT or the drain-induced barrier lowering (DIBL) is explained and validated based on the proposed model-based simulation.

Experimental results

Two-step oxygen anneal-based fabrication of AOS FETs

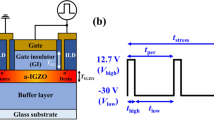

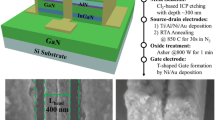

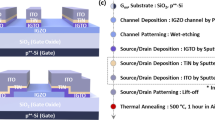

Figure 1a–e show the process of a bottom-gate (BG) IGZO FET fabrication19. First, 5-nm SiCN and 15-nm Al2O3 films are deposited on a p+-Si wafer, serving as back gate dielectrics (for BG). Then, a 12-nm-thick a-IGZO film is deposited by using physical vapor deposition (PVD). After that, a 180-nm SiO2 hard mask is deposited on top of the IGZO layer. Thus, the full stack is formed (Fig. 1a) and then patterned (Fig. 1b). SiO2 is then deposited and planarized (Fig. 1c). Next, the source/drain (S/D) contact trenches are patterned, landing selectively on IGZO (Fig. 1d). Finally, the metallization is implemented by depositing a 6-nm atomic layer deposition (ALD) TiN barrier and ALD/chemical vapor deposition (CVD) W metal contacts followed by a chemical mechanical polishing (CMP). The first oxygen anneal is then performed at 350 °C in an O2 atmosphere for 1 h in order to passivate defects generated during the process fabrication (Fig. 1e). The channel length of BG FET (LBG) is determined by the distance between the source and the drain contact holes. The IGZO active thickness (tact) and the equivalent oxide thickness of BG dielectric (tBGI) are 10 nm and 6.5 nm.

On the other hand, Fig. 1f–m show the process of the DG IGZO FET fabrication20. First, 15-nm Al2O3 film is deposited on a p+-Si wafer, serving as back gate dielectrics (for BG). After a 10-nm-thick a-IGZO film is then PVD deposited, the first oxygen anneal is performed. A top gate dielectric (SiO2, 7 nm) and a TiN gate metal are then deposited (for top-gate (TG)) and followed by the deposition of SiCN/SiO2 hard mask (Fig. 1f). After the active patterning (Fig. 1g), SiO2 gap fill, planarization stopping on TiN, and etch-back are done (Fig. 1h). Then, the rest of the gate stack is deposited (TiN/W/SiCN/SiO2) (Fig. 1i), patterned (Fig. 1j), SiO2 gap fill, and planarized (Fig. 1k). Next, the S/D contact trenches are opened down to the IGZO layer (Fig. 1l). The contact metals are deposited (TiN-contact barrier/W-metal fill) and planarized. The first oxygen anneal is the same as the BG devices (Fig. 1m). Additional interconnections made of vias and metal lines are then implemented to access small devices. The TG channel length (LTG) in the DG structure (unlike the LBG in the BG FET) is determined by the length of the TG electrode.

The scanning electron microscope (SEM) images after active patterning (Fig. 1g) and after planarization (Fig. 1h) of DG FETs are shown in Fig. 1n,o. In addition, the transmission electron microscopy (TEM) images after gate patterning (Fig. 1j) and after metallization (Fig. 1m) of DG FETs are given in Fig. 1p,q. As seen in Figs. S1–S3 (supplementary information), the wafer map for the critical dimension suggests that the entire fabrication process is reproducible, and a high-yield process is used in this work.

To adjust the donor doping concentration of the channel in IGZO (NCH), the second oxygen anneal is performed in both DG and BG FETs (Fig. 1e,m). According to the condition of the second oxygen anneal, two types of samples are prepared; (1) 350 °C in an O2 atmosphere 1 atm for 2 h (called by the standard (STD) sample) and (2) 350 °C in an O2 atmosphere 1 atm for 2 h + 350 °C in an O2 atmosphere 20 atm for 2 h (called by the high pressure (HP) sample).

In the BG structure, the S/D metal acts as a diffusion barrier for oxygen during the oxygen annealing process (Fig. 1e). Meanwhile, in the DG structure, both TG metal and the S/D metal act as oxygen diffusion barriers during the second oxygen annealing (Fig. 1m). Therefore, oxygen infiltrates locally through the separation (ts) between the TG edge and the S/D contact trenches.

As the BG FET goes through the second oxygen annealing process without TG, the IGZO under the S/D metal has a low O concentration (that is, it has a high VO concentration). Owing to this concentration difference, VO diffusion occurs from the IGZO under the S/D metal toward the center of the channel, and the resulting donor doping concentration [n0(x)] has a laterally non-uniform profile (shown as a green line in Fig. 1e). The lateral profile of n0(x) is a crucial factor in determining the electrical characteristics and the SCE of IGZO FETs, which will be modeled in detail later. Compared to BG FET, the O concentration of the channel is relatively low, and the NCH is higher in DG FET (NCH_DG > NCH_BG) because the second oxygen annealing step proceeds in the DG structure while the TG electrode exists. Furthermore, due to O penetrating the ts, a local high-concentration O region (that is, a locally low n0 region) is formed on both edges of the LTG (shown as the green line in Fig. 1m). This region has a vital role in suppressing the SCE of the submicron IGZO BEOL FET, as will be discussed later.

IGZO FET DC characterization

The device sample types are divided into BG and DG according to their structure. They are also divided into STD and HP according to the partial pressure of oxygen during the second O annealing step. The four types of samples are named BG-STD, BG-HP, DG-STD, and DG-HP, respectively. The basic characteristics of the devices were analyzed. Figure 2a,b are the transfer characteristics and device parameters (i.e., VT, SS, and µFE) for the long-channel devices [channel width (W)/channel length (L) = 1/20.2 µm] while Fig. 2c,d show the transfer characteristics and device parameters for the short-channel devices (W/L = 1/0.5 µm). Here µFE_lin means the µFE extracted in the linear region (VGS = 1 V and VDS = 0.05 V). Error bars in Fig. 2b,d were taken from five devices. This supports the reproducibility of device parameters. When measuring the transfer characteristics of the DG FET, the BG voltage (VBG) was swept, and the TG was floated. LTG is 20 µm when L = LBG = 20.2 µm, and is 0.3 µm when L = LBG = 0.5 µm, which is due to ts = 0.1 µm.

The (a) transfer characteristics and (b) device parameters (i.e., VT, SS, and μFE) of long-channel IGZO FETs (L = LBG = 20.2 μm and LTG = 20 μm). The (c) transfer characteristics and (d) device parameters of short-channel IGZO FETs (L = LBG = 0.5 μm and LTG = 0.3 μm). Error bar was taken from five device samples.

As is demonstrated in Fig. 2b,d, the HP sample has a higher VT, a smaller SS, and a lower µFE than the STD sample with the same structure and the same L, regardless of device structure or channel length. For the HP sample, because the amount of O inside the IGZO film is larger than that of the STD sample, the VO concentration (nVo) is lower than the STD sample, and so is the NCH. Since the VO plays the role of electron donor inside the IGZO, the VT of the HP sample is relatively high. In addition, since the electron transport in IGZO follows a percolation transport21, the mobility increases along with electron concentration. The lower µFE in the HP sample is due to the lower electron concentration (relatively lower than in the STD sample). The change in the SS due to the amount of O is related to the trap density at the IGZO/GI interface and in the IGZO thin-film bulk; therefore, it can be explained by analyzing the DOS.

Subgap DOS extraction

The DOS was extracted using the photo-response of the I–V characteristics of the IGZO FET (inset of Fig. 3a). The detailed procedure for the DOS extraction is described in the supplementary information (including Fig. S4 and S5). Figure 3a demonstrates how the DOS of IGZO, extracted from the long-channel BG FET, depends on the amount of O. The bandgap energy (Eg) of IGZO is 3 eV, and the extracted DOS consists of the following terms, in the order of increasing energy level from the valence band (VB) maximum level (EV) to the conduction band (CB) minimum level (EC): gTD (valence band tail states), gVo (neutral VO states), gIn*−M (undercoordinated In states), gVo2+ (ionized VO states), and gTA (conduction band tail states). Additionally, Fig. 3b shows that the extracted DOS fits well with the proposed DOS model. The DOS g(E) model formula is calculated in the following equations, and the extracted DOS model parameters are tabulated in Table S1 in the supplementary information.

When the IGZO DOS change by the O annealing conditions was evaluated, the gVo of the HP sample with high O concentration was confirmed as small compared with the STD sample. The decrease in VO explains this well. In addition, gIn*−M, which indicates the density of the states by the combination of the undercoordinated In and metal cation (In*–M), was also relatively lower in the HP sample case. Consistently with22, this indicates that the In*–M probability of bond formation increases as the carrier concentration increases. In addition, gTA and gVo2+ just below the EC23,24,25 are relatively low in the HP sample case, which is consistent with that the SS of the HP sample is lower than that of the STD sample (Fig. 2b). Noticeably, the O content-dependent DOS in long-channel BG FETs and the device characteristics are well matched; therefore, the extracted DOS is reasonable.

Based on the consistency between DOS and device parameters, it is well understood that under the same O partial pressure condition in a long-channel device, the VT of the BG FET is higher than that of the DG FET, and the SS and the µFE are smaller (Fig. 2a,b). This is because the DG device prevents O from infiltrating (compared with the BG device) into the IGZO during the O annealing process.

On the other hand, the changes by the O content and device structure of VT, SS, and µFE become complicated in a short-channel device (Fig. 2c,d). While the O-dependent change tendencies of VT, SS, and µFE in the same device structure is the same as the long-channel device, the tendency of their changes between the BG-STD and the DG-HP samples is reversed in the short-channel devices (shown as dotted rectangles in Fig. 2b,d). Undoubtedly, this is because the VT of the sample, which experienced the same O annealing condition, varied with L.

The understanding of the L-dependence of VT is eventually central to a robust design of submicron AOS FETs. To understand either the SCE of IGZO FETs or the effect of O content and structure on the SCE, appropriate device modeling and simulation are necessary and should be supported for a robust design of a submicron IGZO FET immune to the SCE.

Modeling and simulation

Device model and parameter extraction

To obtain the robust framework for material-process-device co-design of submicron IGZO FETs, we performed device modeling and incorporated it into a TCAD simulation. First, as is shown in Fig. 4, the BG FET and DG FET device structures were implemented with the TCAD, and the nVo(x) and nOX(x) profiles were generated along with the O annealing process conditions and modeled by the equations in Fig. 4. Here nOX is the concentration of oxygen which is additionally employed during the second oxygen anneal in DG FETs.

In our modeling, the nVo(x) and nOX(x) were assumed to be Gaussian profiles through the previous consideration of the two-step O annealing process and the STD/HP conditions. The LVo and LOX mean characteristic lengths, which are associated with the respective diffusivity of VO and O during the oxygen annealing, describing the nVo(x) and nOX(x). Final donor doping profile [n0(x)] of the BG FET is determined by the combination of the nVo(x) near the S/D extension and the NCH_BG in the center of a channel. In contrast, the final n0(x) of the DG FET is determined as nVo(x)−nOX(x) near the S/D extension and the NCH_DG in the channel part. Then, the NOX was determined as NOX = NCH_BG − NCH_DG because the additional oxygen would compensate the donor concentration.

The detailed procedure for extracting the model parameters is described in Fig. S6 in the supplementary information. The process is outlined as follows. First, after inputting the material parameters and the device structural parameters into the TCAD, we designated the experimentally extracted DOS model into the IGZO active layer. Based on the DOS parameter, the electron effective mass (mn*) and the CB effective DOS (NC) were determined through the formulas below26.

Then, the NCH and the charge density in GI (Qox) were fitted by comparing the simulated VT and flat band voltage (VFB) and the measured ones. After that, the CB mobility (µband) was adjusted by the numerical iteration until the simulated ∂ID/∂VGS and measured ∂ID/∂VGS were in good agreement at various VDS’s. In these fitting processes, the numerical iteration was allowed until the average error between the simulated and measured values fell within a specific error rate (ER). The ER can be selected considering the trade-off between the precision of the model parameter and the computing burden of simulation. An ER = 10% was used in this study.

Next, the parameters that defined the lateral profile of the carrier doping concentration (e.g., NVo, LVo, NOX, and LOX) were decided. These parameters were extracted using the point that they affected the VT roll-off characteristic, i.e., the L-dependency of VT, of the short-channel FET. Since the n0(x) of the BG FET was determined by the nVo(x), we performed the simulation study (Fig. 5) to understand the effect of NVo and LVo changes on the VT roll-off characteristic.

As is shown in Fig. 5, the VT roll-off occurs as L becomes shorter in the BG FET. Here, the channel length at which the VT roll-off begins is defined as L = Lcrit, and the VT at the minimum L (L = 0.245 µm) is defined as VT_min. As demonstrated in Fig. 5a, as the NVo becomes higher, the Lcrit becomes longer, and the VT_min becomes lower simultaneously. It is also shown in Fig. 5b that as the LVo becomes longer, the Lcrit becomes more extended, but VT_min is independent of the LVo. Therefore, in the BG FET, the NVo can be extracted through a fitting with the measured VT_min under a fixed NCH_BG condition, and then the LVo can be extracted through the second fitting with the measured Lcrit at a fixed NVo.

In the DG FET, the changes either in NVo and LVo or in NOX and LOX affect the VT roll-off characteristic since the n0(x) is determined by the combination of the nVo(x) and the nOX(x). Therefore, in the DG FET, a more complex L-dependency of the VT appears compared with the BG FET as seen in Fig. 6. More interestingly, the reverse SCE appears in the medium L range where the VT increases as the L decreases. Here, when the maximum value of the L-dependent VT is defined by VT_max, Lcrit can be re-defined particularly in DG FET as the L where the L-dependency of VT interchanges between the increase and decrease in VT(L). Then, as the NVo increases, VT_min decreases, Lcrit increases, and VT_max decreases (Fig. 6a). In addition, as LOX becomes longer, both Lcrit and VT_max increase, but the VT_min is independent of the LOX (Fig. 6b). Moreover, as LVo lengthens, both Lcrit and VT_max decrease, but the VT_min is immune to the variation of LVo (Fig. 6c).

Therefore, in the DG FET, the parameters, such as NVo, LVo, NOX, LOX, and NCH_DG, can be extracted through the relationship of NOX = NCH_BG − NCH_DG and a fitting between the measured VT_min, Lcrit, and VT_max, and simulated values under the given NCH_BG condition.

The extracted model parameters are summarized in Table S1 (supplementary information).

TCAD simulation

The TCAD framework was setup for each process condition (HP/STD) and structure (BG/DG) by using the parameter set summarized in Table S1. The simulated and measured I–V characteristics are compared with each other (Fig. 7a,b). In the four types of samples (BG-STD, BG-HP, DG-STD, and DG-HP), all the TCAD simulation results reproduce well the measured I–V curves and parameters, i.e., VT, SS, and µFE, for both the long-channel (Fig. 7a) and short-channel FETs (Fig. 7b).

Considering the discrepancies between the measured and simulated results, the ER range is 1.16–13.1%. The main cause of this difference is expected to be due to the bias-dependent mobility of the AOS FETs, suggesting that further studies are needed. In Fig. 7a (L = 20.2 μm), the ER for BG-HP, BG-STD, DG-HP, and DG-STD is 7.35, 5.57, 13.1, and 3.82%, respectively. Meanwhile, in Fig. 7b (L = 0.5 μm), each ER for BG-HP, BG-STD, DG-HP, and DG-STD is 1.16, 3.67, 8.65, and 9.48%.

These values are consistent with the critical ER (< 10%) used in extracting model parameters. Therefore, the proposed model and model parameter extraction are reasonable and accurate enough to expect the electrical characteristics of AOS FETs.

Noticeably, using the L vs. VT relationship in Figs. 5 and 6, we can extract the Gaussian doping parameters for each structure and process condition (Fig. 4) as a unique set. This means that the O and VO diffusion effects are reflected well along with every L, process condition, and structure (including the minimum L of 245 nm). As seen in Table S1, in the long L, the NCH was higher in the order of DG-STD, DG-HP, BG-STD, and BG-HP. In the second O annealing step of the BG structure, since there is no O diffusion barrier, NCH_DG is higher than NCH_BG. In the same structure, the NCH of the STD device is higher than that of the HP device.

Discussion

Short-channel effects

Understanding why the L-dependency of VT in the BG FET changes along the variations of LVo and NVo (Fig. 5) is central to the design of the doping profile of the submicron AOS FET. Similarly, understanding why the L-dependency of VT of the DG FET changes along with the variations of LVo, NVo, and LOX (Fig. 6) is central to the design of the immunity to SCE in the submicron AOS FET.

First, for the BG FET, the n0(x) is composed of NVo (S/D region), \(n_{{V_{O} }} (x) = N_{{V_{O} }} \times e^{{ - \left( {\frac{x}{{L{\kern 1pt}_{Vo} }}} \right)^{2} }}\) (S/D extension area), and NCH_BG (the center of the channel), as illustrated in Fig. 4a. At this time, the NVo is determined by the amount of the VO employed in the IGZO film, which is controlled by the amount of the O inflow and the temperature during the IGZO deposition. The diffusion length of VOs (LVo) is also determined by either the lateral diffusivity of VO or the thermal budget during the process. In the same process conditions, when the L becomes shorter and comparable to the scale of the LVo, then the nVo(x) profiles of both the source and drain merge in the center of the channel to effectively increase the NCH; therefore, the VT starts to decrease. That is, when the L = Lcrit, the NCH_BG increases compared with the long-length device, and the VT roll-off phenomenon begins to occur. Accordingly, as the LVo lengthens and the NVo becomes higher, the longer Lcrit becomes (the SCE becomes severe) because the nVo(x) starts to intersect at the channel center at the longer L (Fig. 5a). At the minimum L (L = 0.245 µm), the channel length is too short, and the donor doping concentration in the center of the channel approaches NVo, i.e., the peak value of the Gaussian donor doping nVo(x), independently of the LVo. Therefore, the VT_min is only affected by NVo (Fig. 5b).

On the other hand, in the DG FET (Fig. 6), if the locally high O concentration area (formed during the second O annealing step) is described as the Gaussian acceptor profile \(n_{OX} (x) = N_{OX} \times e^{{ - \left( {\frac{x}{{L_{{{\kern 1pt} OX}} }}} \right)^{2} }}\), then the n0(x) consists of the NVo in the S/D area, the nVo(x) − nOX(x) in the S/D extension area, and the NCH_DG in the center of the channel. At this time, the O diffusion length LOX is determined by either the lateral diffusivity of O or the thermal budget during the process. Since the nOX(x) region is relatively closer to the channel center than the nVo(x) region, when L is shortened, the locally higher nOX(x) [locally lower n0(x)] regions are merged first, and then VT increases. That is, as shown in Fig. 6, a VT roll-up (the reverse SCE) is observed (VT_max is observed).

Furthermore, as L becomes further shorter, the merge in the nVo(x) section is overlapped. Then, a VT roll-off section, where VT decreases again, is observed. Meanwhile, as LVo increases, the NCH_DG also increases and VT_max decreases. In this case, as LVo increases, Lcrit shortens since the influence of the nOX(x) also decreases (Fig. 6a). In addition, as LOX lengthens, VT_max increases because the NCH_DG decreases. However, Lcrit lengthens because the NCH_DG, which has already been lowered, makes the nVo(x) overlap followed by the decrease in VT occur at a longer L (Fig. 6b). Finally, at the minimum L (L = 0.245 µm), the NCH_DG (also VT_min) is determined by the combination of the NVo and NOX regardless of the LOX and LVo because the channel length is too short (Fig. 6b,c). Thus, when the NOX is fixed, Lcrit shortens and VT_max decreases as the LVo lengthens (Fig. 6c).

Hence it needs to be explained why, in a short-channel case, the VT of the DG FET increases overall and the µFE decreases overall compared with the BG FET (the dotted boxes in Fig. 2b,d). As explained above, the NCH_DG is higher than NCH_BG in the long L. Therefore, the DG device has a lower VT and a higher µFE when compared with the BG device. However, in a short-channel case, the NCH_DG is lower than that of the NCH_BG due to the merging phenomenon of the nOX(x), so that the DG device has a higher VT and a lower µFE than the BG device (Fig. 8a–c). Furthermore, at the same process condition, the SS of the DG device is higher in the short channel (L = 0.5 µm) than that of the BG device, whereas the SS in the long channel is immune to the device structure and process. This is because in the DG device with a short L, there is a big difference between the resistance of the channel and that of the S/D extension (Fig. 8a–c), so the lateral electric field by the drain voltage becomes more focused on the channel center, and the vertical electric field by the gate voltage acts relatively weakly; therefore, this weakens the gate controllability.

The TCAD-simulated n0(x) profiles in the four types of samples along the structures and processes with varying channel length. (a) L = 20.2 μm, (b) L = 2.2 μm, and (c) L = 0.5 μm. The TCAD simulated (line) vs. the measured (symbol) L-dependent (d) VT and (e) DIBL. Error bar was taken from six device samples. (f) The energy band obtained through the TCAD simulation for the BG-HP, BG-STD, DG-HP, and DG-STD devices at W/L = 0.5/1 µm.

The symbols in Fig. 8d,e show the L-dependent VT and DIBL characteristics measured in the IGZO FET. Error bars were taken from six devices. These two characteristics are the performance index representing the SCE. In addition, the lines in Fig. 8d,e show the TCAD simulation results (using the model parameters in Table S1) reproduce well the L-dependent VT and DIBL characteristics over a wide range of the L. Based on these results, the model parameter extraction process and the parameter values confirm that the O and VO diffusion effects are reflected well over a wide range of the L. This is also reasonable for the variations of process condition and device structure, both qualitatively and quantitatively.

In Fig. 8d, when the VT roll-off occurs in the BG FET, the HP device is more immune to the SCE than in the STD device (that is, the Lcrit is longer). This is because the HP device has a relatively lower NCH and NVo than the STD device. Here, it is worthwhile to note that the LVo of HP device is × 1/5 to × 1/3 shorter than that of STD device (Table S1). It indicates that the more O-poor the IGZO active layer is, the more active the lateral diffusion of the VO and the longer the diffusion length of the VO will be. Our finding is consistent with the results of studies that indicate that the diffusion length of the VO increases when the NVo is high27.

Meanwhile, in the DG FET (as was already shown in Fig. 6), the VT roll-up (the reverse SCE) is observed along with a decreasing L, and the DG-HP device suppresses the SCE more effectively than the DG-STD device. As shown in NOX and LOX in Table S1, the nOX(x) spreads more broadly in the DG-HP device, which lowers NOX and lengthens LOX, when compared with the DG-STD device. This broadening further reduces the NCH_DG (Fig. 8c), and both the VT roll-off and roll-up are consequently suppressed by weakening the lateral-merge effect of the nVo and the nOX. Therefore, if the DG-HP device is optimized further, it is expected to effectively suppress the SCE while satisfying a positive VT, which is an essential requirement from the circuit aspect.

Device design perspective

The following points should be noted: the spread of the nVo in the first O annealing step increases as it becomes more O-poor (the nVo spread in the STD device is larger than that in the HP device), and the spread of the nOX in the second O annealing step increases as it becomes more O-rich (broader nOX in the DG-HP device rather than in the DG-STD device). Therefore, if the O pressure during the second annealing step and the ts are further optimized in the two-step O annealing process, we can expect that the VT will become more immune to the scale-down of L.

The TCAD-simulated energy band is shown in Fig. 8f. The DIBL is small in the following device order: DG-HP, BG-HP, DG-STD, and BG-STD, which is consistent with Fig. 8e. The overall tendency shows that the HP device has a smaller DIBL than the STD device, and the DG structure has a smaller DIBL than the BG structure. The HP structure is more robust to DIBL than the STD structure for the following two reasons; first, since the HP structure has a low NCH and the Fermi energy level (EF) is lower than that of the STD structure, a high energy barrier is formed between the S/D and the channel. Second, the LVo of the HP device is shorter than that of the STD device. If the LVo is long, the channel area where the EF rises gets longer, and the potential barrier lowers between the source and the channel, which makes it more vulnerable to the DIBL.

In the DG devices, the voltage drop by the VDS is large because of the existence of a nOX region with large resistance. Thus, the DIBL is suppressed in DG FET. This effect is further enhanced in the HP process (the resistance of the nOX region becomes larger). The role of this nOX region is very reminiscent of the role of halo (or pocket) implantation to block SCE in submicron CMOSFETs. The DG-HP device is the most advantageous from the DIBL point of view (similar to the VT roll-off), and the DIBL is expected to be suppressed more effectively through further optimization.

To compare the performance of devices utilized in this study with previous studies, we compared the main device parameters with those of references, as summarized in Table 1. It should be noted that, since the operating voltage, device structure, and size are different for each device, it is necessary to define another new index for a fair comparison. In the case of mobility, for example, since either the voltage condition from which the mobility is extracted or the channel length is different, it is difficult to evaluate as the performance indicator of AOS. Therefore, we defined α and β as new indices. α is defined by \(\alpha = \frac{{I_{D} \times L_{\min } }}{{W \times (V_{GS} - V_{T} ) \times V_{DS} }}\) and means the operating current normalized by the device size, gate overdrive voltage, and drain voltage. β is also defined by \(\beta = \frac{\alpha }{{C_{ox} }}\), means the current further normalized by Cox, and has the same unit as the mobility. That is, if β is used, fair comparison is possible even if the operating voltage, gate capacitive coupling, and device size are different. In the case of our device, assessed by β, it is confirmed that the performance is excellent compared to the devices of the previous studies. Furthermore, in the viewpoint of Lmin, it is found that our device shows good scalability except for the 3D device structure such as FinFET. From the SCE point of view, it can be seen that the previous studies rarely reported on VT roll-off or DIBL. Noticeably, our study is a rare case that reports both DIBL and VT roll-off, and it is confirmed that our device shows very good SCE properties despite not having a 3D structure.

A method that can optimize VT, SS, μFE and SCE in of the submicron AOS FET is vital, and the key is to control the n0(x) with a combination of VO and O. Figure 9 illustrates the change of n0(x) by the variations of LVo, NVo, NCH_BG, and L. If we perform the co-optimization of ts, NVo, LVo, NOX, and LOX by using both a two-step O annealing and DG structure after we make the IGZO active film sufficiently O-poor and fully raise the CB mobility at the beginning of the process, we will be able to implement AOS BEOL FETs that comprehensively satisfy the VT, SS, μFE, and SCE parameters that match the performance and specification of the application-dependent circuits.

Conclusion

The DOS-based device model and TCAD simulation framework were proposed with emphasis on the control of n0(x), and were demonstrated in the BG/DG IGZO FETs with L = 0.245–20.2 µm. The validity of the device model and its parameters were proved through a TCAD simulation reflecting the extracted model parameters and the IGZO DOS. Based on a two-step O annealing, the effect of O partial pressure on not only the device performance parameters, such as VT, SCE, SS, and µFE, but also DOS was elucidated. The simulation results explained successfully the measured VT roll-off and DIBL characteristics. The results of an analysis based on the proposed model and the extracted parameters indicate that the SCE of submicron AOS FETs is effectively suppressed when the local high O-concentration region (formed by applying the two-step O annealing to the DG FET) is used. We also found that LVo becomes longer as the device becomes O-poor, and LOX becomes longer as the device becomes O-rich.

Our results show that the co-optimization of ts, NVo, LVo, NOX, and LOX is vital to the immunity to SCE in AOS FETs. Proposed model and simulation framework are potentially useful to a comprehensive optimization of the device performance parameters, i.e., VT, SCE, SS, and µFE, for the submicron AOS BEOL FET technology.

Methods

IGZO FET characterization

In this study, to analyze the ID−VGS characteristics of the IGZO FET, HP4156C (Keithley, Santa Rosa, CA, USA) was used, and the measurements were taken in a dark state at room temperature. The measurement conditions were as follows; the gate-to-source voltage (VGS) was swept from 4 to − 6 V in − 0.05 V steps, and the drain-to-source voltage (VDS) was fixed at 0.05 V. The VT was extracted by the VGS at ID/(W/L) = 10−8 A, and the SS was extracted by ID/(W/L) = 10−10–10−9 A. In addition, the µFE_lin was calculated at VGS−VT = 3 V by using the following equation.

The DIBL was calculated from the difference between the VT at VDS = 0.05 V and the VT at VDS = 1.05 V.

Error evaluation

In the case of measured data, the mean value and error bar were calculated by using the root mean square (RMS) value as follows (x = measurement value, m = mean, n = number of data):

These mean and error bar were used in Fig. 2b,d, and in Fig. 8d,e.

In addition, for comparing the measured and simulated data, the error rate (ER) was calculated as follows (y = simulation data, mabs = average of absolute values of measured data).

This ER was used in Fig. 7.

Data availability

The datasets used or analyzed during the current study are available from the corresponding author on reasonable request.

References

Ha, C. et al. Self-aligned coplanar structure for large-sized ultrahigh-definition OLED TV. SID Int. Symp. Dig. Tech. Paper 46, 1020–1022 (2015).

Yeh, B. & Lin, C. High-performance 4K × 2K 65-in. TV with BCE-type oxide TFTs. SID Int. Symp. Dig. Tech. Paper 46, 943–945 (2015).

Oota, M. et al. 3D-Stacked CAAC-In-Ga-Zn oxide FETs with gate length of 72 nm. IEEE International Electron Devices Meeting (IEDM), 3.2.1–3.2.4 (2019).

Ishizu, T. et al. A 140 MHz 1 Mbit 2T1C gain-cell memory with 60-nm indium-gallium-zinc oxide transistor embedded into 65-nm CMOS logic process technology. Symposium on VLSI Circuits, C162–C163 (2017).

Kunitake, H. et al. High thermal tolerance of 25-nm c-axis aligned crystalline In-Ga-Zn oxide FET. IEEE International Electron Devices Meeting (IEDM), 3.6.1–13.6.4 (2018).

Kunitake, H. et al. A c-axis-aligned crystalline In-Ga-Zn oxide FET with a gate length of 21 nm suitable for memory applications. IEEE J. Electron Devices Soc. 7, 495–502 (2019).

Belmonte, A. et al. Capacitor-less, long-retention (>400s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. 2020 IEEE International Electron Devices Meeting (IEDM), 28.2.1–28.2.4 (2020).

Ye, H. et al. Double-gate W-doped amorphous indium oxide transistors for monolithic 3D capacitorless gain cell Edram. IEEE International Electron Devices Meeting (IEDM), 28.3.1–28.3.4 (2020).

Chakraborty, W. et al. BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with Ion = 370 μA/μm, SS = 73 mV/dec and Ion/Ioff ratio > 4 × 109. Symp. VLSI Technol. 6, 10–11 (2020).

Mo, F. et al. Experimental demonstration of ferroelectric HfO2 FET with ultrathin-body IGZO for high-density and low-power memory application. 2019 Symposium on VLSI Technology, T42–T43 (2019).

Ishizu, T. et al. A 48 MHz 880-nW standby power normally-off MCU with 1 clock full backup and 4.69-μs wakeup featuring 60-nm crystalline In–Ga–Zn oxide BEOL-FETs. Symposium on VLSI Circuits, C48 (2019).

Oh, S. et al. Comparison of top-gate and bottom-gate amorphous InGaZnO thin-film transistors with the same SiO2/a-InGaZnO/SiO2 stack. IEEE Electron Device Lett. 35, 1037–1039 (2014).

Oh, S., Baeck, J. H. & Bae, J. U. Effect of interfacial excess oxygen on positive-bias temperature stress instability of self-aligned coplanar InGaZnO thin-film transistors. Appl. Phys. Lett. 108, 41604 (2016).

Choi, S. et al. Systematic decomposition of the positive bias stress instability in self-aligned coplanar InGaZnO thin-film transistors. IEEE Electron Device Lett. 38, 580–583 (2017).

Kim, D. H. et al. Experimental decomposition of the positive bias temperature stress-induced instability in self-aligned coplanar InGaZnO thin-film transistors and its modeling based on the multiple stretched-exponential functions. J. Soc. Inf. Disp. 48, 298–301 (2017).

Hong, S.-Y. et al. Study on the lateral carrier diffusion and source-drain series resistance in self-aligned top-gate coplanar InGaZnO thin-film transistors. Sci. Rep. 9, 6588 (2019).

Jang, J. T. et al. Cation composition-dependent device performance and positive bias instability of self-aligned oxide semiconductor thin-film transistors: Including oxygen and hydrogen effect. ACS Appl. Mater. Interfaces 14, 1389–1396 (2022).

Choi, S. et al. Excessive oxygen peroxide model-based analysis of positive-bias-stress and negative-bias-illumination-stress instabilities in self-aligned top-gate coplanar In–Ga–Zn–O thin-film transistors. Adv. Electron. Mater. 8, 2101062 (2022).

Kljucar, L. et al. 300 mm IGZO nFETs with low-T Ru contacts for localized doping and increased BEOL compatibility. Solid State Devices and Materials (SSDM), J-6-03 (2020).

Rassoul, N. et al. IGZO front-gated TFTs for 3D DRAMs: Process and device advancement. Solid State Devices and Materials (SSDM), J-6-03 (2021).

Lee, D. H., Nomura, K., Kamiya, T. & Hosono, H. Diffusion-limited a-IGZO/Pt Schottky junction fabricated at 200 °C on a flexible substrate. IEEE Electron Device Lett. 32, 1695–1697 (2011).

Nahm, H. & Kim, Y. Undercoordinated indium as an intrinsic electron-trap center in amorphous InGaZnO4. NPG Asia Mater. 6, e143 (2014).

Yang, G. W. et al. Total subgap range density of states-based analysis of the effect of oxygen flow rate on the bias stress instabilities in a-IGZO TFTs. IEEE Trans. Electron Devices 69, 166–173 (2022).

Yen, C. et al. Oxygen-related reliability of amorphous InGaZnO thin film transistors. IEEE J. Electron Devices Soc. 8, 540–544 (2020).

Kamiya, T., Nomura, K., Hirano, M. & Hosono, H. Electronic structure of oxygen deficient amorphous oxide semiconductor a-InGaZnO4-x: Optical analysis and first-principle calculations. Phys. Stat. Solidi (c) 5, 3098–3100 (2008).

Wager, J. F. Real- and reciprocal-space attributes of band tail states. AIP Adv. 7, 125321 (2017).

Liu, L. et al. Oxygen vacancies: The origin of n-type conductivity in ZnO. Phys. Rev. B Condens. Matter 93, 235305 (2016).

Acknowledgements

This work was supported in part by Samsung Electronics Co., Ltd under Grant IO200424-07306-01, in part by the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (MSIT) of Korea Government under Grant 2016R1A5A1012966 and 2020R1A2B5B01001979, and in part by the Institute of Information and Communications Technology Planning and Evaluation (IITP) funded by the Korea government (MSIT) under grant 2021-0-01764. Submicron IGZO FET samples was fabricated by imec. TCAD simulation was supported by SILVACO. The EDA tool was supported by the IC Design Education Center (IDEC), south Korea.

Author information

Authors and Affiliations

Contributions

D.K. and D.H.K. designed this work and wrote the main part of manuscript. D.K., J.-H.K., W.S.C., T.J.Y., and J.T.J. performed the device characterization, modeling and TCAD simulation. A.B., N.R., S.S., R.D., and G.S.K. contributed to the design and fabrication of the submicron IGZO FETs. D.K., A.B., S.S., R.D., W.L., M.H.C., D.H., and D.H.K. discussed the results. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kim, D., Kim, JH., Choi, W.S. et al. Device modeling of two-steps oxygen anneal-based submicron InGaZnO back-end-of-line field-effect transistor enabling short-channel effects suppression. Sci Rep 12, 19380 (2022). https://doi.org/10.1038/s41598-022-23951-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-23951-x

This article is cited by

-

Toward monolithic growth integration of nanowire electronics in 3D architecture: a review

Science China Information Sciences (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.