Abstract

The processing of large amounts of data requires a high energy efficiency and fast processing time for high-performance computing systems. However, conventional von Neumann computing systems have performance limitations because of bottlenecks in data movement between separated processing and memory hierarchy, which causes latency and high power consumption. To overcome this hindrance, logic-in-memory (LIM) has been proposed that performs both data processing and memory operations. Here, we present a NAND and NOR LIM composed of silicon nanowire feedback field-effect transistors, whose configuration resembles that of CMOS logic gate circuits. The LIM can perform memory operations to retain its output logic under zero-bias conditions as well as logic operations with a high processing speed of nanoseconds. The newly proposed dynamic voltage-transfer characteristics verify the operating principle of the LIM. This study demonstrates that the NAND and NOR LIM has promising potential to resolve power and processing speed issues.

Similar content being viewed by others

Introduction

As we have entered the era of the Internet of Things, Big Data, and artificial intelligence, the global need for data processing has exponentially increased in various fields such as medical services, industrial production, and social media1,2,3,4,5. Processing large amounts of data requires high-performance and energy-efficient computation, which is a critical factor for a wide range of data-intensive applications. However, current computer systems based on the von Neumann architecture incur significant power consumption and latency because of the speed gap when accessing data between the separated central processing and memory units6,7,8,9. Recently, logic-in-memory (LIM) has been investigated to overcome the architectural limitations of data movement. LIM performs logical operations in a memory unit to eliminate data movement between the logical and memory tasks. Therefore, LIM architecture has the advantages of not only high bandwidth memory, but also highly energy-efficient computing and processing time.

Various LIM devices can be implemented using either charge-based or resistance-based memory. Charge-based memory mainly refers to static random-access memory (SRAM), dynamic RAM (DRAM), and flash memory. Resistance-based memory includes resistive RAM (RRAM), spin-transfer torque magnetoresistive RAM (STT-MRAM), and phase-change memory (PCM). The read/write time, voltage, LIM computation energy/latency, leakage power, and retention for existing charge-or resistance-based memory, as reported in other studies, are listed in Table 110,11,12,13,14. In charge-based memory, although SRAM is very fast (~ 1 ns) and DRAM has high density, they contain volatile memory devices, and hence have high energy needs. Moreover, SRAM-based LIM suffers from chip area overhead because more transistors than in the conventional 6 T SRAM cells are required for computing operations15,16. Likewise, DRAM-based LIM has the challenges of area and yield due to the limitation of the cell structure16,17,18. NAND/ NOR flash memory with a charge-trapping layer can store data long-term. Nevertheless, for LIM operation, it not only has a low read/write time (< 103/ < 106 ns) and a high operating voltage (< 10 V), but also a relatively high computation energy (41.62/ 0.2 nJ) and latency (8421/ ~ 500 ns).

New emerging resistance-based memory (RRAM, PCM, and STT-MRAM) has a non-volatile memory (NVM) capability, and LIM based on resistance-based memory has been presented19,20,21,22,23,24. However, resistance-based memory has several drawbacks, such as low processing speed, high operating voltage, and fabrication process. Specifically, RRAM-based LIM has inconsistent switching characteristics due to variations in the fabrication process and requires a relatively high voltage (< 3 V) to generate a high current compared to conventional volatile memories24,25. The PCM-based LIM has a low write speed (~ 50 ns) compared to other memory devices due to the switching between crystalline and amorphous phases, and a comparatively high operating voltage (< 3 V)26. The STT-MRAM-based LIM has a low chip yield for mass production, low reliability because of stochastic switching, and read disturbances27. Moreover, resistance-based memory requires new fabrication processes and new materials (not based on CMOS fabrication technology), and it is not yet mature enough to be available for commercial technology/products18,28.

In this study, we propose a NAND and NOR LIM composed of silicon nanowire (SiNW) feedback field-effect transistors (FBFETs) to verify universal gate functions, where the configuration of the SiNW FBFETs maintains conventional CMOS logic gates. The SiNW FBFETs utilized in the LIM have demonstrated near-zero subthreshold swings (SS), high speed, low operating voltage, and quasi-nonvolatile memory characteristics based on the positive feedback loop mechanism29,30,31. The LIM exhibits a high processing speed close to that of SRAM and DRAM (< 5 ns), ultra-low standby power while storing the data, retention characteristics that will retain certain computational logic states without power supply, and relatively low operating voltage (≤ 2.5 V) compared to flash memory. Furthermore, the LIM exhibits a relatively high density compared with charge-based memory because it implements LIM operation on only four FBFETs without separate storage devices. The proposed LIM has excellent gate controllability of charge carriers in the silicon channel and has a simple fabrication process by CMOS-compatible top-down technology32,33. The FBFETs could be produced using commercially available fabrication processes of conventional GAA SiNWs, and our LIM could be implemented by arranging the FBFETs as CMOS logic circuit31. Thus, it is feasible that our LIM is made in commercially available fabrication processes34. Therefore, the presented LIM can not only reduce fabrication costs but also enable rapid commercialization in the LIM market. Moreover, the presented LIM has comparatively low LIM computation energy (~ 0.5/ ~ 0.2 pJ) and latency (~ 1 ns) compared with the figures-of-merit of LIM using other memory devices. Furthermore, we specifically examined the operations of the NAND and NOR LIM using the newly proposed dynamic voltage-transfer characteristics (VTC). We investigated the feasibility of the NAND and NOR LIM through mixed-mode technology computer-aided design (TCAD) simulations35.

Schematic of the FBFETs and circuit diagrams of the LIM

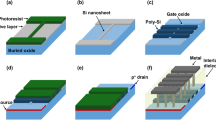

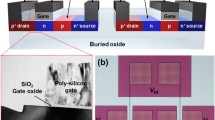

Figure 1 shows a schematic view of a single-gated SiNW p-channel FBFET (p-FBFET) and a single-gated SiNW n-channel FBFET (n-FBFET) utilized in the NAND and NOR LIM. The dimensional parameters of the p-FBFET, as shown in Fig. 1a, are a channel length (LCH) of 150 nm, p+ drain and n+ source region lengths of 50 nm, and a silicon channel diameter of 25 nm. The dimensional parameters of the n-FBFET, as shown in Fig. 1b, are an LCH of 200 nm, p+ drain, and n+ source region lengths of 50 nm, and a silicon channel diameter of 15 nm. The non-gated and gated channel lengths are 1/2LCH for both FBFETs. Supplementary Section 1 provides more details on the device dimensional parameters. Figure 1c,d show the diagrams and truth tables of the NAND and NOR LIM, respectively, consisting of two n-FBFETs, two p-FBFETs, and a parasitic load capacitor connected to the output node with a capacitance of 10 fF36,37. The parasitic load capacitance represents the capacitance of the wire or interconnect between the output of the logic gate and the input of another logic gate. These LIM operations are conducted by applying voltage pulses of supply voltages VDD and VSS (defined as the drain voltage of the p-FBFET and the source voltage of the n-FBFET, respectively), gate input voltage 1 (VIN1), and gate input voltage 2 (VIN2) under dynamic conditions.

Results and discussion

Operating principle of the FBFETs constituting the LIMs

The operation principle of the p- and n-FBFETs is based on a positive feedback loop mechanism in the channel regions29,30,31. The FBFETs consisting of p+–n+–p+–n+ regions have two potential barriers in the channel regions, and the potential barrier heights are controlled by the presence or absence of charge carriers in the potential well. For the off-state under a gate voltage (VGS) of 1 V (or − 1 V) and positive drain voltage (VDS) in the p-FBFET (or n-FBFET), the potential barrier near the drain side of the channel region blocks the injection of holes from the drain into the channel region. Likewise, the potential barrier near the source side blocks the injection of electrons from the source. During the VGS negative (or positive) sweep, the charge carriers are injected into the channel regions and accumulate in the potential wells; the accumulated charge carriers lower the potential barrier height in the channel regions. When the repetition of injection and accumulation of charge carriers generates a positive feedback loop, the two potential barriers collapse abruptly, and the drain current (IDS) rapidly increases. Thus, the p-FBFET (or n-FBFET) changes to an on-state under a VGS of − 1 V (or 1 V). During hold operation under no-bias conditions, the accumulated charge carriers in the potential wells are maintained until the potential barriers in the channels are well-defined, and the FBFETs have quasi-nonvolatile memory characteristics38,39. In the VGS positive (or negative) sweep for the p-FBFET (or n-FBFET), the charge carriers accumulated in the channel regions are reduced, and the two potential barriers are regenerated. Consequently, the positive feedback loop is eliminated, and the IDS rapidly decreases; thus, the p-FBFET (or n-FBFET) changes to an off-state.

NAND and NOR LIM operation under dynamic conditions

Figure 2a shows both the logic operation of the NAND LIM and the memory operation to hold its output logic states (for more details of the logic operation, see Supplementary Section 2). The time width of the input logic pulse is 5 ns, corresponding to a frequency of 0.2 GHz, and the hold time width is 1 ms, corresponding to a frequency of 1 kHz. In the timing diagram in this figure, the LIM operations are performed in a input logic gate combination sequence of ‘00’, ‘01’, ‘10’, and ‘11’, and after each logic operation, the memory operation to hold the output logic states is performed without any external bias (VDD = VSS = VIN1 = VIN2 = 0.0 V). First, the input logic ‘00’ of the NAND LIM operates with VDD = 1.6 V, VSS = − 2.5 V, VIN1 = − 1.0 V, and VIN2 = − 1.0 V, providing the output logic ‘1’ (VOUT = 1.0 V). The output logic ‘1’ is stored for 1 ms in the channel region of the FBFETs without any external bias supplies, and the operation is referred to as the hold ‘1’ operation. When the input logic ‘00’ with VIN1 = VIN2 = − 1.0 V is applied, the two p-FBFETs are turned on, and the two n-FBFETs are simultaneously turned off. Thereafter, during the hold ‘1’ operation under zero-bias conditions, the output logic value is stored by the quasi-nonvolatile memory characteristics of the FBFETs30,38,39. The input logic ‘01’ operates with VIN1 = − 1.0 V and VIN2 = 1.0 V, and the output logic ‘1’ is provided. The state in which the output logic ‘1’ is stored under zero-bias conditions is referred to as the hold ‘1’ operation. The input logic gate ‘10’ operates with VIN1 = 1.0 V and VIN2 = − 1.0 V, and the output logic ‘1’ is provided, and thereby the output logic is stored without any voltages applied. The input logic gate ‘11’ operates with VIN1 = 1.0 V and VIN2 = 1.0 V, and the output logic transits from ‘1’ to ‘0’, which indicates VOUT = − 1.0 V because a current path is created between VOUT and VSS. The output logic ‘0’ is also stored and maintained under zero-bias conditions corresponding to the hold ‘0’ operation. For the write operations, the calculated average write energy is approximately 0.5 pJ/bit. In addition, for the read operations, no sensing voltage is required to read the VOUT because the logic states of the NAND LIM are stored as VOUT. The NAND and NOR LIMs are compared in Table 1 with existing charge- or resistance-based memory technologies reported by other research groups in terms of the read/write time, voltage, LIM computation energy/latency, leakage power, and retention10,11,12,13,14.

Figure 2b shows both the logic operation of the NOR LIM and the memory operation to hold its output logic states (for more details of the logic operation, see Supplementary Section 2). In the timing diagram, the LIM operations are carried out in an input logic gate combination sequence of ‘00’, ‘01’, ‘10’, and ‘11’, and after each logic operation, the memory operation to hold the output logic states is performed without any external bias. First, the input logic gate ‘00’ of the NOR LIM operates with VDD = 2.5 V, VSS = − 1.6 V, VIN1 = − 1.0 V, and VIN2 = − 1.0 V, and the output logic ‘1’ is carried out. Thereafter, the output state is stored under zero-bias conditions, which is referred to as the hold ‘1’ operation. The input logic gate ‘01’ operates with VIN1 = − 1.0 V and VIN2 = 1.0 V, and the output logic transits from ‘1’ to ‘0’. The output logic ‘0’ is also stored under zero-bias conditions while blocking the current path. The input logic gate ‘10’ operates with VIN1 = 1.0 V and VIN2 = − 1.0 V, resulting in output logic ‘0’, and thereby the hold ‘0’ state is maintained. Subsequently, the input logic gate ‘11’ operates with VIN1 = 1.0 V and VIN2 = 1.0 V, and the output state is stored after the output logic ‘0’ is performed because two n-FBFETs are turned on, which pulls VOUT down to VSS. For the write operations, the calculated average write energy is approximately 0.2 pJ/bit. In addition, for the read operations, no sensing voltage is required to read the VOUT because the logic states of the NOR LIM are stored as VOUT.

To demonstrate the retention time of holding the output logic state after the input logic operation of the NAND and NOR LIM, we initialized the output logic to ‘0’. Subsequently, input voltages corresponding to the input logic with a pulse width of 5 ns were applied, and all zero-bias conditions were maintained for 100 s, as shown in Fig. 3. The retention time is calculated as the time at which the output voltage reaches 37% of the initial VOUT. As a result, the retention time of the NAND LIM corresponding to the input logic sequence ‘00’, ‘01’, ‘10’, and ‘11’ is 25.08 s, 21.78 s, 24.75 s, and 57.84 s, which represents 37% of the initial VOUT as shown in Fig. 3a; note that the retention time of the presented LIM is compared in Table 1 with existing charge- or resistance-based memory. Likewise, the retention time of the NOR LIM corresponding to the input logic sequence ‘00’, ‘01’, ‘10’, and ‘11’ is 22.37 s, 29.54 s, 31.21 s, and 33.96 s as shown in Fig. 3b. The retention time of the NAND and NOR LIM is affected by the parasitic capacitor since the output value is temporarily stored in the parasitic capacitor after the dynamic logic operation; the retention time of the logic circuit including the parasitic capacitor is longer than that of the logic circuit without the parasitic capacitor. On the other hand, the logic circuit composed of MOSFETs with the parasitic capacitor does not maintain the logic operation values, in contradistinction to the logic circuit composed of FBFETs with the parasitic capacitor. Changes in retention time depending on the parasitic load capacitance are described in our supplementary section 3. Although the same output states of ‘0’ or’1’ are carried out in the NAND and NOR LIM, there is a slight difference in the retention times. This is because each of the FBFETs has a difference in on-/off-resistance due to a slightly different potential barrier formed in the channel region when the transient switching is operated by the four input pulses40,41. This leads to different resistance ratios between the pull-up and pull-down networks. On the other hand, the use of the different supply voltages becomes a bottleneck in a commercial circuit, and hence the matching of the resistances between the pull-up and -down networks is needed to overcome the supply voltage problem. The resistance ratio determines the VOUT value by dividing the voltage of the supply voltages on each node of the NAND and NOR LIM. Thereafter, the VOUT is retained without any external bias as long as the resistance ratio is maintained because of the presence of a potential barrier that modulates over time. Consequently, the retention characteristics depend not only on the retention feature of a single FBFET, but also on the circuit configuration where the supply voltages are divided.

LIM retention characteristics. (a) Time-dependent retention characteristics for VOUT of NAND LIM, following the input logic of ‘00’, ‘01’, ‘10’, and ‘11’ with each pulse width of 5 ns, respectively. (b) Time-dependent retention characteristics for VOUT of NOR LIM, following the input logic of ‘00’, ‘01’, ‘10’, and ‘11’ with each pulse width of 5 ns, respectively. The retention time for output logic is the time corresponding to 37% of the initial VOUT.

Dynamic voltage-transfer characteristics of the LIMs

We newly defined the dynamic VTC of the NAND and NOR LIM for two input voltages to demonstrate the operation mechanism of these LIMs, as shown in Figs. 4 and 5. In the conventional CMOS NAND and NOR gates, the VTC corresponding to VOUT-VIN characteristics of the gate combination is shown when static bias is applied, and the VTC only indicates the logical operation of the NAND and NOR gates. In contrast, our dynamic VTC of the NAND and NOR LIM additionally shows memory operation without any power supply voltage and uses the same scheme as CMOS NAND and NOR gate combination. In other words, when input voltages (VIN1, VIN2, VDD, and VSS) are applied, the logical operation of the NAND and NOR LIM is conducted, as shown in the truth table of Fig. 1c,d. Additionally, unlike CMOS NAND and NOR logic gates, when all supply voltages are applied at 0 V, the memory operation in which the previous logic state is maintained is performed. This is portrayed graphically using a dynamic VTC.

VTCs demonstration with a certain sequence. (a) Dynamic VTCs of the NAND LIM sweeping VIN1 with pulse values of (a) VIN2 = 1.0 V. (b) Timing diagrams corresponding to the sequential dynamic VTCs. (c) Tables (c) summarize the performed logic operations. (d) Dynamic VTC of the NOR LIM in a sweep of VIN1 with pulse values of (d) VIN2 = 1.0 V. e, Timing diagrams corresponding to the sequential dynamic VTCs. (f) Tables (f) summarize the performed logic operations.

The detailed VTC operation mechanism of the NAND and NOR LIM is depicted in Fig. 4a,d, which includes the sequence of operation under a pulse value of VIN2 = 1.0 V. Figure 4b,e show timing diagrams reflecting the dynamic operation of a pulse width of 5 ns for input logic and a hold time of 10 ns for memory operation under all zero-bias conditions. The notation ① indicates the starting point, and the notations ②–⑨ indicate a sequence of operating VIN1 clockwise. The notation ①, the starting point of the graph, indicates the input logic ‘11’ of the NAND and NOR LIM, and its corresponding results, output logic ‘0’s, are shown in the truth table of Fig. 1c,d. The notation ② indicates the ramping (rising/falling) time of 1 ns for the logic operation, which is the time to reach the next operation, notation ③. Notation ③ shows the hold ‘0’ operations that retains the previous output logic ‘0’ under VDD, VSS, VIN1, and VIN2 of 0.0 V. Notation ④ indicates the ramping time of 1 ns to proceed to the next operation, notation ⑤. Notation ⑤ shows the input logic ‘01’, resulting in an output logic of ‘1’ in the NAND LIM and ‘0’ in the NOR LIM. To move on to the next operation of holding the output logic ‘1’ of NAND LIM and the output logic ‘0’ of NOR LIM, notation ⑥ has a ramping time of 1 ns. The hold ‘1’ and the hold ‘0’ are maintained, which achieves approximately zero static power consumption, as shown in notation ⑦. After notation ⑧ operates, which comprises a ramping time of 1 ns, the input logic ‘11’ corresponding to notation ⑨ operates. Finally, the closed memory windows of the dynamic VTCs are completed as VIN1 sweeps clockwise to 1.0 V. Figure 4c,f are summaries of the logic operations performed in Fig. 4a,d, respectively. The memory windows as shown in Fig. 4a,b indicate not only the input logic combinations ‘11’, ‘01’, and ‘11’ of the NAND and NOR LIM but also the memory operation of the output logic under all zero bias conditions. Figure 5a,b show the dynamic NAND and NOR VTCs that VIN1 operates from 1.0 V in the clockwise direction with different VIN2 pulses of − 1.0 V, − 0.5 V, 0.0 V, 0.5 V, and 1.0 V, respectively. All starting points are VIN1 = 1.0 V in the dynamic VTC, which represents the initial logic combinations, and the operating sequence of the dynamic VTCs as shown in Fig. 5 corresponds to the explanation in Fig. 4. Additional analyses of other combinations and the VTC corresponding to the anticlockwise direction sweeping VIN2 with different pulses of VIN1 are shown in supplementary sections 4–9.

Consequently, the memory windows of the dynamic VTC have important aspects for interpreting the NAND and NOR LIM operation under the same dynamic bias conditions, as shown in Fig. 2a,b. Note that the sharp transition performance reveals that p- and n-FBFETs utilized in NAND and NOR LIM have steep switching characteristics of near-zero SS. Therefore, our NAND and NOR LIMs can accurately perform not only the output voltage swings for well-defined logic ‘0’ and logic ‘1’ voltages but also memory operation at a range of voltage of the memory windows.

Conclusion

The presented NAND and NOR LIM composed of two-component SiNW p- and n-FBFETs exhibit logic operations with a fast processing speed of 5 ns and memory characteristics that retain the output logic states for input logic combination without any additional bias supplies, based on a positive feedback mechanism. The dynamic VTCs verify the electrical characteristics of two-input gates, which correspond to the NAND and NOR LIM operations. This work contributes to a timely discussion of new computing systems, proposing the NAND and NOR LIMs to improve the energy efficiency and latency compared to traditional computing architecture with the von Neumann bottleneck.

Methods

This simulation was conducted based on the two-dimensional structure of the FBFETs using a TCAD simulator (Synopsys’ Sentaurus™, Version O_2018.06, https://www.synopsys.com/ silicon/tcad.html) to investigate the NAND and NOR LIM26. This simulation based on the two-dimensional structure was performed to investigate and understand the overall functionality of the LIMs comprising nanoscale single-gated FBFETs, gaining an insight into its future memory applications; the two-dimensional simulation results can be sufficient to demonstrate the functionality of three-dimensional devices42,43. The simulation models for analyzing the FBFETs included Fermi–Dirac carrier statistics, doping-dependent mobility, high-field saturation mobility, Lombardi including a transverse field-dependent model of mobility with phonon scattering and surface roughness scattering according to Matthiessen’s rule, and Slotboom bandgap-narrowing. We also considered the Shockley–Read–Hall recombination and Auger recombination. We used the default parameters for these models using the Sentaurus Device in our simulations. All dynamic operations in this study were performed through transient simulation.

References

Gubbi, J. R. et al. Internet of Things (IoT): A vision, architectural elements, and future directions. Futur. Gener. Comput. Syst. 29, 1645–1660 (2013).

Philip, C. C. L. et al. Data-intensive applications, challenges, techniques and technologies: A survey on Big Data. Inf. Sci. 275, 314–347 (2014).

Gantz, J. et al. The digital universe in 2020: Big data, bigger digital shadows, and biggest growth in the far east. IDC iView IDC Anal. Future 2007, 1–16 (2012).

Zhang, B. et al. 90% yield production of polymer nano-memristor for in-memory computing. Nat Commun. 12, 1984 (2021).

Sebastian, A. et al. Memory devices and applications for in-memory computing. Nat Nanotechnol. 15, 529–544 (2020).

Burks, A. W. et al. Preliminary discussion of the logical design of an electronic computing instrument. in Texts and Monographs in Computer Science Book Series 399–413 (1982).

Neumann, J. V. First draft of a report on the EDVAC. IEEE Ann. Hist. Comput. 15, 27–75 (1993).

Wadden, J. et al. Characterizing and mitigating output reporting bottlenecks in spatial automata processing architectures. In Proc. 2018 IEEE International Symposium on High Performance Computer Architecture (HPCA) 749–761 (2018).

Mutlu, O. et al. Processing data where it makes sense: Enabling in-memory computation. Microprocess. Microsyst. 67, 28–41 (2019).

Reis, D. et al. Modeling and benchmarking computing-in-memory for design space exploration. in Proc. the 2020 on Great Lakes Symposium on VLSI 1–1 (2020).

Zahoor, F. et al. Resistive Random Access Memory (RRAM): An overview of materials, switching mechanism, performance, multilevel cell (mlc) storage, modeling, and applications. Nanoscale Res Lett. 15, 90 (2020).

Zhao, J. et al. Memory and storage system design with nonvolatile memory technologies. IPSJ Trans. Syst. LSI Des. Methodol. 8, 2–11 (2015).

Merrikh-Bayat, F. et al. High-performance mixed-signal neurocomputing with nanoscale floating-gate memory cell arrays. IEEE Trans. Neural Netw. Learn. Syst. 29, 4782–4790 (2018).

Kang, M. et al. S-FLASH: A NAND flash-based deep neural network accelerator exploiting bit-level sparsity. IEEE Trans. Comput. https://doi.org/10.1109/TC.2021.3082003 (2021).

Jhang, C. J. et al. Challenges and trends of SRAM-based computing-in-memory for AI edge devices. IEEE Trans. Circuits Syst. 68, 1773–1786 (2021).

Wang, G. et al. A 1T2C FeCAP-based in-situ bitwise X(N)OR logic operation with two-step write-back circuit for accelerating compute-in-memory. Micromachines 12, 385 (2021).

Sudarshan, C. et al. A novel DRAM-based process-in-memory architecture and its implementation for CNNs. In Proc. 26th Asia and South Pacific Design Automation Conference 35–42 (2021).

Wang, K. L. et al. Low-power non-volatile spintronic memory: STT-RAM and beyond. J. Phys. D Appl. Phys. 46, 074003 (2013).

Chen, A. et al. Emerging Nanoelectronic Devices (Wiley, 2014).

Wong, H. S. P. et al. Phase change memory. Proc. IEEE. 98, 2201–2227 (2010).

Burr, G. W. et al. Recent progress in phase-change memory technology. IEEE J. Emerg. Sel. Top. Circuits Syst. 6, 146–162 (2016).

Khvalkovskiy, A. V. et al. Erratum: Basic principles of STT-MRAM cell operation in memory arrays. J. Phys. D: Appl. Phys. 46, 139601 (2013).

Xue, C-X. et al. A 1Mb multibit ReRAM computing-in-memory macro with 14.6ns parallel MAC computing time for CNN based AI edge processors. In Proc. 2019 IEEE International Solid-State Circuits Conference—(ISSCC) 388–390 (2019).

Zhang, L. et al. Experimental investigation of the reliability issue of RRAM based on high resistance state conduction. Nanotechnology 22, 254016 (2011).

Ching-Yi, C. et al. RRAM defect modeling and failure analysis based on march test and a novel squeeze-search scheme. IEEE Trans. Comput. 64, 180–190 (2015).

Pirovano, A. et al. Reliability study of phase-change nonvolatile memories. IEEE Trans. Device Mater. Reliab. 4, 422–427 (2004).

Zhao, W. S. et al. Failure and reliability analysis of STT-MRAM. Microelectron. Reliab. 52, 1848–1852 (2012).

Gao, B. Emerging non-volatile memories for computation-in-memory. In Proc. 25th Asia and South Pacific Design Automation Conference 381–384 (2020).

Kim, M. et al. Steep switching characteristics of single-gated feedback field-effect transistors. Nanotechnology 28, 055205 (2017).

Kim, Y. et al. Switchable-memory operation of silicon nanowire transistor. Adv. Electron. Mater. 4, 1800429 (2018).

Woo, S. et al. Device design of single-gated feedback field-effect transistors to achieve latch-up behaviors with high current gains. Curr. Appl. Phys. 20, 1156–1162 (2020).

Son, J. et al. Steep switching characteristics of partially gated p+–n+–i–n+ silicon-nanowire transistors. J. Nanosci. Nanotechnol. 21, 4330–4335 (2021).

Lee, M. et al. Top-down fabrication of fully CMOS-compatible silicon nanowire arrays and their integration into CMOS inverters on plastic. ACS Nano 5, 2629–2636 (2011).

Bangsaruntip, S. et al. High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling. In Proc. 2009 IEEE International Electron Devices Meeting (IEDM) 12.3.1–12.3.4 (2009).

Sentaurus Device User Guide. Version O-201806 (Synopsys, 2018).

Nayak, K. et al. CMOS logic device and circuit performance of Si gate all around nanowire MOSFET. IEEE Trans. Electron Devices 61, 3066–3074 (2014).

Gugulothu, B. et al. Modeling of capacitive coupled interconnects for crosstalk analysis in high speed VLSI circuits. In Proc. 2019 International Conference on Communication and Signal Processing (ICCSP) 7–11 (2019).

Lim, D. et al. Quasi-nonvolatile silicon memory device. Adv. Mater. Technol. 5, 2000915 (2020).

Park, Y. S. et al. Inverting logic-in-memory cells comprising silicon nanowire feedback field-effect transistors. Nanotechnology 32, 225202 (2021).

Chen, W. C. et al. A novel supersteep subthreshold slope dual-channel FET utilizing a gate-controlled thyristor mode-induced positive feedback current. IEEE Trans. Electron Devices 64, 1336–1342 (2017).

Tura, A. et al. Performance comparison of silicon steep subthreshold FETs. IEEE Trans. Electron Devices 57, 1362–1368 (2010).

Zhu, G. et al. Subcircuit compact model for dopant-segregated Schottky gate-all-around Si-nanowire MOSFETs. IEEE Trans. Electron Devices 57, 772–781 (2000).

Manikandan, S. et al. Analytical model of double gate stacked oxide junctionless transistor considering source/drain depletion effects for CMOS low power applications. SILICON 12, 2053–2063 (2020).

Acknowledgements

This research was supported by a National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT; 2020R1A2C3004538), the Brain Korea 21 Plus Project of 2021 through the NRF funded by the Ministry of Science, ICT & Future Planning, and the Korea University Grant.

Author information

Authors and Affiliations

Contributions

Y.Y., J.J., J.S., and S.K. provided the conceptualization and methodology. Y.Y. and K.C. verified and investigated. Y.Y. and S.K. analyzed the results and wrote the manuscript; S.K. supervised the research. All authors edited the manuscript and approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yang, Y., Jeon, J., Son, J. et al. NAND and NOR logic-in-memory comprising silicon nanowire feedback field-effect transistors. Sci Rep 12, 3643 (2022). https://doi.org/10.1038/s41598-022-07368-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-07368-0

This article is cited by

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.