Abstract

We demonstrate the measurement of p-channel silicon-on-insulator quantum dots at liquid helium temperatures by using a radio frequency (rf) reflectometry circuit comprising of two independently tunable GaAs varactors. This arrangement allows observing Coulomb diamonds at 4.2 K under nearly best matching condition and optimal signal-to-noise ratio. We also discuss the rf leakage induced by the presence of the large top gate in MOS nanostructures and its consequence on the efficiency of rf-reflectometry. These results open the way to fast and sensitive readout in multi-gate architectures, including multi qubit platforms.

Similar content being viewed by others

Introduction

Hole spins confined in silicon structures have attracted considerable attention due to their ability to provide quantum bit architectures a longer coherence1 and faster gate operation times2 compared to electrons in III–V materials3. They also take advantage of an all electric field control due to the increase in the spin-orbit coupling strength4,5,6,7, a charge offset stability8 necessary for scalability purposes as well as a necessary compatibility with current industry production lines in view of commercialisation9,10,11. However, to take full advantage of these properties for quantum computing applications, one has to circumvent the limitation in bandwidth resulting from the formation of the low-pass filter circuit made from the large input impedance of the device or the measurement unit and the large cabling capacitance. In the first case, traditional transimpedance amplifiers are structurally limited to bandwidths of a few kilohertz due to a large input resistance and capacitance12. Also one has to manage the intrinsic trade-off between output gain and bandwidth, with III–V amplifiers giving the highest speed while silicon based amplifiers generally providing a better gain. For the second case, the restriction lies in the length of cable that, all quality considered, has a capacitance in excess of 70 pF/m13. Finally, device geometry and structure play a significant part in the reduction in bandwidth. For example, tunnel barrier-based sensors require resistances of a few h/e\(^2\) for the observation of high quality Coulomb blockade oscillations that are used for monitoring of the charge state or for spin-to-charge conversion14.

Reflectometry techniques in the radio frequency (rf) range have purposely been developed to address the former issue by incorporating the device into an LC resonant circuit and measuring the modulated reflected signal at a frequency close to the resonant condition15. In quantum dot architectures, such a circuit can be integrated either at the sensor, for example a single electron transistor or a quantum point contact close to the device to measure16,17,18,19, or directly at one of the control gate of the device itself20,21,22,23,24,25,26,27. Both techniques have proven to be reliable with bandwidths in excess of 10 MHz and are particularly suited to quantum dots where the low-stray parasitic capacitance, generally lower than 1 pF, allows the use of moderate inductance sizes and values to obtain a high resonance frequency while retaining good impedance matching. Gated devices including double gate stacks, whose the top gate is generally large as it is used to create the inversion layer at the Si–SiO\(_2\) interface and provide conduction to the device whereas the underlying set of gates only aim at creating tunnel barriers and adjusting the tunneling rates28, provide a significant advantage in terms of charge noise screening, uniformity of the 2DEG compared with similar but doped structures. However, such advantages can be overcome by the formation of a low impedance leakage pathway to the ground for the rf signal that results from the large parasitic capacitance between the accumulation gate and the two-dimensional electron gas (2DEG)19,29,30. This is particularly severe for the area larger than a few tens of \(\upmu {\text{m}}^2\)31.

Aside bandwidth considerations, the reduction in the readout integration time has important implications. It allows improving readout fidelity once reaching timescales typically shorter than the relaxation time of the system \(T_1\) and envisioning surface code-based applications when measurements become much faster than the coherence time \(T_2\). However, shorter integration times unequivocally implies a reduction in the signal-to-noise ratio (SNR)32. In the low-signal regime, when the changes in the ratio of resistance to capacitance are small, the SNR depends on the coupling coefficient33,34 that becomes maximum at perfect matching condition. In order to achieve a high sensitivity while keeping perfect impedance matching, voltage-controlled capacitors, or varactors, are generally incorporated into the resonant circuit. Such an implementation has already been used to tune the resonant frequency of a quantum point contact in situ at 1.8 K35. Similarly, a couple of varactors have been used for impedance matching purposes to measure both the charge sensitivity and the impedance of a quantum dot at 1 K33. More recently, a high-quality resonator with low parasitic capacitance was combined with varactors to improve significantly the charge sensitivity in the range of 55 mK to 1.5 K34. Such a limitation in the use of rf reflectometry can be severe in certains architectures, like in p-channel silicon devices where mobilities are lower compared to the ones found in n-type devices. This generates an excess resistance in the 2DHG and decreases the readout sensitivity rendering rf measurements more challenging. In this study, we purposely use p-channel Metal-Oxide-Semiconductor (PMOS) devices to demonstrate such an rf leakage effect induced by the top gate and discuss the ability to perform rf reflectometry.

Results

We first used device 2 and determined the parasitic capacitance \(C_{\text {p}}\) of the tank circuit by monitoring the variation of the resonance frequency \(f_{\text {r}} = 1/2\pi \sqrt{L C_{\text {p}}}\) with the inductance value L. We obtained \(C_{\text {p}} \sim\) 0.48 pF. Several inductors were then used to obtain a set of resonant frequencies \(f_{\text {r}}\) between 401 and 201 MHz that we used as carrier frequencies. For each inductors, the top gate voltage \(V_{\text {tg}}\) was swept and both the DC conductivity and the reflective RF signal were measured as shown in Fig. 1. We noticed that for probing frequency \(f_{c}\gg\) 326 MHz and despite having a clear DC signal, no reflective signal was observed. This is a consequence of the too high value of the parasitic capacitance and consequently a gate impedance much lower than the matching circuit impedance. However, an rf-response is clearly observed for frequencies lower than 306 MHz. One can find out that the impedance of the parasitic capacitance decreases as the probing frequency increases allowing determining an upper bound for the usable probing frequency in our rf-setup. We should underline that all measurements have been performed under relatively good matching conditions with the depth of resonant dip exceeding 7 dB, which indicates that the impedance matching mostly affects the measurement sensitivity and not the ability to perform reflectivity measurements itself.

The rf-response at various probing frequencies for device 2. (a) Reflectivity response \(S_{\text {11}}\) together with the corresponding DC current as a function of the top gate voltage \(V_{\text {tg}}\) at 4.2 K. (b) Comparison of the rf- and DC responses in the accumulation, depletion and inversion regions.

Despite the parasitic capacitance in device 2 being reduced compared with even larger devices (\(C_{\text {p}} \approx\) 0.6 pF for a device with a top gate of \(4\times 10^2\) \(\upmu{\text{m}}^2\)), this still remains an issue for measurements requiring a high sensitivity. To mitigate this, we used the smallest gate area device (device 1) for which \(C_{\text{p}} \sim\) 0.26 pF for the remaining experiments. It is worth mentioning that several parameters affect the parasitic capacitance, such as the material used in the printed circuit board (PCB), the distance between the PCB and the device, as well as the number of bonding wires used to connect the device to the PCB. Moreover, capacitance components are distributed in actual CMOS devices. Therefore, there is not necessarily a direct ratio between the reduced area of the top gate and parasitic capacitance obtained.

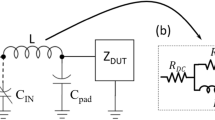

We first check the ability to independently adjust the \(f_{\text{r}}\) and the sensibility of the reflectometry circuit by mapping out the variation of the reflection coefficient \(S_{{11}}\) in terms of \(V_{\text{t}}\) and \(V_{\text{m}}\), associated with varactor capacitance \(C_{\text{t}}\) and \(C_{\text{m}}\), respectively, over the range 0 to 10 V. As expected the resonance amplitude, and so the quality factor Q of the matching circuit, changes with \(V_{\text{m}}\) without significantly affecting the resonant frequency value \(f_{\text{r}}\)33. We then selected a reduced range of varactor voltages and optimised the \(S_{{11}}\) parameter to obtain the best matching condition among our measurements (see S2). We observe two set of possible voltage values (\(V_{\text{t}}\), \(V_{\text{m}}\)) for which the \(\Delta S_{{11}}\) value is maximum (Fig. 2a). Despite \(V_{\text{t}}\) being able to improve the matching, it mostly controls \(f_{\text{r}}\) due to its proximity to the circuit. On the contrary, \(C_{\text{m}}\) is located upfront of the matching input point, making it more suitable and more efficient for matching purposes. Best matching is obtained for \(V_{\text{m}}\) = 1.5 V and \(V_{\text{t}}\) = 5 V, corresponding to \(C_{\text{t}} = 6\) pF and \(C_{\text{m}} = 5.5\) pF. This gives a reflective signal depth of 63 dB. In the view of increasing the measurement sensitivity, namely the quality factor, a higher value for the inductor would be needed but this would ultimately reduce the bandwidth and introduce unintentionally inductor self-resonances around the carrier frequency.

SNR measurement of device 1. (a) Variation of the reflection’s magnitude as a function of varactor voltages \(V_{\text{m}}\) versus \(V_{\text{t}}\). \(\Delta\) \(S_{{11}}\) represents the amplitude in dB while voltages are applied to both varactors. The minimum amplitude is 9 dB and, it is obtained in the case \(V_{\text{m}} =\) 0 V, \(V_{\text{t}} =\) 10 V. Best matching is obtained for \(V_{\text{m}}\) = 1.5 V (\(\sim\) 5.5 pF) and \(V_{\text{t}}\) = 5 V (\(\sim\) 6 pF) giving a maximum reflective depth of 63 dB for \(\Delta\) \(S_{{11}}\) (b) gate oscillations for device 1 as a function of top gate voltage (\(V_{\text{tg}}\)) at 4.2 K with \(V_{\text{t}} = 5\) V and \(V_{\text{m}} = 1\) V. The operating point was set to the maximum transconductance \(V_{\text{tg}}=-1.85\) V for the SNR measurements in order to achieve the maximum sensitivity. (c) Modulation spectrum showing the 3 kHz sidebands due to the modulating signal (\(f_{\text{m}}\)) of amplitude 10 mV rms applied to the top gate. (d) Variation of the SNR with \(V_{\text{m}}\) at \(V_{\text{t}} =\) 5 V showing a maximum value at \(V_{\text{m}}\) = 1.5 V.

In order to correlate the depth of the impedance matching to the SNR, we set \(V_{\text{t}} = 5\) V and adjusted the value of the top gate to the maximum of the transconductance, i.e. \(-1.85\) V (Fig. 2b). We then applied a small ac-signal of amplitude 10 mV rms and frequency 3 kHz on the top gate and observed the amplitude modulation (AM) spectrum of the quantum dot prior demodulation. The visibility of the sidebands at \(f_{\text{c}}\pm\) 3 kHz allows determining the SNR value (Fig. 2c). We were then able to obtain the variation of the measurement sensitivity as a function of \(V_{\text{m}}\) while keeping the resonant frequency unaffected.

As observed previously, the maximum SNR is obtained at \(V_{\text{m}} = 1.5\) V implying a best matching condition (Fig. 2d). However, we did perform additional rf measurements at different matching conditions to monitor the value of the sensitivity. In the case both varactors were turned off, we did not observed any Coulomb diamonds (Fig. 3a). Away from optimal matching, Coulomb diamonds were barely discernable (Fig. 3b) while their visibility was largely improved under best matching (Fig. 3c). These results confirm the increase in SNR as the matching conditions get optimised.

Charge stability diagram of device 1 obtained by rf reflectometry for three different impedance matching conditions. (a) Both varactors are turned off, (b) impedance matching is away from best matching (\(V_{\text{m}}\) = 1.1 V, \(V_{\text{t}}\) = 5 V), (c) best matching condition (\(V_{\text{m}}\) = 1.5 V, \(V_{\text{t}}\) = 5 V).

Discussion

The charge sensitivity is given by \(\delta _q = \Delta _{\text{q}}\) \(_{\text{rms}}/{(\sqrt{2{\text{RBW}}}. 10^{{\text{SNR}}/20}})\) where \(\Delta {\text{q}}_{\text{rms}}\) is the applied root-mean-square gate charge, RBW the resolution bandwidth, and SNR the signal-to-noise ratio. At the best matching point, we obtained \(\Delta {\text{q}}_{\text{rms}}\) \(\sim 0.11e_{\text{rms}}\), RBW \(=5.1\) Hz, and SNR \(=15.5\) dB giving \(\delta _q \approx {6.10^{-3}} e/\sqrt{\text{Hz}}\). The maximum sensitivity in pure rf mode has been calculated by Korotkov and Paalanen36. In our setup, the sensitivity is mainly limited by the tunnel resistance, \(R_{\text{t}} = 5.10^7\ \Omega\), and total island capacitance, \(C_\Sigma =10^{-17} \ {\text{F}}\) which are both device related. Having a relatively high resistance in PMOS devices results in a low charge sensitivity. Other limiting factors include the noise generated by room temperature amplifiers, the losses at the inductor, and dielectric losses at the PCB. All account for the decrease in sensitivity. We should mention that thermal noise and device characteristics may be responsible of irregularity in the Coulomb diamonds even at the best matching condition (Fig. 3c).

As a conclusion, we have determined an upper bound for the usable frequency in our rf-reflectometry setup above which the gate impedance becomes sufficiently small and the rf-leakage to the ground gets dominant. By tuning the frequency into the appropriate range and by using two GaAs-based varactors to alleviate the stray capacitance, tune the resonant frequency and improve the matching condition of the circuit, we were able to perform an rf-readout of physically defined p-channel silicon quantum dots. Under best matching condition and optimum SNR, we successfully observed Coulomb diamonds at 4.2 K. This study underlines the necessity of carefully designing the device structure in order to achieve high measurement sensitivity and increase the operability of the rf-reflectometry. The addition of the two varactors in the circuit allows the necessary tuning flexibility which will be required in a multi-qubit platform, where crosstalks are unavoidable and frequency multiplexing is expected to be used for both addressing and readout. The demonstration of optimised circuitry at 4.2 K is promising for future high temperature operation of quantum bits.

Methods

Device fabrication

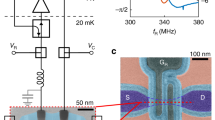

Scanning electron microscope (SEM) image and schematic image of the device are shown in Fig. 4a,b, respectively. All devices were fabricated from an undoped 40-nm-thick silicon-on-insulator (SOI) with a 145-nm-thick buried oxide. Quantum dot structures and the side gate were then formed by etching the silicon active layer at selected regions using inductive coupled plasma reactive ion etching (ICP-RIE)31,37,38,39. However, in these experiments the side gate was not used. After a standard RCA clean, a 3-nm-thick thermal oxide layer was grown with dry oxidation at 850\(^\circ\) before the deposition of a 65-nm-thick gate oxide. A top gate made from highly phosphorus-doped polysilicon at a concentration of \(10^{-20}\) cm\(^{-3}\) was then deposited. Two devices are used in our study, both having the same structure but different top gate areas, one with a surface area of 0.09 \(\upmu{\text{m}}^2\) (device 1) and the other with an area of 1 \(\upmu{\text{m}}^2\) (device 2).

Measurement setup

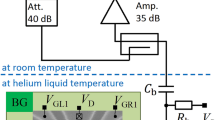

Experiments are performed using the setup shown in Fig. 5. Figure 5a,b refer to the room temperature measurement setup while Fig. 5c shows the cryogenic part of the setup used at 4.2 K. The rf-signal passing through the directional coupler is first attenuated with a \(-40\) dB attenuator before be sent to the quantum dot and the tank circuit. The reflected signal is then amplified with room temperature amplifiers with a total gain of 60 dB either using the setup (a) or (b) depending on the measurement intended. For the resonant circuit, we used a GaAs double varactor (a Macom MA46H202-1056 for \(C_{\text{m}}\) and a Macom MA46H204-1056 for \(C_{\text{t}}\)) in order to tune both the resonance frequency to the region of operation and the impedance matching. This allows reading out the charge states of a PMOS quantum dot at 4.2 K, under high SNR and up tp perfect the matching conditions. For the measurement of device 1, we added a matching capacitor \(C_{\text{m}}\) as well as a decoupling capacitor \(C_{\text{d}}\) (\(\sim\) 24 pF) at the input point of the matching circuit. The aim of \(C_{\text{d}}\) is to increase the quality factor Q of the circuit by decoupling it from the input. The varactor \(C_{\text{t}}\) controlled by \(V_{\text{t}}\), aims at controlling the resonant frequency \(f_{\text{r}}\) and the loaded impedance \(Z_{\text{L}}\) while the second varactor \(C_{\text{m}}\), controlled by \(V_{\text{m}}\), mostly adjusts the value of \(Z_{\text{L}}\) and hence the sensitivity (see S2). The rf-signal was added via a bias tee to the drain of the device with all the electronic components mounted on a standard FR4 printed circuit board (see S1).

Device structure. (a) Scanning electron microscope (SEM) image of the device after reactive ion etching. Darkest areas are parts of the SOI that have been etched away whereas the island at the centre is the quantum dot under study with its associated control gate \(G_{\text{SDQ}}\), (b) device internal structure once fully processed.

Measurement setup. (a) Room temperature part of the circuit used for the resonant frequency \(f_{\text{r}}\) dependence measurement. The rf signal at 0 dBm is first attenuated before entering a directional coupler and being sent to the quantum dot via the resonant circuit at low temperature. The reflected signal is then amplified at high gain before being measured at the port 2 of the vector network analyzer (VNA). (b) Room temperature part of the circuit used to readout the charge state. Here, the signal from the rf-source is split between the incident signal sent directly to the device at low temperature and the demodulator for the measurement of the in-phase (I) and quadrature (Q) components of the reflected signal. (c) The resonant circuit with an inductor of 277 nH together with the two varactors \(C_{\text{m}}\) and \(C_{\text{t}}\). \(R_{\text{d}}\) represents the losses in the measurement system including the dielectric losses in the device, the printed circuit board (PCB), and in tuning the varactors.

In rf experiments, the choice for \(f_{\text{c}}\) is dictated by both noise and circuit impedance considerations, typically. To maintain a high SNR, \(f_{\text{c}}\) should always exceed the 1/f noise caused by charge fluctuations15. On the other hand, if the rf-signal is connected to the leads, the impedance of the matching circuit \(Z_{\text{m}}\) shall not be much larger than the gate impedance \(Z_{\text{g}} = 1/2\pi \dot{\imath } f_{\text{c}} C_{\text{g}}\) where \(C_{\text{g}}\) is the parasitic capacitance of the gate, if one wants to avoid leakage of the rf-signal. Such a leakage effect is well demonstrated in the device with the larger gate area (device 2) by exploring its rf-response at different carrier frequencies and so, at different values of the resonant circuit inductance.

References

Veldhorst, M. et al. An addressable quantum dot qubit with fault-tolerant control-fidelity. Nat. Nanotechnol. 9, 981 (2014).

Hendrickx, N. W., Franke, D. P., Sammak, A., Scappucci, G. & Veldhorst, M. Fast two-qubit logic with holes in germanium. Nature 577, 487–491. https://doi.org/10.1038/s41586-019-1919-3 (2020).

Pribiag, V. S. et al. Electrical control over single hole spins in nanowire quantum dots. Nat. Nanotechnol. 8, 170–174. https://doi.org/10.1007/10.1038/nnano.2013.5 (2013).

Voisin, B. et al. Electrical control of g-factor in a few-hole silicon nanowire MOSFET. Nano Lett. 16, 88–92 (2016).

Li, R., Hudson, F. E., Dzurak, A. S. & Hamilton, A. R. Pauli spin blockade of heavy holes in a silicon double quantum dot. Nano Lett. 15, 7314–7318 (2015).

Maurand, R. et al. A CMOS silicon spin qubit. Nat. Commun. 7, 1–6 (2016).

Szumniak, P., Bednarek, S., Partoens, B. & Peeters, F. M. Spin-orbit-mediated manipulation of heavy-hole spin qubits in gated semiconductor nanodevices. Phys. Rev. Lett. 109, 107201. https://doi.org/10.1103/PhysRevLett.109.107201 (2012).

Zimmerman, N. M., Huber, W. H., Fujiwara, A. & Takahashi, Y. Excellent charge offset stability in a Si-based single-electron tunneling transistor. Appl. Phys. Lett. 79, 3188–3190 (2001).

Veldhorst, M., Eenink, H., Yang, C. & Dzurak, A. S. Silicon CMOS architecture for a spin-based quantum computer. Nat. Commun. 8, 1–8 (2017).

Vandersypen, L. et al. Interfacing spin qubits in quantum dots and donors—Hot, dense, and coherent. npj Quantum Inf. 3, 1–10 (2017).

Gonzalez-Zalba, M. et al. Scaling silicon-based quantum computing using cmos technology: State-of-the-art, challenges and perspectives. arXiv preprint arXiv:2011.11753 (2020).

Manoharan, M., Tsuchiya, Y., Oda, S. & Mizuta, H. Silicon-on-insulator-based radio frequency single-electron transistors operating at temperatures above 4.2 K. Nano Lett. 8, 4648–4652 (2008).

Gautschi, G. Piezoelectric Sensorics: Force Strain Pressure Acceleration and Acoustic Emission Sensors Materials and Amplifiers (Springer, 2013).

Elzerman, J. J. M. et al. Few-electron quantum dot circuit with integrated charge read out. Phys. Rev. B 67, 161308(R). https://doi.org/10.1103/PhysRevB.67.161308 (2003).

Schoelkopf, R. J., Wahlgren, P., Kozhevnikov, A. A., Delsing, P. & Prober, D. E. The radio-frequency single-electron transistor (RF-SET): A fast and ultrasensitive electrometer. Science 280, 1238–1242. https://doi.org/10.1126/science.280.5367.1238 (1998).

Qin, H. & Williams, D. A. Radio-frequency point-contact electrometer. Appl. Phys. Lett. 88, 203506 (2006).

Cassidy, M. et al. Single shot charge detection using a radio-frequency quantum point contact. Appl. Phys. Lett. 91, 222104 (2007).

Reilly, D., Marcus, C., Hanson, M. & Gossard, A. Fast single-charge sensing with a rf quantum point contact. Appl. Phys. Lett. 91, 162101 (2007).

Noiri, A. et al. Radio-frequency-detected fast charge sensing in undoped silicon quantum dots. Nano Lett. 20, 947–952 (2020).

Colless, J. et al. Dispersive readout of a few-electron double quantum dot with fast rf gate sensors. Phys. Rev. Lett. 110, 046805 (2013).

Petersson, K. et al. Charge and spin state readout of a double quantum dot coupled to a resonator. Nano Lett. 10, 2789–2793 (2010).

Crippa, A. et al. Gate-reflectometry dispersive readout and coherent control of a spin qubit in silicon. Nat. Commun. 10, 1–6 (2019).

Schroer, M., Jung, M., Petersson, K. & Petta, J. R. Radio frequency charge parity meter. Phys. Rev. Lett. 109, 166804 (2012).

Urdampilleta, M. et al. Charge dynamics and spin blockade in a hybrid double quantum dot in silicon. Phys. Rev. X 5, 031024 (2015).

Gonzalez-Zalba, M., Barraud, S., Ferguson, A. & Betz, A. Probing the limits of gate-based charge sensing. Nat. Commun. 6, 1–8 (2015).

Ahmed, I. et al. Radio-frequency capacitive gate-based sensing. Phys. Rev. Appl. 10, 014018. https://doi.org/10.1103/PhysRevApplied.10.014018 (2018).

Schaal, S. et al. Fast gate-based readout of silicon quantum dots using Josephson parametric amplification. Phys. Rev. Lett. 124, 067701 (2020).

Nakagawa, T., Sekigawa, T., Tsutsumi, T., Suzuki, E. & Koike, H. Primary consideration on compact modeling of DG MOSFETs with four-terminal operation mode. In 2003 Nanotechnology Conference and Trade Show-Nanotech 2003, 330–333 (2003).

Connors, E. J., Nelson, J. & Nichol, J. M. Rapid high-fidelity spin-state readout in Si/Si–Ge quantum dots via rf reflectometry. Phys. Rev. Appl. 13, 024019 (2020).

Liu, Y.-Y. et al. Radio frequency reflectometry in silicon-based quantum dots. arXiv preprint arXiv:2012.14560 (2020).

Bugu, S. et al. RF reflectometry for readout of charge transition in a physically defined p-channel MOS silicon quantum dot. Jpn. J. Appl. Phys. 60, SBBI07. https://doi.org/10.35848/1347-4065/abeac1 (2021).

Ibberson, D. J. et al. Large dispersive interaction between a CMOS double quantum dot and microwave photons. arXiv preprint arXiv:2004.00334 (2020).

Ares, N. et al. Sensitive radio-frequency measurements of a quantum dot by tuning to perfect impedance matching. Phys. Rev. Appl. 5, 034011 (2016).

Ibberson, D. J. et al. Low-temperature tunable radio-frequency resonator for sensitive dispersive readout of nanoelectronic devices. Appl. Phys. Lett. 114, 123501 (2019).

Müller, T. et al. An in situ tunable radio-frequency quantum point contact. Appl. Phys. Lett. 97, 202104 (2010).

Korotkov, A. N. & Paalanen, M. A. Charge sensitivity of radio frequency single-electron transistor. Appl. Phys. Lett. 74, 4052–4054 (1999).

Kambara, T., Kodera, T., Arakawa, Y. & Oda, S. Dual function of single electron transistor coupled with double quantum dot: Gating and charge sensing. Jpn. J. Appl. Phys. 52, 04CJ01 (2013).

Horibe, K., Kodera, T. & Oda, S. Back-action-induced excitation of electrons in a silicon quantum dot with a single-electron transistor charge sensor. Appl. Phys. Lett. 106, 053119 (2015).

Yamaoka, Y., Iwasaki, K., Oda, S. & Kodera, T. Charge sensing and spin-related transport property of p-channel silicon quantum dots. Jpn. J. Appl. Phys. 56, 04CK07 (2017).

Acknowledgements

S. B. would like to thank M. F. Gonzalez-Zalba, J. Yoneda, and H. Takahashi for helpful discussion. S. B. also thanks the Hitachi Cambridge Laboratory for the hospitality. This work was partly supported by JST CREST (JPMJ CR1675), JSPS KAKENHI (Grant Numbers JP18K18996 and JP20H00237), MEXT Quantum Leap Flagship Program (Q-LEAP) Grant Number JPMXS0118069228, JST Moonshot R&D Grant Number JPMJMS2065 as well as MEXT Project for Developing Innovation Systems.

Author information

Authors and Affiliations

Contributions

S.B. designed the scheme, and conducted the experiments. S.B. also provided feedback for device fabrication. S.N., K.K., Y.L., S.M., T.M., and T.K. fabricated the devices. S.B., T.F. and T.K. analyzed the results and wrote the manuscript. T.K. managed the project.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Bugu, S., Nishiyama, S., Kato, K. et al. 4.2 K sensitivity-tunable radio frequency reflectometry of a physically defined p-channel silicon quantum dot. Sci Rep 11, 20039 (2021). https://doi.org/10.1038/s41598-021-99560-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-99560-x

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.