Abstract

Power devices (PD) are ubiquitous elements of the modern electronics industry that must satisfy the rigorous and diverse demands for robust power conversion systems that are essential for emerging technologies including Internet of Things (IoT), mobile electronics, and wearable devices. However, conventional PDs based on “bulk” and “single-crystal” semiconductors require high temperature (> 1000 °C) fabrication processing and a thick (typically a few tens to 100 μm) drift layer, thereby preventing their applications to compact devices, where PDs must be fabricated on a heat sensitive and flexible substrate. Here we report next-generation PDs based on “thin-films” of “amorphous” oxide semiconductors with the performance exceeding the silicon limit (a theoretical limit for a PD based on bulk single-crystal silicon). The breakthrough was achieved by the creation of an ideal Schottky interface without Fermi-level pinning at the interface, resulting in low specific on-resistance Ron,sp (< 1 × 10–4 Ω cm2) and high breakdown voltage VBD (~ 100 V). To demonstrate the unprecedented capability of the amorphous thin-film oxide power devices (ATOPs), we successfully fabricated a prototype on a flexible polyimide film, which is not compatible with the fabrication process of bulk single-crystal devices. The ATOP will play a central role in the development of next generation advanced technologies where devices require large area fabrication on flexible substrates and three-dimensional integration.

Similar content being viewed by others

Introduction

A power device (PD) is a general term for semiconductor on/off control elements, such as diodes and transistors for energy conversion (e.g. AC–DC conversion)1,2,3. Two important characteristics for designing PDs are specific on-resistance (Ron,sp) and breakdown voltage (VBD). According to these parameters, the numerical factor related to the efficiency of power conversion, which is critical for PDs, is represented by the figure of merit (FOM) according to the following relationship1,4:

which shows that a PD with low energy loss requires a large FOM value. Recently, application of materials such as gallium-nitride (GaN) and silicon-carbide (SiC) are being developed to replace single-crystal silicon (Si) because they are expected to exhibit higher FOM than Si1,5. However, PDs fabricated using these materials still suffer from fundamental constraints associated with “bulk” and “single-crystalline” materials that restrict the flexibility of designing devices (Fig. 1 bottom panel)1,5,6. Therefore, PDs based on “amorphous” and “thin-film” materials mitigate both of these problems and enable the fabrication of flexible devices using low temperature processes (Fig. 1 top panel). Although there have not been any reports of applications to date, amorphous oxide semiconductors (AOS) typically based on indium–gallium–zinc–oxide (InGaZnO)7,8 are candidates for producing PDs because Schottky barrier diodes (SBDs) with low Ron,sp9,10,11,12 and high VBD13,14 have been reported for these materials, with the high potential of achieving high FOM.

Concepts of amorphous thin-film oxide power device (ATOP, upper panel) compared with conventional bulk single crystal power device (PD, lower panel). (a) Structures of amorphous indium–gallium–zinc–oxide (InGaZnO) and single crystal silicon (Si). (b) Typical fabrication process of ATOP: thin-film growth on an arbitrary substrate by sputtering. That of the conventional PD: Bulk and epitaxial growth for bulk ingot and single-crystal semiconductor with the bulk substrate, respectively. (c) Material parameters of measured mobility μ and estimated critical breakdown field EC from measured bandgap for amorphous oxide semiconductor materials used in this work, and typical μ and EC for conventional PD materials. (d) PD structures of novel flexible ATOP and conventional rigid discrete.

Results and discussion

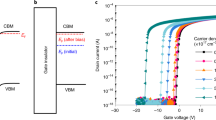

To demonstrate the potential of amorphous thin-film oxide power devices (ATOPs), we first fabricated SBD structures to assess the basic performance of PDs with a view to realizing high FOM. Notably, in order to improve FOM, both low Ron,sp and high VBD have to be achieved at the same time in spite of the trade-off between them1. In conventional AOS-SBD, the surfaces of Schottky electrodes of palladium (Pd) are oxidized with UV ozone treatment to improve the Schottky interface for lower Ron,sp and higher VBD13,14. With this approach, however, it is difficult to achieve high FOM because of a thin ~ 1 nm oxide layer on the Pd surface, resulting in insufficient Schottky interfaces which have relatively high resistance up to ~ 1 × 10–3 Ω cm2 and low VBD up to − 16 V13. To resolve this problem, we used a much thicker palladium-oxide (PdO) layer and succeeded in forming PdO layers with arbitrary thicknesses by introducing oxygen-added sputtering, which has not been applied to AOS-SBD so far. As shown in Fig. 2a and b, a 40 nm-thick PdO layer drastically improved VBD compared to AOS-SBD without PdO (Supplementary Fig. 1a, Supplementary Table 1a). Although the PdO layer led to an increase in Ron,sp because of an additional contact resistance, we found that an insertion of a Pd/Titanium(Ti) layer under the PdO layer circumvented this issue, maintaining low Ron,sp (Supplementary Fig. 1a, Supplementary Table 1a). Furthermore, we also developed a new method to control the drift layer thickness d, which is an important parameter as described later to maximize FOM for ATOPs. In contrast to conventional methods15, which cannot produce uniform layers with the thicknesses larger than 50 nm, our method enables the formation of uniform layers up to ~ 1000 nm (Supplementary Fig. 2a–c) by adding water vapour during the sputtering (see "Method" section). Accordingly, we succeeded in producing an SBD with VBD that varied linearly with d (Supplementary Fig. 6, Supplementary Table 1a). Such an optimized SBD was also confirmed to have an ideal Schottky barrier without pinning16,17 as shown in Fig. 2c and d.

Schottky interface improved by palladium-oxide (PdO) layer for high breakdown voltage VBD. (a) Schematic images of Schottky barrier diode (SBD) structures with and without a PdO layer at the Schottky interface. (b) Current density (J)–voltage (V) characteristics of before and after the optimization by PdO layer shown in (a). (c,d) Band diagrams for the Schottky contact of Pd–InGaZnO and PdO–InGaZnO, respectively. The work function ФWF, Schottky barrier height Vb and built-in voltage Vbi were obtained from the results of UPS (from Supplementary Fig. 2e and Supplementary Table 1b), J–V (from Supplementary Table 1a) and Capacitance (C)–Voltage (V) (from Supplementary Table 11c) measurements, respectively. The semiconductor electronic affinity χ is determined by VbCV, VbiCV and ФWF(InGaZnO). The interface dipole Δ is defined as ФWF(Metal) – (VbJV + χ). Δ = 0 indicates no pinning effect at the Schottky interface: Pd–InGaZnO contact with pinning (Δ ≠ 0) and PdO–InGaZnO contact without pinning (Δ = 0). Cross-sectional transmission electron microscope (TEM) images of the interface as shown in lower panel. The disordered interface, which can cause the pinning, is observed in (c).

The schematic illustration of ATOP that we fabricated based on InGaZnO-SBD is shown in Fig. 3a with the current density–voltage (J-V) dependence on the thickness of each layer and the area of top electrode. The characteristics of the device according to the Schottky theory18 were determined from − 5 to + 0.5 V in both forward and reverse directions and were independent of the drift layer thickness and the electrode size. This ATOP exhibited a superior SBD performance with a rectification ratio of over 1014, a diode ideal factor (n) of approximately 1.1, and a Schottky barrier height (Vb) of 1.2 eV in the forward direction (Supplementary Table 1a). It should be noted that ATOP with 100 nm and 200 nm of d exhibited Ron,sp < 10–4 Ω cm2 (Fig. 3b), which is difficult to realize even with a single-crystal semiconductor PD5,19. In the reverse direction, on the other hand, a flat thermionic emission current characteristic20 was observed with less than 10–9 A cm−2 even under high electric fields before breakdown, which is also challenging even for a single-crystal SBD. The FOMs obtained for these ATOPs are comparable or even higher than theoretical values of single-crystal silicon5,19,21, as shown in Fig. 3b.

Forward and reverse diode characteristics of ATOP. (a) J–V characteristics of the ATOP with different drift layer thicknesses. The right and left sides show the forward and reverse characteristics with different scales in horizontal axes, respectively. The thicknesses and the sizes of Au/Mo top electrodes are indicated by different shapes and colours of each data point, respectively. The arrows indicate the breakdown voltage. (b) Breakdown voltage VBD and minimum specific on-resistance Ron,sp min were obtained from J–V characteristics in (a). Figures-of-Merit (FOM) of power devices were calculated from VBD and Ron,sp min. (c) Forward characteristic of 200 nm SBD. The circles and the dashed line show the experimental data and the result of numerical calculation, respectively. The numerical calculation was performed on the basis of the new model taking account of the initial free carrier concentration n0, using Eq. (28) in "Method" section and fitting parameters with Supplementary Table 1d. (d) Band diagrams for the forward characteristics in the 200 nm SBD. Left: Common Schottky operation at 0 V. Right: Dominant SCLC operation. The equivalent circuit at the top represents the Schottky-SCLC model with the diode component at the InGaZnO–PdO interface and variable resistance in the drift layer. (e) The calculated (C/A)−2 (the capacitance(C) divided by the electrode area(A))–voltage(V) plots of the ATOPs in (a). (f) Depth profile of electric fields distribution at the breakdown. (g) Breakdown mechanism by the local electrical field concentration at the interface of InGaZnO-PdO at the breakdown voltage of 200 nm SBD.

To clarify the performance limit of ATOP with respect to Ron,sp and VBD, we first focused on Ron,sp. For a typical single-crystal PD based on drift conduction, Ron,sp is given by d/μnq1, where μ, n and q correspond to mobility, carrier density and elementary charge, respectively. It is important to notice that ATOP has a low Ron,sp irrespective of the low μ (~ 10 cm2 V−1 s−1; ~ 1/100 compared to Si in Fig. 1c) of AOSs. Therefore, we constructed a forward conduction model through the ATOP in Fig. 3c and d. As shown in the inset of Fig. 3d, the resistance of an SBD can be regarded as consisting of the two components with the diode at the Schottky interface and the resistance of the drift layer1. Notably the latter component is more important for PD design because it is common for a wide range of semiconductor elements. We confirmed that the diode component obeys the relationship based on the common thermionic emission theory through a Schottky contact18 (Eq. 5 in "Method" section). As for the resistance of the drift layer, our new model (Eq. 28 in "Method" section) based on the space-charge limited current (SCLC) model22,23 with a modification to account for AOS characteristics was found to be applied. It should be noted that the resistance model for the drift layer is not based on conventional drift conduction with single-crystal semiconductors, but on the SCLC conduction, which is current behaviour for the injection of external carriers into substances with low carrier density such as insulators. In the case of ideal solid insulators, the current density is given by JSCLC, Std. = 9εμV2/8d3 where ε is a dielectric constant; JSCLC, Std. is inversely proportional to the cube of d and proportional to the square of the divided voltage V to the drift layer. The characteristics according to the model (Eqs. 5, 7, 28 in "Method" section) were experimentally confirmed in Fig. 3c and also for each temperature and thickness (Supplementary Fig. 3). Furthermore, in the region for applied voltage over 2 V, the resistance of the drift layer was confirmed to obey the ideal SCLC model of JSCLC, Std. (Supplementary Fig. 4a and b) described above. This behaviour can be ascribed to the reduced effect of trap levels24 in the band-gap occupied by electrons supplied from top electrodes (Supplementary Fig. 4c). Figure 3d shows the simplified band diagram in the forward direction of the InGaZnO-SBD for applied voltages of 0 V and 3 V. This diagram shows that the diode component is dominant up to the built-in voltage Vbi of ~ 1.2 V (Fig. 3d left panel) and the SCLC conduction in the drift layer becomes dominant for higher applied voltages (Fig. 3d right panel). Since the ideal SCLC takes place for the low resistance region for applied voltages higher than 2 V in the case of an ATOP (Supplementary Fig. 4d), the Ron,sp of ATOP can be approximated as follows:

Figure-of-merits (FOM) for PDs and the demonstration of flexible ATOP. (a) The relationship between breakdown voltage VBD and on-specific resistance Ron,sp. The circles and the stars correspond to the present results of the single- and double-layer diodes, respectively. The asterisk and cross grey marks are taken from the references to Si and GaN single-crystal semiconductors, respectively. ATOP limit obtained from Eq. (4) with the parameters in Supplementary Fig. 5a and V at 5 V. (b) Schematic images of flexible ATOP (c) Photograph of ATOPs on polyimide film. (d) Photograph of measured SBD on a flexible polyimide film with the optimized diode structure. e, J–V characteristics of SBD shown in (d).

This equation shows that small d with large V leads to low Ron,sp. In the case of ATOP, d is ~ 1/10 smaller than that of bulk single-crystal Si PD, achieving surprisingly low Ron,sp (< 10–4 Ω cm2) in spite of low μ (~ 1/100), as shown in Supplementary Fig. 5a.

As for the VBD that eliminates the effect of layer thickness, we focus on the breakdown electric field EBD, which is a normalized value of VBD divided by d. We found that the EBD of all the devices we fabricated exhibited around 1 MVcm−1 (Supplementary Fig. 6, Supplementary Table 1a). While this value is already higher than that of single-crystal Si (~ 0.3 MVcm−1)5, it is still lower than the expected value of approximately 3 MVcm−1 based on the critical breakdown field EC25—intrinsic breakdown field determined by the properties of materials—estimated by the band-gap of InGaZnO, 3.2–3.3 eV (Supplementary Fig. 2f, Supplementary Table 1b). According to the capacitance–voltage (C-V) measurements and the depth profile of electric fields distribution in Fig. 3e and f (through Supplementary Fig. 7), respectively, it was confirmed that the local electric field concentrating at the PdO–InGaZnO interface (Fig. 3g) caused the breakdown with such a low electric field. It should be noted that the high electric field of 2.9–3.8 MV cm−1 in Fig. 3f, comparable to the estimated EC values, was induced within 1 nm of the interface, resulting in the breakdown of the ATOPs. To achieve higher EBD, an amorphous gallium-oxide (Ga2O3) layer having a wider band gap of 4.4 eV (Supplementary Fig. 1c and d, Supplementary Table 1b) was inserted between the PdO and InGaZnO layers. As the results shown in Supplementary Fig. 1c, the EBD (~ 1.8 MVcm−1) was improved to double that of a single PdO layer without sacrificing Ron,sp. This result demonstrates that EBD can be improved close to EC by optimizing the interface, showing that VBD can be designed by the following Eq. (3) for ideal ATOP (Supplementary Fig. 5c):

Accordingly, the FOM of ATOP can be described by the materials parameters as follows:

Methods

Device fabrication

Heavily doped n++ silicon (phosphorus doped, 1 mΩ cm, 300 μm thick, Okmetic) was used as the substrate for the Schottky barrier diodes (SBDs). First, a 150 nm titanium (Ti) film was deposited on the backside of the silicon substrate by DC magnetron sputtering in argon (Ar) atmosphere at 0.5 Pa, as a backside electrode. Next, a 10 nm Ti and a 50 nm palladium (Pd) were deposited on the surface of the substrate under the same sputtering condition as both an adhesion layer and a contact resistance reducing layer. A 40 nm palladium-oxide (PdO) layer, which works as a Schottky electrode, was then deposited by DC magnetron sputtering in oxygen (O2) atmosphere at 0.5 Pa. On the PdO layer, thin amorphous indium–gallium–zinc–oxide (InGaZnO) films with different thicknesses (i.e. 100 nm, 200 nm, 500 nm, and 1000 nm) were formed by DC magnetron sputtering of a InGaZnO ceramic target. During the sputtering, a 1% water vapour content (H2O/Ar + H2O) was introduced under the conditions of 0.5 Pa at room temperature. To form an amorphous gallium-oxide (Ga2O3) layer, Ga2O3 target was sputtered under the condition of 0.5 Pa and 1% partial pressure of O2. All samples were then annealed at 300 °C for 1 h in an air atmosphere. Finally, 150 nm Mo/ 500 nm gold (Au) was deposited as a top electrode by photolithography. We used different diameters of the electrodes ranging from 50 to 500 µm. To create a flexible device, ~ 10 μm polyimide film was spin-coated on a carrier glass wafer. Then, Mo/Pd layer was deposited as a bottom electrode. For the subsequent processes, the same processes described above were applied. Finally, flexible ATOP with 200 nm InGaZnO is realized by peeling off the polyimide film from the carrier wafer.

Device evaluation

The current density–voltage (J–V) characteristics of the diodes were measured with a semiconductor parameter analyser (Agilent B1500 A). Current can be measured over a wide range (from 10–15 to 1 A) owing to the several types of equipped SMUs (Source/Measure Unit) and ASU (atto-sense and switch unit). Capacitance–voltage (C–V) measurements were performed with an Agilent E4980A LCR meter under a frequency condition at 1 kHz. In both the J–V measurements and the C–V measurements including temperature dependence, the Ti backside electrode (the anodic electrode) was connected to the stage. Here, a Kelvin (4 probes/wire) connection was used to minimize the measurement error caused by parasitic resistance, that is the residual resistance of the connection cable and contact between the probe and electrode. For voltage measurement and applied current, the two cathodic probes were connected to the top Au electrode of the device, while the two anode cables were connected to the stage. All measurements were performed in a black box with a semi-automatic probe station (Cascade Microtech PA200).

Diode analysis

Forward characteristics

Current density J was defined as the current divided by the area of the top electrode. Basic transport properties of a Schottky junction are described by the following equations:

where VSchottky is the voltage applied to the Schottky interface, n is the ideality factor (n = 1 is the ideal value), ΦB is the height of the Schottky barrier, k is the Boltzmann constant, q is the elementary charge, T is absolute temperature and V is the applied voltage to the device. Equation (6) shows the saturation current density J0 and is equivalent to the intercept of lnJ in (5)18. Equation (7) shows the relationship between VSchottky, V and Vdrift (Vdrift is the voltage distributed to the semiconductor drift layer)1,26. Equations (8) and (9) are derived from Eqs. (6) and (5), respectively. A** is the effective Richardson constant; the theoretical value for InGaZnO is 41 A cm−2 K−2 (calculated from m* = 0.34 me)27. In this paper, ΦB and n were calculated for T = 298 K and A** = 42 A cm−2 K−2. ΦB and A** were evaluated by the Richardson plot (Supplementary Fig. 8b). As shown in Eq. (10), the mean barrier height ΦB.M, which is independent of A** and T, is obtained by plotting J0 against temperature T. Experimental results obtained with the 200 nm InGaZnO SBD was analysed according to Eq. (10), resulting in A** = 42 Acm−2 K−2 and ΦB.M = ΦB.

Reverse characteristics

Breakdown voltage VBD is defined as the highest voltage that is recorded just before a current continuously exceeds 1 μA for more than three measurement points. In this study, it was found that the depletion width WD is approximately the same as the film thickness d of the oxide semiconductor when a reverse voltage (negative bias) is applied (Supplementary Fig. 7a, Supplementary Table 1c). Therefore, it is reasonable to assume that the electric field is homogeneously distributed in the semiconductor drift layer. The breakdown strength EBD was defined as the breakdown voltage VBD divided by the film thickness d as the following form:

CV measurements

From the measured capacitance of the diode C, the depletion width WD at different voltages, the built-in voltage Vbi, and the charge density which contributes to the depletion layer Ndelp, were obtained according to the following equations18:

where εr is the static dielectric constant of the semiconductor, ε0 is the dielectric constant of a vacuum and A is the active area of the SBD. The Schottky barrier height ΦB,CV can be calculated from the result of C–V measurements according to the following equation:

where NC is the effective density of state in the conduction band. In the case of InGaZnO, NC is 5.2 × 1018 cm−3 28. Ne is the free charge density, which can be experimentally obtained by Hall measurements.

Power law

The forward J–V characteristics can be described as the following equation:

where K is a constant and m is the power law index. By differentiating the logarithm of both sides of Eq. (15), m is obtained the following equation:

Thus, m depends on V in the SCLC conduction according to the J–V relationship described as Eqs. (17) and (18). Based on this Eq. (16), we discussed various conduction models [Eqs. (17), (18), and (28)] and the drift model (Johmic = μnq V/d) in Supplementary Fig. 4b.

Existing SCLC model

The space charge limited current (SCLC) between two terminals forming Ohmic contacts can be explained by the Child’s law for solids. In the simplest standard model, the relationship between current density JSCLC,Std and applied voltage V can be given as the following equation22:

where ε is the permittivity of the semiconductor, μ is the carrier mobility and d is the film thickness. When the carriers are affected by exponentially distributed traps (EDTs), the current changes according to the filling of traps below the quasi-Fermi level. Assuming the traps with an exponential energy distribution in the bandgap, the current JSCLC,EDT can be described by the following equation23:

where Nc is the effective density of states, Nt is the total number of traps per unit volume. l is defined as l = Tt/T, where Tt is the characteristic temperature which determines the trap distribution. The validity of this model is supported by the result of deep-level transient spectroscopy (DLTS), which shows the distribution of the subgap states in the amorphous oxide semiconductor24. However, the effect of the free carrier concentration at the steady state was not considered in this model. Based on our model validation results, Eq. (18) needs to be modified so as to include the effect of initial free carrier concentration. Therefore, referring to Reference29, we expanded (18) to include the effect of the initial free carrier concentration.

New SCLC model

We modified Eq. (18) so as to include the effect of initial free carrier concentration n0. According to the reference29, the current considering JSCLC,EDT,n0 can be described as follows:

where n(x) is the the carrier concentration contributing to conduction (x = 0 is the edge of the top electrode), ni,f(x) is the concentration of untrapped injected free carriers, ni,t(x) is the concentration of trapped injected carriers, and ninj(x) is the total concentration of injected carriers. Equations (19) and (20) show the drift current and Poisson’s equation, respectively. Equation (28) can be derived from Eqs. (19) and (20). Equations (21) and (22) show the boundary conditions. The diffusion current is not considered as its effect can be negligible in the present current region.

First, the exponential trap distribution nt(ε) is defined by the following equation:

where ε is the energy level of the trap states.

Using the Fermi–Dirac distribution as a step function, ni,t(x) can be written as shown in the following equation:

where F0 is the Fermi level in thermal equilibrium. As the quasi-Fermi level F(x) shows the depth dependence, the concentration of trapped injected electrons at a position x can be estimated from Eq. (24). Since the concentration of the injected electrons is high near the cathode, the position of the quasi-Fermi level is also relatively closer to the conduction band in that region. To connect ni,t(x) with the concentration of total electrons that contribute to conduction, we rearrange Eq. (24) by using the Boltzmann’s distribution law:

Equation (25) shows the trap distribution including the effect of the initial free carrier concentration. Based on Eq. (25) and the Poisson’s Eq. (20), the following equation can be derived:

From Eqs. (19), (26) can be written as

By integrating Eq. (27), the voltage applied to the drift layer VSCLC can be obtained, which represents a new SCLC model considering the effect of the initial free carrier concentration.

To determine Ed (a numerically calculated value), the boundary condition is written as follows:

Here, E(0) is set at 0. Note that Eqs. (28) and (29) must be calculated under the following conditions: JSCLC,EDT,n0 , VSCLC ≥ 0 and E(x), Ed ≥ 0. By using (28), it becomes possible to discuss the mechanism of EDT-type SCLC conduction, in which the concentration of free carriers at the steady state is considered.

To explain the experimentally-obtained J–V characteristics, we performed numerical calculations as the current density components of Eqs. (5) and (28) coincide with an intervening variable parameter of VSCLC. In the new SCLC model described as Eq. (28), we treated JSCLC,EDT,n0 as an arbitrary input parameter. μ and n0 are obtained through the Hall measurement. Tt and Nt are fitting parameters to obtain VSCLC. The sample temperature was used for T, and ε was set at the converted value in the case of εr = 16 (determined from the C-V measurements). By verifying J in Eq. (5) corresponding to the arbitrary JSCLC,EDT,n0 in Eq. (28), comparison between the experimental results and the numerical calculation results can be possible. As J and JSCLC,EDT,n0 should be the same value for the series circuit model as shown is Fig. 3d, Vdrift in Eq. (7) can be replaced by VSCLC in Eq. (28). Based on the results of the temperature dependence (Supplementary Fig. 8), ΦB and n in Eq. (5) are determined from Eqs. (8) and (9), respectively. Then, we can obtain J from Eq. (5) through VSchottky as V – VSCLC. In the case of J = JSCLC,EDT,n0, the fitting parameter of Tt and Nt are correct.

Estimation of E c

The critical breakdown field Ec (the maximum electric field at the Schottky interface when the breakdown voltage VBD is applied) can be estimated according to the relationship between the depletion layer width WD and the charge concentration contributing to the depletion layer Ndepl as shown in Eqs. (12) and (13). The calculations were performed with a model that considers the charge density distribution of a one-sided abrupt junction30. We assumed that the effect of minority carriers on the space charge formation is negligible. By using the depth profile of Ndepl obtained from the C–V measurements, the field distribution in the film thickness direction can be calculated by the following equation:

As the reverse current is almost 0, Eq. (30) can be written as the following form:

By integrating Eq. (31), V can be described as

where E(x) is the electric field intensity at a position x, and E(0) is the electric field at the Schottky interface. WDcan be approximated to d as the depletion layer is formed through the whole diode even at 0 V. From the definition of Ec, E(0) can be replaced by Ec when the breakdown voltage VBD is applied. Then, Eq. (32) can be written as the following form:

Ec can be estimated from Eq. (33) by using the profiling of E as described in Eq. (31). VBD and the Ndepl profile for WD can be experimentally obtained from the J–V characteristics and the results of the C–V measurements. The resolution of this technique depends on the Debye screening length; that is, the length by the influence of the impurity concentration in the semiconductor. Thus, the resolution is better than 1 nm for Ndepl > 1019 cm−3 at the Schottky interface31,32.

Characterization of thin film

Cross-sectional observation of the SBDs by transmission electron microscopy (TEM) was performed with a focused-ion-beam device (FB-2100, Hitachi) and TEM (JEM-2800, JEOL). TEM observations were performed at an accelerating voltage of 200 keV. X-ray diffraction (XRD) was performed with a Rigaku SmartLab system under a condition of 40 kV and 40 mA by using the Cu–Kα line (l.5406 Å). The same XRD system was also used to evaluate the crystallinity of the thin films: the grazing incident X-ray diffraction (GIXD, angle of incidence ω) and the conventional θ − 2θ scan (XRD). The thin film samples were deposited on a quartz glass substrate for the XRD measurements and annealed at 300 °C for 1 h before the measurement. The GIXD measurement was performed for a multilayer sample of PdO thin films to avoid the change in crystallinity by annealing on a different substrate. This analysis was also done in the multilayer condition of the actual diode structure to avoid transformation of the polycrystalline structure of the PdO during annealing on a different substrate.

To estimate the bandgap Eg, UV–VIS spectroscopy (V-370, JASCO) was performed for the thin film samples deposited on quartz glass substrates. The samples were annealed before the measurement. The work function ΦWF was determined by using ultraviolet photoelectron spectroscopy (UPS) by focusing on the secondary electron cutoff. Monolayer thin films deposited on a Si substrate were used as samples. In the UPS measurements, monochromatized 7.7 eV photons from a D2 lamp were used, and a negative bias of 10 V was applied to the sample. A customized system equipped with a zero-dispersion type double monochromator and a 120 mm hemispherical analyser (PSP Vacuum Technology RESOLVE120) was used for the measurement.

Hall mobility μHall, the free electron carrier concentration nHall and the specific electrical resistance ρ were obtained with a Hall measurement system (ResiTest 8400, TOYO Corporation) by using an AC magnetic field. The measurements were performed with the Van der Pauw method at room temperature. Thin films deposited on quartz glass substrates (10 mm × 10 mm) were used as samples. The samples were annealed before the measurement, and indium electrodes were deposited on the 4 corners of the samples.

Conclusions

The properties of the ATOPs fabricated in this study are summarized in Fig. 4a, comparing with conventional PDs. The theoretical limit of single-crystal Si can be estimated by \({\text{FOM}} = \varepsilon \mu E_{c}^{3} /4\) through materials parameters1,4. For the ATOP, on the other hand, a superior performance to single-crystal Si was confirmed for both experimental values and the theoretical limit estimated by Eq. (4). It is worth noting that the ATOP exhibits higher performance than GaN transistors33, which have the advantage in lowering resistance, in the region with VBD < 100 V and Ron,sp < 10–4 Ω cm2. This ultra-low resistance is one of the advantages of ATOP, which has almost no restriction on the type of substrate and is not significantly affected by the contact resistance unlike that of the conventional PDs. Finally, we demonstrated the fabrication of devices on a flexible polyimide film (Fig. 4b–e), making most of the characteristics of ATOP that enables low temperature (≤ 300 °C) sputtering on any type of substrate. ATOP has the potential to replace conventional bulk single-crystal PDs, thereby expanding the applications of PDs into new areas, where bulk single-crystal is intrinsically unable to reach.

References

Baliga, J. Fundamentals of Power Semiconductor Devices (Springer, 2008).

Jeon, S. et al. High performance bilayer oxide transistor for gate driver circuitry implemented on power electronic devices. Symp. VLSI Technol. Dig. 2012, 125–126 (2012).

Shenai, K. Switching MegaWatts with power transistors. J. Electrochem. Soc. 22, 47–53 (2013).

Kondrath, N. & Kazimierczuk, M. K. Characteristics and applications of silicon carbide power devices in power electronics. INTL J. Electron. Telecommun. 56, 231–236 (2010).

Okumura, H. Present status and future prospect of widegap semiconductor high-power devices. Jpn. J. Appl. Phys. 45, 7565–7586 (2006).

Momma, K. & Izumi, F. VESTA 3 for three-dimensional visualization of crystal, volumetric and morphology data. J. Appl. Crystallogr. A 44, 1272 (2011).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Kamiya, T., Nomura, K. & Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 11, 044305 (2010).

Lee, M. J. et al. 2-stack 1D-1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications, in Proceedings of the IEEE International Electron Devices Meeting, 771–777 (2007)

Lee, D. H., Nomura, K., Kamiya, T. & Hosono, H. Diffusion-limited a-IGZO/Pt Schottky junction fabricated at 200 °C on a flexible substrate. IEEE Elec. Dev. Lett. 32, 1695–1697 (2011).

Chasin, A. et al. High-performance a-IGZO thin film diode as selector for cross-point memory application. IEEE Electron Device Lett. 35, 642–644 (2014).

Zhang, J. et al. Flexible indium–gallium–zinc–oxide Schottky diode operating beyond 2.45 GHz. Nat. Commun. 6, 7561–7567 (2015).

Chasin, A. et al. High-performance a-In–Ga–Zn–O Schottky diode with oxygen-treated metal contacts. Appl. Phys. Lett. 101, 113505 (2012).

Xin, Q. H., Yan, L., Luo, Y. & Song, A. Study of breakdown voltage of indium–gallium–zinc–oxide-based Schottky diode. Appl. Phys. Lett. 106, 113506 (2015).

Nomura, K., Kamiya, T. & Hosono, H. Effects of diffusion of hydrogen and oxygen on electrical properties of amorphous oxide semiconductor, In–Ga–Zn–O. ECS J. Solid State Sci. Technol. 2, P5–P8 (2013).

Léonard, F. & Tersoff, J. Role of fermi-level pinning in nanotube Schottky diodes. Phys. Rev. Lett. 84, 4693–4697 (2000).

Brillson, L. J. & Lu, Y. ZnO Schottky barriers and Ohmic contacts. J. Appl. Phys. 109, 121301 (2011).

Rhoderick, E. H. & Williams, R. H. Metal-Semiconductor Contacts 2nd edn. (Clarendon, 1988).

Wang, Z., Zhang, B., Fu, Q., Xie, G. & Li, Z. An L-shaped trench SOI-LDMOS with verticaland lateral dielectric field enhancement. IEEE Elec. Dev. Lett. 33, 703–705 (2012).

Hatakeyama, T. & Shinohe, T. Reverse characteristics of a 4H–SiC Schottky barrier diode. Mater. Sci. Forum 389–393, 1169–1172 (2002).

Shenai, K. Optimally scaled low-voltage vertical power MOSFET’s for high-frequency power conversion. IEEE Transact. Elec. Dev. 37, 1141–1153 (1990).

Lampert, M. A. & Mark, P. Current Injection in Solids (Academic, 1970).

Mark, P. & Helfrich, W. Space-charge-limited currents in organic crystals. J. Appl. Phys. 33, 205–215 (1962).

Chasin, A. et al. Deep-level transient spectroscopy on an amorphous InGaZnO4 Schottky diode. Appl. Phys. Lett. 104, 082112 (2014).

Higashiwaki, M., Sasaki, K., Kuramata, A., Masui, T. & Yamakoshi, S. Gallium oxide (Ga2O3) metal-semiconductor field-effect transistors on single-crystal β-Ga2O3 (010) substrates. Appl. Phys. Lett. 100, 013504 (2012).

Cibils, R. M. & Buitrago, R. H. Forward I–V plot for nonideal Schottky diodes with high series resistance. J. Appl. Phys. 58, 1075–1077 (1985).

Takagi, A. et al. Carrier transport and electronic structure in amorphous oxide semiconductor, a-InGaZnO4. Thin Solid Films 486, 38–41 (2005).

Kamiya, T., Nomura, K. & Hosono, H. Origins of high mobility and low operation voltage of amorphous oxide TFTs: electronic structure, electron transport, defects and doping. J. Disp. Technol. 5, 273–288 (2009).

Chen, C. W. & Wu, C. I. Analytical solution to space charge limited currents with exponentially distributed traps. J. Appl. Phys. 104, 123706 (2008).

Glover, G. H. & Tantraporn, W. Doping profile measurements from avalanche space−charge resistance: a new technique. J. Appl. Phys. 46, 867–874 (1975).

Kennedy, D. P., Murley, P. C. & Kleinfelder, W. On the measurement of impurity atom distributions in silicon by the differential capacitance technique. IBM J. Res. Dev. 12, 399–409 (1968).

Schubert, E. F. et al. Spatial resolution of the capacitance-voltage profiling technique on semiconductors with quantum confinement. Appl. Phys. Lett. 57, 497–499 (1990).

Roccaforte, F. Challenges for energy efficient wide band gap semiconductor power devices. Phys. Status Solidi A 211, 2063–2071 (2014).

Acknowledgements

We are grateful to N. Iwamuro, H. Tadano, H. Yano, R. Hasunuma and K. Yamabe (University of Tsukuba) for discussions about electrical characterization for power devices. We thank H. Tokairin, S. Ishii, A. Yao, Y. Harada and H. Kondo (Idemitsu Kosan Co., Ltd) for technical support of thin-film analysis and fabrication of flexible device. We acknowledge A. Sandhu (The University of Electro-Communications) for helping with writing.

Author information

Authors and Affiliations

Contributions

Y.T. conceived the idea for the study. E.K. designed the project. Y.T., E.K., and T.S. designed experiments and performed measurements. Y.N. prepared the samples by photolithography. Y.T. performed data analysis and developed the model. Y.T. wrote the first draft of the manuscript. Y.T. and E.K. drew the figures. T.S., G.I and G.Y. provided major revisions and verified the model. All authors read and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tsuruma, Y., Kawashima, E., Nagasaki, Y. et al. Amorphous thin-film oxide power devices operating beyond bulk single-crystal silicon limit. Sci Rep 11, 9435 (2021). https://doi.org/10.1038/s41598-021-88222-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-88222-7

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.