Abstract

Two-dimensional (2D) semiconductors, such as transition metal dichalcogenides (TMDs) and black phosphorus, are the most promising channel materials for future electronics because of their unique electrical properties. Even though a number of 2D-materials-based logic devices have been demonstrated to date, most of them are a combination of more than two unit devices. If logic devices can be realized in a single channel, it would be advantageous for higher integration and functionality. In this study we report high-performance van der Waals heterostructure (vdW) ReS2 transistors with graphene electrodes on atomically flat hBN, and demonstrate a NAND gate comprising a single ReS2 transistor with split gates. Highly sensitive electrostatic doping of ReS2 enables fabrication of gate-tunable NAND logic gates, which cannot be achieved in bulk semiconductor materials because of the absence of gate tunability. The vdW heterostructure NAND gate comprising a single transistor paves a novel way to realize “all-2D” circuitry for flexible and transparent electronic applications.

Similar content being viewed by others

Introduction

Ultrathin two-dimensional (2D) semiconducting materials are useful for a number of electronic applications because of their unique properties originating from their atomically thin nature1,2,3,4,5. Among them, transition metal dichalcogenides (TMDs) have been actively studied as channel materials because of absence of short-channel effect6,7. It has been anticipated that a scale-down limit can be overcome by 2D semiconductors for higher integration of electronic devices. In this regard, “all-2D” devices comprising only 2D materials, i.e., van der Waals heterostructure (vdW) devices, have been demonstrated8,9,10,11. As emerging 2D materials, rhenium-based TMDs, such as ReS2 or ReSe2, have exhibited promising properties. Typically, few-layer TMDs outperform monolayer in terms of carrier mobility, while the band structure of TMDs transforms from direct to indirect band structure as the thickness changes from monolayer to few-layers, which limits their use for optoelectronic applications12. However, ReS2 and ReSe2 exhibit direct band structure at all thickness because of the distorted 1 T’ structure and weak interlayer coupling13. Despite the unique properties of ReS2 and ReSe2, there have been only limited studies on them, which reported preliminary results of transistors and photodetectors based on ReS2 and ReSe2 with conventional device geometry14,15,16,17,18,19.

To improve the device performance of 2D semiconductors, contact resistance and carrier scattering should be reduced. Significant contact resistance between deposited metal and 2D semiconducting channels severely deteriorates device performance due to the Fermi level pinning at the interface20, which makes it difficult to utilize the 2D semiconductors for practical applications required by the industry. In addition, because the band gap of TMDs increases with decreasing thickness, the Schottky barrier height for monolayer TMDs is significantly higher than that for few-layer TMDs, leading to a lower field-effect mobility21,22. The use of graphene electrodes has been considered as a solution because of the de-pinning of the graphene Fermi level and absence of chemical bonds at a stacked heterointerface of 2D layers23. In addition, it has been shown that hexagonal boron nitride (hBN), used as an ultraflat dielectric, suppresses charged impurity scattering, resulting in enhanced carrier mobility of hBN-encapsulated 2D materials9,11,24.

A number of logic devices based on 2D materials have been demonstrated by combinations of two different 2D transistors: n-type and p-type5,25,26,27,28. Even though the NMOS inverters using ReS2 have been demonstrated19,27, all of the logic devices reported so far are made of double devices (two connected devices). Therefore, for higher integration and functionality, a novel device geometry is required for logic devices. Because atomically thin 2D materials are highly sensitive to electric fields with no screening effect, it is possible to locally tune the densities and types of carriers, leading to electrically controlled p-n junction devices comprising graphene or WSe229,30,31,32,33. Therefore, by locally tuning the Fermi level of a 2D channel, a multi-functional logic device can be realized in one 2D channel.

Here we report a NAND gate based on a single ReS2 channel with a graphene split gate. We first demonstrate ReS2 field-effect transistors (FETs) on an hBN substrate with graphene electrodes. The field-effect mobility (μFE) of an n-type ReS2 FET is 35 cm2/V·s and the on/off ratio is as high as 106 at room temperature. When the graphene split gate is used to locally modulate the channel, two regions, separately tuned by the split gates, act as independent transistors, which can be used as a gate-tunable NAND logic gate.

Results

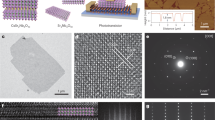

For “all-2D” devices, a vdW heterostructure of ReS2, graphene, and hBN was fabricated by stacking the exfoliated nanosheets, as shown in Fig. 1. The 2D nanosheets were exfoliated directly onto a polydimethylsiloxane (PDMS) stamp and transferred onto another flake on the SiO2 substrate22. The ReS2 channel was placed on the hBN to reduce scattering from charged impurities of the substrate and interfacial impurities. As ReS2 has a smaller effective mass along the a-axis, it has anisotropy in conductance, leading to higher carrier mobility along the a-axis27. Therefore, the ReS2 flake, which has an elongated shape along the a-axis, was chosen as a channel. Graphene was used as an electrode to lower the Schottky barrier. Two pieces of graphene were placed on the ends of the ReS2 channel to form source and drain electrodes. After stacking, e-beam lithography and metal deposition (1 nm Cr/50 nm Au) were used to define the metal electrodes. Figure 2(a,b) show the schematic and optical microscopic (OM) images of the fabricated device.

PDMS stacking process for fabrication of vdW heterostructure. The flake exfoliated directly on PDMS is aligned with a target flake on the SiO2 substrate. The PDMS stamp is smoothly lowered for conformal contact onto the bottom target flake on the substrate. The lift-up process follows after five minutes.

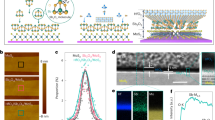

The electrical performance of the tri-layer ReS2 FET on the hBN substrate with graphene electrodes is shown in Fig. 3. The few-layer graphene (>10 L) and thick hBN of 6.4 nm were used in the device. The output curves (IDS − VDS) at different back gate voltages (VBG) clearly exhibit a gate-dependent linearity, as shown in Fig. 3(a). The linear output curves at small gate voltages indicate that the ReS2-graphene interface forms Ohmic contact even at low carrier concentrations. As shown in the transfer curves (IDS − VBG) in Fig. 3(b), ReS2 exhibits n-type transport as typically observed in MoS2 or WS234. Because of the low contact resistance and reduced carrier scattering in the vdW heterostructure device, higher mobility (μFE = 35 cm2/V·s) and a high on-off ratio (~106) were extracted, compared with the same ReS2 FET with metal electrodes on a SiO2/Si substrate (Fig. S1). It should be noted that the field-effect mobility of a vdW heterostructure device of ReS2 is significantly greater than previously reported values (<10 cm2/V·s) of ReS2 devices with metal or graphene electrodes and SiO2 dielectric14,15,16,17,18,19. We also fabricated ReSe2 devices using the same procedure and device structure. As ReSe2 exhibits a smaller mobility of 6.6 cm2/V·s than ReS2, ReS2 was used for the logic device. (Fig. S2)

Electrical characteristics of tri-layer ReS2 FET. (a) Output curves (IDS − VDS) of device. Linearity of output curves at all gate voltages indicates that graphene-ReS2 junction is Ohmic contact. (b) Transfer curves (IDS − VBG) plotted in semi-log scale (red) and linear scale (blue). The ReS2 FET exhibits high field effect mobility of 35 cm2/V·s and on-off ratio of 106.

We modified the previous device structure to demonstrate the logic devices comprising a single 2D channel. To locally tune the ReS2 channel, graphene was inserted between the bottom hBN and SiO2 and patterned into split gates separated by a nanogap, as shown in Fig. 4(a). (See Fig. S3 for detail of the fabrication.) After exfoliation of the graphene on the SiO2 substrate, e-beam lithography is performed to define a nanogap on the graphene, followed by reactive-ion etching (RIE) etching for cutting. The patterned graphene split gates are annealed at 350 °C for 4 hrs in forming gas (5% H2 in Ar) to remove residue. After cleaning, other 2D flakes of hBN dielectric, ReS2 channel, and graphene electrodes were sequentially transferred by the PDMS stamping technique as described in Fig. 1. After stacking, e-beam lithography and metal deposition were conducted to form metal contacts to the source, drain, and gate graphene electrodes. The OM image in Fig. 4(b) shows the fabricated tri-layer ReS2 device with graphene split gates.

When different voltages are applied separately to the two graphene split gates (VGG1 and VGG2), the corresponding band alignments are shown in Fig. 5(a). When both gate voltages of VGG1 and VGG2 are higher than the threshold voltage (Vth), the whole channel region is conductive and the Schottky barrier is lowered because of the simultaneous up-shift of the graphene Fermi level, which results in n-type conductance of the device. When the VGG1 is higher than the threshold voltage and VGG2 is smaller, carrier transport through the ReS2 channel is blocked because of the depletion of the negatively gated ReS2 region, while the Schottky barrier is still small, resulting in carrier injection of the positively gated channel (middle of Fig. 5(a)). When both gate voltages are within the off-state, carrier transport is impossible due to depletion of the channel and higher contact barrier, resulting in a significantly low off-current level. Figure 5(b) shows the transfer curves (IDS − VGG1) of the ReS2 device with graphene split gates when VGG1 is varying while VGG2 is fixed. The transfer curves are plotted on a semi-log scale in Fig. 5(c). In the device, hBN was used as an ultrathin and ultraflat dielectric in the device geometry, which is appropriate for “all-2D” devices. A small operating voltage (VBG < 3 V) and low subthreshold swing (SS) of <300 mV/dec were obtained, which were an order of magnitude smaller in the ReS2 device on the 300 nm-thick SiO2 substrate which is calculated from the device described in Figs 2, 3. In the on-state (VGG1 > −1.5 V), conductance of the whole channel increases with increasing VGG1. However, in the off-state (VGG1 < −1.5 V), the off-current remains at a low level of 10−12 A at different VGG1 because the region where VGG1 is applied is completely off. Therefore, the on-current can be strongly modulated by VGG1 and VGG2. The on-off ratio modulation ranges from 102 to 106, which is beneficial for multifunctional applications (more clearly observed in the semi-log scale plot of Fig. 5(c)). Regardless of a gap (~200 nm), it is validated that the device operates reliably without significant deterioration of the performance, which have been also verified in previous reports29,32.

Band diagram and electrical modulation characteristics of the device. (a) Band alignment under various combinations of different gate voltages by split gates. When both gates are on (VGG1 and VGG1 > Vth), charge carriers transport through ReS2 channel (left). If one of split gates is off (VGG1 > Vth and VGG1 < Vth), half of channel is depleted and charge carriers do not transport (middle). When both gates are off (VGG1 and VGG1 < Vth), charge carriers cannot be injected from graphene and transport through channel (right). (b,c) Transfer curves (IDS − VGG1) of the ReS2 FET at varying VGG2 and fixed VGG1 in linear scale (b) and semi-log scale (c).

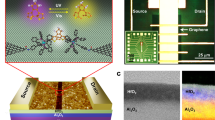

The logic device characteristics of the ReS2 device with graphene split gates was measured, as shown in Fig. 6. As can be seen in the circuit diagram of Fig. 6(a), two graphene split gates are used as input signal gates. An external load of 100 MΩ, the middle off and on resistances value of the device, was used. Input terminals 1 (in1) and 2 (in2) were set as the GG1 and GG2, respectively. Because of high modulation ability, one half of the channel (controlled by one of split gates) operates as an independent inverter. The voltage transfer curves (VTCs) of Fig. 6(a) show the inverter characteristics. When Vin1 varies with a fixed Vin2, it can be clearly seen that the output signals are inverted, indicating that only half of the channel plays a role as an inverter. However, when the current is totally blocked by depletion of the half of the channel modulated by Vin2, there is no inversion of the output signal. This means that the output signals can be effectively controlled by two input signals from the graphene split gates. The calculated gain values of the ReS2 inverter, defined as dVout/dVin, are shown in Fig. 6(b). Even though the gain value is relatively lower than those of previously reported 2D-materials-based inverters comprising two n-type and p-type transistors (similar to complementary metal oxide semiconductor (CMOS)), it is comparable to the gain values of unipolar-type inverters5,27,35,36. In addition, the supply voltage (VDD) used in this study is 1 V and the dielectric constant (εr = 3–4) of hBN is relatively small compared to previous studies37,38. Therefore, the gain can be further enhanced by increasing VDD as shown in the inset in Fig. 6(c). In this study, VDD was set as 1 V because the VTC exhibits a mirror reflection and a gain larger than 1 (unity gain), as shown in Fig. 6(c), compared to lower or higher VDD.

Logic device characteristics of ReS2 FET with graphene split gates. (a) Voltage transfer curves (VTCs) of GG1 region (Vout − Vin1) at VDD = 1 and varying Vin2. Inset shows circuit diagram of logic device. External load is 100 MΩ. At Vin2 > 1 V, VTC exhibits mirror symmetry. (b) Gain extracted by VTC as function of Vin2. Maximum gain is 1.6 at Vin2 = −3 V. (c) VTC at varying VDD and fixed Vin2 of 3 V. The inset shows gain extracted from VTC. (d) Time domain plot of output voltage for NAND logic gates.

To utilize ReS2 devices as NAND logic devices, output voltages were measured under different combinations of input states, as shown in Fig. 6(d). Because the output voltage is linked to the VDD, a logic state of 1 can be realized when either Vin1 or Vin2 is −3 V (defined as an input logic state of 0). For Vout of state 0, positive input voltage of 3 V was applied to both graphene split gates of GG1 and GG2. If a gate voltage smaller than −1.5 V is applied to one of the two gates, the whole device is non-conducting. Therefore, ReS2 devices with graphene split gates can be used as a NAND gate, one of the universal logic gates. It should be noted that a NAND gate was fabricated on a single 2D channel material, which is distinct from other reports using two transistors regardless of the carrier type. Output voltages measured at different combinations of the two input signals are shown in Fig. 6(d). This indicates that a single channel ReS2 device with graphene split gates operates well as a NAND gate. Unlike bulk materials, gate tunability of 2D semiconducting materials enables independent control of the separated channel regions by split gates. Therefore, NAND logic device can be fabricated within single 2D channel, which is clearly different from conventional logic gates that require more than two separate transistors.

Discussion

In conclusion, we fabricated high performance ReS2 transistors by using graphene and hBN as electrode and dielectric, respectively. The high field effect mobility of 35 cm2/V·s and high on-off ratio of 106 were obtained by suppression of Fermi level pinning at the graphene-ReS2 junction and reduction of charged impurity scattering. For the “all-2D” integration, we also fabricated ReS2 devices with graphene split gates for logic devices. The graphene split gates and bottom hBN enables us to locally and effectively modulate channel regions. By independently changing gate voltages from the two split gates, the device conductance can be controlled with a higher degree of freedom: the whole device is turned off by applying a negative voltage to only one gate, while a positive gate voltage is applied to both split gates to turn-on the device. By utilizing local tunability of the channel by split gates, it was shown that the ReS2 device with graphene split gates can be used as an efficient NAND gate, which is one of the most essential elements in integrated circuits. The vdW heterostructure NAND gate comprising a single transistor fabricated in this work provides a further step toward realization of “all-2D” circuitry for flexible and transparent electronic applications.

Methods

Device fabrication

PDMS transfer First, the PDMS base (Sylgard 184) was cured with 10 wt% of curing agent at 120 °C for 2 h. We then mechanically exfoliated hBN, which is the bottom of the heterostructure on SiO2/Si chips, and exfoliated other 2D materials, such as graphene and ReS2, separately onto each cured PDMS flake on glass slides. After careful alignment with a micromanipulator in the transfer stage, the PDMS with 2D materials were attached and detached, as carefully and slowly as possible, at room temperature.

E-beam lithography

To pattern metal electrodes on the as-stacked heterostructure or gap on the graphene for the split gate, we performed e-beam lithography with a Raith Pioneer 2 nanolithography system.

Metal deposition

We deposited metal electrodes (Cr 1 nm/Au 50 nm or Cr 1 nm/ Pd 20 nm/Au 30 nm) with an e-beam evaporator (Korea Vacuum Tech.) in a high vacuum, of approximately 10−8 Torr, to create the interconnection to the pads for the electrical measurement from the graphene electrodes, where 1 nm of Cr is an adhesive layer. For the lift-off process, the samples were soaked in acetone overnight.

Reactive ion etching

We etched the developed region after the e-beam lithography using O2 RIE (Femto Science) for only 5 s to prevent etching of e-beam resist. (100 kHz, 100 W in 10−2 Torr of O2) We then put the samples in acetone to remove the e-beam resist.

Electrical characterization

All electrical measurements were carried out by semiconductor parameter analyzers at room temperature under ambient condition. (Keithely 4200, Keithely for FET characterization in Figs 3, 5; and HP 4155 C, Agilent Technologies for logic device measurement in Fig. 6)

Data Availability

The authors declare that all data supporting the findings of this study are available within the paper and its supplementary information files.

References

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147 (2011).

Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotechnol. 8, 497 (2013).

Cheng, R. et al. Electroluminescence and photocurrent generation from atomically sharp WSe2/MoS2 heterojunction p–n diodes. Nano Lett. 14(10), 5590–5597 (2014).

Tsai, M.-L. et al. Monolayer MoS2 heterojunction solar cells. ACS Nano 8(8), 8317–8322 (2014).

Wang, H. et al. Integrated circuits based on bilayer MoS2 Transistors. Nano Lett. 12(9), 4674–4680 (2012).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354(6308), 99–102 (2016).

Xu, K. et al. Sub-10 nm nanopattern architecture for 2D material field-effect transistors. Nano Lett. 17(2), 1065–1070 (2017).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

Wang, L. et al. Shepard, K. L.; Dean, C. R., One-dimensional electrical contact to a two-dimensional material. Science 342(6158), 614–617 (2013).

Lee, C.-H. et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol. 9, 676 (2014).

Son, J. et al. Atomically precise graphene etch stops for three dimensional integrated systems from two dimensional material heterostructures. Nat. Commun. 9(1), 3988 (2018).

Splendiani, A. et al. Emerging photoluminescence in monolayer MoS2. Nano Lett. 10(4), 1271–1275 (2010).

Tongay, S. et al. Monolayer behaviour in bulk ReS2 due to electronic and vibrational decoupling. Nat. Commun. 5, 3252 (2014).

Zhang, E. et al. ReS2-based field-effect transistors and photodetectors. Adv. Func. Mater. 25(26), 4076–4082 (2015).

Park, J. Y. et al. Contact effect of ReS2/metal interface. ACS Appl. Mater. Inter. 9(31), 26325–26332 (2017).

Liu, F. et al. Highly sensitive detection of polarized light using anisotropic 2D ReS2. Adv. Func. Mater. 26(8), 1169–1177 (2016).

Shim, J. et al. High-Performance 2D Rhenium Disulfide (ReS2) Transistors and photodetectors by oxygen plasma treatment. Adv. Mater. 28(32), 6985–6992 (2016).

Xu, K. et al. Sulfur vacancy activated field effect transistors based on ReS2 nanosheets. Nanoscale 7(38), 15757–15762 (2015).

Dathbun, A. et al. Large-area CVD-grown sub-2 V ReS2 transistors and logic gates. Nano Lett. 17(5), 2999–3005 (2017).

Kim, C. et al. Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. ACS Nano 11(2), 1588–1596 (2017).

Kwon, J. et al. Thickness-dependent Schottky barrier height of MoS2 field-effect transistors. Nanoscale 9(18), 6151–6157 (2017).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534 (2015).

Liu, Y., Stradins, P. & Wei, S.-H. Van der Waals metal-semiconductor junction: Weak Fermi level pinning enables effective tuning of Schottky barrier. Sci. Adv. 2 (4) (2016).

Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, 722 (2010).

Liu, X. et al. P-type polar transition of chemically doped multilayer MoS2 transistor. Adv. Mater. 28(12), 2345–2351 (2016).

Jeon, P. J. et al. Low power consumption complementary inverters with n-MoS2 and p-WSe2 dichalcogenide nanosheets on glass for logic and light-emitting diode circuits. ACS Appl. Mater. Inter. 7(40), 22333–22340 (2015).

Liu, E. et al. Integrated digital inverters based on two-dimensional anisotropic ReS2 field-effect transistors. Nat. Commun. 6, 6991 (2015).

Cho, A.-J., Park, K. C. & Kwon, J.-Y. A high-performance complementary inverter based on transition metal dichalcogenide field-effect transistors. Nanoscale Res. Lett. 10(1), 115 (2015).

Ross, J. S. et al. Electrically tunable excitonic light-emitting diodes based on monolayer WSe2 p–n junctions. Nat. Nanotechnol. 9, 268 (2014).

Baugher, B. W. H., Churchill, H. O. H., Yang, Y. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable p–n diodes in a monolayer dichalcogenide. Nat. Nanotechnol. 9, 262 (2014).

Lemme, M. C. et al. Gate-activated photoresponse in a graphene p–n junction. Nano Lett. 11(10), 4134–4137 (2011).

Pospischil, A., Furchi, M. M. & Mueller, T. Solar-energy conversion and light emission in an atomic monolayer p–n diode. Nat. Nanotech. 9, 257 (2014).

Groenendijk, D. J. et al. Photovoltaic and photothermoelectric effect in a double-gated WSe2 Device. Nano Lett. 14(10), 5846–5852 (2014).

Kim, I. S. et al. Influence of stoichiometry on the optical and electrical properties of chemical vapor deposition derived MoS2. ACS Nano 8(10), 10551–10558 (2014).

Tosun, M. et al. High-gain inverters based on WSe2 complementary field-effect transistors. ACS Nano 8(5), 4948–4953 (2014).

Cheng, R. et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 5143 (2014).

Kim, K. K. et al. Synthesis and characterization of hexagonal boron nitride film as a dielectric layer for graphene devices. ACS Nano 6(10), 8583–8590 (2012).

Laturia, A., Van de Put, M. L. & Vandenberghe, W. G. Dielectric properties of hexagonal boron nitride and transition metal dichalcogenides: from monolayer to bulk. npj 2D Mater. Appl. 2(1), 6 (2018).

Acknowledgements

This study was supported by the National Research Foundation of Korea Grant funded by the Korean Government (2017R1A5A1014862 and 2018M3D1A1058793) and Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Science, ICT & Future Planning (NRF-2017R1A2B2006568). C.-H.L. acknowledges the support from the KU-KIST School Project.

Author information

Authors and Affiliations

Contributions

J.Kwon and G.-H.L. conceived and designed the study. J.Kwon fabricated samples and carried out all related experiments under the guidance of G.-H.L. and with the help of the other authors. Y.S. assisted in the preparation of heterostructure samples. H.K. carried out the logic device measurement under the guidance of S.I., J.Y.L. performed electrical measurements under the guidance of C.-H.L., H.P. assisted electrical measurements under the guidance of J.Kim, K.W. and T.T. prepared high quality hBN crystals. All authors contributed to the discussion of this work. J.Kwon and G.-H.L. wrote the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kwon, J., Shin, Y., Kwon, H. et al. All-2D ReS2 transistors with split gates for logic circuitry. Sci Rep 9, 10354 (2019). https://doi.org/10.1038/s41598-019-46730-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-46730-7

This article is cited by

-

Longitudinal and latitudinal split-gate field-effect transistors for NAND and NOR logic circuit applications

npj 2D Materials and Applications (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.