Abstract

Wafer scale (2”) BN grown by metal organic chemical vapor deposition (MOCVD) on sapphire was examined as a weakly interacting dielectric substrate for graphene, demonstrating improved transport properties over conventional sapphire and SiO2/Si substrates. Chemical vapor deposition grown graphene was transferred to BN/sapphire substrates for evaluation of more than 30 samples using Raman and Hall effects measurements. A more than 2x increase in Hall mobility and 10x reduction in sheet carrier density was measured for graphene on BN/sapphire compared to sapphire substrates. Through control of the MOCVD process, BN films with roughness ranging from <0.1 nm to >1 nm were grown and used to study the effects of substrate roughness on graphene transport. Arrays of graphene field effect transistors were fabricated on 2” BN/sapphire substrates demonstrating scalability and device performance enhancement.

Similar content being viewed by others

Introduction

Due to its amazing properties, graphene continues to be of great interest more than a decade after its experimental discovery1. Unfortunately, interactions between graphene and its environment, including the substrate, greatly degrade its transport properties. Substrate induced scattering from charged impurities, roughness, and phonons will reduce mobility2,3. The most successful approach to mitigate these effects has been the use of a thin van der Walls (vdW) buffer layer, like hBN4,5 or MoS26, preserving the mobility of the graphene to values near those of suspended material. Of the available vdW materials, hBN is one of the only insulators and due to is dielectric properties (comparable to SiO27), high surface optical phonon energy (169 eV)8 and atomically smooth surface; it has been the most successful and widely used material for preserving and protecting the intrinsic properties of 2D materials (graphene, phosphorene, MoS2, …)4,5,6,9,10,11,12,13,14. The overwhelming majority of this work has used hBN flakes exfoliated from high quality bulk materials. The high purity and crystal quality of this exfoliated material has given rise to amazing properties; however, due to the small size, low yield and poor reproducibility of these exfoliated flakes this process is not scalable or suitable for device fabrication beyond the laboratory.

The need for large area high quality hBN thin films for 2D substrates, dielectrics, and tunneling barriers has generated considerable upswing in hBN growth. High quality hBN thin films from mono to many layers thick over large areas have been produced using chemical vapor deposition (CVD) using both metallic15,16,17,18 and insulating substrates19,20,21,22. Taking advantage of the catalytic nature of metal substrates, like Cu and Ni, high quality material can be grown at quite low temperatures (<1000 °C). Since this process it typically surface catalyzed the controlled growth of mono-to few-layer hBN is possible23. The hBN grown on metal films can then be transferred to insulating substrates for further processing and characterization. Improved transport in graphene has been demonstrated using such transferred hBN films24,25 as compared to conventional substrates. Lee et al.24 demonstrated a 3x increase in graphene mobility when a few layer hBN buffer was inserted on SiO2/Si. Back gated graphene field effect transistors (FET) on hBN, grown on Fe substrates showed improved mobility and reduced intrinsic doping as compared to similar devices directly on SiO2/Si25. For many of the applications described above hBN grown on a metal will inevitably require transfer to insulating substrates adding complexity, sources of contamination, and damage from the fabrication process.

Alternatively, hBN films grown directly on insulating substrates do not require transfer prior to device processing. Due to the challenges of growing hBN directly on an insulating substrate, such as sapphire, it has been much less explored than its counterpart grown on metals. Growing on sapphire it is much more challenging to produce continuous ultra-thin films of mono– or bi-layer thickness, and as such, most reports demonstrate films from few to tens of nanometers thick20,26,27. The formation of large hexagonal wrinkles has also been observed in BN grown on sapphire due to the thermal expansion mismatch between BN and the substrate20,28. These features make BN films grown on sapphire distinct from those on metals. Jang et al. reported growth of smooth few-layer hBN on sapphire and demonstrated a 2x increase in graphene field effect mobility as compared to graphene on SiO2/Si29. Now with the availability of high quality large area CVD grown BN films on sapphire, more work is needed to explore their applications as substrates and dielectrics for 2D electronics.

In this paper, we investigate the use of few-layer sp2-BN on sapphire as a weakly interacting substrate for graphene. The basal plane of sp2 bonded BN forms the same honeycomb lattice as graphene and can form atomically thin and smooth layers. In multilayer BN, layers are known to stack hexagonal (AB stacking), rhombohedral (ABC stacking), or turbostratic (random stacking) with very small differences in inter planar spacing. For this work, CVD grown graphene was transferred to wafer scale sp2 BN/sapphire (now referred to as BN) grown by metal organic chemical vapor deposition (MOCVD) to study the effects on transport properties by Hall and FET device measurements. The effect of BN roughness was also investigated using BN films with roughness from <0.1 nm to >1 nm. Results show a more than 2x increase in graphene mobility when transferred to BN on sapphire substrate with a strong dependence on substrate induced doping related to BN roughness.

Results

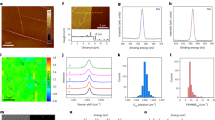

For application as a graphene substrate, BN films need to be atomically smooth, atomically flat, insulating and uniform over large areas. Growth of BN on sapphire by MOCVD at low pressure (20 Torr) and high V/III ratios (>2250) has been shown to produce films fitting these parameters with excellent thickness uniformity (1.6 + /−0.1 nm) and low roughness (<0.1 nm) over large areas (Fig. 1a). Under these low-pressure high V/III ratio conditions growth has been shown to be self-terminating (Supplementary Fig. S1) resulting in c-oriented films, which are consistently 4 mono-layers thick26. Reducing the V/III ratio or increasing the pressure disrupts these self-terminating conditions resulting in thicker, rougher (>1 nm) films with a random orientation (Fig. 1b)30. Varying the V/III ratio across a range of 450 to 2250 produces films with RMS roughness from a few nanometer to atomically smooth (Supplementary Fig. S2). From TEM the BN interlayer spacing was measured to be~ 3.45 and 3.5 Å for the smooth (high V/III ratio) and rough (low V/III ratio) BN films, respectively, which is larger than that for hBN (3.35 Å) indicating disorder in the stacking sequence. Raman spectroscopy of these films (Supplementary Fig. S3) shows the characteristic E2g mode of sp2-bonded BN at 1369 cm−1 30 and X-ray photoelectron spectroscopy (Supplementary Fig. S4) shows B 1 s and N 1 s peaks at a binding energy of 190.2 and 397.6 eV consistent with B-N bonding16 (see ref.30 for more BN material details). From XPS analysis, the B/N was measured to be 1/1 to 1.05 across a range of samples. To demonstrate uniformity across each wafer Fig. 1a,b gives the measured roughness, thickness and full width at half maximum (FWHM) from the sp2-BN E2g mode at 5 points across 2” BN/sapphires wafers. The atomically smooth BN/sapphire is well suited for application as a substrate for 2D materials, while rougher films are useful to study the effects of substrate roughness on graphene transport.

Boron Nitride on sapphire as a substrate for graphene. Optical image with BN thickness, roughness, and full width at half maximum of sp2 BN E2g Raman mode at five points for (a) smooth and (b) rough BN/sapphire substrates. Top left insets are AFM images for the center of each BN/sapphire substrate (scale bar 250 nm) and bottom right are cross-sectional TEM images.

Monolayer graphene films grown by CVD on Cu were transferred to 20 different BN on sapphire substrates with BN roughness ranging from >1 nm to <0.1 nm to study the effects of BN roughness and morphology on graphene. Half of the BN/sapphire substrates were grown under self-terminating conditions and have measured roughness <0.1 nm. Graphene was also transferred to sapphire and SiO2/Si as reference substrates. Raman spectroscopy of graphene films was used to compare the different dielectric substrates. Figure 2a shows typical graphene spectra taken from films on each substrate. Analysis of these graphene samples shows the substrate has limited effect on G and G’ peak position (Supplementary Fig. S5). Characteristic of all samples is a small defect peak and a G’/G intensity ratio of ~2 indicating films are of good structural quality and predominately monolayer. Raman was also used to evaluate variation between samples on similar substrates as a method to qualify reproducibility of the BN MOCVD growth and graphene transfer processes. The D/G intensity ratio (ID/IG) taken from multiple spots on each sample was used for comparison, Fig. 2b–d. On sapphire the mean ID/IG is 0.09 with a standard deviation (STD) of 0.05 across 6 samples. Comparable values of ID/IG of 0.1 with a STD of 0.05 were found for the samples transferred onto both the smooth and rough BN/Sapphire substrates indicating that the graphene is both uniform and undamaged during the transfer process regardless of the substrate.

Raman analysis of graphene on various dielectric substrates. (a) Representative Raman spectra from graphene on SiO2/Si, sapphire, rough BN/sapphire and smooth BN/sapphire substrates. Measured ID/IG distribution from graphene films on (b) 11 smooth BN/sapphire, (c) 9 rough BN/sapphire, and (d) 6 sapphire substrates.

To probe the effects of the dielectric substrate on graphene transport, room temperature Hall measurements were performed on more than 35 1 cm × 1 cm graphene samples on various substrates. Regardless of substrate material, all samples were found to be p-type. Figure 3a shows Hall mobility (µH) as a function of sheet carrier density (ns) for each sample. As a comparison, graphene transferred to c-plane sapphire and SiO2/Si substrates was also investigated. From this data a clear separation into groups based on the substrate can be observed, illustrating the impact the underlying substrate has on transport. Graphene films on sapphire and SiO2/Si have the lowest µH and highest ns. By switching to even a very rough (>1 nm) BN/sapphire substrate a noticeable reduction in ns and increase in µH is achieved. This trend of improving graphene transport continues as the BN roughness is reduced. A 2x increase in µH and one order of magnitude decrease in ns was achieved on the smoothest BN/sapphire substrates. The substrate is known to effect ns and µH in a number of ways causing doping, phonon scattering and/or corrugation of the graphene layer. At the surface of SiO2 and sapphire hydroxyl groups can form31,32, which will adsorb water and p-type dope the graphene33,34. Switching to the inert vdW surface of BN will eliminate this substrate doping effect assuming a near perfect surface and interface. For graphene supported by MOCVD BN/sapphire we expect a contribution to ns from surface impurities and defects, which may form hydroxyl groups similar to sapphire and SiO2. As such, it is not surprising to see a higher ns in graphene supported by rough BN. If we compare the morphologies and layer orientation (Fig. 1) for the different BN/sapphire substrates, we can visualize how improving surface roughness and morphology may reduce surface defects contributing to ns. The corresponding increase in mobility with decreasing roughness can be attributed to multiple factors. Most obviously from Fig. 3, mobility is inversely affected by ns, which as previously reported for CVD graphene on BN may been due to the reduction in charged impurity Coulomb scattering35,36. The additional effects of substrate roughness and phonons may also contribute, as will be explored below.

For substrate supported graphene, scattering due to the surface impurities37, roughness38, and surface optical (SO) phonons3 from the substrate as well as graphene longitudinal acoustic (LA) phonon2 and short range scattering39 will all effect mobility. The mobility limited by Coulomb scattering from impurities, short range scattering from defects and roughness are all temperature independent mechanisms that will be defined here as µ0. The temperature dependent mechanisms for the graphene LA phonon (µAL) and substrate SO phonon (µSO) can be expressed as:

where ρ s is the graphene 2D mass density, vf is the fermi velocity, vs is velocity of sound, DA is the acoustic deformation potential, E0 is the substrate phonon energy, and C is the coupling strength. Using Matthiessen’s rule, the total limited mobility is expressed as 1/µtot = 1/µ0 + 1/µLA + 1/µSO. Accordingly, we observe an inverse mobility dependence on ns (Fig. 3). At high temperatures the substrate SO phonons will have a strong effect on the temperature dependence of µtot. Comparison of the lowest E0 values, taken from literature, for BN (169 meV)8 and sapphire (55 meV)40 shows that switching to a BN/sapphire substrate can positively impact µH at room temperature.

Further studying the effects of BN on graphene transport, temperature dependent Hall measurements were performed on graphene samples on sapphire, rough BN/sapphire and smooth BN/sapphire substrates. From all samples, we find ns to be independent of temperature over the range of 10 to 320 K (Fig. 4a) indicative of the 2D nature of graphene. The substrate dependence of ns further illustrates the strong contribution of surface charge and impurities to graphene. Comparison of ns for graphene on rough vs. smooth BN suggests a higher concentration of surface charges on the rough BN with more random layer morphology as observed in room temperature measurements.

Analysis of graphene transport on various dielectric substrates. (a) Temperature dependence of graphene sheet carrier density. Temperature dependent mobility of graphene on (b) sapphire, (c) rough BN/sapphire, and (c) smooth BN/sapphire. Red lines are fits to µtot = (1/µ0 + 1/µLA + 1/µSO)−1. Fitting parameters µ0, DA, C, and E0 are given for each sample.

Temperature dependent mobility for graphene on sapphire, rough BN, and smooth BN are shown in Fig. 4b–d. From initial inspection, a clear difference between samples can be observed. The graphene films on smooth BN and sapphire substrates show the typical trend of increasing mobility with decreasing temperature over the full range of measurement, while on the rough BN/sapphire substrate a decrease in mobility with temperature is observed at temperatures below ~150 K. Although both the graphene on smooth BN/sapphire and sapphire have the same inverse temperature dependence, we clearly see that on sapphire mobility continues to increase up to ~20 K, while on smooth BN mobility increases until only ~125 K. As described in Eqn. (2) this is due to the difference in E0 for BN and sapphire. Fitting of the measured Hall mobility to µtot = (1/µ0 + 1/µLA + 1/µSO)−1 shows good agreement with graphene on both smooth BN and sapphire. Only µ0, DA, C, and E0 were obtained from fitting given in Fig. 4b–d. All other constants were taken from literature (Supplementary Table S1). The values for DA were determined to be 17.7 and 16 eV for sapphire and smooth BN substrates in good agreement with theoretical and experimental values2. The experimentally determined values for E0 are 135 meV for the smooth BN/sapphire and 60 meV sapphire. On a rough BN/sapphire substrate, graphene mobility is not well described by Eqns. (1) and (2), which both have an inverse temperature dependence. Instead, a positive temperature dependence below 150 K is observed, more indicative of a 3D scattering mechanism like ionized impurity scattering. Positive temperature dependence of mobility has been observed in highly defective irradiated41 or fluorinated42 graphene. This thermally activated transport in highly defective graphene has been attributed to localization effects. As discussed above, the high substrate roughness is expected to produce local defects in the graphene, which may cause a similar effect, but more work is needed to further elucidate this phenomenon. Similarly, transport has also been observed in graphene on SiC due to parallel conduction in the 2D graphene and 3D SiC substrate43. We do not expect to see any contributions to electrical measurement from the BN/sapphire substrate due to the highly insulating nature of both BN and sapphire. Attempts to measure sheet resistivity in BN/sapphire substrates give values greater than 1010 Ω (system limit). Since at higher temperatures mobility is limited by substrate induced SO phonon scattering, we fit the graphene on rough BN mobility to µtot = (1/µ0 + 1/µSO)−1 for temperatures greater than 150 K. This fit gives us an estimate of E0 (140 meV) for these BN/sapphire substrates, which is in good agreement with the smooth BN/sapphire. Using this modified version of µtot we also obtain a value of 1851 cm2/Vs for µ0, which is between those for the smooth BN and sapphire. Although, this term contains the contribution of roughness to µtot we cannot explicitly determine its contribution considering Coulomb and short range scattering are also temperature independent. If we qualitatively compare µ0 from the graphene on smooth BN and sapphire samples, which have similar roughness (<0.1 nm), we find the effects of impurity and carrier density (Coulomb and short range) to be significant suggesting a stronger contribution to µtot than roughness.

Further quantifying MOCVD grown BN as a substrate for graphene devices, top-gated FETs were fabricated on a 1” graphene film transferred to a 2” BN/sapphire substrate (Fig. 5a). The mask design included a large array of device dimensions; however, yield on devices with channel lengths <2 µm was very low. As a result, this work focused on devices with channel lengths 2 to 10 µm. As a comparison, graphene on SiO2/Si FETs were also fabricated and tested. Typical Id-Vd measurements showing gate modulation in devices on smooth and rough BN/sapphire are shown in Fig. 5b. Gate modulation in devices on smooth BN/sapphire shows a positive dependence on gate voltage, indicating electrons as the majority carrier. In devices on rough BN/sapphire the modulation has a negative dependence on gate voltage indicating the majority carriers are holes. The observed n-type nature of graphene (g)FETs on the smooth BN/sapphire is contrary to the p-type nature observed in the Hall measurements. Since Al2O3 has been shown to dope graphene and can significantly increase electron concentration, it is expected that the deposition of the Al2O3 top gate is related to this difference in majority carrier type44. The observed switch (from p to n) in majority carrier type in devices on smooth BN/graphene, but not rough BN/sapphire, is due to the lower background carrier density.

The transfer characteristics of gFET devices on rough BN/sapphire, smooth BN/sapphire and SiO2/Si were also studied. The Dirac point voltage is clearly different for these three dielectric substrates, Fig. 5c. Controlled doping is not easy in graphene and the Dirac point of gFETs cannot readily be adjusted by tuning the doping density of the graphene channel. However, as shown here the material in contact with the graphene channel can dictate the type of charged carriers. The Dirac point of a graphene device can be adjusted by selecting a gate metal with suitable work function and/or having a large gate capacitance to ensure a strong response between the gate electrode and graphene channel45. In our case, the bottom BN layer in the devices presented here also changes the Dirac point. Figure 5c shows the transfer characteristics for the three sets of devices. The Dirac point for devices on smooth BN/sapphire is ~ −7 V, while for devices on rough BN/sapphire and SiO/Si it is about 1 and −4.5 V, respectively. Devices show the typical ambipolar gFET behavior as manifested by the “V” shape of the transfer curve. A slight shift in the Dirac point with the drain voltage was observed due to hysteresis in the channel. This is likely from impurities and defects at the graphene-substrate and graphene-gate interfaces46.

Next, field effect mobility values for devices with different dimensions were extracted to determine the uniformity of our process. One common method is to use transfer curves to extract mobility using the following equation

where gm is transconductance, defined as gm = dId/dVg, Cox is the gate oxide capacitance (Cox = κε0/tox), W is channel width, and L channel length. Using this method, we found mobility depended strongly on the channel length (Supplementary Fig. S6). This significant variation in mobility is largely due to effects of contact resistance, which can obscure the true field effect mobility in transistor devices. The so-called Y-function method47 has been used has an effective way to limit effects of contact resistance in extracting field effect mobility in low dimensional FETs48,49. This method relies on combining drain current and transconductance transfer characteristics considering the first order mobility attenuation coefficient and contact resistance. Assuming contact resistance does not depend on Vg Y-function is defined as:

Plotting Y against Vg, mobility can be extracted from the slope of the linear portion of the curve. The mobility values extracted from this method are more consistent than those calculated using the transconductance method. We characterized more than 50 devices with channel lengths from 2 to 10 µm across the wafer. Figure 6 shows the distribution of the Dirac voltage and extracted mobility across the graphene FET array on a smooth BN/sapphire wafer. A mean VDirac of −7 with a standard deviation of only 1 V is quite narrowly distributed indicating relatively good carrier uniformity. A mean extracted µ of 409 with a standard deviation of 60 cm2/Vs was also measured. For comparison FETs on rough BN/sapphire and SiO2/Si have a typical mobility of 260 and 96 cm2/Vs, respectively. These values are considerably lower than those measured using the Hall effect, which is believed to be caused by impurities and graphene degradation from the top gate fabrication process. One way to reduce process degradation and doping from Al2O3 deposition would be to cap the graphene surface with a thin BN layer prior to processing. The narrow distribution of these typical device metrics highlights the uniformity of the BN/sapphire substrate and its usefulness as a weakly interacting substrate for graphene devices.

Conclusion

We have presented results from a detailed study on MOCVD BN on sapphire as a weakly interacting dielectric substrate for graphene. Wafer scale BN can be grown on sapphire with low roughness and excellent uniformity. Using Raman, Hall effect, and FET device characterization we studied the impact the dielectric substrate has on CVD transferred graphene. A greater than 10x decrease in graphene carrier density and 2x increase in mobility is achieved by using a BN/sapphire substrate as compared to SiO2/Si or sapphire. Scattering due to increased ns and SO phonons from the substrate were found to have the most significant impact on mobility at room temperature. Substrate roughness was also found to be correlated with graphene doping. Large area (1” square) graphene FET arrays were fabricated on 2” BN/sapphire and investigated showing good uniformity across the array. This collective work demonstrates significant performance improvements in graphene using scalable methods for producing BN/sapphire substrates.

Methods

Boron Nitride thin films used in this study were grown via a metalorganic chemical vapor deposition (MOCVD) technique. The substrates used for BN growth were c-plane sapphire which allows for uniform, few layer BN to be grown. In a cold-walled vertical MOCVD reactor, the NH3 and TEB precursor gases used for N and B, respectively, are injected such that they are not heated nor do they interact with one another until they reach the surface of the substrate. The reactor was kept at a pressure of 20 Torr and the substrate was heated to 1000 °C during the growth. The ratio of NH3 to TEB was set between 2250 to 950 to achieve the desired morphology and quality of BN films.

Graphene was grown on a copper substrate by CVD using methane as the carbon source. Films were subsequently transferred to dielectric substrates using a typical wet transfer with PMMA, similar to the process described in ref.50. After transfer, graphene films were annealed in forming gas (5% H2: 95% Ar) for 1 hr at 300 °C to remove any additional residue from the transfer process.

Transferred graphene and BN MOCVD layers were characterized using a suite of techniques. The BN thickness was measured by X-ray reflectance (XRR) using a PANalytical Empyrean X-ray diffractometer at a grazing incidence angle. Cross section TEM samples were prepared using the in-situ FIB lift out technique on an FEI Dual Beam FIB/SEM and imaged with a FEI Tecnai TF-20 FEG/TEM operated at 200 kV in high-resolution (HR) TEM mode. The surface morphologies of the graphene and BN films were analyzed by AFM using a Bruker Dimension Icon in tapping mode. Raman measurements were performed using a Renishaw inVia system under a backscattering geometry with scattered radiation collected along the sapphire [0001] direction. A 4 mW 488 nm excitation source, 20 µm slits, and a 3000 l/mm grating was used for each measurement. The transport properties were characterized by Hall-effect measurements. For room temperature measurements, an Accent 5500 system was used under ambient conditions. For temperature dependent measurements from 10 to 320 K, a Lakeshore 7507 system was used. Prior to measurement the sample was loaded into the cryostat, heated to 350 K under a He atmosphere and held overnight. Measurement sweeps were taken during cooling to 10 K and heating to insure a consistent measurement. If samples were not heated to 350 K, the measurements were found to be quite different on heating and cooling.

Top-gated graphene FETs were fabricated on transferred graphene on BN/sapphire and SiO2/Si substrates. Graphene mesas were defined using O2-plasma etch followed by source/drain metal contacts (Ti/Pt/Au) using a first lift-off process. A 20-nm thick Al2O3 was used as gate dielectric. Finally, 100-nm thick gate metal (Ti/Au) contacts were defined using a second lift-off process. Gate dimensions were chosen such that electron beam lithography process is not required for the FET fabrication process. An Agilent 4156 C precision semiconductor parametric analyzer was used for all the electrical characterization of the FETs.

References

Novoselov, K. S. et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature 438, 197–200 (2005).

Chen, J. H., Jang, C., Xiao, S., Ishigami, M. & Fuhrer, M. Intrinsic and extrinsic performance limits of graphene devices on SiO2. Nat. Nanotechnol. 3, 206–209 (2008).

Fratini, S. & Guinea, F. Substrate-limited electron dynamics in graphene. Phys. Rev. B 77, 195415 (2008).

Dean, C. R. et al. Boron nitride substrates for high quality graphene electronics. Nature. Mat

Mayorov, A. S. et al. Micrometer-scale ballistic transport in encapsulated graphene at room temperature. Nano Lett. 11, 2396–2399 (2011).

Lu, C. P., Li, G., Watanabe, K., Taniguchi, T. & Andrei, E. Y. MoS 2: choice substrate for accessing and tuning the electronic properties of graphene. Phys. Rev. Lett. 113, 156804 (2014).

Lee, G. H. et al. Electron tunneling through atomically flat and ultrathin hexagonal boron nitride. Appl. Phys. Lett. 99, 243114 (2011).

Serrano, J. et al. Vibrational Properties of Hexagonal Boron Nitride: Inelastic X-Ray Scattering and Ab Initio Calculations. Phys. Rev. Lett. 98, 095503 (2007).

Geim, A. K. & Grigorieva, I. V. (2013). Van der Waals heterostructures. Nature 499, 419–425 (2013).

Wang, H. et al. BN/Graphene/BN Transistors for RF Applications. IEEE Electron Device Lett. 32, 1209–1211 (2011).

Zomer, P. J., Dash, S. P., Tombros, N. & van Wees, B. J. A transfer technique for high mobility graphene devices on commercially available hexagonal boron nitride. Appl. Phys. Lett. 99, 232104 (2011).

Lee, H. G. et al. Highly stable, dual-gated MoS2 Transistors Encapsulated ny hexagonal boron nitride with gate-controllable contact, resistance, and threshold votage. ACS Nano 9, 7019–7026 (2015).

Doganov, R. A. et al. Transport properties of ultrathin black phosphorus on hexagonal boron nitride. Appl. Phys. Lett. 106, 083505 (2015).

Chen, X. L. et al. High-quality sandwiched black phosphorus heterostructure and its quantum oscillations. Nature Comm. 6, 7315, https://doi.org/10.1038/ncomms8315 (2015).

Song, L. et al. Large scale growth and characterizations of atomic hexagonal boron nitride layers. Nano Lett. 10, 3209–3215 (2010).

Ismach, A. et al. Toward the controlled synthesis of hexagonal boron nitride films. ACS Nano 6, 6378–6385 (2012).

Tay, R. Y. et al. Growth of large single-crystalline two-dimensional boron nitride hexagons on electropolished copper. Nano Lett. 14, 839–846 (2014).

Lu, J. et al. Step flow versus mosaic film growth in hexagonal boron nitride. J. Am. Chem. Soc. 135, 2368–2373 (2013).

Kobayashi, Y. & Akasaka, T. Hexagonal BN epitaxial growth on (0001) sapphire substrate by MOVPE. J. Crys. Gro. 310, 5044–5047 (2008).

Li, X. Large-area two-dimensional layered hexagonal boron nitride grown on sapphire by metalorganic vapor phase epitaxy. Cryst. Growth Des. 16, 3409–3415 (2016).

Chubarov, M., Pedersen, H., Hogberg, H., Jensen, J. & Henry, A. Growth of high quality epitaxial rhombohedral boron nitride. Cryst. Growth Des. 12, 3215–3220 (2012).

Dahal, R. Epitaxially grown semiconducting hexagonal boron nitride as a deep ultraviolet photonic material. App. Phys. Lett. 98, 211110 (2011).

Siegel, G., Ciobanu, C. V., Narayanan, B., Snure, M. & Badescu, S. C. Heterogeneous pyrolysis: a route for epitaxial growth of hBN atomic layers on copper using separate boron and nitrogen precursors. Nano Lett. 17, 20404–2413 (2017).

Lee, K. H. et al. Large-scale synthesis of high quality hexagonal boron nitride nanosheets for large-area graphene electronics. Nano Lett. 12, 714–718 (2012).

Kim, S. M. et al. Synthesis of large-area multilayer hexagonal boron nitride for high material performance. Nat. Commun. 6, 9662, https://doi.org/10.1038/ncomms9662 (2015).

Paduano, Q. S., Snure, M., Bondy, J. & Zens, T. W. C. Self-terminating growth in hexagonal boron nitride by metal organic chemical vapor deposition. Appl. Phys. Express 7, 071004 (2014).

Chubarov, M. et al. Polytype pure sp2-BN films as dictated by substrate crystal structure. Chem. Mater. 27, 1640–1645 (2015).

Yang, X. et al. Growth of hexagonal boron nitride on sapphire substrate by pulsed-mod metalorganic vapor epitaxy. J. Cryst. Growth 482, 1–8 (2018).

Jang, A. R. et al. Wafer-Scale and Wrinkel-Free Epitaxial Growth of Single-Oriented Multilayer Hexagonal Boron Nitride on Sapphire. Nano Lett. 16, 3360–3366 (2016).

Paduano, Q. et al. Metalorganic chemical vapor deposition of few-layer sp2 bonded boron nitride films. J. Crys. Gro. 449, 148–155 (2016).

Assy, D. B., Barnette, A. L. & Kim, S. H. Effects of Surface Chemistry on Structure and Thermodynamics of Water Layers at Solid-Vapor Inerfaces. J. Phys. Chem. C 113, 2128–2133 (2009).

Yang, D., Krasowska, M., Sedev, R. & Ralston, J. The unusual surface chemistry of α-Al2O3 (0001). Phys. Chem. Chem. Phys. 12, 13724–13729 (2010).

Lafkioti, M. et al. Graphene on a hydrophobic substrate: Doping reduction and hysteresis suppression under ambient conditions. Nano Lett. 10, 1149–1153 (2010).

Wehling, T. O., Katsnelson, M. I. & Lichtenstein, A. I. First-principles studies of water adsorption on graphene: The role of the substrate. Appl. Phys. Lett. 93, 202110 (2008).

Uddin, M. A. et al. Mobility enhancement in graphene transistors on low temperature pulsed laser deposited boron nitride. Appl. Phys. Lett. 107, 203110 (2015).

Wang, M. et al. A platform for large-scale graphene electronics – CVD growth of single-layer graphene on CVD-grown hexagonal boron nitride. Adv. Mater. 25, 2746–2752 (2010).

Ando, T. Screening Effect and Impurity Scattering in Monolayer Graphene. J. Phys. Soc. Jpn. 75, 074716 (2006).

Katsnelson, M. I. & Geim, A. K. Electron scattering on microscopic corrugations in graphene. Phil. Trans. R. Soc. A 366, 195–204 (2008).

Hwang, E. H., Adam, S. & Das Sarma, S. Carrier Transport in Two Dimensional Graphene Layers. Phys. Rev. Lett. 98, 186806 (2007).

Konar, A., Fang, T. & Jena, D. Effects of high κ-gate dielectric on charge transport in graphene-based filed effect transistors. Phys. Rev. B 82, 115452 (2010).

Chen, J. H., Cullen, W. G., Jang, C., Fuhrer, M. S. & Williams, E. D. Defect scattering in graphene. Phys. Rev. Lett. 102, 236805 (2009).

Withers, F., Dubois, M. & Savchenko, A. K. 2010. Electron properties of fluorinated single-layer graphene transistors. Phys. Rev. B 82, 073403 (2010).

Lisesivdin, S. B. et al. Extraction and scattering analyses of 2D and bulk carriers in epitaxial graphene-on-SiC structure. Physica E 63, 87–92 (2014).

Graces, N. Y. et al. Epitaxial graphene surface preparation for atomic layer deposition of Al2O3. J. Appl. Phys. 109, 124304 (2011).

Xu, H. et al. Top-gated graphene field-effect transistors with high normalized transconductance and designable Dirac point voltage. Acs Nano 5, 5031–5037 (2011).

Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano 4, 7221–7228 (2010).

Ghibaudo, G. New method for extraction of MOSFET parameters. Electron. Lett. 24, 543–545 (1988).

Cao, Q., Han, S. J., Tulevski, G. S., Franklin, A. D. & Haensch, W. Evaluation of field effect mobility and contact resistance of transistors that use solution-processed single wall carbon nanotubes. ACS Nano 6, 6471–6477 (2012).

Chang, H. Y., Zhu, W. & Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. Appl. Phys. Lett. 104, 113504 (2014).

Li, X. et al. Large-area synthesis of high quality and uniform graphene films on copper foil. Science 324, 1312–1314 (2009).

Acknowledgements

The authors would like to thank Timothy Cooper for help with Hall measurements. This work was funded by the Air Force Office of Scientific Research under award number FA9550-16RYCOR331. Graphene growth and transfer was performed by Graphenea S. A.

Author information

Authors and Affiliations

Contributions

S.V. and M.S. prepared the manuscript. S.V. fabricated and tested devices. G.S. synthesized B.N. on sapphire substrates. T.P. preformed Raman measurements. M.S. planned the research and analyzed Raman and Hall data. All authors read and commented on the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Vangala, S., Siegel, G., Prusnick, T. et al. Wafer scale BN on sapphire substrates for improved graphene transport. Sci Rep 8, 8842 (2018). https://doi.org/10.1038/s41598-018-27237-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-018-27237-z

This article is cited by

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.