Abstract

Black silicon (b-Si) is currently being adopted by several fields of technology, and its potential has already been demonstrated in various applications. We show here that the increased surface area of b-Si, which has generally been considered as a drawback e.g. in applications that require efficient surface passivation, can be used as an advantage: it enhances gettering of deleterious metal impurities. We demonstrate experimentally that interstitial iron concentration in intentionally contaminated silicon wafers reduces from 1.7 × 1013 cm−3 to less than 1010 cm−3 via b-Si gettering coupled with phosphorus diffusion from a POCl3 source. Simultaneously, the minority carrier lifetime increases from less than 2 μs of a contaminated wafer to more than 1.5 ms. A series of different low temperature anneals suggests segregation into the phosphorus-doped layer to be the main gettering mechanism, a notion which paves the way of adopting these results into predictive process simulators. This conclusion is supported by simulations which show that the b-Si needles are entirely heavily-doped with phosphorus after a typical POCl3 diffusion process, promoting iron segregation. Potential benefits of enhanced gettering by b-Si include the possibility to use lower quality silicon in high-efficiency photovoltaic devices.

Similar content being viewed by others

Introduction

The special properties of black silicon (nanostructured silicon, b-Si), such as large surface area, negligible reflectance and superhydrophobicity, provide interesting opportunities in various applications, including biological and chemical sensors1, self-cleaning surfaces2, and photodiodes3. Currently b-Si is of particular interest within the photovoltaics industry4,5 due to its high compatibility with recently introduced diamond wire-sawn multicrystalline silicon wafers6.

Although several interesting properties of b-Si have been extensively studied in recent years, many potential advantages have yet remained undiscovered. One advantage worth studying is the potentially enhanced gettering of metal impurities which are deleterious in several applications, including transistors and photovoltaic devices7. In gettering, the impurities are typically relocated to less critical sites within the device. This is often realised via impurity segregation to a heavily phosphorus-doped region8,9,10,11, typically referred as phosphorus diffusion gettering (PDG). Since the b-Si nanostructures are typically more heavily doped than planar wafers after dopant diffusion12,13,14, b-Si is likely to enhance PDG via increased segregation.

In addition to enhanced segregation, the large surface area or possible structural defects induced by b-Si fabrication15,16,17 may provide additional gettering sites by introducing nucleation sites for metal precipitates. An idea of enhanced gettering via increased surface area in silicon solar cells was proposed by Dimassi et al.18. They fabricated sacrificial porous silicon (PS) layers on Si wafers and demonstrated that the harmful impurities were gettered from the bulk material to the porous layer during thermal annealing due to the high surface reactivity of PS. Similarly, mechanical19 or saw damage20,21 has been used as effective gettering sites. Thus, b-Si could promote the removal of impurities via near-surface precipitation, in addition to enhanced segregation.

We perform here a benchmark study to quantitatively compare the gettering performance of b-Si and planar reference wafers for iron, the most deleterious metal impurity in p-type silicon7,22. We intentionally contaminate IC-grade CZ-Si wafers with iron at specific concentrations and manufacture b-Si on these substrates. The wafers are subjected to PDG processes with varying temperature profiles, and the resulting gettering efficiencies are characterised by minority charge carrier lifetime measurements. Finally, we draw guidelines toward implementing these findings into predictive process simulators23,24 via discussing the dominant gettering mechanisms and compare the experimental findings with simulations.

Methods

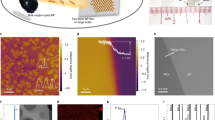

The experimental procedure is outlined in Fig. 1. First, a controlled contamination procedure10 was carried resulting in two different initial total iron levels typically found in high-performance multicrystalline silicon22: 1.7 × 1013 cm−3 (low) and 3.6 × 1014 cm−3 (high). After wet oxidation, b-Si was fabricated on one half of each wafer by cryogenic deep reactive ion etching (RIE) using process parameters described in25. As a result, every wafer had both b-Si and planar halves (Fig. 2a) to make the comparison between the two surfaces reliable and straightforward. A phosphorus-doped layer was formed in the front side of the wafers by POCl3 diffusion. Subsequently, temperature was ramped down to 600–800 °C with a 4 °C/min rate to a low temperature anneal (LTA) step for 2 h at 800 °C, 3.5 h at 750 °C, 5.5 h at 700 °C or 8 h at 650 °C. The annealing times were chosen based on simulations to reach steady state iron concentration throughout the whole wafer26.

(a) A photograph showing b-Si etched on half of each wafer and μ-PCD lifetime maps of a contaminated wafer without gettering and a selected gettered wafer (800 °C LTA, low Fe). (b) Effective minority carrier lifetimes of the passivated wafers LTA treated at different temperatures. Note the break in the y-axis. The reported values have been averaged from μ-PCD maps measured before Fe-B pair dissociation. The dashed lines act as a guide for eye. The error bars have been determined from the range of variation in lifetime within the μ-PCD maps. (c) Interstitial iron concentration of the gettered b-Si and planar wafer halves determined from injection-level dependent QSSPC measurements. The left-hand bars represent the low Fe wafers and the right-hand bars the high Fe samples as indicated by the white bars which denote the interstitial iron concentration of the ungettered reference wafers. The dashed lines indicate the solid solubility limit of iron at each temperature according to42. Note the logarithmic y-axis. The error bars have been determined assuming a 5% uncertainty in the QSSPC measured lifetime.

In order to determine the bulk minority charge carrier recombination lifetime – a proxy for cell efficiency potential27 – the heavily-doped layers were removed by wet etching. A 2-minute dip in a CH3COOH:HF:HNO3 solution etched approximately 5 µm from both surfaces of a planar reference wafer. The wafer surfaces were subsequently passivated with atomic-layer-deposited (ALD) aluminum oxide (Al2O3) using a process described in14. To determine the bulk interstitial iron concentration, lifetime was measured before and after Fe-B pair dissociation with both microwave-detected photoconductance decay (μ-PCD) and quasi-steady-state photoconductance (QSSPC) techniques. The iron concentration was determined from the measured QSSPC data per an extended model developed by Macdonald et al.28 at an injection level around 1016 cm−3.

Finally, simulations were carrier out to elucidate the underlying physical processes operating in the experiment. Phosphorus diffusion was simulated using Sentaurus Process by applying the model and parameters from29. In analogy to13, the phosphorus concentration in the phosphosilicate glass was fitted to the electrochemical capacitance-voltage (ECV) profile measured at planar wafers, and b-Si was treated as a triangular 2D structure in the simulations. The phosphorus profile in b-Si was averaged over a single needle in lateral direction to obtain a 1D profile comparable to the planar case. The resulting gettering efficiency was simulated using an iron segregation model involving iron point defects reacting with doubly-charged vacancies and pairing with positively charged phosphorus originally suggested by Haarahiltunen et al.26 with a parametrization revised by Talvitie et al.9.

Results and Discussion

Figure 2a shows μ-PCD lifetime maps of a low Fe contamination level wafer without gettering and a corresponding wafer after POCl3 diffusion and a LTA at 800 °C for 2 h. The carrier lifetime significantly improves by the presence of b-Si. The lifetime in the b-Si half (720 μs) is more than two orders of magnitude higher than in the ungettered wafer (1.9 μs) and more than three times that of the gettered planar half (200 μs), implying a significantly higher cell efficiency potential for the b-Si wafers27. Since both halves have been passivated simultaneously, the lifetime difference is a direct result of differences in the wafer bulk, indicating more efficient gettering in b-Si. Possible slight surface roughness on the b-Si area after Si etching would be visible only as a reduced effective lifetime in the b-Si half, which indicates that the difference in bulk lifetime may be even higher.

Figure 2b presents the effective minority carrier lifetime averaged from μ-PCD maps for all the samples gettered with various LTA sequences. Regardless of the LTA conditions, b-Si results in a higher lifetime than a planar surface in both low and high Fe samples. As hypothesised, the increased carrier lifetime in the b-Si halves is indeed due to a reduced amount of iron in the bulk (Fig. 2c) caused by enhanced gettering. For instance, the lifetime map shown in Fig. 2a corresponds to final bulk iron concentrations of 3 × 1010 cm−3 and 2 × 1011 cm−3 in the b-Si and planar wafer halves, respectively.

The segregation efficiency improves with decreasing temperature due to a larger iron solubility difference between the heavily phosphorus-doped region and the wafer bulk30. This phenomenon is clearly visible in Fig. 2b and c as an increase in lifetime and decrease in iron concentration with reducing LTA temperature. Within the high Fe samples, carrier lifetimes in b-Si and planar wafer halves increase with equal rate within the measurement accuracy. In the low Fe samples instead, lifetime in the planar reference approaches b-Si with decreasing LTA temperature. Lifetime limited by surfaces (~1.5 ms) with a reasonable surface recombination velocity of 15 cm/s31 agrees with the highest measured value and is more than one order of magnitude lower than iron-limited lifetime with 109 cm−3 impurity concentration32. Thus, the diminishing difference between b-Si and planar lifetimes with decreasing LTA temperature is due to surface recombination dominating the effective lifetime despite the efficient ALD Al2O3 passivation. Similar behavior is not observed in the iron concentration values since the effect of surfaces cancels out in its extraction. However, the flash used to dissociate Fe-B pairs may improve the efficiency of ALD Al2O3 surface passivation33, which would slightly overestimate the extracted iron concentration in the low Fe samples28. Nevertheless, this does not affect the comparison between b-Si and planar samples.

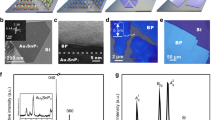

An explanation for the enhanced gettering is likely to be the high phosphorus concentration in the b-Si nanostructure. To further investigate this hypothesis, phosphorus diffusion into b-Si was simulated since the experimental determination of doping profile in the nanoscopic b-Si needles is challenging. Figure 3a verifies the used models by showing a good fit between the experimental and simulated profiles of electrically active phosphorus in a planar wafer diffused at 830 °C for 20 minutes. A corresponding simulated 2D doping profile in b-Si is presented in Fig. 3b, which shows that the silicon needles are extremely heavily doped with phosphorus. Furthermore, the simulations show that the active phosphorus dose in b-Si is three to four times that in the planar wafers. Also the experimental sheet resistance values shown in Fig. 3c illustrate that the doping concentration in b-Si is always considerably higher than in the planar samples.

(a) Experimental and simulated phosphorus profiles of a planar sample POCl3-diffused at 830 °C for 20 min with no low temperature anneal. The experimental ECV data is from14. Note the logarithmic y-axis. (b) A SEM image of a single b-Si needle and the corresponding simulated phosphorus profile. (c) Experimental sheet resistance values for the b-Si and planar samples after various LTA treatments.

The sheet resistance varies with LTA temperature (Fig. 3c), due to two effects. First, at higher temperatures, the phosphorus diffusivity is higher, allowing more phosphorus to diffuse into the wafer. On the other hand, with reducing LTA temperature a larger portion of phosphorus precipitates and turns electrically inactive due to reduced phosphorus solid solubility. Nevertheless, although doping concentration is higher in the samples with higher LTA temperature, which would enhance segregation, the temperature dependence of iron segregation coefficient dominates the observed trend in interstitial iron concentration (Fig. 2c), resulting in more iron gettered with lower temperatures.

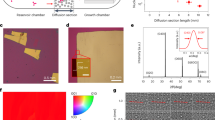

The final iron concentrations are below the solid solubility limits at every temperature (Fig. 2c), which suggests segregation to be the dominant gettering mechanism. Similarly, the observation that the gettering efficiency is rather independent of initial iron concentration is also characteristic of segregation7. Furthermore, activation energies calculated from the low Fe data are 2.4–2.5 eV for both b-Si and planar samples, which agree well with the previously reported 2.5 eV activation energy for the segregation coefficient9. Figures 4a and b compare simulated bulk iron concentrations, with segregation gettering as the only active gettering mechanism9,26, to the experimental values in planar and b-Si samples, respectively. In all cases, the trends of the simulated and experimental results are consistent, further supporting our hypothesis that segregation is the main gettering mechanism. In the b-Si samples, however, the simulation predicts lower iron concentrations than are experimentally observed. Nevertheless, the differences can be attributed to challenges in accurate quantitative simulation of dopant diffusion and segregation in b-Si, and measuring iron accurately at concentrations below ~5 × 109 cm−328.

Comparison of experimental and simulated interstitial iron concentration in planar (a) and b-Si (b) samples. The left-hand bars represent the low Fe wafers and the right-hand bars the high Fe samples as indicated by the open bars which denote the interstitial iron concentration of the ungettered reference wafers. The dashed lines indicate the solid solubility limit of iron at each temperature according to42. Note the logarithmic y-axes. The error bars are determined assuming a 5% uncertainty in the QSSPC measurements.

Among planar samples, also the quantitative results mainly agree with the experiments within the accuracy limits (Fig. 4a). However, the experiments systematically show slightly more efficient gettering than the simulation predicts, which could be explained by iron precipitation within the wafer bulk. This hypothesis is supported by the experimental iron concentrations of high Fe samples, where the difference between b-Si and planar halves is not as evident as in the low Fe samples (Fig. 2c). As the initial iron concentration in the high Fe samples is well above the iron solid solubility limit, iron starts to precipitate in the bulk during the LTA sequence34. As bulk precipitation is independent of wafer surfaces, the phenomenon reduces interstitial iron concentration in b-Si and planar samples to a similar degree. Nevertheless, iron segregation is likely dominant also in the high Fe samples since the final iron concentrations are below the solid solubility limits and the difference in gettering efficiency is visible in carrier lifetime (Fig. 2b).

No evidence was observed within this study for gettering enhancement by RIE-caused surface damage. On the other hand, earlier microscopic investigations of the specific b-Si fabrication process used here found little to no damage35. Some other b-Si fabrication methods, such as metal-assisted chemical etching36,37, introduce contaminants, and b-Si gettering could be efficiently used to remove the residual metals afterwards. The gettering efficiency may have been intensified by iron accumulation at the Al2O3/Si interface during post-deposition anneal38,39, which, nevertheless, does not dilute the lifetime or iron concentration difference between b-Si and planar samples. Lastly, the role of electrically inactive phosphorus on gettering remains ambiguous40,41. The used diffusion process is known to result in a significant amount of inactive phosphorus near the wafer surface, which is further pronounced in b-Si14. The simulations confirmed an increasing amount of inactive dopants in b-Si with decreasing LTA temperature, which could partly contribute to the gettering efficiency enhancement.

Conclusions

In conclusion, we have shown that the large surface area of b-Si, a considerable barrier for high efficiency b-Si solar cells in the past, can be used as an advantage to enhance gettering of detrimental metal impurities, specifically iron. We demonstrated that the effective minority carrier lifetime increased from less than 2 μs of an intentionally contaminated wafer to more than 1.5 ms via b-Si gettering, implying a significant increase in the substrate efficiency potential for b-Si solar cells27. The significant lifetime improvement was achieved by the reduction of the interstitial iron concentration from 1.7 × 1013 cm−3 to less than 1010 cm−3. A systematic series of different low temperature anneals, supported by simulations, suggested that the main gettering mechanism was segregation in both b-Si and planar samples, implying that the enhanced gettering efficiency can readily be described by predictive silicon solar cell process models23,24. Additionally, damage caused by b-Si fabrication could promote iron precipitation at the surface. These results hence indicate that the implementation of b-Si could enable the usage of lower quality silicon in e.g. photovoltaic devices via enhanced gettering.

Data availability

The datasets generated and analysed during the current study are available in the figshare repository, https://figshare.com/s/709964545df554612b29.

References

Stewart, M. P. & Buriak, J. M. Chemical and biological applications of porous silicon technology. Adv. Mater. 12, 859–869 (2000).

Qi, D. et al. Simple approach to wafer-scale self-cleaning antireflective silicon surfaces. Langmuir 25, 7769–7772 (2009).

Juntunen, M. A. et al. Near-unity quantum efficiency of broadband black silicon photodiodes with an induced junction. Nat. Photonics 10, 777–782 (2016).

Liu, X., Coxon, P. R., Hoex, B., Cole, J. M. & Fray, D. J. Black silicon: fabrication methods, properties and solar energy applications. Energy Environ. Sci. 7, 3223–3263 (2014).

Savin, H. et al. Black silicon solar cells with interdigitated back-contacts achieve 22.1% efficiency. Nat. Nanotech. 10, 624–628 (2015).

International technology roadmap for photovoltaic: Results 2016. 8th Edition, Mar. 2017.

Istratov, A. A., Hieslmair, H. & Weber, E. R. Iron contamination in silicon technology. Appl. Phys. A 70, 489–534 (2000).

Kang, J. S. & Schroder, D. K. Gettering in silicon. J. Appl. Phys. 65, 2974–2985 (1989).

Talvitie, H., Vähänissi, V., Haarahiltunen, A., Yli-Koski, M. & Savin, H. Phosphorus and boron diffusion gettering of iron in monocrystalline silicon. J. Appl. Phys. 109, 093505 (2011).

Vähänissi, V., Haarahiltunen, A., Talvitie, H., Yli-Koski, M. & Savin, H. Impact of phosphorus gettering parameters and initial iron level on silicon solar cell properties. Prog. Photovolt: Res. Appl. 21, 1127–1135 (2013).

Peral, A., Míguez, J. M., Ordás, R. & del Cañizo, C. Lifetime improvement after phosphorous diffusion gettering on upgraded metallurgical grade silicon. Sol. Energy Mater. Sol. Cells 130, 686–689 (2014).

Oh, J., Yuan, H.-C. & Branz, H. M. An 18.2%-efficient black-silicon solar cell achieved through control of carrier recombination in nanostructures. Nat. Nanotech. 7, 743–748 (2012).

Kafle, B. et al. On the emitter formation in nanotextured silicon solar cells to achieve improved electrical performances. Sol. Energy Mater. Sol. Cells 152, 94–102 (2016).

Pasanen, T., Vähänissi, V., Theut, N. & Savin, H. Surface passivation of black silicon phosphorus emitters with atomic layer deposited SiO2/Al2O3 stacks. Energy Procedia 124, 307–312 (2017).

Zaidi, S. H., Ruby, D. S. & Gee, J. M. Characterization of random reactive ion etched-textured silicon solar cells. IEEE Trans. Electron Dev. 48, 1200–1206 (2001).

Crouch, C. H. et al. Comparison of structure and properties of femtosecond and nanosecond laser-structured silicon. Appl. Phys. Lett. 84, 1850–1852 (2004).

Otto, M. et al. Extremely low surface recombination velocities in black silicon passivated by atomic layer deposition. Appl. Phys. Lett. 100, 191603 (2012).

Dimassi, W. et al. Porous silicon-based passivation and gettering in polycrystalline silicon solar cells. Nucl. Instr. Meth. Phys. Res. B 186, 441–445 (2002).

Sawada, R., Karaki, T. & Watanabe, J. Mechanical damage gettering effect in Si. Jpn. J. Appl. Phys. 10, 2097–2104 (1981).

Martins, G. F., Macdonald, P., Burton, T., Bonilla, R. S. & Wilshaw, P. R. Saw damage gettering for improved multicrystalline silicon. Energy Procedia 77, 607–612 (2015).

Shaw, E. C. et al. Saw Damage Gettering for industrially relevant mc-Si feedstock. Phys. Status Solidi A 214, 1700373 (2017).

Stokkan, G. et al. Impurity control in high performance multicrystalline silicon. Phys. Status Solidi A 214, 1700319 (2017).

Hofstetter, J. et al. Impurity-to-efficiency simulator: predictive simulation of silicon solar cell performance based on iron content and distribution. Prog. Photovolt: Res. Appl. 19, 487–497 (2011).

Morishige, A. E. et al. Building intuition of iron evolution during solar cell processing through analysis of different process models. Appl. Phys. A 120, 1357–1373 (2015).

Repo, P. et al. Effective passivation of black silicon surfaces by atomic layer deposition. IEEE J. Photovolt. 3, 90–94 (2013).

Haarahiltunen, A., Savin, H., Yli-Koski, M., Talvitie, H. & Sinkkonen, J. Modeling phosphorus diffusion gettering of iron in single crystal silicon. J. Appl. Phys. 105, 023510 (2009).

Wagner, H., Müller, M., Fischer, G. & Altermatt, P. P. A simple criterion for predicting multicrystalline Si solar cell performance from lifetime images of wafer prior to cell production. J. Appl. Phys. 114, 054501 (2013).

Macdonald, D. H., Geerlings, L. J. & Azzizi, A. Iron detection in crystalline silicon by carrier lifetime measurements for arbitrary injection and doping. J. Appl. Phys. 95, 1021–1028 (2004).

Schön, J. et al. Predictive simulation of doping processes for silicon solar cells. Energy Procedia 38, 312–320 (2013).

Nadahara, S., Tsunoda, H., Shiozaki, M., Watanabe, M. & Yamabe, K., in Defects inSilicon II, Proceedings of the Second Symposium on Defects in Silicon, edited by Bullis, W. M., Gösele, U. & Shimura, F. (Electrochemical Society, Pennington, NJ, 1991), pp. 667–674.

Dingemans, G. & Kessels, W. M. M. Status and prospects of Al2O3-based surface passivation schemes for silicon solar cells. J. Vac. Sci. Technol. A 30, 040802 (2012).

Yli-Koski, M. et al. Recombination activity of iron in boron doped silicon. Phys. Scr. T101, 86–88 (2002).

Dingemans, G. et al. Stability of Al2O3 and Al2O3/a-SiNx:H stacks for surface passivation of crystalline silicon. J. Appl. Phys. 106, 114907 (2009).

Murphy, J. D. & Falster, R. J. The relaxation behaviour of supersaturated iron in single-crystal silicon at 500 to 750 °C. J. Appl. Phys. 122, 113506 (2012).

von Gastrow, G. et al. Analysis of the atomic layer deposited Al2O3 field-effect passivation in black silicon. Sol. Energy Mater. Sol. Cells 142, 29–33 (2015).

Koynov, S., Brandt, M. S. & Stutzmann, M. Black nonreflecting silicon surfaces for solar cells. Appl. Phys. Lett. 88, 203107 (2006).

Toor, F. et al. Nanostructured silicon via metal assisted catalyzed etch (MACE): chemistry fundamentals and pattern engineering. Nanotechnology 27, 412003 (2016).

Liu, A. Y. et al. Gettering of interstitial iron in silicon by plasma-enhanced chemical vapour deposited silicon nitride films. J. Appl. Phys. 120, 193103 (2016).

Liu, A. Y. & Macdonald, D. Impurity gettering effect of atomic layer deposited aluminium oxide films on silicon wafers. Appl. Phys. Lett. 110, 191604 (2017).

Chen, R., Trzynadlowski, B. & Dunham, S. T. Phosphorus vacancy cluster model for phosphorus diffusion gettering of metals in Si. J. Appl. Phys. 115, 054906 (2014).

Peral, A., Dastgheib-Shirazi, A., Wagner, H., Hahn, G. & del Cañizo, C. Effect of electrically inactive phosphorus versus electrically active phosphorus on iron gettering. Energy Procedia 77, 311–315 (2015).

Murphy, J. D. & Falster, R. J. Contamination of silicon by iron at temperatures below 800 C. Phys. Status Solidi Rapid Res. Lett. 5, 370–372 (2011).

Acknowledgements

The authors acknowledge the provision of facilities by Aalto University at OtaNano – Micronova Nanofabrication Centre. This work was funded by project “BLACK” (project No. 2956/31/2014) which is supported under the umbrella of SOLAR-ERA.NET by the Finnish Funding Agency for Innovation TEKES. T.P.P. acknowledges the Aalto ELEC Doctoral School and Jenny and Antti Wihuri Foundation for the financial support. H.S.L. acknowledges the support of the Finnish Cultural Foundation, Tiina & Antti Herlin Foundation, and Walter Ahlström Foundation.

Author information

Authors and Affiliations

Contributions

H.S.L., V.V., T.P.P. and H.S. conceived and designed the experiments. H.S.L. and V.V. performed the controlled contamination, and T.P.P. conducted the rest of the experiments. T.P.P., H.S.L. and V.V. analyzed the results. J.S. performed the phosphorus diffusion simulations, and H.S.L. conducted the iron segregation simulations. T.P.P. prepared the manuscript. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Pasanen, T.P., Laine, H.S., Vähänissi, V. et al. Black silicon significantly enhances phosphorus diffusion gettering. Sci Rep 8, 1991 (2018). https://doi.org/10.1038/s41598-018-20494-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-018-20494-y

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.