Abstract

The metal–oxide–semiconductor field-effect transistor (MOSFET), a core element of complementary metal–oxide–semiconductor (CMOS) technology, represents one of the most momentous inventions since the industrial revolution. Driven by the requirements for higher speed, energy efficiency and integration density of integrated-circuit products, in the past six decades the physical gate length of MOSFETs has been scaled to sub-20 nanometres. However, the downscaling of transistors while keeping the power consumption low is increasingly challenging, even for the state-of-the-art fin field-effect transistors. Here we present a comprehensive assessment of the existing and future CMOS technologies, and discuss the challenges and opportunities for the design of FETs with sub-10-nanometre gate length based on a hierarchical framework established for FET scaling. We focus our evaluation on identifying the most promising sub-10-nanometre-gate-length MOSFETs based on the knowledge derived from previous scaling efforts, as well as the research efforts needed to make the transistors relevant to future logic integrated-circuit products. We also detail our vision of beyond-MOSFET future transistors and potential innovation opportunities. We anticipate that innovations in transistor technologies will continue to have a central role in driving future materials, device physics and topology, heterogeneous vertical and lateral integration, and computing technologies.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Change history

05 September 2023

A Correction to this paper has been published: https://doi.org/10.1038/s41586-023-06576-6

References

Fleming, J. Instrument for converting alternating electric currents into continuous currents. US patent 803684A (1905).

Bardeen, J. & Brattain, W. The transistor, a semi-conductor triode. Phys. Rev. 74, 230–231 (1948). Demonstration of a solid-state transistor.

Lilienfeld, J. E. Method and apparatus for controlling electric currents. US patent 1,745,175 (1930). The original idea of a FET.

Atalla, M. M. et al. Stabilization of silicon surfaces by thermally grown oxides. Bell Syst. Tech. J. 38, 749–783 (1959). The key enabling innovation responsible for the rise of MOSFETs.

Kahng, D. Electric field controlled semiconductor device. US patent 3,102,230 (1963).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In IEEE International Electron Devices Meeting 673–676 (IEEE, 2017).

Dennard, R. et al. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid State Circuits 9, 256–268 (1974).

Mistry, K. et al. A 2.0V, 0.35 µm partially depleted SOI-CMOS technology. In IEEE International Electron Devices Meeting 583–586 (IEEE, 1997).

Tenbroek, B. et al. Self-heating effects in SOI MOSFETs and their measurement by small signal conductance techniques. IEEE Trans. Electron Devices 43, 2240–2248 (1996).

Ghani, T. et al. A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In IEEE International Electron Devices Meeting 978–980 (IEEE, 2003). Commercialization of strained-silicon technology.

Mistry, K. et al. A 45 nm logic technology with high-k + metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In IEEE International Electron Devices Meeting 247–250 (IEEE, 2007). Commercialization of high-k + metal-gate CMOS technology.

Auth, C. et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In IEEE VLSI Technology Symposium 131–132 (IEEE, 2012). Commercialization of 3D FinFETs.

Bohr, M., Chau, R., Ghani, T. & Mistry, K. The high-k solution. IEEE Spectr. 44, 29–35 (2007).

Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59, 1813–1828 (2012).

More Moore table. (page 13, Table MM9) International Roadmap for Devices and Systems IRDS 2022 More Moore (ieee.org) (2022).

Luryi, S. Quantum capacitance devices. Appl. Phys. Lett. 52, 501–503 (1988).

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices 3rd edn (Wiley-Interscience, 2007).

Asenov, A. Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 µm MOSFET’s: a 3-D atomistic simulation study. IEEE Trans. Electron Devices 45, 2505–2513 (1998).

Dadgour, H., Endo, K., De, V. & Banerjee, K. Modeling and analysis of grain-orientation effects in emerging metal-gate devices and implications for SRAM reliability. In IEEE International Electron Devices Meeting 705–708 (IEEE, 2008).

Kuhn, K. et al. Process technology variation. IEEE Trans. Electron Devices 58, 2197–2208 (2011).

Grasser, T. et al. NBTI in nanoscale MOSFETs—the ultimate modeling benchmark. IEEE Trans. Electron Devices 61, 3586–3593 (2014).

Cartier, E. et al. Fundamental aspects of HfO2-based high-k metal gate stack reliability and implications on tinv-scaling. In IEEE International Electron Devices Meeting 441–444 (IEEE, 2011).

Yu, B., Wann, C., Nowak, E. D., Noda, K. & Hu, C. Short-channel effect improved by lateral channel-engineering in deep-submicronmeter MOSFETs. IEEE Trans. Electron Devices 44, 627–634 (1997).

Welser, J., Hoyt, J. L. & Gibbons, J. F. NMOS and PMOS transistors fabricated in strained silicon/relaxed silicon–germanium structures. In IEEE International Electron Devices Meeting 1000–1002 (IEEE, 1992).

Ota, K. et al. Novel locally strained channel technique for high performance 55 nm CMOS. In IEEE International Electron Devices Meeting 27–30 (IEEE, 2002).

Yeo, Y., Lu, Q., King, T-J. & Hu, C. Enhanced performance in sub-100 nm CMOSFETs using strained epitaxial silicon-germanium. In IEEE International Electron Devices Meeting 753–756 (IEEE, 2000).

Takagi, S. et al. III–V/Ge channel MOS device technologies in nano CMOS era. Jpn J. Appl. Phys. 54, 06FA01 (2015).

del Alamo, J. A. et al. Nanometer-scale III–V MOSFETs. IEEE J. Electon Devices Soc. 4, 205–214 (2016).

Yeap, G. et al. 5nm CMOS production technology platform featuring full-fledged EUV and high-mobility channel FinFETs with densest 0.021 µm2 SRAM cells for mobile SoC and high-performance computing applications. In IEEE International Electron Devices Meeting 879–882 (IEEE, 2019).

Skotnicki, T. & Boeuf, F. How can high mobility channel materials boost or degrade performance in advanced CMOS. In IEEE VLSI Technology Symposium 153–154 (IEEE, 2010).

Jin, D., Kim, D., Kim, T. & del Alamo, J. A. Quantum capacitance in scaled down III–V FETs. In IEEE International Electron Devices Meeting 495–498 (IEEE, 2009).

Koba, S. et al. Channel length scaling limits of III–V channel MOSFETs governed by source–drain direct tunneling. Jpn J. Appl. Phys. 53, 04EC10 (2014).

Zheng, Z. et al. Gallium nitride-based complementary logic integrated circuits. Nat. Electron. 4, 595–603 (2021).

Yan, R., Ourmazd, A. & Lee, K. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710 (1992). Provides a simple but important MOSFET scaling guideline.

Frank, D., Taur, Y. & Wong, H. Generalized scale length for two-dimensional effects in MOSFET’s. IEEE Electron Device Lett. 19, 385–387 (1998).

Ando, T. Ultimate scaling of high-k gate dielectrics: higher-κ or interfacial layer scavenging? Materials 5, 478–500 (2012).

Robertson, J. & Wallace, R. M. High-k materials and metal gates for CMOS applications. Mater. Sci. Eng. R 88, 1–41 (2014).

Hayashi, Y. Gate insulator type field effect transistor. Japanese patent JP1791730 (filed 24 June 1980) (1993). Proposal for a 3D transistor.

Hisamoto, D., Kaga, T., Kawamoto, Y. & Takeda, E. A fully depleted lean-channel transistor (DELTA)—a novel vertical ultrathin SOI MOSFET. In IEEE International Electron Devices Meeting 833–836 (IEEE, 1989).

Hisamoto, D. et al. A folded‐channel MOSFET for deep‐sub‐tenth micron era. In IEEE International Electron Devices Meeting 1032–1034 (IEEE, 1998). A prototype demonstration of an ultrathin-body 3D FinFET.

Huang, X. et al. Sub 50‐nm FinFET: PMOS. In IEEE International Electron Devices Meeting 67–70 (IEEE, 1999).

Rasouli, S., Dadgour, H., Endo, K., Koike, H. & Banerjee, K. Design optimization of FinFET domino logic considering the width quantization property. IEEE Trans. Electon Devices 57, 2934–2943 (2010).

Kawasaki, H. Challenges and solutions of FinFET integration in an SRAM cell and a logic circuit for 22 nm node and beyond. In IEEE International Electron Devices Meeting 289–292 (IEEE, 2009).

Niimi, H. et al. Sub-10−9 Ω-cm2 n-type contact resistivity for FinFET technology. IEEE Electron Device Lett. 37, 1371–1374 (2016).

He, X. et al. Impact of aggressive fin width scaling on FinFET device characteristics. In IEEE International Electron Devices Meeting 493–496 (IEEE, 2017).

Appenzeller, J. et al. Toward nanowire electronics. IEEE Trans. Electron Devices 55, 2827–2845 (2008).

Mizutani, T. et al. Threshold voltage and current variability of extremely narrow silicon nanowire MOSFETs with width down to 2 nm. In Silicon Nanoelectronics Workshop 1–2 (Publishers are Japan Society of Applied Physics, IEEE, 2015).

Mertens, H. et al. Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates. In IEEE VLSI Technology Symposium 1–2 (IEEE, 2016).

Yang, B. et al. Vertical silicon-nanowire formation and gate-all-around MOSFET. IEEE Electron Device Lett. 29, 791–794 (2008).

Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In IEEE VLSI Technology Symposium 230–231 (IEEE, 2017).

Jagannathan, H. et al. Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices. In IEEE International Electron Devices Meeting 557–560 (IEEE, 2021).

Weckx, P. et al. Novel forksheet device architecture as ultimate logic scaling device towards 2nm. In IEEE International Electron Devices Meeting 36.5.1–36.5.4 (IEEE, 2019).

Wang, R. et al. Experimental study on quasi-ballistic transport in silicon nanowire transistors and the impact of self-heating effects. In IEEE International Electron Devices Meeting 1.4.1–1.4.4 (IEEE, 2008).

Zhuge, J. et al. Experimental investigation and design optimization guidelines of characteristic variability in silicon nanowire CMOS technology. In IEEE International Electron Devices Meeting 61–64 (IEEE, 2009).

Iijima, S. & Ichihashi, T. Single-shell carbon nanotubes of 1-nm diameter. Nature 363, 603–605 (1993).

Novoselov, K. S. et al. Two-dimensional atomic crystals. Proc. Natl Acad. Sci. USA 102, 10451–10453 (2005).

Ajayan, P., Kim, P. & Banerjee, K. Two-dimensional van der Waals materials. Phys. Today 69, 38–44 (2016).

Tans, S., Verschueren, A. & Dekker, C. Room-temperature transistor based on a single carbon nanotube. Nature 393, 49–52 (1998). Demonstration of a carbon nanotube transistor.

Javey, A. et al. High-k dielectrics for advanced carbon nanotube transistors and logic gates. Nat. Mater. 1, 241–246 (2002).

Wang, Z. et al. Growth and performance of yttrium oxide as an ideal high-k gate dielectric for carbon-based electronics. Nano Lett. 10, 2024–2030 (2010).

Javey, A., Guo, J., Wang, Q., Lundstrom, M. & Dai, H. Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003).

Franklin, A. & Chen, Z. Length scaling of carbon nanotube transistors. Nat. Nanotechnol. 5, 858–862 (2010).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate length. Science 355, 271–276 (2017).

Shabrawy, K., Maharatna, K., Bagnall, D. & Hashimi, B. Modeling SWCNT bandgap and effective mass variation using Monte Carlo approach. IEEE Trans. Nanotechnol. 9, 184–193 (2010).

Cao, Q. et al. End-bonded contacts for carbon nanotube transistors with low, size-independent resistance. Science 350, 68–72 (2015).

Cao, Q., Tersoff, J., Farmer, D., Zhu, Y. & Han, S. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 356, 1369–1372 (2017). Demonstration of carbon nanotube FETs outperforming state-of-the-art Si MOSFETs.

Jin, S. et al. Using nanoscale thermocapillary flows to create arrays of purely semiconducting single-walled carbon nanotubes. Nat. Nanotechnol. 8, 347–355 (2013).

Shulaker, M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

Ghosh, S., Bachilo, S. & Weisman, R. Advanced sorting of single-walled carbon nanotubes by nonlinear density-gradient ultracentrifugation. Nat. Nanotechnol. 5, 443–450 (2010).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

Cao, Q., Han, S. & Tulevski, G. Fringing-field dielectrophoretic assembly of ultrahigh-density semiconducting nanotube arrays with a self-limited pitch. Nat. Commun. 5, 5071 (2014).

Liu, L. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 368, 850–856 (2020).

Islam, A. Variability and reliability of single-walled carbon nanotube field effect transistors. Electronics 2, 332–367 (2013).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Iannaccone, G., Bonaccorso, F., Colombo, L. & Fiori, G. Quantum engineering of transistors based on 2D materials heterostructures. Nat. Nanotechnol. 13, 138–191 (2018).

Li, M., Su, S., Wong, H. & Li, L. How 2D semiconductors could extend Moore’s law? Nature 567, 169–170 (2019).

Wang, H. et al. Graphene nanoribbons for quantum electronics. Nature Rev. Phys. 3, 791–802 (2021).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011). Demonstration of a top-gated monolayer 2D semiconductor FET.

Fuhrer, M. & Hone, J. Measurement of mobility in dual-gated MoS2 transistors. Nat. Nanotechnol. 8, 146–147 (2013).

Kaasbjerg, K., Thygesen, K. & Jacobsen, K. Phonon-limited mobility in n-type single-layer MoS2 from first principles. Phys. Rev. B 85, 115317 (2012).

Liu, W. et al. High-performance few-layer-MoS2 field-effect-transistor with record low contact-resistance. In IEEE International Electron Devices Meeting 499–502 (IEEE, 2013).

Jena, D. & Konar, A. Enhancement of carrier mobility in semiconductor nanostructures by dielectric engineering. Phys. Rev. Lett. 98, 136805 (2007).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013). Demonstration of high-performance monolayer 2D-TMD FET.

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Das, S., Chen, H., Penumatcha, A. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2012).

Kang, J., Liu, W., Sarkar, D., Jena, D. & Banerjee, K. Computational study of metal contacts to monolayer transition-metal dichalcogenide semiconductors. Phys. Rev. X 4, 031005 (2014). Comprehensive ab initio analysis of metal contacts to 2D semiconductors.

English, C., Shine, G., Dorgan, V., Saraswat, K. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Kang, J., Sarkar, D., Khatami, Y. & Banerjee, K. Proposal for all-graphene monolithic logic circuits. Appl. Phy. Lett. 103, 083113 (2013).

Yeh, C., Cao, W., Pal, A., Parto, K. & Banerjee, K. Area-selective-CVD technology enabled top-gated and scalable 2D-heterojunction transistors with dynamically tunable Schottky barrier. In IEEE International Electron Devices Meeting 23.4.1–23.4.4 (IEEE, 2019). Demonstration of single-crystal 2D semiconductor growth in pre-designed sites enabling high-performance FETs.

Kappera, R. et al. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 13, 1128–1134 (2014).

Shen, P. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

O’Brien, K. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In IEEE International Electron Devices Meeting 146–149 (IEEE, 2021).

Chou, A. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In IEEE International Electron Devices Meeting 150–153 (IEEE, 2021)

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Cao, W., Chu, J.-H., Parto, K. & Banerjee, K. A mode-balanced reconfigurable logic gate built in a van der Waals strata. npj 2D Mater. Appl. 5, 20 (2021).

Fang, H. et al. Degenerate n-doping of few-layer transition metal dichalcogenides by potassium. Nano Lett. 13, 1991–1995 (2013).

Kang, J. et al. On-chip intercalated-graphene inductors for next-generation radio frequency electronics. Nat. Electron. 1, 46–51 (2018).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42 nm contact pitch and 250 µA/µm drain current. In IEEE International Electron Devices Meeting 23.4.1–23.4.4 (IEEE, 2019).

Yang, L., Lee, R., Rao, S., Tsai, W. & Ye, P. 10 nm nominal channel length MoS2 FETs with EOT 2.5 nm and 0.52 mA/µm drain current. Device Research Conference 237−238 (IEEE, 2015).

Li, K. et al. MoS2 U-shape MOSFET with 10 nm channel length and poly-Si source/drain serving as seed for full wafer CVD MoS2 availability. In IEEE Symposium on VLSI-TSA 52–53 (IEEE, 2016).

Cao, W., Liu, W. & Banerjee, K. Prospects of ultra-thin nanowire gated 2D-FETs for next-generation CMOS technology. In IEEE International Electron Devices Meeting 14.7.1–14.7.4 (IEEE, 2016).

Desai, S. et al. MoS2 transistor with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Osada, M. & Sasaki, T. Two-dimensional dielectric nanosheets: novel nanoelectronics from nanocrystal building blocks. Adv. Mater. 24, 210–228 (2012).

Chamlagain, B. et al. Thermally oxidized 2D TaS2 as a high-κ gate dielectric for MoS2 field-effect transistors. 2D Mater. 4, 031002 (2017).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015). Wafer-scale (4 inch) growth of 2D semiconductor.

Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. Nat. Electron. 1, 228–236 (2018).

Kang, J., Liu, W. & Banerjee, K. High performance MoS2 transistors with low resistance molybdenum contacts. Appl. Phys. Lett. 104, 093106 (2014).

Guo, Y. et al. Study on the resistance distribution at the contact between molybdenum disulfide and metals. ACS Nano 8, 7771–7779 (2014).

Baugher, B., Churchill, H., Yang, Y. & Jarillo-Herrero, P. Intrinsic electronic transport properties of high-quality monolayer and bilayer MoS2. Nano Lett. 13, 4212–4216 (2013).

Kiriya, D., Tosun, M., Zhao, P., Kang, J. & Javey, A. Air-stable surface charge transfer doping of MoS2 by benzyl viologen. J. Am. Chem. Soc. 136, 7853–7856 (2014).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Li, S. et al. Thickness scaling effect on interfacial barrier and electrical contact to two-dimensional MoS2 layers. ACS Nano 8, 12836–12842 (2014).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electric contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, 722–726 (2010).

Liu, Y. et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. Nano Lett. 16, 6337–6342 (2016).

Smithe, K., Suryavanshi, S., Rojo, M., Tedjarati, A. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Liu, W., Sarkar, D., Kang, J., Cao, W. & Banerjee, K. Impact of contact on the operation and performance of back-gated monolayer MoS2 field-effect-transistors. ACS Nano 9, 7904–7912 (2015).

Zhang, W., Huang, Z., Zhang, W. & Li, Y. Two-dimensional semiconductors with possible high room temperature mobility. Nano Res. 7, 1731–1737 (2014).

Cui, Y. et al. High-performance monolayer WS2 field-effect transistors on high-κ dielectrics. Adv. Mater. 27, 5230–5234 (2015).

Withers, F., Bointon, T. H., Hudson, D. C., Craciun, M. F. & Russo, S. Electron transport of WS2 transistors in a hexagonal boron nitride dielectric environment. Sci. Rep. 4, 4967 (2014).

Song, H. S. et al. High-performance top-gated monolayer SnS2 field-effect transistors and their integrated logic circuits. Nanoscale 5, 9666–9670 (2013).

Lin, Y. et al. Single-layer ReS2: two-dimensional semiconductor with tunable in-plane anisotropy. ACS Nano 9, 11249–11257 (2015).

Wang, X. et al. Chemical vapor deposition growth of crystalline monolayer MoSe2. ACS Nano 8, 5125–5131 (2014).

Podzorov, V., Gershenson, M. E., Kloc, Ch., Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. Appl. Phys. Lett. 84, 3301–3303 (2004).

Li, S. et al. Halide-assisted atmospheric pressure growth of large WSe2 and WS2 monolayer crystals. Appl. Mater. Today 1, 60–66 (2015).

Pei, T. et al. Few-layer SnSe2 transistors with high on/off ratios. Appl. Phys. Lett. 108, 053506 (2016).

Yang, S. et al. Layer-dependent electrical and optoelectronic responses of ReSe2 nanosheet transistors. Nanoscale 6, 7226–7231 (2014).

Feng, W., Zheng, W., Cao, W. & Hu, P. Back gated multilayer InSe transistors with enhanced carrier mobilities via the suppression of carrier scattering from a dielectric interface. Adv. Mater. 26, 6587–6593 (2014).

Zhang, Z. et al. Two-step heating synthesis of sub-3 millimeter-sized orthorhombic black phosphorus single crystal by chemical vapor transport reaction method. Sci. China Mater. 59, 122–134 (2016).

Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

Qiao, J., Kong, X., Hu, Z., Yang, F. & Ji, W. High-mobility transport anisotropy and linear dichroism in few-layer black phosphorus. Nat. Commun. 5, 4475 (2014).

Late, D. J. et al. GaS and GaSe ultrathin layer transistors. Adv. Mater. 24, 3549–3554 (2012).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Singh, J. et al. 14 nm FinFET technology for analog and RF applications. In IEEE VLSI Technology Symposium 140–141 (IEEE, 2017).

Du, Y., Yang, L., Zhou, H. & Ye, P. Performance enhancement of black phosphorus field-effect transistors by chemical doping. IEEE Electron Device Lett. 37, 429–432 (2016).

Yang, L. et al. Chloride molecular doping technique on 2D materials: WS2 and MoS2. Nano Lett. 14, 6275–6280 (2014).

Pang, C., Wu, P., Appenzeller, J. & Chen, Z. EOT WS2-FET with IDS > 600 µA/µm at VDS = 1V and SS < 70mV/dec at LG = 40 nm. In IEEE International Electron Devices Meeting 3.4.1–3.4.4 (IEEE, 2020).

Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs- Projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices 62, 3459–3469 (2015). A comprehensive scalability analysis of 2D FETs that established the viability of certain 2D semiconductors as optimal channel materials for sub-10-nm FETs.

Liu, L., Kumar, S., Ouyang, Y. & Guo, J. Performance limits of monolayer transition metal dichalcogenide transistors. IEEE Trans. Electron Devices 58, 3042–3047 (2011).

Liu, R. et al. Integrated digital inverters based on two-dimensional anisotropic ReS2 field-effect transistors. Nat. Commun. 6, 6991 (2015).

Mudd, G. et al. Tuning the bandgap of exfoliated InSe nanosheets by quantum confinement. Adv. Mater. 25, 5714–5718 (2013).

Chau, R. Process and packaging innovations for Moore’s law continuation and beyond. In IEEE International Electron Devices Meeting 1.1.1–1.1.6 (IEEE, 2019).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008). Proposal of an NC FET.

Ionescu, A. M. et al. Modeling and design of a low-voltage SOI suspended-gate MOSFET (SG-MOSFET) with a metal-over-gate architecture In Proceedings International Symposium on Quality Electronic Design 496–501 (IEEE, 2002).

Huang, Q., Huang, R., Pan, Y., Tan, S. & Wang, Y. Resistive-gate field-effect transistor: a novel steep-slope device based on a metal–insulator–metal–oxide gate stack. IEEE Electron Device Lett. 35, 877–879 (2014).

Han, J., Moon, D. & Meyyappan, M. Nanoscale vacuum channel transistor. Nano Lett. 17, 2146–2152 (2017).

Shukla, N. et al. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 6, 7812 (2015).

Gnani, E., Reggiani, S., Gnudi, A. & Baccarani, G. Steep-slope nanowire FET with a superlattice in the source extension. Solid State Electron. 65–66, 108–113 (2011).

Qiu, C. et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science 361, 387–392 (2018). Demonstration of a Dirac source FET.

Quinn, J., Kawamoto, G. & McCombe, B. Subband spectroscopy by surface channel tunneling. Surf. Sci. 73, 190–196 (1978). Proposal for a tunnel FET structure using band-to-band tunnelling.

Appenzeller, J., Knoch, Y. & Avouris, P. Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93, 196805 (2004).

Wan, J., Zaslavsky, A., Le Royer, C. & Cristoloveanu, S. Novel bipolar-enhanced tunneling FET with simulated high on-current. IEEE Electron Device Lett. 34, 24–26 (2013).

Saeidi, A. et al. Negative capacitance as performance booster for tunnel FETs and MOSFETs: an experimental study. IEEE Electron Device Lett. 38, 1485–1488 (2017).

Gopalakrishnan, K., Griffin, P. & Plummer, J. Impact ionization MOS (I-MOS)-part I: device and circuit simulations. IEEE Trans. Electron Devices 52, 69–76 (2005).

Padilla, A., Chun Wing, Y., Shin, C., Hu, C. & King Liu, T.-J. Feedback FET: a novel transistor exhibiting steep switching behavior at low bias voltages. In IEEE International Electron Devices Meeting 1–4 (IEEE, 2008).

Datta, S. & Das, B. Electronic analog of the electro‐optic modulator. Appl. Phys. Lett. 56, 665–667 (1990). Proposal of a spin FET.

Manchon, A. et al. New perspectives for Rashba spin–orbital coupling. Nat. Mater. 14, 871–882 (2015).

Banerjee, S., Register, L., Tutuc, E., Reddy, D. & MacDonald, A. Bilayer pseudospin field-effect transistor (BiSFET): a proposed new logic device. IEEE Electron Device Lett. 30, 158–160 (2009).

Akarvardar, K. et al. Design considerations for complementary nanoelectro-mechanical logic gates. In IEEE International Electron Devices Meeting 299–302 (IEEE, 2007).

Dadgour, H., Hussain, M., Cassell, A., Singh, N. & Banerjee, K. Impact of scaling on the performance and reliability degradation of metal-contacts in NEMS devices. IEEE International Reliability Physics Symposium 280–289 (IEEE, 2011).

Cao, W., Sarkar, D., Khatami, Y., Kang, J. & Banerjee, K. Subthreshold-swing physics of tunnel field-effect transistors. AIP Adv. 4, 067141 (2014).

Gandhi, R. et al. CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with ≤50 mV/decade subthreshold swing. IEEE Electron Device Lett. 32, 1504–1506 (2011).

Tomioka, K., Yoshimura, M. & Fukui, T. Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction. In IEEE Symposium on VLSI Technology 47–48 (IEEE, 2012). A heterojunction tunnel FET with a steep slope.

Knoll, L. et al. Inverters with strained Si nanowire complementary tunnel field-effect transistors. IEEE Electron Device Lett. 34, 813–815 (2013).

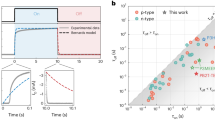

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015). A 2D semiconductor channel tunnel FET with a steep slope.

Memisevic. E., Svensson, J., Hellenbrand, M., Lind, E. & Wernersson, L. Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion = 10 µA/µm for Ioff = 1 nA/µm at VDS = 0.3 V. In IEEE International Electron Devices Meeting 500–503 (IEEE, 2016).

Kim, S. et al. Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nat. Nanotechnol. 15, 203–206 (2020).

Cao, W. et al. Designing band-to-band tunneling field-effect transistors with 2D semiconductors for next-generation low-power VLSI. In IEEE International Electron Devices Meeting 12.3.1–12.3.4 (IEEE, 2015).

Ross, I. M. Semiconductive translating device. US patent 2791760 (1957).

Scott, J. F. & Araujo, C. Ferroelectric memories. Science 246, 1400–1405 (1989).

Zhou, J. et al. Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis. In IEEE International Electron Devices Meeting 373–376 (IEEE, 2017).

Z. Yu, et al. Negative capacitance 2D MoS2 transistors with sub-60 mV/dec subthreshold swing over 6 orders, 250 µA/µm current density, and nearly-hysteresis-free. In IEEE International Electron Devices Meeting 577–580 (IEEE, 2017).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Lee, M. et al. Ferroelectric Al:HfO2 negative capacitance FETs. In IEEE International Electron Devices Meeting 565–568 (IEEE, 2017).

Fan, C. et al. Energy-efficient HfAlOx NCFET: using gate strain and defect passivation to realize nearly hysteresis- free sub-25 mV/dec switch with ultralow leakage. In IEEE International Electron Devices Meeting 561–564 (IEEE, 2017).

Chung, W. et al. Hysteresis-free negative capacitance germanium CMOS FinFETs with bi-directional sub-60 mV/dec. In IEEE International Electron Devices Meeting 365–368 (IEEE, 2017).

Cao, W. & Banerjee, K. Is negative capacitance FET a steep-slope logic switch?. Nat. Commun. 11, 196 (2020). This study demystifies the fundamental limitations of NC FETs and identifies alternative roles of NC in FET design.

Wang, H. et al. New insights into the physical origin of negative capacitance and hysteresis in NCFETs. In IEEE International Electron Devices Meeting 31.1.1–31.1.4 (IEEE, 2018).

Li, X. & Toriumi, A. Direct relationship between sub-60 mV/dec subthreshold swing and internal potential instability in MOSFET externally connected to ferroelectric capacitor. In IEEE International Electron Devices Meeting 31.3.1–31.3.4 (IEEE, 2018).

Jin, C., Jang, K., Saraya, T., Hiramoto, T. & Kobayashi, M. Experimental study on the role of polarization switching in subthreshold characteristics of HfO2-based ferroelectric and anti-ferroelectric FET. In IEEE International Electron Devices Meeting 31.5.1–31.5.4 (IEEE, 2018).

Toprasertpong, K., Takenaka, M. & Takagi, S. Direct observation of interface charge behaviors in FeFET by quasi-static split C-V and Hall techniques: revealing FeFET operation. In IEEE International Electron Devices Meeting 23.7.1–23.7.4 (IEEE, 2019).

Su, L. T., Naffziger, S. & Papermaster, M. Multi-chip technologies to unleash computing performance gains over the next decade. In IEEE International Electron Devices Meeting 1–8 (IEEE, 2017).

Huang, C. et al. 3-D self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued Moore’s law scaling. In IEEE International Electron Devices Meeting 20.6.1–20.6.4 (IEEE, 2020).

Banerjee, K., Souri, S., Kapur, P. & Saraswat, K. 3-D ICs: a novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration. Proc. IEEE 89, 602–633 (2001). A comprehensive treatise on 3D and heterogeneous integration from a circuit, system, thermal and technology perspective.

Batude, P. et al. Advances in 3D CMOS sequential integration. In IEEE International Electron Devices Meeting 14.1.1–14.1.4 (IEEE, 2009).

Wei, H. et al. Cooling three-dimensional integrated circuits using power delivery networks. In IEEE International Electron Devices Meeting 327–330 (IEEE, 2012).

Jiang, J., Parto, K., Cao, W. & Banerjee, K. Ultimate monolithic-3D integration with 2D materials: rationale, prospects, and challenges. IEEE J. Electron Devices Soc. 7, 878–887 (2019). A detailed analysis quantifying the benefits of monolithic and heterogeneous 3D integration with 2D materials.

Sachid, A. et al. Monolithic 3D CMOS using layered semiconductors. Adv. Mater. 28, 2547–2554 (2016).

Jiang, J., Kang, J., Chu, J. & Banerjee, K. All-carbon interconnect scheme integrating graphene-wires and carbon-nanotube-vias. In IEEE International Electron Devices Meeting 342–345 (IEEE, 2017).

Shulaker, M. et al. Monolithic 3D integration of logic and memory: carbon nanotube FETs, resistive RAM, and silicon FETs. In IEEE International Electron Devices Meeting 638–641 (IEEE, 2014).

Zhang, D., Yeh, C., Cao, W. & Banerjee, K. 0.5T0.5R—an ultracompact RRAM cell uniquely enabled by van der Waals heterostructures. IEEE Trans. Electron Devices 68, 2033–2040 (2021). A novel FET-RRAM hybrid device.

Silver, D. et al. Mastering the game of Go with deep neural networks and tree search. Nature 529, 484–489 (2016).

Gonzalez-Zalba, M. et al. Scaling silicon-based quantum computing using CMOS technology. Nat. Electron. 4, 872–884 (2021).

Maurand, R. et al. A CMOS silicon spin qubit. Nat. Commun. 7, 13575 (2016). Demonstration of a spin qubit based on CMOS technology.

Merolla, P. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345, 668–673 (2014).

Davies, M. et al. Loihi: a neuromorphic manycore processor with on-chip learning. IEEE Micro 38, 82–99 (2018).

Burd, T. et al. Zen3: the AMD 2nd-generation 7nm x86-64 microprocessor core. In IEEE International Solid-State Circuits Conference 1–3 (IEEE, 2022).

Acknowledgements

K.B. acknowledges support from the Army Research Office (grant W911NF1810366), the Air Force Office of Scientific Research (grant FA9550-18-1-0448), the Japan Science and Technology Agency CREST Program (grant SB180064) and the National Science Foundation (grant CCF 2132820). K.B. thanks the following individuals for their selfless support during the organization of the collaboration: T. Ernst, CEA-LETI, Grenoble, France; T. Sakurai, The University of Tokyo, Tokyo, Japan; J. Welser, IBM Almaden Research Centre, San Jose, USA. K.B. also thanks S. Oda, Tokyo Institute of Technology, Ōokayama, Japan, for useful discussions.

Author information

Authors and Affiliations

Contributions

K.B. organized and led the collaboration. W.C. and K.B. wrote the paper with input from all other authors.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks the anonymous reviewers for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary information

Supplementary Sections 1–4 and Supplementary Figs. 1–2.

Source data

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Cao, W., Bu, H., Vinet, M. et al. The future transistors. Nature 620, 501–515 (2023). https://doi.org/10.1038/s41586-023-06145-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-023-06145-x

This article is cited by

-

Three-dimensional integration of two-dimensional field-effect transistors

Nature (2024)

-

An ultra energy-efficient hardware platform for neuromorphic computing enabled by 2D-TMD tunnel-FETs

Nature Communications (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.