Abstract

Optoelectronic logic gates (OELGs) are promising building blocks for next-generation logic circuits and potential applications in light detection and ranging, machine vision and real-time video analysis. On-chip OELGs operating at telecom wavelengths are highly desirable for integration with the growing possibilities offered by silicon-based optoelectronics. However, at present operations are limited to linear logic functions in the ultraviolet or visible range and high-performance OELGs for multiple logic functions are lacking. Here we integrate up to three silicon waveguides with black phosphorus for optoelectronic logic operations at 1.55 μm. We demonstrate linear (AND, OR, NOT, NAND, NOR) and nonlinear (XOR and XNOR) OELGs by programming optical inputs into the waveguides and reading out electronic signals. The devices exhibit a responsivity as high as 0.35 A W−1 and a 3 dB bandwidth of 230 MHz. The combination of a photovoltaic OR gate and a voltage-switchable AND gate enables two-layer composite logic computing in the form (A + B)C. We also demonstrate symbol recognition, edge extraction, image fusion and encryption/decryption performed by these OELGs. This work paves the way for the development of new optoelectronic logic computing circuits.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$209.00 per year

only $17.42 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

All of the data are presented in the main text and the Supplementary Information. The figures are also available via Figshare at https://doi.org/10.6084/m9.figshare.24056781. Data that support the findings of this study are available from the corresponding authors upon reasonable request. The 3D car models shown in Fig. 5 are available from TurboSquid at https://www.turbosquid.com/zh_cn/3d-model/free/cartoon-car?file_type=194%2C115. Source data are provided with this paper.

References

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Caulfield, H. J. & Dolev, S. Why future supercomputing requires optics. Nat. Photon. 4, 261–263 (2010).

Fu, Y. et al. All-optical logic gates based on nanoscale plasmonic slot waveguides. Nano Lett. 12, 5784–5790 (2012).

Cheng, Z. et al. Device-level photonic memories and logic applications using phase-change materials. Adv. Mater. 30, e1802435 (2018).

Zhang, K., Meng, D., Bai, F., Zhai, J. & Wang, Z. L. Photon‐memristive system for logic calculation and nonvolatile photonic storage. Adv. Funct. Mater. 30, 2002945 (2020).

Hao, Z., Yan, Y., Shi, Y. & Li, Y. Emerging logic devices beyond CMOS. J. Phys. Chem. Lett. 13, 1914–1924 (2022).

Zeng, S. et al. An application-specific image processing array based on WSe2 transistors with electrically switchable logic functions. Nat. Commun. 13, 56 (2022).

Chen, H. et al. Logic gates based on neuristors made from two-dimensional materials. Nat. Electron. 4, 399–404 (2021).

Zhou, F. et al. Optoelectronic resistive random access memory for neuromorphic vision sensors. Nat. Nanotechnol. 14, 776–782 (2019).

Jang, H. et al. An atomically thin optoelectronic machine vision processor. Adv. Mater. 32, e2002431 (2020).

Atabaki, A. H. et al. Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip. Nature 556, 349–354 (2018).

Zhou, F., Chen, J., Tao, X., Wang, X. & Chai, Y. 2D materials based optoelectronic memory: convergence of electronic memory and optical sensor. Research 2019, 9490413 (2019).

Wang, X. et al. Ultrafast, superhigh gain visible-blind UV detector and optical logic gates based on nonpolar a-axial GaN nanowire. Nanoscale 6, 12009–12017 (2014).

Kim, J. et al. Photon-triggered nanowire transistors. Nat. Nanotechnol. 12, 963–968 (2017).

Chen, J. et al. Work‐function‐tunable MXenes electrodes to optimize p‐CsCu2I3/n‐Ca2Nb3‐xTaxO10 junction photodetectors for image sensing and logic electronics. Adv. Funct. Mater. 32, 2201066 (2022).

Pei, J., Wu, X., Liu, W. J., Zhang, D. W. & Ding, S. J. Photoelectric logic and in situ memory transistors with stepped floating gates of perovskite quantum dots. ACS Nano 16, 2442–2451 (2022).

Kim, B. J. et al. Highly transparent phototransistor based on quantum-dots and ZnO bilayers for optical logic gate operation in visible-light. RSC Adv. 10, 16404–16414 (2020).

Li, L. et al. Room-temperature valleytronic transistor. Nat. Nanotechnol. 15, 743–749 (2020).

Boolakee, T. et al. Light-field control of real and virtual charge carriers. Nature 605, 251–255 (2022).

Kim, Y. L. et al. Voltage-switchable photocurrents in single-walled carbon nanotube–silicon junctions for analog and digital optoelectronics. Nat. Photon. 8, 239–243 (2014).

Youngblood, N., Chen, C., Koester, S. J. & Li, M. Waveguide-integrated black phosphorus photodetector with high responsivity and low dark current. Nat. Photon. 9, 247–252 (2015).

Chen, Y. et al. Unipolar barrier photodetectors based on van der Waals heterostructures. Nat. Electron. 4, 357–363 (2021).

Wu, P. et al. Van der Waals two-color infrared photodetector. Light Sci. Appl. 11, 6 (2022).

Xia, F., Mueller, T., Lin, Y.-M., Valdes-Garcia, A. & Avouris, P. Ultrafast graphene photodetector. Nat. Nanotechnol. 4, 839–843 (2009).

Mueller, T., Xia, F. & Avouris, P. Graphene photodetectors for high-speed optical communications. Nat. Photon. 4, 297–301 (2010).

Gan, X. et al. Chip-integrated ultrafast graphene photodetector with high responsivity. Nat. Photon. 7, 883–887 (2013).

Pospischil, A. et al. CMOS-compatible graphene photodetector covering all optical communication bands. Nat. Photon. 7, 892–896 (2013).

Lin, H. et al. Chalcogenide glass-on-graphene photonics. Nat. Photon. 11, 798–805 (2017).

Flöry, N. et al. Waveguide-integrated van der Waals heterostructure photodetector at telecom wavelengths with high speed and high responsivity. Nat. Nanotechnol. 15, 118–124 (2020).

Wang, X., Cheng, Z., Xu, K., Tsang, H. K. & Xu, J.-B. High-responsivity graphene/silicon-heterostructure waveguide photodetectors. Nat. Photon. 7, 888–891 (2013).

Shan, Z. et al. Phonon-assisted electro-optical switches and logic gates based on semiconductor nanostructures. Adv. Mater. 31, e1901263 (2019).

Phare, C. T., Daniel Lee, Y.-H., Cardenas, J. & Lipson, M. Graphene electro-optic modulator with 30 GHz bandwidth. Nat. Photon. 9, 511–514 (2015).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Behura, S. K., Wang, C., Wen, Y. & Berry, V. Graphene–semiconductor heterojunction sheds light on emerging photovoltaics. Nat. Photon. 13, 312–318 (2019).

Ahmetoglu, M. & Akay, S. K. Determination of the parameters for the back-to-back switched Schottky barrier structures. Curr. Appl. Phys. 10, 652–654 (2010).

Chiquito, A. J. et al. Back-to-back Schottky diodes: the generalization of the diode theory in analysis and extraction of electrical parameters of nanodevices. J. Phys. Condens. Matter 24, 225303 (2012).

Osvald, J. Back-to-back connected asymmetric Schottky diodes with series resistance as a single diode. Phys. Stat. Solidi A 212, 2754–2758 (2015).

Liu, C. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019).

Zhihong, L. & Guifang, L. Ultrahigh-speed reconfigurable logic gates based on four-wave mixing in a semiconductor optical amplifier. IEEE Photon. Technol. Lett. 18, 1341–1343 (2006).

Ashtiani, F., Geers, A. J. & Aflatouni, F. An on-chip photonic deep neural network for image classification. Nature 606, 501–506 (2022).

Kim, W. et al. Perovskite multifunctional logic gates via bipolar photoresponse of single photodetector. Nat. Commun. 13, 720 (2022).

Yang, C. M. et al. Bidirectional all‐optical synapses based on a 2D Bi2O2Se/graphene hybrid structure for multifunctional optoelectronics. Adv. Funct. Mater. 30, 2001598 (2020).

Li, M. et al. The fabrication of a self-powered CuInS2/TiO2 heterojunction photodetector and its application in visible light communication with ultraviolet light encryption. J. Mater. Chem. C 9, 14613–14622 (2021).

Acknowledgements

This work was financially supported by the Strategic Priority Research Program (B) of the Chinese Academy of Sciences (grant no. XDB0580000 to W.H.), the National Natural Science Foundation of China (grant nos. 62205082 to T.H., 62104053 to Q.L., 62105349 to Z.W., 62134009 to P.W. and 61975179 and 92150302 to H.L.), the Science and Technology Commission of Shanghai Municipality (grant nos. 23WZ2500400 and 21JC1406100 to W.H. and 22ZR1472300 to T.H.), the China Postdoctoral Science Foundation (grant no. 2021M700156 to T.H.), the Hangzhou Key Research and Development Program of China (grant no. 20212013B01 to W.H.) and the open fund of the State Key Laboratory of Infrared Physics (grant no. SITP-NLIST-ZD-2022-02 to H.L.). We thank ZJU Micro-Nano Fabrication Center at Zhejiang University.

Author information

Authors and Affiliations

Contributions

W.H. and H.L. conceived and supervised the project. T.H., Z.W. and Q.L. designed the experiments. T.H. and H.M. fabricated the devices and performed the electrical and photoresponse characterizations. Q.L., P.M. and A.R. performed the technology computer-aided design calculations. S. Liu simulated the application demonstration. Z.W., S.D., S. Lin, F.Z., K.Z. and P.W. performed the experiments. J. Wang, Y.Y., J. Wu and L.L. assisted with the data analysis and interpretation. H.W. provided the circuit configuration. W.H., H.L., T.H., H.M. and T.X. wrote the manuscript. All authors discussed the results and revised the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Photonics thanks Ye Zhou and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

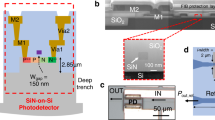

Extended Data Fig. 1 Optical microscopy images of OELGs.

(a) Optical microscopy image of integrated Au/BP/Au device with three waveguides. (b) Enlarged optical microscopy image of integrated Au/BP/Au device. (c) Enlarged optical microscopy image of optoelectronic logic AND gate. (d) Optical microscopy image of optoelectronic logic AND gate.

Extended Data Fig. 2 Fabrication process of integrated device.

(a) The devices were fabricated on the 220 nm SOI substrate. First, the photoresist (maN2403) was patterned through Electron Beam Lithography (EBL, Raith Voyager). And, the ridge waveguide (500 nm width) was etched by 150 nm through Inductively Coupled Plasma (OXFORD, Plasmapro100 Cobra 180). Then, the pad window (arp6200.13) was patterned, Ti (5 nm)/Au (100 nm) was deposited. Finally, BP was transferred by the dry method above three waveguides and two electrodes. The h-BN or PMMA was used as the passivation layer to protect BP. Grating couplers were used as fiber-to-waveguide couplings with a period of 0.67 μm, and a duty cycle of 0.5. (b) Transmission spectrum of WG1, WG2, and WG3. (c) Absorption of BP as a function of the wavelength. Due to the narrow bandgap, BP has a stable absorption at the S and C bands.

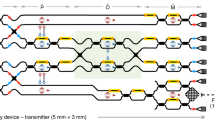

Extended Data Fig. 3 Layout of waveguide chip.

(a) Optical loss as a function of the gap between waveguide and metal electrode. (b) Relationship of coupling length and gap between two waveguides. (c) Limit scale of three waveguide device with three waveguides. (d) The size of fabricated Au/BP/Au device with three waveguides. (e) The size of fabricated optoelectronic logic AND device.

Extended Data Fig. 4 STEM results of integrated Au/BP/Au device.

(a) SEM picture of Au/BP/Au device from the top view. (b) Cross-section scanning transmission electron microscope (STEM) image of Au/BP/Au device. (c) The thickness of BP is approximately 11.7 nm. (d) Enlarged STEM image of Au/BP/Au device.

Extended Data Fig. 5 Simulated optoelectronic characteristics of OELGs.

(a) Electric potential distribution of Au/BP/Au device and an “M” shape potential distribution of optoelectronic logic AND device simulated by Sentaurus TCAD. (b) Surface potential difference between BP and Au by Kelvin probe force microscopy. The results show that the work function of BP is around 0.38 eV higher than that of Au. The work function difference between BP and Au is smaller than that of the theoretical value, which may be attributed to the surface oxidation of BP. (c) Diffusion process of photogenerated electrons and holes in Au/BP/Au device under WG1 triggering. (d) Energy band diagram for drift process of photogenerated electrons and holes in Au/BP/Au device under WG1 triggering. (e) Simulated structure of Au/BP/Au device and illumination mode. The light spot diameter is approximately 1 µm. (f) Simulated I-V curves of Au/BP/Au device under light illumination of different spot positions.

Extended Data Fig. 6 Performance of MoS2/BP/MoS2 and Au/BP/Au for XOR gate.

(a) Schematic of MoS2/BP/MoS2 device with logic XOR function. (b) Optical microscope image of MoS2/BP/MoS2 device. (c) Raman spectra of BP, MoS2, and overlapped region. (d) Output characteristics of device in dark and under 1.55 μm light illumination. (e) Output current of logic XOR gate with four input states. Inset is truth table of logic XOR. (f) External quantum efficiency (EQE) as a function of incident light power for MoS2/BP/MoS2 device at zero bias voltage. (g) Responsivity of Au/BP/Au device as a function of the incident light power at zero bias voltage. (h) EQE of Au/BP/Au device as a function of the incident light power at zero bias. (i) 3 dB bandwidth of Au/BP/Au device under 1.55 μm light illumination from WG1.

Extended Data Fig. 7 Logic XNOR, NAND, NOR, and NOT gates.

(a) Fiber-coupled measurement system. A tunable light (Santec TSL 550) was used as the source and amplified by EDFA. The light was coupled to the grating coupler in a chip, and the rest light was monitored by a power meter. Device was biased by a source meter (Keithley 2450). Two light beams with the same power was obtained with a 1×2 optical fiber splitter. The optical switch was used to open or close the optical circuits. (b) Output characteristic curves of Au/BP/Au device with three waveguides. Design scheme of (c) logic XNOR gate, (d) logic NAND gate, (e) logic NOR gate, and (f) logic NOT gate. For NOT gate, WG3 serve as input 1. The input signal with the value of 0 or 1 indicates zero and high light power. The high and low output current represent OUT-1 and OUT-0, respectively. When sequence signals (IN-0, IN-1, bias of Voc) are sent, a logic NOT gate can be constructed.

Extended Data Fig. 8 Integrated Au/InSe/Au and Au/BP/Au under free space for OELGs.

(a) Optical microscopy image of Au/InSe/Au device. (b) Raman spectrum of the InSe. (c) Output characteristic curves of Au/InSe/Au device in the dark and under 1.55 μm light illumination. It is found that OR, AND, and XNOR logic functions can be constructed in the integrated Au/BP/Au device. (d) Output current for four states of logic OR gate with all-optical inputs at a bias voltage of 3 V. (e) Output current for four input states with mixed optical and electrical inputs. (f) Output current for four input states of logic XNOR gate with mixed optical and electrical inputs. (g) Optical microscopy image of Au/BP/Au device without integrating with waveguides. The red circles mean the position of the localized light spot. (h) Output characteristics of Au/BP/Au device under spot illumination. (i) Output current for four input states of logic XNOR gate with mixed optical and electrical inputs.

Supplementary information

Supplementary Information

Supplementary Figs. 1–8, Notes 1 and 2 and Tables 1 and 2.

Source data

Source Data Fig. 1

Statistical source data.

Source Data Fig. 2

Statistical source data.

Source Data Fig. 3

Statistical source data.

Source Data Fig. 4

Statistical source data.

Source Data Fig. 5

Statistical source data.

Source Data Extended Data Fig. 2

Statistical source data.

Source Data Extended Data Fig. 3

Statistical source data.

Source Data Extended Data Fig. 5

Statistical source data.

Source Data Extended Data Fig. 6

Statistical source data.

Source Data Extended Data Fig. 7

Statistical source data.

Source Data Extended Data Fig. 8

Statistical source data.

Source Data Extended Data Table 1

Statistical source data.

Source Data Extended Data Table 2

Statistical source data.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

He, T., Ma, H., Wang, Z. et al. On-chip optoelectronic logic gates operating in the telecom band. Nat. Photon. 18, 60–67 (2024). https://doi.org/10.1038/s41566-023-01309-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41566-023-01309-7

This article is cited by

-

A novel approach to the fabrication of photonic XOR and XNOR gates employing a 2:1 all-optical multiplexer made of nonlinear Kerr type materials

Proceedings of the Indian National Science Academy (2024)