Abstract

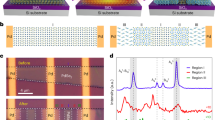

Three-dimensional monolithic integration of memory devices with logic transistors is a frontier challenge in computer hardware. This integration is essential for augmenting computational power concurrent with enhanced energy efficiency in big data applications such as artificial intelligence. Despite decades of efforts, there remains an urgent need for reliable, compact, fast, energy-efficient and scalable memory devices. Ferroelectric field-effect transistors (FE-FETs) are a promising candidate, but requisite scalability and performance in a back-end-of-line process have proven challenging. Here we present back-end-of-line-compatible FE-FETs using two-dimensional MoS2 channels and AlScN ferroelectric materials, all grown via wafer-scalable processes. A large array of FE-FETs with memory windows larger than 7.8 V, ON/OFF ratios greater than 107 and ON-current density greater than 250 μA um–1, all at ~80 nm channel length are demonstrated. The FE-FETs show stable retention up to 10 years by extension, and endurance greater than 104 cycles in addition to 4-bit pulse-programmable memory features, thereby opening a path towards the three-dimensional heterointegration of a two-dimensional semiconductor memory with silicon complementary metal–oxide–semiconductor logic.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

All data needed to evaluate the conclusions of this study are present in the Article and its Supplementary Information.

References

Migliato Marega, G. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

Wang, Z. et al. Resistive switching materials for information processing. Nat. Rev. Mater. 5, 173–195 (2020).

Yang, R. et al. Ternary content-addressable memory with MoS2 transistors for massively parallel data search. Nat. Electron. 2, 108–114 (2019).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Dutta, S. et al. Monolithic 3D integration of high endurance multi-bit ferroelectric FET for accelerating compute-in-memory. In 2020 IEEE International Electron Devices Meeting (IEDM) 36.4.1–36.4.4 (IEEE, 2020).

Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 3, 588–597 (2020).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Polyushkin, D. K. et al. Analogue two-dimensional semiconductor electronics. Nat. Electron. 3, 486–491 (2020).

Ni, K. et al. Ferroelectric ternary content-addressable memory for one-shot learning. Nat. Electron. 2, 521–529 (2019).

Wang, D. et al. Ferroelectric switching in sub-20 nm aluminum scandium nitride thin films. IEEE Electron Device Lett. 41, 1774–1777 (2020).

Liu, X. et al. Post-CMOS compatible aluminum scandium nitride/2D channel ferroelectric field-effect-transistor memory. Nano Lett. 21, 3753–3761 (2021).

Tsai, S.-L. et al. Room-temperature ÿdeposition of a poling-free ferroelectric AlScN film by reactive sputtering. Appl. Phys. Lett. 118, 082902 (2021).

Wang, D. et al. Sub-microsecond polarization switching in (Al,Sc)N ferroelectric capacitors grown on complementary metal-oxide-semiconductor-compatible aluminum electrodes. Phys. Status Solidi RRL 15, 2000575 (2021).

Islam, M. R. et al. On the exceptional temperature stability of ferroelectric Al1-xScxN thin films. Appl. Phys. Lett. 118, 232905 (2021).

Fichtner, S., Wolff, N., Lofink, F., Kienle, L. & Wagner, B. AlScN: a III-V semiconductor based ferroelectric. J. Appl. Phys. 125, 114103 (2019).

Lederer, M. et al. Local crystallographic phase detection and texture mapping in ferroelectric Zr doped HfO2 films by transmission-EBSD. Appl. Phys. Lett. 115, 222902 (2019).

Dragoman, M. et al. Ferroelectrics at the nanoscale: materials and devices—a critical review. Crit. Rev. Solid State Mater. Sci. 1–19 (2022).

Siao, M. D. et al. Two-dimensional electronic transport and surface electron accumulation in MoS2. Nat. Commun. 9, 1442 (2018).

Mulaosmanovic, H. et al. Ferroelectric field-effect transistors based on HfO2: a review. Nanotechnology 32, 502002 (2021).

Mikolajick, T. et al. Next generation ferroelectric materials for semiconductor process integration and their applications. J. Appl. Phys. 129, 100901 (2021).

Aljarb, A. et al. Ledge-directed epitaxy of continuously self-aligned single-crystalline nanoribbons of transition metal dichalcogenides. Nat. Mater. 19, 1300–1306 (2020).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Zhang, Y., Brar, V. W., Girit, C., Zettl, A. & Crommie, M. F. Origin of spatial charge inhomogeneity in graphene. Nat. Phys. 5, 722–726 (2009).

Liu, Y.-S. & Su, P. Variability analysis for ferroelectric FET nonvolatile memories considering random ferroelectric-dielectric phase distribution. IEEE Electron Device Lett. 41, 369–372 (2020).

Lederer, M. et al. Ferroelectric field effect transistors as a synapse for neuromorphic application. IEEE Trans. Electron Devices 68, 2295–2300 (2021).

Luo, Y et al. MLP+NeuroSimV3.0: improving on-chip learning performance with device to algorithm optimizations. In ICONS ’19: Proc. International Conference on Neuromorphic Systems 1–7 (ACM, 2019).

Ko, C. et al. Ferroelectrically gated atomically thin transition-metal dichalcogenides as nonvolatile memory. Adv. Mater. 28, 2923–2930 (2016).

Xu, L. et al. Ferroelectric-modulated MoS2 field-effect transistors as multilevel nonvolatile memory. ACS Appl. Mater. Interfaces 12, 44902–44911 (2020).

Young Tack Lee, H. K. et al. Nonvolatile ferroelectric memory circuit using black phosphorus nanosheet-based field-effect transistors with P(VDF-TrFE) polymer. ACS Nano 9, 10394–10401 (2015).

Jiang, X. et al. Ferroelectric field-effect transistors based on WSe2/CuInP2S6 heterostructures for memory applications. ACS Appl. Electron. Mater. 3, 4711–4717 (2021).

Si, M., Liao, P. Y., Qiu, G., Duan, Y. & Ye, P. D. Ferroelectric field-effect transistors based on MoS2 and CuInP2S6 two-dimensional van der Waals heterostructure. ACS Nano 12, 6700–6705 (2018).

Wang, X. et al. Ferroelectric FET for nonvolatile memory application with two-dimensional MoSe2 channels. 2D Mater 4, 025036 (2017).

Liu, L. et al. Electrical characterization of MoS2 field-effect transistors with different dielectric polymer gate. AIP Adv 7, 065121 (2017).

Jiawen, X. et al. Experimental demonstration of HfO2-based ferroelectric FET with MoS2 channel for high-density and low-power memory application. In 2021 Silicon Nanoelectronics Workshop (SNW) 1–2 (IEEE, 2021).

Huang, K. et al. Hf0.5Zr0.5O2 ferroelectric embedded dual-gate MoS2 field effect transistors for memory merged logic applications. IEEE Electron Device Lett. 41, 1600–1603 (2020).

Zhang, S. et al. Low voltage operating 2D MoS2 ferroelectric memory transistor with Hf1–xZrxO2 gate structure. Nanoscale Res. Lett. 15, 157 (2020).

Acknowledgements

This material is based on work supported by the Defense Advanced Research Projects Agency (DARPA) TUFEN program under agreement no. HR00112090046. The work was carried out in part at the Singh Center for Nanotechnology at the University of Pennsylvania, which is supported by the National Science Foundation (NSF) National Nanotechnology Coordinated Infrastructure Program (NSF grant NNCI-1542153). H.M.K., K.K. and D.J. acknowledge partial support from the Penn Center for Undergraduate Research and Fellowships. We gratefully acknowledge the use of the facilities and instrumentation supported by NSF through the University of Pennsylvania Materials Research Science and Engineering Center (MRSEC) (DMR-1720530). P.K., E.A.S. and D.J. also acknowledge partial support from the NSF DMR Electronic Photonic and Magnetic Materials (EPM) core program (grant no. DMR-1905853) as well as the University of Pennsylvania Laboratory for Research on the Structure of Matter, a Materials Research Science and Engineering Center (MRSEC) supported by the NSF (no. DMR-1720530). A.A., Y.W. and V.C.T. are indebted to the support from the King Abdullah University of Science and Technology (KAUST) Solar Center and Office of Sponsored Research (OSR) under award no. OSR-2018-CARF/CCF-3079. The MOCVD-grown MoS2 monolayer samples were provided by the 2D Crystal Consortium—Materials Innovation Platform (2DCC-MIP) facility at the Pennsylvania State University, which is funded by the NSF under cooperative agreement nos. DMR-1539916 and DMR-2039351. S.S. acknowledges support from the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (grant no. 2021R1A6A3A14038492). K.K. acknowledges support from the NSF Graduate Research Fellowship Program (GRFP), Fellow ID: 2022338725. N.T. acknowledges that this material is based upon work supported by the National Science Foundation Graduate Research Fellowship Program under Grant No. DGE1255832.

Author information

Authors and Affiliations

Contributions

D.J., R.H.O. and K-H.K. conceived the idea of using large-area 2D semiconductors with AlScN to make the CMOS BEOL-compatible FE-FETs at scale and with scaled dimensions. K.-H.K. designed the experiments and performed the device fabrication and characterization of the samples. K.-H.K. and D.J. wrote the manuscript. M.M.A.F. and K.-H.K. conducted the P–E loop and PUND measurements and R.H.O. supervised them. J.Z. and K.-H.K. performed sputtering to prepare the various AlScN substrates and R.H.O. supervised them. P.M. and P.K. performed the TEM and SEM characterizations, respectively. P.K. prepared the cross-sectional lamella for the subsequent TEM observation. E.A.S. supervised the microscopy efforts. N.T. prepared the two-inch wafer-scale MoS2 using MOCVD and J.M.R. supervised it. CVD-based two-inch wafer-scale MoS2 was prepared by A.A., Y.W., J.-H.F. and M.H., and V.T. supervised them. K.-H.K. and P.K. performed the wet transfer of MoS2 on AlScN and SiO2. S.O. and K.K. contributed to the MLP-based artificial neural network simulation and technology computer-aided design simulation. K.-H.K. and H.M.K. performed the electrical measurements of 130 FE-FET arrays. S.S. and G.K. performed the device fabrication for revision. Z.T. developed the recipe for electron-beam lithography. All the authors contributed to the discussion and analysis of the results.

Corresponding authors

Ethics declarations

Competing interests

D.J., R.H.O., K.-H.K. and E.A.S. are co-inventors on a patent (US Patent App. 17/354,256) based on this work. The other authors declare no competing interests.

Peer review

Peer review information

Nature Nanotechnology thanks Kah-Wee Ang and Weida Hu for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–27.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, KH., Oh, S., Fiagbenu, M.M.A. et al. Scalable CMOS back-end-of-line-compatible AlScN/two-dimensional channel ferroelectric field-effect transistors. Nat. Nanotechnol. 18, 1044–1050 (2023). https://doi.org/10.1038/s41565-023-01399-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-023-01399-y

This article is cited by

-

Nonvolatile and reconfigurable two-terminal electro-optic duplex memristor based on III-nitride semiconductors

Light: Science & Applications (2024)

-

High-performance ferroelectric field-effect transistors with ultra-thin indium tin oxide channels for flexible and transparent electronics

Nature Communications (2024)

-

A 2D route to 3D computer chips

Nature (2024)

-

Ferroelectric memory for back-end-of-line 3D integration

Nature Reviews Materials (2023)

-

p-Type Two-Dimensional Semiconductors: From Materials Preparation to Electronic Applications

Nano-Micro Letters (2023)