Abstract

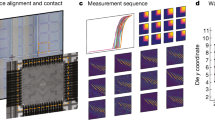

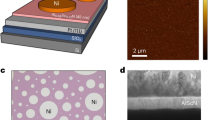

As conventional circuits based on field-effect transistors are approaching their physical limits due to quantum phenomena, semi-floating gate transistors have emerged as an alternative ultrafast and silicon-compatible technology. Here, we show a quasi-non-volatile memory featuring a semi-floating gate architecture with band-engineered van der Waals heterostructures. This two-dimensional semi-floating gate memory demonstrates 156 times longer refresh time with respect to that of dynamic random access memory and ultrahigh-speed writing operations on nanosecond timescales. The semi-floating gate architecture greatly enhances the writing operation performance and is approximately 106 times faster than other memories based on two-dimensional materials. The demonstrated characteristics suggest that the quasi-non-volatile memory has the potential to bridge the gap between volatile and non-volatile memory technologies and decrease the power consumption required for frequent refresh operations, enabling a high-speed and low-power random access memory.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Wang, P. F. et al. A semi-floating gate transistor for low-voltage ultrafast memory and sensing operation. Science 341, 640–643 (2013).

Makarov, A., Sverdlov, V. & Selberherr, S. Emerging memory technologies: trends, challenges, and modeling methods. Microelectron. Reliab. 52, 628–634 (2012).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotech. 8, 13–24 (2013).

International Technology Roadmap for Semiconductors 2.0 (ITRS, 2015); http://www.itrs2.net/

Lembke, D. & Kis, A. Breakdown of high-performance monolayer MoS2 transistors. ACS Nano 6, 10070–10075 (2012).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotech. 6, 147–150 (2011).

Fang, H. & Chuang et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Deng, Y. et al. Black phosphorus-monolayer MoS2 van der Waals heterojunction p-n diode. ACS Nano 8, 8292–8299 (2014).

Roy, K. et al. Graphene-MoS2 hybrid structures for multifunctional photoresponsive memory devices. Nat. Nanotech. 8, 826–830 (2013).

Baugher, B. W., Churchill, H. O., Yang, Y. & Jarilloherrero, P. Optoelectronic devices based on electrically tunable p–n diodes in a monolayer dichalcogenide. Nat. Nanotech. 9, 262–267 (2014).

Yu, Z. et al. Analyzing the carrier mobility in transition metal dichalcogenide MoS2 field effect transistors. Adv. Funct. Mater. 27, 1604093 (2017).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Zhao, W. et al. Evolution of electronic structure in atomically thin sheets of WS2 and WSe2. ACS Nano 7, 791–797 (2012).

Zhang, Y. et al. Direct observation of the transition from indirect to direct bandgap in atomically thin epitaxial MoSe2. Nat. Nanotech. 9, 111–115 (2014).

Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotech. 9, 372–377 (2014).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Yu, W. J., Chae, S. H., Lee, S. Y., Duong, D. L. & Lee, Y. H. Ultra transparent, flexible single walled carbon nanotube non-volatile memory device with an oxygen decorated graphene electrode. Adv. Mater. 23, 1889–1893 (2011).

Lee, S. et al. Impact of gate work-function on memory characteristics in Al2O3/HfOx/Al2O3/graphene charge-trap memory devices. Appl. Phys. Lett. 100, 023109 (2012).

Kim, S. M. et al. Transparent and flexible graphene charge-trap memory. ACS Nano 6, 7879–7884 (2012).

Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano 7, 3246–3252 (2013).

Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 4, 1624 (2013).

Zhang, E. et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 9, 612–619 (2014).

Vu, Q. A. et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat. Commun. 7, 12725 (2016).

He, G. et al. Thermally assisted nonvolatile memory in monolayer MoS2 transistors. Nano Lett. 16, 6445 (2016).

Lee, H. S. et al. MoS2 nanosheets for top gate nonvolatile memory transistor channel. Small 8, 3111–3115 (2012).

Lee, Y. T. et al. Nonvolatile ferroelectric memory circuit using black phosphorus nanosheet-based field-effect transistors with P(VDF-TrFE) polymer. ACS Nano 9, 10394–10401 (2015).

JEDEC Solid State Technology Association Standard JESD79-2b 65 (2005); http://cs.ecs.baylor.edu/~maurer/CSI5338/JESD79-2B.pdf

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Yu, L. et al. Design, modeling and fabrication of CVD grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Yan, R. et al. Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment. Nano Lett. 15, 5791–5798 (2015).

Hong, X. et al. Ultrafast charge transfer in atomically thin MoS2/WS2 heterostructures. Nat. Nanotech. 9, 682–686 (2014).

Ji, Y. et al. Boron nitride as two dimensional dielectric: reliability and dielectric breakdown. Appl. Phys. Lett. 108, 012905 (2016).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 474–479 (2010).

Zeng, H. et al. Optical signature of symmetry variations and spin-valley coupling in atomically thin tungsten dichalcogenides. Sci. Rep. 3, 1608 (2013).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Gong, C., Zhang, H., Wang, W. & Colombo, L. Band alignment of two-dimensional transition metal dichalcogenides: application in tunnel field effect transistors. Appl. Phys. Lett. 103, 053513 (2013).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2012).

Xu, K. et al. Ultrasensitive phototransistors based on few-layered HfS2. Adv. Mater. 27, 7881–7887 (2015).

Shi, H. et al. Exciton dynamics in suspended monolayer and few-layer MoS2 2D crystals. ACS Nano 7, 1072–1080 (2013).

Imam, S. A., Deshpande, T., Guermoune, A., Siaj, M. & Szkopek, T. Charge transfer hysteresis in graphene dual-dielectric memory cell structures. Appl. Phys. Lett. 99, 082109 (2011).

Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano 4, 7221–7228 (2010).

Late, D. J., Liu, B., Matte, H. R., Dravid, V. P. & Rao, C. Hysteresis in single-layer MoS2 field effect transistors. ACS Nano 6, 5635–5641 (2012).

Acknowledgements

This work was supported by the National Natural Science Foundation of China (61622401, 61734003) and the National Key Research and Development Program 2017YFB0405600. P.Z. thanks D. Sandubashao's group for encouragement and help, and P.F. Wang, F. Xiu, Q. Sun and N. Yan for assistance during device fabrication and for fruitful discussions.

Author information

Authors and Affiliations

Contributions

P.Z. conceived the idea and supervised the experiments. C.L. performed the device fabrication and carried out the electrical characteristics measurements. X.Y. and X.S. provided valuable input to the overall experiments. S.D. and D.W.Z. provided input on the experiment conditions. C.L., D.W.Z. and P.Z. wrote the paper with help from all authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figures 1–11, Supplementary Table 1, Supplementary References.

Rights and permissions

About this article

Cite this article

Liu, C., Yan, X., Song, X. et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nature Nanotech 13, 404–410 (2018). https://doi.org/10.1038/s41565-018-0102-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-018-0102-6

This article is cited by

-

High performance artificial visual perception and recognition with a plasmon-enhanced 2D material neural network

Nature Communications (2024)

-

Artificial visual perception neural system using a solution-processable MoS2-based in-memory light sensor

Light: Science & Applications (2023)

-

Epitaxial substitution of metal iodides for low-temperature growth of two-dimensional metal chalcogenides

Nature Nanotechnology (2023)

-

Two-dimensional complementary gate-programmable PN junctions for reconfigurable rectifier circuit

Nano Research (2023)

-

Recent developments in CVD growth and applications of 2D transition metal dichalcogenides

Frontiers of Physics (2023)