Abstract

Multi-valued logic (MVL) circuits based on heterojunction transistor (HTR) have emerged as an effective strategy for high-density information processing without increasing the circuit complexity. Herein, an organic ternary logic inverter (T-inverter) is demonstrated, where a nonvolatile floating-gate flash memory is employed to control the channel conductance systematically, thus realizing the stabilized T-inverter operation. The 3-dimensional (3D) T-inverter is fabricated in a vertically stacked form based on all-dry processes, which enables the high-density integration with high device uniformity. In the flash memory, ultrathin polymer dielectrics are utilized to reduce the programming/erasing voltage as well as operating voltage. With the optimum programming state, the 3D T-inverter fulfills all the important requirements such as full-swing operation, optimum intermediate logic value (~VDD/2), high DC gain exceeding 20 V/V as well as low-voltage operation (< 5 V). The organic flash memory exhibits long retention characteristics (current change less than 10% after 104 s), leading to the long-term stability of the 3D T-inverter. We believe the 3D T-inverter employing flash memory developed in this study can provide a useful insight to achieve high-performance MVL circuits.

Similar content being viewed by others

Introduction

Organic thin-film transistors (OTFTs) have gained tremendous attention as a building block for the next-generation electronic devices such as wearable/stretchable electronics1,2,3, flexible sensors4,5, and electronic skins6,7. With the numerous efforts in the last two decades, the performance of OTFT and OTFT-based integrated circuits (ICs) has been enhanced remarkably8,9,10,11. However, the strong susceptibility of organic materials to high temperature and organic solvent has significantly hampered their compatibility with lithography-based down-scaling12,13. Alternatively, three-dimensional (3D) vertical stacking of OTFTs has been demonstrated to increase the number of transistors per unit area, without reducing the device size14,15,16. Among the various approaches to fabricating vertically stacked devices, such as etching-based via-hole processes or inkjet printing14,15,17, a via-hole-less metal interconnects scheme for OTFTs enabled by forming an insulating layer on a selective area was proposed as an attractive way to minimize damage to the underlying layers or devices16,18.

In addition to the 3D stacking of the devices, multi-valued logic (MVL) devices have emerged as a promising strategy to accommodate the increasing demand for higher data processing capability in advanced electronic systems such as artificial intelligence and internet-of-things (IoT)19,20,21. When compared to conventional binary logic, which has two simple distinct logic states (“0” and “1”), MVL can process signals with fewer interconnects, allowing for a significant reduction in the number of devices and hence the complexity of the ICs22,23. For example, ternary logic can reduce the system complexity reportedly to ~63% compared to the binary logic in principle24. However, the conventional complementary metal-oxide-semiconductor (CMOS) technology requires at least four additional transistors to demonstrate ternary logic, which unavoidably results in increased complexity and power consumption25,26. To overcome these limitations, heterojunction transistors (HTRs) displaying negative differential resistance (NDR) or negative transconductance (NTC) have been proposed by utilizing various device designs and materials such as organic semiconductors27,28,29, 2D materials30,31,32,33,34,35, and organic–inorganic heterostructures36,37,38. The key advantage of the HTR lies in the fact that the ternary logic can be implemented simply by replacing a transistor with an HTR without increasing the number of devices to achieve the ternary logic.

Organic HTRs have been developed based on a partial junction between p-and n-type organic semiconductors in the active layer, using the intrinsic semiconducting feature of organic semiconductors that makes them suitable for achieving highly ordered heterointerfaces20,28. Such anti-ambipolar transistors (AATs) with NTC behavior displayed a “flipped V”-shaped transfer characteristic, which could create intermediate logic states27. Despite the successful demonstration of the ternary logic inverter (T-inverter), however, the full swing of the output voltage (VOUT) was hardly achieved, mainly due to the inherently low on/off current ratio (Ion/Ioff) of the AATs27,39. To address this issue, a modified HTR structure was proposed where one of the semiconducting layers was in contact with both source (S) and drain (D) electrodes (main-semiconductor), on top of the partial semiconducting layer with the opposite polarity (sub-semiconductor)21,29. In contrast with AATs, the main-semiconductor connected from S to D electrodes led to high on-current (Ion) at higher gate voltage (VG) while maintaining the NTC characteristics in the modified HTR, which enabled the full-swing operation of the T-inverter29. However, it is still challenging to satisfy all the important requirements of T-inverters including (i) a well-defined intermediate logic state with the optimized value (VOUT~half of the supply voltage (VDD/2), logic “1”) in the sufficient input voltage (VIN) range, (ii) full-swing operation (VOUT from VDD (logic “2”) to ground (GND) (logic “0”)) as well as (iii) hysteresis-free, low-voltage operation. One of the most critical obstacles to achieving the optimum intermediate logic value is the mismatch in channel conductance between the HTR and complementary transistor, particularly in the NTC range. Therefore, it is imperative to develop a systematic strategy to optimize T-inverter and constituent transistor performance.

As an effective method to systematically control the electrical characteristics (i.e., channel conductance) of a transistor, a nonvolatile floating-gate (FG) flash memory was utilized and integrated with HTR to implement a T-inverter in this study. The implementation of the nonvolatile FG flash memory enabled systematic circuit programmability, where the precise control of the threshold voltage (VT) allows for enhancement of the T-inverter performance by optimizing the intermediate logic state. Furthermore, by utilizing the via-hole-less metal interconnection method16,18, the flash memory on the first floor was vertically integrated with the HTR on the second floor to realize a vertically stacked, 3D T-inverter. Considering the unit inverter logic, the vertical stacking effect can improve the information density by a factor of 2, and the ternary logic effect can enhance the information density by a factor of 1.5, so the proposed vertically stacked ternary circuit can further improve the information density by a factor of 3. Moreover, the integration density can increase exponentially as the circuit configuration becomes more complex. It is worthwhile to note that the introduction of flash memory is a powerful strategy in that the adjustability of the channel dimension is limited in the stacked structure.

In the 3D T-inverter fabrication process, a vapor-phase deposition method, termed initiated chemical vapor deposition (iCVD) process was introduced to deposit the high-performance polymer dielectric layers while minimizing the damage to the underlying devices40,41,42,43. The polymer dielectric materials were introduced with an optimized dielectric layer configuration, which reduced the programming/erasing voltage (Vprg/Vers), and enabled the operating voltage <5 V, which is comparable to or even lower than those obtained in the previous organic 3D logic circuits14,15,16. Meanwhile, the high device-to-device uniformity was also fully retained. Most of all, the solvent-free deposition process was capable of in situ patterning of the dielectric layer simply through shadow mask during the deposition process, which allowed etching-free, via-hole-less metal interconnection, and thus 3D vertical integration of the HTR and flash memory devices16. According to the programming/erasing states of the flash memory device, the intermediate logic value of the 3D T-inverter could be controlled systematically. The 3D T-inverter with the optimized memory programming state exhibited long retention characteristics and operational stability against the repeated operation cycles.

Results

Design of the organic 3D T-inverter

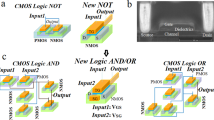

The schematic illustration for the fabrication process and the structure of the vertically stacked organic ternary logic inverter are shown in Fig. 1a, b, respectively. All the dielectric layers were deposited by iCVD process and patterned in situ through a shadow mask to achieve via-hole-less metal interconnection16. Also, a 1 μm-thick interlayer dielectric (ILD) was imposed between the unit devices to electrically isolate the flash memory and HTR. A schematic illustration of the device structure with various viewpoints according to the fabrication process is shown in Supplementary Fig. 1. To optimize the voltage transfer characteristic (VTC) and the intermediate logic state of the resulting 3D T-inverter, organic flash memory with FG was used to match the channel conductance with the HTR in the NTC area (Fig. 1c, d). The n-type flash memory and HTR were utilized as a pull-down and pull-up transistor and those devices were fabricated on the first and second floor, respectively. It should be noted that the drain electrode on top of the heterojunction in HTR was interconnected to the drain electrode in the flash memory and used as an output electrode in the inverter operation to induce an intermediate logic state29. The chemical structures of the polymer dielectrics and organic semiconductors used in this study are shown in Fig. 2a. For the polymer dielectric layers, poly(2-cyanoethyl acrylate-co-diethylene glycol divinyl ether) [p(CEA-co-DEGDVE)] (named pC1D1), whose composition was optimized to maximize the dielectric constant (the dielectric constant, k > 6) while retaining the insulating performance (breakdown field, Ebreak > 3 MV/cm)42, was used as blocking dielectric layer (BDL) in this study. Poly(1,3,5-trivinyl-1,3,5-trimethyl cyclotrisiloxane) (pV3D3) with a low dielectric constant (k < 2.3)40 was also employed as a tunneling dielectric layer (TDL) in the flash memory, and gate dielectric layer (GDL) in the HTR to provide a non-polar interface for the facilitated charge transport in the organic semiconductors44. The dielectric layers were deposited using the iCVD process, which commonly exhibited robust insulating performance even at a thickness of 100 nm for BDL and 24 nm for TDL (Supplementary Figs. 2 and 3). Dinaphtho[2,3-b:2’,3’-f]thieno[3,2-b]thiophene (DNTT) and N,N’-ditridecylperylene-3,4,9,10-tetracarboxylic diimide (PTCDI-C13) were utilized as p- and n-type organic semiconductors, respectively, which show charge transport characteristics that are comparable to each other29,45. The high-resolution transmission electron microscope (HRTEM) images of the flash memory, 3D T-inverter and HTR are shown in Fig. 2b–d, respectively. The vertical integration of the device was achieved without damaging the underlying layers or devices as all the fabrication processes were based on solvent-free, dry methods with mild process conditions16,40,42. In addition, no notable defect or intermixing was observed in the energy dispersive spectroscopy (EDS) mapping analysis (Supplementary Fig. 4). These results clearly exhibited that the flash memory-integrated organic 3D T-inverter was successfully fabricated in the vertically stacked structure which can enhance the integration density by increasing the number of devices per unit area14,15,16.

a A schematic of device fabrication and b the vertically stacked 3-dimensional (3D) ternary logic inverter (T-inverter) consisting of the flash memory and heterojunction transistor (HTR). The schematic illustrations of c the transfer curve shift along with the memory programming, and d corresponding voltage transfer characteristic (VTC) of the 3D T-inverter.

a The chemical structures of the polymer dielectrics and organic semiconductors used in this study. The high-resolution transmission electron microscope (HRTEM) images of the b flash memory, c 3-dimensional (3D) ternary logic inverter (T-inverter), and d heterojunction transistor (HTR). The false-color modification was attempted to organic layers to distinguish each layer in HRTEM images.

Electrical characteristics of the devices

Fig. 3a shows the schematic illustration of n-type PTCDI-C13 flash memory consisting of the FG sandwiched by high-k pC1D1 and low-k pV3D3 as BDL and TDL layers, respectively. In the operation of flash memory with FG, the electric field (E) applied to each TDL and BDL (ETDL/EBDL) is scaled with the gate coupling ratio, αCR (=VFG/VG, where VFG is the amount of voltage applied to FG) which is associated with the relative capacitance of the dielectric layers (CBDL/(CBDL + CTDL), where C is capacitance)46,47. In other words, the increased CBDL is important to distribute higher effective voltage to the TDL. In our flash memory device, the dielectric constant of the pC1D1 BDL (~6.2) is about 2.8 times higher than that of the pV3D3 TDL (~2.2). Therefore, far higher E is applied to TDL to facilitate Fowler-Nordheim (F-N)-like tunneling through pV3D3 TDL, while the E applied to BDL is quite small, which can efficiently prevent the charge leakage through BDL (Supplementary Fig. 3). The programming/erasing voltage (Vprg/Vers) of flash memory might be significantly decreased by carefully designing the dielectric layer structure while taking into account the dielectric constant of each material. Moreover, employing high-k BDL also enabled low-voltage operation while retaining thicker dielectric layer (~100 nm), which is highly desirable for securing the reliable device operation. The cumulative transfer characteristics of the 11 flash memory devices are shown in Fig. 3b, where all the devices exhibited distinct transistor characteristics. The applied drain voltage (VD) was 2.5 V for the flash memory and −2.5 V for the HTR. All the measured transfer curves were hysteresis-free, due to the extremely low leakage current through the TDL in the given operating voltage range. As shown in the statistical analysis, all the flash memory devices exhibited on/off current ratio (Ion/Ioff) higher than 105 with the operating voltage <5 V (Fig. 3c). Furthermore, the average VT was <0.7 V with narrow distribution (0.55 ± 0.09 V), thus ensuring the uniform channel conductance of the pull-down transistor. It is also worthwhile to note that even with a relatively thick polymer ILD with low thermal conductivity, only negligible change in the temperature of the flash memory was observed during the continuous operation at 5 V, owing to the low operating voltage (Supplementary Figs. 5 and 6).

a Schematic illustration of the organic flash memory on the first floor, b transfer characteristics of the 11 memory devices, and c their threshold voltage (VT), on/off current ratio (Ion/Ioff) variation. d Schematic illustration of the heterojunction transistor (HTR) on the second floor, e transfer characteristics of the 11 HTR devices, and f their negative transconductance (NTC) length, peak-to-valley current ratio (PVCR) variation. g voltage transfer characteristics (VTCs), h DC gain profiles, and i intermediate logic value, DC gain variation of the 11 3-dimensional (3D) ternary logic inverter (T-inverter) devices.

The device structure of the HTR is shown in Fig. 3d, where n-type PTCDI-C13 was deposited and annealed to obtain the enlarged grain with high crystallinity, followed by the deposition of p-type DNTT film. An atomic force microscope (AFM) analysis clearly verified the formation of the heterojunction structure at the middle edge of the heterojunction (Supplementary Fig. 7). As a GDL, pV3D3 was utilized, enabling the interfacial matching with both PTCDI-C13 and DNTT, as well as imparting thermal stability to survive the thermal annealing step at 200 °C16,45. The DNTT film connected the S and D electrodes, which allowed to induce hole accumulation at high |VG|, thus leading to the high Ion/Ioff29. The thickness of the GDL in the HTR was optimized to 50 nm, to match the capacitance per unit area (Ci) of the flash memory and HTR. All the HTR exhibited NTC characteristics with four different operation regions: (i) off-state (−0.8 V < VG < 2 V), (ii) subthreshold region (−1.5 V (=Vpeak, peak voltage) < VG < −0.8 V) where both hole-induced current and electron-induced band-to-band tunneling (BTBT) contributed to drain current (ID). (iii) NTC region (−2.6 V (=Vvalley, valley voltage) < VG < −1.5 V) where a depletion of n-type PTCDI-C13 occurred, thus |ID| was decreased with the increasing |VG|, and (iv) on-state (−5 V < VG < −2.6 V) with more hole accumulation in the higher |VG| range (Fig. 3e). A more detailed description of the origin of ID in each regime of HTR can be found in Supplementary Fig. 8. All the HTR devices exhibited distinct NTC behaviors in the transfer characteristic. The NTC length was 1.09 ± 0.10 V, and the peak-to-valley current ratio (Ipeak/Ivalley) was >12.0 in the NTC region, as defined by the VG range whereby |ID| decreased with the increasing |VG| (Fig. 3f). In addition, the narrow distribution of VT, Vpeak, and Vvalley was also confirmed in the HTR transfer curves (Supplementary Fig. 9).

The VTC and gain profile of the vertically integrated 3D T-inverter are shown in Fig. 3g, h, respectively. Through the successful operation of the 3D T-inverter, it was confirmed that the electrical interconnection of the electrodes between the top and bottom floors, separated by the shadow-mask patterned dielectric layers. All the fabricated 3D T-inverters showed full-swing operation with the uniform electrical characteristics stemming from the high device-to-device uniformity of the constituent devices, together with the high Ion/Ioff ratio of the HTR, which can be hardly achieved in conventional AATs where two semiconductors are overlapped only at the center of the channel27,28. Also, no notable hysteresis was observed in the transfer curves of the flash memory and HTR, and the VTC of the T-inverter regardless of the sweeping speed (Supplementary Figs. 10 and 11). Moreover, all the 3D T-inverters displayed a distinct intermediate logic state with two clearly distinguishable maximum gain values. The maximum DC gain in the first peak (1st gain) value was higher than the maximum DC gain in the second peak (2nd gain) value due to the relatively low intermediate logic value compared to the VDD/2. The intermediate logic value was located not in the middle value, but leaned toward 0 V, indicating that the channel conductance of the pull-down transistor (flash memory) was higher than that of the pull-up transistor (HTR), which can be further tuned exquisitely by adjusting the channel conductance of the flash memory. The statistical analysis revealed that the high device-to-device uniformity of the 3D T-inverter with a narrow distribution of the intermediate logic value (VOUT~1.35 ± 0.11 V at VIN = 2.5 V) and maximum DC gain values (−24.21 ± 1.55 and −4.81 ± 0.54 V/V for the 1st and 2nd gain, respectively), even with the 3D stacked structure (Fig. 3i).

Optimization of the 3D T-inverter characteristics

Positive (programming) or negative (erasing) gate biases were applied to the gate (G) electrode to pump electrons from the channel to the FG or to detrap the stored charges from the FG, respectively, to analyze memory characteristics (Supplementary Fig. 12). The memory programming and erasing window was investigated via an incremental step pulse programming (ISPP) and erasing (ISPE), respectively, and the pulse width was commonly set to 1 s (Fig. 4a). The change in transfer curves of the memory device in ISPP operation is shown in Fig. 4b. The transfer curve was shifted gradually toward the positive direction with the increasing Vprg without any notable degradation of the transistor characteristics nor apparent hysteresis behavior. The critical VG (VC), where VT shift (∆VT) starts to occur was as low as 12 V thanks to the high αCR. The ∆VT also increased gradually with the increasing Vprg, and reached 2.5 V with a maximum Vprg of +19 V, which was quite large considering the operating voltage (<5 V) (Fig. 4c). Based on the observed programming operation, it was verified that the n-type channel conductance can be controlled systematically by adjusting Vprg. In addition, the VT of the memory device could also be controlled by applying Vprg or Vers with various ∆t and the VT split was enlarged in accordance with the increasing ∆t (Supplementary Fig. 13). We also investigated the cycling endurance where the memory device exhibited reversible and reliable programming/erasing operation with ID ratio higher than 103 (at VG = 1 V) over 50 cycles (Supplementary Fig. 14).

a A schematic diagram of the incremental step pulse programming (ISPP) of the flash memory. b The transfer characteristics of the memory and c change in threshold voltage (VT) with respect to a programming voltage (Vprg). A schematic illustration of d the 3D T-inverter with different flash memory states and e 3D T-inverter measurement. f The voltage transfer characteristics (VTCs), g intermediate logic value, and h DC gain values according to Vprg of the flash memory.

The electrical characteristics of the vertically stacked 3D T-inverter were analyzed according to the programming/erasing states of the flash memory on the first floor (Fig. 4d, e). The ID of the flash memory was modulated successfully by programming operation (Supplementary Fig. 15), and with the decreasing channel conductance by charge trapping into the FG, the intermediate logic state was systematically controlled as shown in the VTC of the 3D T-inverter (Fig. 4f). The intermediate logic value was gradually increased in accordance with the increasing Vprg and reached 2.49 V with Vprg = + 19 V (Fig. 4g). As a result, the optimal programming state of the flash memory allowed the intermediate logic value to be practically identical to VDD/2 (logic “1”), which made the intermediate logic state clearly distinguishable from VDD (logic “2”) and GND (logic “0”). The VIN range where the intermediate logic states appeared was gradually shifted with the increasing Vprg, because the NTC region of the HTR was shifted to lower |VG| region with the decreasing |VD| (Supplementary Fig. 16). The VIN range of the intermediate logic states decreased slightly with the increasing Vprg, because only the NTC region in the HTR could be represented in the intermediate logic state, which enabled us to obtain the optimum Vout value (VDD/2) by optimizing the memory programming process (Supplementary Fig. 17). The 1st gain decreased gradually while 2nd gain increased with the increasing Vprg, resulting from the increased intermediate logic value (Fig. 4h and Supplementary Fig. 18). Nevertheless, the obtained gain value was still high, compared to the previously reported non-Si-based ternary logic inverters reported to date (Supplementary Table 1)23,29,30,32,33,34,37. Also, the obtained gain values were comparable to those observed in the organic binary logic inverters with polymer dielectric materials48,49,50,51,52,53,54,55,56. Moreover, the dramatic increase of the 2nd gain value strongly suggests that the balance between channel conductance of the flash memory and HTR is important to achieving a high-performance T-inverter, which was achieved successfully in this study by replacing the n-type transistor with flash memory.

On the other hand, the transfer curve shifted gradually toward the negative direction in ISPE (Supplementary Fig. 19). The ∆VT was −3.4 V in erasing operation, thus total memory window between the programming and erasing operations was calculated to be as large as 5.9 V. In contrast to the programming operation, the intermediate logic value decreased with the increasing |Vers| and even the full-swing operation could not be retained at higher |Vers|, because the n-channel conductance of the flash memory overwhelmed the channel conductance of the HTR (Supplementary Figs. 19 and 20).

To verify the practical applicability of the proposed 3D T-inverter, we performed transient measurements with different memory states (Fig. 5a). The VIN pulse and VOUT response of the 3D T-inverter with the pristine and programmed flash memory is shown in Fig. 5b, c, respectively. Three different VIN values were applied, of which value was adjusted every 3 s. The 3D T-inverter with both states exhibited no notable hysteresis regardless of the VIN history throughout the measuring time. However, the intermediate logic value was clearly enhanced in the programming state, compared to that observed in the pristine state. The switching speed of the T-inverter was also investigated (Supplementary Fig. 21 and Supplementary Table 2), which showed that the switching speed was comparable to those obtained frequently in the organic binary logic circuits57,58,59. It follows from the above observation that the electrical characteristics of the vertically stacked 3D T-inverter, particularly the intermediate logic state, could be controlled systematically by the programming/erasing states of the flash memory. The intermediate logic value became close to the optimum value (VDD/2) with the proper programming state, without sacrificing other electrical characteristics such as full-swing operation and negligible hysteresis. The 3D T-inverter developed in this study can accommodate many important requirements for high-performance ternary logic circuits, including the optimized intermediate logic value, full-swing operation, high DC gain as well as low-voltage operation (Supplementary Table 1). The customizable channel conductance offered by the introduction of flash memory structure resulted in such optimized T-inverter performance. It is also worthwhile to mention that the T-inverter in the form of vertical stack was realized (Supplementary Table 1), which can further enhance the integration density. In addition, the electrical characteristics could be adjusted with low Vprg/Vers as well as low operating voltage <5 V, resulting from high αCR together with the ultrathin but high-performance polymer dielectric layers.

Retention characteristics of the flash memory and T-inverter

On top of the successful control and optimization of the intermediate logic state, the stability should also be secured to achieve a reliable long-term 3D T-inverter operation. In detail, it is imperative that the 3D T-inverter fully maintains its superior electrical characteristics over time, which is directly related to the retention characteristics of the flash memory. To investigate the memory retention, the transfer curves of the optimum programming state (Vprg = +19 V) were monitored with time (Fig. 6a). The flash memory showed negligible change in transfer characteristics over time with only the 0.7 V of ∆VT even after 105 s. The change in ID at VG = 1 V and VD = 2.5 V was extracted from the transfer curves with the programming/erasing states (Fig. 6b and Supplementary Fig. 22). The ID in on-state (erasing state) at 103, 104, and 105 s showed 0.999, 0.911, and 0.716 times of the initial ID, respectively, which indicates the ID change less than an order of magnitude even after 105 s. Such long retention characteristics enabled the flash memory to retain sufficient ID difference in the programming/erasing states over time. To the best of our knowledge, the flash memory device developed in this study exhibited long retention characteristics as well as the lowest Vprg/Vers among the reported organic FG flash memories based on polymer dielectrics, resulting from the tunneling-based programming mechanism through the robust dielectric layers with high αCR (Fig. 6c and Supplementary Table 3)60,61,62,63,64,65,66,67,68,69,70. Moreover, the flash memory showed the retention characteristics even superior or at least comparable to those obtained from the organic memories with different operating principles including charge trapping memories and photonic memories71,72,73,74,75,76,77,78. Accordingly, the 3D T-inverter fully maintained its three distinct logic states with full-swing operation over time owing to the long retention characteristic of the flash memory (Fig. 6d, e). Also, no notable device degradation was observed, such as hysteresis behavior. The intermediate logic values were kept close to the optimum value (2.45, 2.47, and 2.42 V at 103, 3 × 103, and 104 s, respectively) and became 2.18 V even after 105 s (Fig. 6f). The intermediate logic value was slightly decreased with time, because the transfer curve of the flash memory was shifted to negative VG direction, which made ID of the flash memory higher than that of the HTR in the NTC region (Fig. 6d). Because of the long retention of three evidently discernable logic states, high DC gain values of the measured 3D T-inverter were maintained up to 105 s (Supplementary Fig. 23). The 1st and 2nd gain values were also retained to −13.6 and −20.8 V/V, respectively, and their change was <4.5 V/V for the 1st gain and 3.0 V/V for the 2nd gain over the whole range of the measuring time. The 3D T-inverter with erasing state of the flash memory also maintained its electrical characteristics, even though the full-swing operation could not be retained. The changes in the intermediate logic value and DC gain value <0.10 V and 5.5 V/V, respectively, even after 105 s (Supplementary Fig. 22). It follows from the observations above that the electrical characteristics of the 3D T-inverter were fully preserved once the constituent flash memory was adequately programmed, mainly due to the long retention performance of the flash memory developed in this study.

a The change in transfer characteristics of the flash memory according to time after the optimum programming state (programming voltage (Vprg) = + 19 V) and b drain current (ID) at gate voltage (VG) = 1 V and ID = 2 V versus time in the programming (open symbol) and erasing (closed symbol) states. c The comparison of the retention characteristics and programming voltage/erasing voltage (Vprg/Vers) of the flash memory in this study to those based on polymer dielectrics in the previous reports. d The change in transfer curves of the flash memory according to time and the transfer curve of the heterojunction transistor (HTR). e The change in voltage transfer characteristics (VTCs) and f intermediate logic value of the 3-dimensional (3D) ternary logic inverter (T-inverter) according to time. g The VTCs of 100 consecutive sweeps of the 3D T-inverter with the optimum programming states, and h output voltage (VOUT) values at input voltage (VIN) = 0, 3.25, and 5 V extracted from each cycle.

The operational stability test of the 3D T-inverter with the memory programming state was also performed. The VTCs with 100 consecutive cycles are shown in Fig. 6g. The 3D T-inverter fully retained its initial VTC behavior, including full-swing operation with three discernable logic states even after 100 times of the consecutive operation. The VOUT values at VIN = 0, 3.25, and 5 V were retrieved based on the number of cycles, corresponding to the logic “2”, “1”, and “0”, respectively (Fig. 6h). Those values commonly showed negligible change throughout the entire cycles, which verifies the highly stable operation of the vertically stacked 3D T-inverter. The 3D T-inverter with the optimum programming state exhibited the exceptionally stable operation against time and repeated operation, even with the proposed vertically stacked structure.

Discussion

A low-voltage organic ternary logic circuit, in which the organic HTR was vertically integrated with the organic nonvolatile flash memory, was demonstrated in this study. The integration of nonvolatile flash memory into T-inverter allowed for the circuit programmability, where the electrical characteristics including the intermediate logic state could be controlled precisely by the charge storage in FG. All the device fabrication processes were based on the solvent-free vapor-phase deposition methods, which enabled a high degree of uniformity in the device performance. By applying the via-hole-less, vertical interconnection scheme to the MVL circuit, the T-inverter in 3D structure was fabricated, which can enhance the device density per unit area. In the organic flash memory, the high-k and low-k polymer dielectric pairs were used as BDL and TDL, respectively, which could effectively reduce the Vprg/Vers as well as operating voltage (~5 V). The electrical characteristics of the 3D T-inverter were controlled systematically according to the programming/erasing state of the flash memory. With the optimum programming state of the flash memory, the 3D T-inverter showed three clearly distinguishable logic states with the intermediate logic value close to the optimum one (~VDD/2) as well as full-swing operation and low-voltage operation. The 3D T-inverter fully maintained its superior electrical characteristics and well-defined logic states over time, mainly resulting from the long retention characteristics of the flash memory. We believe the integration of the flash memory that enabled the controllable intermediate logic states in ternary logic circuits developed in this study can provide a useful insight to enhance the MVL circuit performance.

Methods

Materials and substrate

For dielectric deposition, V3D3 (95%) and CEA ( >95%) monomers were purchased from Gelest, Tokyo Chemical Industry (TCI), respectively. DEGDVE (99%) and tert-butyl peroxide (TBPO) initiator (98%) were purchased from Sigma-Aldrich. For organic semiconductors, DNTT (99%) and PTCDI-C13 (98%) were purchased from Sigma-Aldrich. All the chemicals were used as received without further purification. The glass substrate of 25 mm × 25 mm (Samsung Corning Co.) was cleaned with ultrasonication by the subsequent immersing in deionized (DI) water, acetone, and isopropyl alcohol for 20 min, followed by blowing with dry N2 gas.

Deposition of dielectric layers

The dielectric layers were deposited by the custom-built iCVD system. For pV3D3 deposition, the V3D3 and TBPO were injected into the chamber at the flow rates of 2.5 and 1 standard cubic centimeter per minute (sccm)40. The chamber pressure and substrate temperature were maintained to 300 mTorr and 40 °C, respectively. For pC1D1 deposition, CEA, DEGDVE, and TBPO were injected with the flow rates of 0.28, 0.28 and 0.48 sccm, respectively42. The chamber pressure and substrate temperature were maintained to 60 mTorr and 30 °C, respectively. To decompose the initiator into the radicals, the filament was heated to 130 °C in the iCVD process. The V3D3, CEA, DEGDVE monomers were heated to 40, 50, and 50 °C, respectively, to vaporize. The dielectric layers were deposited through a shadow mask to achieve via-hole-less metal interconnection.

Thin-film characterization

To investigate the chemical composition of the dielectric layers, the XPS spectra were obtained by a Sigma probe multipurpose spectrometer (Thermo VG Scientific) with monochromatized Al Kα source. The AFM images were taken by using a scanning probe microscope (XE-100, Park Systems) to analyze the surface morphologies of the organic semiconductors and polymer dielectric. The thickness of the polymer films and organic semiconductors was measured by a spectroscopic ellipsometer (M2000, Woollam).

Device fabrication and characterization

To fabricate the vertically stacked organic 3D T-inverter, the flash memory device was fabricated. For gate and FG electrode, Al was thermally evaporated with the deposition rate of 0.1 nm/s. The thickness of the gate and FG electrode was commonly set to 50 nm, which was monitored in situ by quartz crystal microbalance (QCM), and all the thermal evaporation processes were performed under a high vacuum lower than 2 × 10−6 torr. The dielectric layers were deposited via iCVD process and the thicknesses of the pC1D1 BDL and pV3D3 TDL were 100 and 24 nm, respectively. The organic semiconductors including DNTT and PTCDI-C13 were also thermally deposited with a deposition rate of 0.03 nm/s. The PTCDI-C13 was recrystallized by the following thermal annealing at 200 °C for an hour. For S/D electrodes, 70 nm-thick Au was thermally evaporated with a deposition rate of 0.1 nm/s. The channel width and length were 800 and 400 μm, respectively. 1 μm-thick pV3D3 was deposited onto the flash memory by the iCVD process as an ILD, and the HTR was fabricated directly on top of the ILD. For the fabrication of the HTR, 50-nm-thick Al electrode was thermally evaporated and used as gate electrode and the thickness of pV3D3 dielectric layer was 40 nm. The partial PTCDI-C13 semiconducting layer was deposited and recrystallized at 200 °C for one hour, followed by the DNTT layer that ranges from S to D electrode. 70 nm-thick Au S/D electrode was deposited and the D electrode of the HTR was connected to D electrode of the flash memory through via-hole-less multi-metal interconnection. The overall areal dimension of the active area was 0.64 mm2 (0.8 mm by 0.8 mm for width and length) including S/D electrodes, and the areal dimension of the patterned dielectric layer was 1.44 mm2 (1.2 mm by 1.2 mm for width and length). To visualize the 3D T-inverter, the device was sliced by a focused ion beam (Helios Nanolab 450), and cross-sectional HRTEM images were taken by Cs-corrected TEM (Titan cubed G2, FEI) with EDS mapping analysis. The insulating performance was analyzed by using metal-insulator-metal (MIM) devices where the polymer dielectric layers were deposited between thermally evaporated Al electrodes. The electrical characteristics were measured by B1500A semiconductor analyzer (Agilent Technologies). The sweeping speed of the input voltage was set to ~0.1 V/s, otherwise specified. The temperature of the devices was measured by infrared thermometer (Fluke 62 MAX). All the device fabrication and characterization were performed in the N2-filled glovebox.

Data availability

The data within the article and its supplementary information are available from the corresponding authors upon request.

References

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Xu, J. et al. Highly stretchable polymer semiconductor films through the nanoconfinement effect. Science 355, 59–64 (2017).

Shi, W., Guo, Y. & Liu, Y. When flexible organic field‐effect transistors meet biomimetics: a prospective view of the internet of things. Adv. Mater. 32, 1901493 (2020).

Kim, Y. et al. A bioinspired flexible organic artificial afferent nerve. Science 360, 998–1003 (2018).

Yuvaraja, S. et al. Organic field-effect transistor-based flexible sensors. Chem. Soc. Rev. 49, 3423–3460 (2020).

Fukuda, K. et al. Fully-printed high-performance organic thin-film transistors and circuitry on one-micron-thick polymer films. Nat. Commun. 5, 4147 (2014).

Wang, S. et al. Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. Nature 555, 83–88 (2018).

Paterson, A. F. et al. Recent progress in high‐mobility organic transistors: a reality check. Adv. Mater. 30, 1801079 (2018).

Lenz, J., Del Giudice, F., Geisenhof, F. R., Winterer, F. & Weitz, R. T. Vertical, electrolyte-gated organic transistors show continuous operation in the mA cm−2 regime and artificial synaptic behaviour. Nat. Nanotechnol. 14, 579–585 (2019).

Borchert, J. W. et al. Flexible low-voltage high-frequency organic thin-film transistors. Sci. Adv. 6, eaaz5156 (2020).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Bae, J.-H. et al. Thermal annealing effect on the crack development and the stability of 6, 13-bis (triisopropylsilylethynyl)-pentacene field-effect transistors with a solution-processed polymer insulator. Org. Electron. 11, 784–788 (2010).

Lee, E. K., Lee, M. Y., Park, C. H., Lee, H. R. & Oh, J. H. Toward environmentally robust organic electronics: approaches and applications. Adv. Mater. 29, 1703638 (2017).

Kwon, J. et al. Three-dimensional, inkjet-printed organic transistors and integrated circuits with 100% yield, high uniformity, and long-term stability. ACS Nano 10, 10324–10330 (2016).

Kwon, J. et al. Three-dimensional monolithic integration in flexible printed organic transistors. Nat. Commun. 10, 54 (2019).

Yoo, H. et al. Highly stacked 3D organic integrated circuits with via-hole-less multilevel metal interconnects. Nat. Commun. 10, 2424 (2019).

Nomura, K. et al. Three-dimensionally stacked flexible integrated circuit: amorphous oxide/polymer hybrid complementary inverter using n-type a-In–Ga–Zn–O and p-type poly-(9, 9-dioctylfluorene-co-bithiophene) thin-film transistors. Appl. Phys. Lett. 96, 263509 (2010).

Park, H., Yoo, H., Lee, C., Kim, J.-J. & Im, S. G. Multi-stage organic logic circuits using via-hole-less metal interconnects. IEEE Electron Device Lett. 41, 1685–1687 (2020).

Smith, K. C. The prospects for multivalued logic: a technology and applications view. IEEE Comput. Archit. Lett. 30, 619–634 (1981).

Jo, S. B., Kang, J. & Cho, J. H. Recent advances on multivalued logic gates: a materials perspective. Adv. Sci. 8, 2004216 (2021).

Yoo, H. & Kim, C.-H. Multi-valued logic system: New opportunities from emerging materials and devices. J. Mater. Chem. C. 9, 4092–4104 (2021).

Jeong, J. W. et al. Tunnelling-based ternary metal–oxide–semiconductor technology. Nat. Electron. 2, 307–312 (2019).

Lee, L. et al. ZnO composite nanolayer with mobility edge quantization for multi-value logic transistors. Nat. Commun. 10, 1998 (2019).

Hurst, S. L. Multiple-valued logic? Its status and its future. IEEE Comput. Archit. Lett. 33, 1160–1179 (1984).

Gan, K.-J., Tsai, C.-S., Chen, Y.-W. & Yeh, W.-K. Voltage-controlled multiple-valued logic design using negative differential resistance devices. Solid State Electron 54, 1637–1640 (2010).

Mariani R., Pessolano F. & Saletti R. A new CMOS ternary logic design for low-power low-voltage circuits. PATMOS, Louvain-la-Neuve, Belgium, (1997).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Multi-valued logic circuits based on organic anti-ambipolar transistors. Nano Lett. 18, 4355–4359 (2018).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Negative differential resistance transistor with organic p‐n heterojunction. Adv. Electron. Mater. 3, 1700106 (2017).

Yoo, H., On, S., Lee, S. B., Cho, K. & Kim, J. J. Negative transconductance heterojunction organic transistors and their application to full‐swing ternary circuits. Adv. Mater. 31, 1808265 (2019).

Nourbakhsh, A., Zubair, A., Dresselhaus, M. S. & Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 16, 1359–1366 (2016).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Huang, M. et al. Multifunctional high-performance van der waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Duong, N. T. et al. Modulating the functions of MoS2/MoTe2 van der waals heterostructure via thickness variation. ACS Nano 13, 4478–4485 (2019).

Wu, E. et al. Photoinduced doping to enable tunable and high-performance anti-ambipolar MoTe2/MoS2 heterotransistors. ACS Nano 13, 5430–5438 (2019).

Kim, J. Y. et al. Distinctive field-effect transistors and ternary inverters using cross-type WSe2/MoS2 heterojunctions treated with polymer acid. ACS Appl. Mater. Interfaces 12, 36530–36539 (2020).

Jariwala, D., Marks, T. J. & Hersam, M. C. Mixed-dimensional van der waals heterostructures. Nat. Mater. 16, 170–181 (2017).

Park, C.-J. et al. Photo-responsive MoS2/organic-rubrene heterojunction field-effect-transistor: application to photo-triggered ternary inverter. Semicond. Sci. Technol. 35, 065020 (2020).

Kim, B. Inkjet‐printed ternary inverter circuits with tunable middle logic voltages. Adv. Electron. Mater. 6, 2000426 (2020).

Kim, C. H., Hayakawa, R. & Wakayama, Y. Fundamentals of organic anti‐ambipolar ternary inverters. Adv. Electron. Mater. 6, 1901200 (2020).

Moon, H. et al. Synthesis of ultrathin polymer insulating layers by initiated chemical vapour deposition for low-power soft electronics. Nat. Mater. 14, 628–635 (2015).

Yu, S. J. et al. Initiated chemical vapor deposition: a versatile tool for various device applications. Adv. Eng. Mater. 20, 1700622 (2018).

Choi, J. et al. Flexible, low-power thin-film transistors made of vapor-phase synthesized high-k, ultrathin polymer gate dielectrics. ACS Appl. Mater. Interfaces 9, 20808–20817 (2017).

Choi, J., Kang, J., Lee, C., Jeong, K. & Im, S. G. Heavily crosslinked, high‐k ultrathin polymer dielectrics for flexible, low‐power organic thin‐film transistors (OTFTs). Adv. Electron. Mater. 6, 2000314 (2020).

Chen, H., Zhang, W., Li, M., He, G. & Guo, X. Interface engineering in organic field-effect transistors: principles, applications, and perspectives. Chem. Rev. 120, 2879–2949 (2020).

Seong, H. et al. A low‐voltage organic complementary inverter with high operation stability and flexibility using an ultrathin iCVD polymer dielectric and a hybrid encapsulation layer. Adv. Electron. Mater. 2, 1500385 (2016).

Lee, S., Seong, H., Im, S. G., Moon, H. & Yoo, S. Organic flash memory on various flexible substrates for foldable and disposable electronics. Nat. Commun. 8, 725 (2017).

Yang, S. C. et al. Large‐scale, low‐power nonvolatile memory based on few‐layer MoS2 and ultrathin polymer dielectrics. Adv. Electron. Mater. 5, 1800688 (2019).

Feng, L. et al. All-solution-processed low-voltage organic thin-film transistor inverter on plastic substrate. IEEE Trans. Electron Devices 61, 1175–1180 (2014).

Feng, L., Cui, Q., Zhao, J., Tang, W. & Guo, X. Dual-Vth low-voltage solution processed organic thin-film transistors with a thick polymer dielectric layer. IEEE Trans. Electron Devices 61, 2220–2223 (2014).

Shiwaku, R. et al. Printed organic inverter circuits with ultralow operating voltages. Adv. Electron. Mater. 3, 1600557 (2017).

Shin, E.-Y., Choi, E.-Y. & Noh, Y.-Y. Parylene based bilayer flexible gate dielectric layer for top-gated organic field-effect transistors. Org. Electron. 46, 14–21 (2017).

Takeda, Y. et al. Organic complementary inverter circuits fabricated with reverse offset printing. Adv. Electron. Mater. 4, 1700313 (2018).

Stucchi, E., Dell’Erba, G., Colpani, P., Kim, Y. H., & Caironi, M. Low‐voltage, printed, all‐polymer integrated circuits employing a low‐leakage and high‐yield polymer dielectric. Adv. Electron. Mater. 4, 1800340 (2018).

Jo, I. Y. et al. Low-voltage-operating complementary-like circuits using ambipolar organic-inorganic hybrid thin-film transistors with solid-state-electrolyte gate insulator. Org. Electron. 75, 105358 (2019).

Stucchi, E., Scaccabarozzi, A. D., Viola, F. A. & Caironi, M. Ultraflexible all-organic complementary transistors and inverters based on printed polymers. J. Mater. Chem. C. 8, 15331–15338 (2020).

Park, H. et al. Tailored polymer gate dielectric engineering to optimize flexible organic field-effect transistors and complementary integrated circuits. ACS Appl. Mater. Interfaces 13, 30921–30929 (2021).

Zschieschang, U., Bader, V. P. & Klauk, H. Below-one-volt organic thin-film transistors with large on/off current ratios. Org. Electron. 49, 179–186 (2017).

Chang, J. S., Facchetti, A. F. & Reuss, R. A circuits and systems perspective of organic/printed electronics: review, challenges, and contemporary and emerging design approaches. IEEE J. Emerg. Sel. Top. 7, 7–26 (2017).

Kumar, B., Kaushik, B. K. & Negi, Y. S. Organic thin film transistors: Structures, models, materials, fabrication, and applications: a review. Polym. Rev. 54, 33–111 (2014).

Mabrook, M. F., Yun, Y., Pearson, C., Zeze, D. A. & Petty, M. C. A pentacene-based organic thin film memory transistor. Appl. Phys. Lett. 94, 122 (2009).

Kim, S.-J. & Lee, J.-S. Flexible organic transistor memory devices. Nano Lett. 10, 2884–2890 (2010).

Kang, M., Baeg, K. J., Khim, D., Noh, Y. Y. & Kim, D. Y. Printed, flexible, organic nano‐floating‐gate memory: effects of metal nanoparticles and blocking dielectrics on memory characteristics. Adv. Funct. Mater. 23, 3503–3512 (2013).

Li, J. & Yan, F. Solution-processable low-voltage and flexible floating-gate memories based on an n-type polymer semiconductor and high-k polymer gate dielectrics. ACS Appl. Mater. Interfaces 6, 12815–12820 (2014).

Shih, C. C., Chiu, Y. C., Lee, W. Y., Chen, J. Y. & Chen, W. C. Conjugated polymer nanoparticles as nano floating gate electrets for high performance nonvolatile organic transistor memory devices. Adv. Funct. Mater. 25, 1511–1519 (2015).

Kang, M. et al. Synergistic high charge-storage capacity for multi-level flexible organic flash memory. Sci. Rep. 5, 12299 (2015).

Park, Y., Park, S., Jo, I., Hong, B. H. & Hong, Y. Controlled growth of a graphene charge-floating gate for organic non-volatile memory transistors. Org. Electron. 27, 227–231 (2015).

Yi, M. et al. The effect of porous structure of PMMA tunneling dielectric layer on the performance of nonvolatile floating-gate organic field-effect transistor memory devices. Org. Electron. 33, 95–101 (2016).

Wang, G., Liu, X. & Wang, W. Solution processed organic transistor nonvolatile memory with a floating-gate of carbon nanotubes. IEEE Electron Device Lett. 39, 111–114 (2017).

Wang, K. et al. A centimeter‐scale inorganic nanoparticle superlattice monolayer with non‐close‐packing and its high performance in memory devices. Adv. Mater. 30, 1800595 (2018).

Kwon, H. J. et al. Newly synthesized nonvacuum processed high‐k polymeric dielectrics with carboxyl functionality for highly stable operating printed transistor applications. Adv. Funct. Mater. 31, 2007304 (2021).

Asadi, K., De Leeuw, D. M., De Boer, B. & Blom, P. W. Organic non-volatile memories from ferroelectric phase-separated blends. Nat. Mater. 7, 547–550 (2008).

Koo, J. et al. Nonvolatile electric double-layer transistor memory devices embedded with Au nanoparticles. ACS Appl. Mater. Interfaces 10, 9563–9570 (2018).

Zhou, Y. et al. An upconverted photonic nonvolatile memory. Nat. Commun. 5, 4720 (2014).

Chiu, Y. C. et al. Oligosaccharide carbohydrate dielectrics toward high‐performance non‐volatile transistor memory devices. Adv. Mater. 27, 6257–6264 (2015).

Wang, W. et al. Highly reliable top-gated thin-film transistor memory with semiconducting, tunneling, charge-trapping, and blocking layers all of flexible polymers. ACS Appl. Mater. Interfaces 7, 10957–10965 (2015).

Tung, W. Y. et al. High performance nonvolatile transistor memories utilizing functional polyimide‐based supramolecular electrets. Chem. Asian J. 11, 1631–1640 (2016).

Pak, K., Choi, J., Lee, C. & Im, S. G. Low‐power, flexible nonvolatile organic transistor memory based on an ultrathin bilayer dielectric stack. Adv. Electron. Mater. 5, 1800799 (2019).

Lee, C. et al. Long‐term retention of low‐power, nonvolatile organic transistor memory based on ultrathin, trilayered dielectric containing charge trapping functionality. Adv. Funct. Mater. 30, 2004665 (2020).

Acknowledgements

This work was supported by the Wearable Platform Materials Technology Center (WMC) funded by the National Research Foundation of Korea (NRF) Grant by the Korean Government (MSIT) (NRF-2022R1A5A6000846) (S.G.I.). This work was also supported by NRF grants funded by the MSIT, No. 2021R1A2B5B03001416 (S.G.I.) and No. 2020R1A2C1101647 (H.Y.).

Author information

Authors and Affiliations

Contributions

J.C., C.L., H.Y., and S.G.I. conceived the idea and designed the experiments. J.C. and C.L. designed, fabricated, and measured all the devices and circuits. C.L. assisted with device characterization and H.P. helped with the circuit design. S.M.L. assisted device fabrication and C.-H.K. performed thermal simulation analysis. J.C., C.L., H.Y., and S.G.I. wrote the manuscript. All authors reviewed the manuscript and discussed the results. J.C. and C.L. contributed equally to this work. H.Y. and S.G.I. contributed equally as corresponding authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Weiguo Huang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Choi, J., Lee, C., Lee, C. et al. Vertically stacked, low-voltage organic ternary logic circuits including nonvolatile floating-gate memory transistors. Nat Commun 13, 2305 (2022). https://doi.org/10.1038/s41467-022-29756-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-022-29756-w

This article is cited by

-

Highly parallel and ultra-low-power probabilistic reasoning with programmable gaussian-like memory transistors

Nature Communications (2024)

-

PWM-to-message signal decoder circuit system based on opto-electronic devices and their PPC characteristics

Journal of the Korean Physical Society (2024)

-

Vapor-Phase Deposited Polymer Dielectric Layers for Organic Electronics: Design, Characteristics, and Applications

Korean Journal of Chemical Engineering (2024)

-

A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors

Nature Communications (2023)

-

Deep-trap dominated degradation of the endurance characteristics in OFET memory with polymer charge-trapping layer

Scientific Reports (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.