Abstract

Grayscale structured surfaces with nanometer-scale features are used in a growing number of applications in optics and fluidics. Thermal scanning probe lithography achieves a lateral resolution below 10 nm and a vertical resolution below 1 nm, but its maximum depth in polymers is limited. Here, we present an innovative combination of nanowriting in thermal resist and plasma dry etching with substrate cooling, which achieves up to 10-fold amplification of polymer nanopatterns into SiO2 without proportionally increasing surface roughness. Sinusoidal nanopatterns in SiO2 with 400 nm pitch and 150 nm depth are fabricated free of shape distortion after dry etching. To exemplify the possible applications of the proposed method, grayscale dielectric nanostructures are used for scalable manufacturing through nanoimprint lithography and for strain nanoengineering of 2D materials. Such a method for aspect ratio amplification and smooth grayscale nanopatterning has the potential to find application in the fabrication of photonic and nanoelectronic devices.

Similar content being viewed by others

Introduction

Nanotechnologies have been consistently advancing with the improvement of lithography techniques1,2. Grayscale lithography at the sub-micrometer scale has gained attention for its ability to create 2.5D topographies with multiple depth levels, leading to enhanced functionality of micro- and nanodevices such as diffractive optical elements3 and microelectromechanical systems4. Grayscale electron beam lithography (EBL) has been used to fabricate staircase patterns with a step height of 6 nm and width down to 32 nm5. The lateral and vertical resolution of this lithography process is limited by electron beam scattering. Interference lithography is another way to create surface topographies with varying height levels. The vertical and lateral resolution of the resulting grayscale nanopatterns is constrained by the exposure wavelength, as well as the intensity and phase of the interfering light waves6.

Thermal scanning probe lithography (t-SPL) has also been used for grayscale nanopatterning, demonstrating lateral spatial resolutions down to the single-digit nanometer and sub-nanometer vertical depth control7,8,9,10. The thermal spreading effect caused by the heated tip in t-SPL is not as severe as the proximity effect caused by electron scattering in EBL. In particular, the endothermic decomposition reaction of the thermally-sensitive resist, polyphthalaldehyde (PPA), localizes patterning at the contact area of the tip, enabling sub-10 nm lateral resolutions with sharp tips. PPA sublimates within microseconds11,12, allowing for rapid patterning at scan speeds of around 1 mm/s, which are comparable to EBL9. t-SPL speeds up to 20 mm/s have also been reported13. The combined write-and-read mechanism of t-SPL, called closed-loop lithography, enables simultaneous correction of the patterned depths, achieving sub-nanometer vertical depth control14.

t-SPL has been used for both high-resolution binary15,16,17,18,19,20,21 and grayscale patterning14,22,23,24,25,26. Single-digit nanometer resolution grayscale lithography with sub-1 nm vertical depth control has been successfully implemented in a nanofluidic device that can separate nanoparticles with a diameter variation of only 1 nm22 and has also been used for the fabrication of sinusoidal gratings for more precise control over a diffracted wavefront compared to binary-shaped conventional gratings25. The grayscale fabrication capability of t-SPL enables the fabrication of sinusoidal patterns with adaptable amplitude, spatial frequency, and phase25. Despite the impressive nanofabrication results achieved using t-SPL, one of the main challenges lies in achieving large patterning depths. The practical nanostructure patterning depth limit in PPA with t-SPL is about 100 nm due to the probe and tip geometry as well as the thermomechanical response of the polymer resist17. Deeper writing in the resist reduces heating efficiency due to tip cooling, particularly for sharper tips where the boundary scattering of phonons further decreases the efficiency27,28. This shallow patterning depth limits the use of t-SPL for applications requiring high aspect ratio grayscale nanopatterning, such as optical diffractive elements29,30. In addition, the depth of sub-10 nm patterns is typically limited to values below 10 nm due to the conical geometry of the tip31,32. To achieve larger depths, pattern transfer from PPA into multiple underlying layers is used. However, this approach has been demonstrated only for binary patterns, and each pattern transfer process caused feature widening, in turn affecting the achievable lateral resolution31,32. Non-binary transfer has been shown for saw-tooth and sinusoidal profile transfer from PPA to SiNx, but with significant shape deformation and large depth amplification variation23. As an alternative approach, cyclic infiltration of inorganic materials has been shown to convert patterned PPA resists into more etch-resistant inorganic hard masks, allowing for the amplification of depths in underlying layers after pattern transfer33. However, this approach requires additional chemical post-processing steps on PPA.

To overcome these limitations in patterning depth, in this work, we demonstrate an advanced combination of grayscale patterning in PPA and dry etching-based transfer into dielectric layers to amplify the depths of grayscale nanopatterns through optimized etching parameters with cooling cycles. The reported etch transfer and pattern amplification approach is generic and applicable to various polymer/dielectric stacks, regardless of the lithography techniques employed. To exemplify the possible applications of the proposed approach, we use grayscale dielectric nanostructures as thermal nanoimprint lithography (NIL) stamps for scalable replication and as a platform to induce local strain in atomically thin MoS2 layers.

Results and Discussion

Grayscale nanopatterning and depth amplification

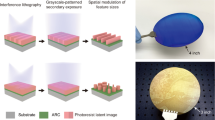

In the following, we describe the process for grayscale nanopattern amplification based on the combination of t-SPL and dry etching. As illustrated in Fig. 1, a silicon substrate with a thin film of either SiO2 or Si3N4 is spin-coated with thermally-sensitive PPA resist and grayscale nanopatterns are fabricated by direct sublimation of the resist according to the pre-defined depths for each pixel of the grayscale bitmap (see Figure S1 for bitmap design). Binary and sinusoidal patterns are fabricated with sub-nanometer depth control using t-SPL. The sinusoidal nanopatterns with a pitch of 400 nm and peak-to-peak depths of up to 30 nm are defined by the equation \(f(x,y)=A\cos (gx)\), where A and g are amplitude and spatial frequency, respectively. Patterning at peak-to-peak depths larger than 30 nm significantly reduces the lateral resolution due to the tip’s conical geometry (Figures 1 and S2). Deeper tip indentations result in broader and non-symmetrical patterns, as we experimentally show in Figure S3. In addition to the tip apex, the slope of the tip also plays a role in heat transfer for deep indentations, preventing the fabrication of closely spaced patterns and limiting the aspect ratios of fabricated nanostructures (see Figures S4–S6). In addition to our experimental demonstrations, the minimum achievable pitch with respect to tip diameter and indentation depths has been theoretically calculated in a recent study34. Therefore, we limit grayscale nanopattern depths to achieve the highest spatial resolutions in sinusoidal wave patterns with pitches below 400 nm.

Cross-sectional illustration of the process flow for grayscale nanopattern amplification in dielectrics. a Spin-coating of the thermally-sensitive resist PPA on a thin dielectric film, in our case SiO2 or Si3N4. b Fabrication of binary and grayscale nanostructures on a thin layer of PPA using a heated nanotip (see Figure S2 for the details of the nanotip). c Transfer of the nanostructures from PPA to SiO2 or Si3N4. d Complete transfer of the nanostructures written in PPA into the dielectric film with depth amplification. The vertical peak-to-peak depth amplification (Δzdielectric/Δzresist) results from the difference in etch rates between the resist and substrate in CHF3/SF6 plasma. Illustration images are not to scale. e SEM image of the tip of the cantilever (NanoFrazor Monopede, Heidelberg Instruments Nano AG)

Following grayscale t-SPL, the nanopatterns are transferred from the resist into a dielectric layer, either SiO2 or Si3N4, using inductively coupled plasma (ICP) reactive ion etching (RIE). The progressive erosion of the grayscale patterns locally modifies the opening in the resist masking layer (Fig. 1c). Hence, patterns on the resist are replicated on the substrate with a depth amplification that depends on the etch selectivities of SiO2 to PPA or Si3N4 to PPA in CHF3/SF6 plasma. See Methods and Table S1 in the Supplementary Information for further details.

During the aspect ratio amplification process by RIE, the substrate cooling temperature was fixed to 10 °C using a temperature-controlled electrostatic clamping chuck and backside He cooling as the substrate temperature is one of the parameters that allows the control of the etch selectivities4. Cooling cycles of 5 min were added after every 100 s of plasma etching to prevent substrate overheating. By changing the CHF3/SF6 rate from 50/20 sccm to 50/10 sccm (at 5 mTorr and 15 W RF bias power), the etch rate of SiO2 decreases by 35%. However, the SiO2 to PPA etch selectivity, which provides the depth amplification, increases by 125% as shown in Fig. 2a. At the optimal flow rate, a depth amplification of 5 times is achieved. Further reduction of the CHF3/SF6 relative gas flow rates (50/5 sccm) induces polymerization due to CHx and CFx adsorption on the nanostructured surface, preventing nanopattern transfer. Adding 5 or 10 sccm O2 to the 50/10 sccm of CHF3/SF6 plasma results in a 49% and 65% reduction in average amplification, respectively (Fig. 2b). Higher chamber pressure results in faster SiO2 etching due to increased concentrations in reactive gases, but this reduces the amplification (Fig. 2c). The highest depth amplifications are observed at a pressure of 3.5 mTorr, while a reduction to 3 mTorr results in an 8% drop in average grayscale depth amplification (see Figure S7 for the comparison of amplification at 3.5 and 5 mTorr pressures). At lower pressures, physical etching dominates, leading to a reduction in etch selectivity.

a Effect of CHF3/SF6 gas flow rate and b effect of adding O2 on the depth amplification and SiO2 etch rate at a fixed pressure of 5 mTorr and an RF bias power of 15 W. c Influence of chamber pressure on depth amplification and SiO2 etch rate for a CHF3/SF6 plasma with flow rate of 50/10 sccm at 15 W fixed RF bias power. d Effect of RF bias power on depth amplification for a CHF3/SF6 plasma with flow rate of 50/10 sccm at 5 mTorr fixed pressure. The error bars correspond to one standard deviation (±σ) for 16 to 48 surface profile comparisons, and the dashed lines represent polynomial fits of the experimental data. e Effect of the substrate temperature on the grayscale depth amplification. Depth amplification is obtained after three consecutive 100 s plasma etching cycles separated by substrate cooling periods of 0, 2, 5, 10, and 15 min. The shaded area represents one standard deviation (±σ) for 16 surface profile comparisons. In all cases (from a to e), RF ICP power and substrate cooling temperature are kept constant at 950 W and 10 °C, respectively. f Depth amplification and corresponding surface roughness amplification after dry etching for varying values of RF bias power

The RF bias power applied to the substrate through the bottom electrode generates a self-bias that controls the reactive species bombardment energy and physical etching yield, affecting the depth amplification. Figure 2d shows the significant influence of the RF bias power on the grayscale depth amplification. An amplification of up to 10 ± 1 is achieved at 12 W, showing a 2-fold increase compared to etching at 15 W. Lower RF bias powers result in higher amplification. A further reduction of the bias power to 10 W causes polymerization, blocking pattern transfer into SiO2. On the contrary, higher RF bias powers lead to lower amplifications (1.2-fold at 80 W). Furthermore, CHF3/SF6 plasma is used to transfer grayscale PPA nanopatterns to Si3N4, another commonly used dielectric in semiconductor devices, but with reduced amplifications compared to SiO2 (see Figure S8).

Despite the continuous backside cooling, heat inflow from the plasma causes the substrate temperature to increase, reducing the sticking probability of reaction byproducts to the nanopattern surfaces. Therefore, at higher substrate temperatures, the presence of CHx and CFx is less efficient in protecting the sidewalls of patterns. This affects the anisotropy of the etching process35 and causes a reduction in the grayscale depth amplification. To prevent substrate overheating, we performed a cycled RIE process that alternates between plasma etching and cooling phases. When the dry etching process is paused for more than 5 min every 100 s of plasma etching to let the substrate cool down, the average depth amplification is increased by up to 33% compared to continuous plasma etching (Fig. 2e). Higher substrate temperatures affect the sidewall protection, in turn, reducing the depth amplification. See Figure S9 for details on the substrate cooling.

Despite the sub-nanometer depth control, the nanopatterns produced by t-SPL have a certain surface roughness14, which is typically about 0.4 to 0.5 nmrms on the patterned PPA resist. This inherent surface roughness is typically further enhanced during the dry etch-based transfer. Substrate temperature, pressure, bias power, and the C/F ratios significantly affect the emission of fluorocarbon and silicon oxide species from the substrates and their redeposition rates35,36,37,38. Additionally, ion damage on the resist surface modifies the resist surface roughness39, which is translated to the underlying layer on the substrate. This transferred roughness can be smoothened, up to a certain limit, with post-treatments such as ion-beam milling40, but it is mostly efficient for flat surfaces rather than high aspect ratio nanopatterns. Therefore, minimizing the surface roughness generated by the plasma etching step while amplifying the depths of nanopatterns is crucial in achieving smooth grayscale nanostructures.

The highest amplification value reported so far in literature between PPA and SiO2, which is a 3-fold amplification in depth profiles of binary patterns, was achieved using C4F8/H2/He plasma14. However, the plasma used for this depth amplification process also increases the surface roughness up to 8 times, which in turn reduces the functional quality of the nanostructures for device integration. Figure 2f shows that our newly developed dry etching recipe, the CHF3/SF6 plasma (50/10 sccm) at 5 mTorr pressure with controlled substrate temperature, enables the transfer without introducing additional surface roughness. To evaluate the quality of pattern transfer in terms of roughness, we compare the ratio of depth amplification to roughness amplification. We observe that the CHF3/SF6 gas flow rate ratios have a larger effect on surface roughness than the RF bias power and pressure. For example, while the ratio is 0.94 for CHF3/SF6 plasma with a flow rate of 50/10 sccm, it is reduced to 0.41 when the SF6 flow rate is increased to 20 sccm under the same plasma conditions. The surface roughness is quantitatively characterized using atomic force microscopy (AFM) on both flat and sinusoidal surfaces, yielding similar values, on 2 μm2 and 8 μm2 areas, respectively. See Figure S10 for the comparison of our recipes with current state-of-the-art processes.

Next, we investigate the surface topographies of PPA and dielectric layers. Figure 3 shows 5-fold amplification in depth profiles of rectangular and sinusoidal nanostructures (400 nm pitch with 10, 20 and 30 nm depths) when transferred from PPA to SiO2 using CHF3/SF6 plasma with a flow rate of 50/10 sccm at 950 W RF ICP power, 15 W RF bias power, and 5 mTorr pressure (process #11 in Table S1; see Figure S11 for nanohole arrays with a diameter-to-depth ratio of up to 1.7 fabricated on SiO2 using the same plasma conditions). The nanopatterns in PPA are accurately and proportionally transferred into the dielectric layers with a significant increase in amplitude and without adding extra roughness during dry etching, keeping the pattern depth-to-roughness ratio almost constant. This is achieved due to the high vertical etch rates with respect to lateral etch rates. In Fig. 3, we also show Fourier transforms of the measured topographies on PPA and SiO2 to evaluate the quality of the pattern transfer. Fourier transforms are performed on the measured topographies along 140 lines (2.8 x 2.8 μm2 area with 20 x 20 nm2 pixels) and then averaged. The second harmonic has an amplitude of 3.1% of the main Fourier component at the spatial frequency of 2.5 μm−1 after t-SPL patterning on PPA, whereas the one measured after pattern transfer and amplification in SiO2 has an amplitude of 3.4% of its main Fourier component for sinusoidal patterns amplified from 20 ± 1 nm to 102 ± 2 nm peak-to-peak depths (Fig. 3e, f). This indicates that a 5-fold aspect ratio amplification is achieved without any significant distortion of the original sinusoidal shapes. At higher depth amplifications, distortion of the sinusoidal shapes becomes significant. For instance, for 12 W RF bias power, a 10 times depth amplification of the sinusoidal nanopatterns is obtained. However, the sinusoidal shapes are deformed because of increased lateral etching, with a second harmonic component as large as 37% of the main component (see Figures S12–S14 for AFM images and Fourier transform).

a AFM image of sinusoidal patterns fabricated on PPA. b AFM image of the sinusoidal patterns shown in a after their transfer into SiO2 by dry etching (CHF3/SF6 plasma with flow rate of 50/10 sccm at 5 mTorr pressure, and 15 W RF bias power). c Comparison of the PPA and SiO2 cross-section profiles measured by AFM along Line 1 and Line 3. After dry etching, the sinusoidal pattern has been amplified 5 times and the sample surface has been shifted 100 nm lower in SiO2. d Comparison of the sinusoidal profiles before (Line 2) and after (Line 4) pattern transfer by dry etching. The sinusoidal pattern has been amplified in peak-to-peak amplitude from 20 nm to 100 nm. e, f Fourier transforms of the measured topographies after t-SPL on PPA (left sinusoidal nanopattern in a) and transferred into SiO2 (left sinusoidal nanopattern in b). g Tilt (54°) corrected cross-sectional SEM image of sinusoidal nanostructure fabricated on SiO2 by depth amplification corresponding to Line 4. The areas of interest are protected by a deposited carbon layer and milled by FIB (see Figure S15 for SEM images before and after FIB milling). h AFM images and surface profile comparison of rectangular and sinusoidal nanopatterns having varying aspect ratios after t-SPL patterning in PPA and pattern transfer into SiO2

Application of grayscale stamps to nanoimprint lithography

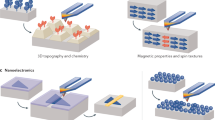

In the following, we discuss the combination of t-SPL with dry etching for grayscale NIL stamp fabrication as a possible strategy to overcome the limited throughput of t-SPL41. NIL is a cost-efficient technique to replicate high-resolution grayscale nanostructures on large surfaces by step-and-repeat process42,43. We use a structured SiO2 (500 nm thick)/Si substrate fabricated by t-SPL and dry etching processes shown above as grayscale stamp to replicate the nanopatterns on a thermoplastic NIL resist, mr-I 8010R, and then transfer them into thin dielectric films on wafers. The fabricated 50 nm in depth sinusoidal nanostructures on SiO2 with surface roughness of 0.5 nmrms are replicated on a 100 nm thick thermoplastic resist layer with surface roughness of 0.5 nmrms. Then, the nanopatterns are transferred from the NIL resist to a SiO2 thin film by dry etching (Fig. 4) using CHF3/SF6 (50/15 sccm) plasma (see Methods). These transferred sinusoidal nanopatterns on 100 mm wafer have 30 nm depths with surface roughness of 0.3 nmrms, proportional to the depth reduction (NIL resist to SiO2 etch selectivity is 1:0.6). The integration of t-SPL, NIL, and dry etching techniques demonstrated in this work is suitable for scalable and reproducible fabrication of high-resolution grayscale nanopatterns.

a Thermal NIL of grayscale nanostructures on thermoplastic resist and pattern transfer into SiO2 substrates. b AFM image of grayscale stamp fabricated on thin film SiO2 by combining t-SPL and dry etching. c AFM image of nanopatterns replicated on thermoplastic resist and transferred into a SiO2 dielectric layer with CHF3/SF6 plasma (see Figure S16 for AFM image of replicated nanostructures on NIL resist)

Application of grayscale nanostructures to strain 2DMs

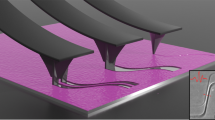

Similar to the approach used in Si-based devices44, the strain has been used for 2D materials (2DMs) to increase the charge carrier mobility in field-effect transistors45. Recently, we used t-SPL to obtain strain-induced bandgap modulation of 2DMs placed on top of a PPA layer with thermomechanical indentations46. Here, we fabricate grayscale dielectric nanostructures with higher aspect ratios, switching from PPA to high-quality SiO2 as the underlying dielectric. This provides a robust platform for straining 2DMs. The increase in aspect ratio is translated into a higher strain, and the absence of the underlying PPA polymer reduces the risk of a possible degradation of the nano-corrugations over time. In this way, we induce deterministic local strain to 2DMs through the precise nanopatterning of the substrate in contrast to other cases where only random surface roughness45 or global strain47 is used. We fabricated a SiO2 layer with sinusoidal waves modulated in two dimensions (f(x, y) = A [\(\cos (gx)\) + \(\cos (gy)\)]). MoS2 monolayer grown by metal-organic chemical vapor deposition (MOCVD)48 was then transferred by pressing against the grayscale nanostructures using a polymer support (Fig. 5a; see Methods). This induces a bi-axial tensile strain to the 2DMs deterministically placed on structured SiO2 layers.

a Fabrication process flow of grayscale dielectric nanostructures for 2DMs strain. b Optical microscope (left) and AFM images of a MoS2 monolayer that conformally covers the SiO2 layer nanostructured with sinusoidal waves modulated in two dimensions (400 nm pitch, 60 nm peak-to-peak depth). c Raman micro-spectroscopy to visualize strain modulation of MoS2 monolayer on grayscale SiO2 nanostructures having different depth-to-pitch ratios (pitches from 300 to 500 nm, and depths from 60 to 120 nm). The plot shows the shift of \({\,{{\mbox{E}}}\,}_{2g}^{1}\) Raman peaks, \({\,{{\mbox{E}}}\,}_{2g}^{1-}\) and \({\,{{\mbox{E}}}\,}_{2g}^{1+}\) peaks in case of peak splitting, as a function of depth-to-pitch ratio. Raman peaks of unstrained MoS2 are obtained from the part of the flake placed on flat SiO2 surfaces

Compared to other studies with nanopillar arrays fabricated by EBL49, our sinusoidal pattern avoids sharp edges that pose a high risk of breaking the 2DMs and allows for conformal attachment of the 2DM to the nanopatterned dielectric layer through van der Waals forces, mitigating wrinkling and suspension of the 2DMs (Fig. 5b). The use of t-SPL is consequently a promising option to produce mechanically stable semiconductor-dielectric interfaces for strained 2DMs-based devices (Figure S17). In addition to high-resolution AFM imaging, the continuity of 2DM flakes and their conformal adherence to the structured substrate are further studied by TEM and energy-dispersive X-ray (EDX) elemental mapping (Figure S18). Based on the analysis, we conclude that the flakes are intact on sinusoidal nanopatterns. When MOCVD-grown MoS2 monolayers are strained on grayscale nanostructures, both the \({\,{{\mbox{E}}}\,}_{2g}^{1}\) and A1g modes exhibit redshifts. These shifts correspond to the optically averaged strain induced over about 1 μm2 area of the atomically thin material50. Different strain values in the same 2DMs are obtained by changing the depth-to-pitch ratios of the nanostructures, as shown in Fig. 5c. The linear fit of the Raman measurements shows about -5 cm−1 shift per unit dept-to-pitch ratio for \({\,{{\mbox{E}}}\,}_{2g}^{1}\) modes. In some cases, up to 7.9 cm−1 redshifts, corresponding to a 1.8% strain according to previously reported experiments51, are observed. The smaller redshifts are most probably caused by the formation of the cracks during the two-step manual handling process, which causes strain relaxation (see Methods; Table S2; Figures S19 and S20). Although with large deviations, this data indicates, as intuitively expected, that higher depths in sinusoidal nanopatterns result in higher tensile strain in 2DMs.

Conclusion

In this work, we present an innovative fabrication process for grayscale nanopatterning, specifically with depths greater than 100 nm and up to 400 nm, based on the combination of t-SPL and dry etching. Thanks to the high etch selectivity of SiO2 and Si3N4 compared to PPA in optimized CHF3/SF6 RIE conditions with controlled substrate temperature, this process enables the fabrication of complex high aspect ratio nanostructures. Depth amplifications up to 5 times into SiO2 of the shallow polymer patterns written by t-SPL were achieved without introducing shape distortion and additional surface roughness due to plasma process. A 10-fold amplification is also achieved, although with significant distortion from the sinusoidal shape. We introduce a cycled process alternating between plasma etching and cooling steps to prevent substrate overheating, influencing, in turn, the aspect ratio amplification.

To exemplify the possible applications of the proposed process, we show its applications to NIL and to strain engineering of 2DMs. The grayscale nanostructured substrates are used as a stamp for thermal NIL to address the scalability limitation of scanning probe-based fabrication. Sinusoidal nanosurfaces are faithfully replicated in dielectric films by combining NIL and dry etching. The developed etch recipes were utilized for pattern transfer from PPA to SiO2 and Si3N4, as well as from thermoplastic NIL resist to SiO2, demonstrating consistent quality, particularly in terms of roughness. We also present the use of sinusoidal dielectric layers as a tool for 2DM strain engineering, where the amplitude modulation of the sinusoidal waves is tuned to control the local strain rates. Bi-axial tensile strains are achieved in the same flake of MoS2 monolayer on structured areas. Varying depth-to-pitch ratios of the nanostructures are used to control locally the induced strain in atomically thin material. This opens the way to use the high aspect ratio and smooth dielectric grayscale nanopatterns presented in this study for the development of advanced nanoelectronics, photonics, and optoelectronics devices, with potential applications in sensors and processors.

Materials and Methods

Sample preparation and grayscale nanopatterning

For rectangular and sinusoidal (\(f(x,y)=A\cos (gx)\)) nanopattern fabrication, a 5 wt% solution of polyphthalaldehyde (PPA, Allresist) in anisole (Sigma-Aldrich Chemie GmbH) was spin-coated on SiO2 (500 nm thick wet oxide)/Si (500 μm thick, 10 x 10 mm2 size) substrate or Si3N4 (low-pressure chemical vapor deposited (LPCVD) 500 nm thick)/Si (500 μm thick, 10 x 10 mm2 size) substrate at 5000 rpm and soft baked at 110 °C for 2 min. For sine waves (f(x, y) = A[\(\cos (gx)\) + \(\cos (gy)\)]) fabrication, a 5 wt% PPA solution in anisole was spin-coated on SiO2 (200 nm thick dry oxide)/Si (500 μm thick, 10 x 10 mm2 size) substrate at 5000 rpm and soft baked at 110 °C for 2 min.

A commercial t-SPL system (Nanofrazor Explore) and thermal cantilevers of type NanoFrazor Monopede (Heidelberg Instruments Nano AG) were used to pattern grayscale nanostructures on PPA. For grayscale design, the analytical design of a sinusoidal surface was converted into a grayscale bitmap consisting of a 20x20 nm2 pixel grid. The normalized depth was set to 256 levels. Then, the grayscale bitmap image was imported into the t-SPL software, and the depth for each pixel was assigned. In case of combined binary and sinusoidal design (Figure S1), the minimum depth (white pixel) and maximum depth (black pixel) were set to 10 nm and 40 nm, respectively. For t-SPL, the writing heater temperature was set to 950 °C, and the step size to 20 nm, the scan speed to 25 μs per pixel, and the force pulse to 5 μs. The patterned depths were simultaneously corrected by integrated in-situ AFM metrology, and NanoFrazor’s Kalman feedback system adjusted the actuation forces for high-resolution depth control.

Reactive ion etching

The nanopatterns were transferred from PPA to thin film SiO2 by a commercial ICP-based RIE system (SPTS Advanced Plasma System). In the dry etching processes, high density CHF3/SF6 and CHF3/SF6/O2 plasma were used at different flow rates, plasma times, process pressures and RF bias powers applied to the bottom electrode for wafer voltage biasing (independent from the RF ICP source), but at fixed RF ICP power of 950 W (13.56 MHz RF field). 10 x 10 mm2 size substrates were glued onto 100 mm silicon wafers by mounting wax (PELCO® Quickstick 135). The wafer was placed on the bottom electrode and was gripped by electrostatic clamping. A backside cooling flow of He was used to cool down the substrate temperature to 10 °C. For the processes lasting longer than 100 s, the plasma was turned off to lower the substrate temperature. Meanwhile, Ar was inserted into the plasma chamber to accelerate substrate cooling. At the end of the dry etching processes, substrates were removed from the wafer by melting the mounting wax on a hot plate at 135 °C, and cleaned with 5 min acetone, 5 min IPA and 10 min O2 plasma. For cleaning of the substrates used for 2DM strain, a piranha solution (3:1 mixture of H2SO4(96%):H2O2(30%)) was used for 10 min followed by 5 min acetone, 5 min IPA and 10 min O2 plasma.

Nanoimprint lithography and pattern transfer

For thermal NIL replication on thermoplastic resist, mr-I 8010R resist (micro resist technology GmbH) was spin-coated on SiO2 (500 nm thick wet oxide)/Si (500 μm thick) 100 mm wafer at 3000 rpm and soft baked at 90 °C for 1 min. Grayscale stamps fabricated by combining t-SPL and dry etching were placed on mr-I 8010R resist-coated wafer. NanoImprint EHN-3250 thermal nanoimprinter was used for the replication of grayscale nanostructures. 0.2 MPa pressure was applied at 160 °C for 5 min and cooled down to 90 °C in 1 min. Demolding of the grayscale stamp was performed at 90 °C. Grayscale nanostructures on mr-I 8010R resist were then transferred to SiO2 thin films on Si wafers using the same ICP-based RIE system (SPTS Advanced Plasma System) with CHF3/SF6 plasma with a flow rate of 50/15 sccm at 950 W RF ICP power, 80 W RF bias power, 5 mTorr pressure, and 10 °C substrate temperature.

2D material growth and transfer

The MoS2 flakes are grown on a c-plane sapphire chip by the MOCVD, as presented by Cun et al.48. The sapphire chip was annealed in air for 6 hours to achieve a smooth atomic surface and then spin-coated with 0.026 mol/L NaCl solution in deionized water to suppress nuclear density and accelerate the growth rate. Then, the chip was loaded into a tube furnace with controlled temperature and gas flow rate. During the growth process, molybdenum hexacarbonyl (Mo(CO)6) and hydrogen sulfide (H2S) were introduced into the quartz tube as precursors using Ar as the carrier gas. The flow rates of Mo(CO)6 and H2S were set at 6 sccm and 3 sccm, respectively. The Mo(CO)6 precursor was stored in a bubbler immersed in a water bath maintained at a temperature of 15 °C to achieve a constant vapor rate. Small amounts of H2 and O2 were separately introduced into the growth chamber to balance the growth rate and achieve MoS2 monolayers. At the end of the growth, the precursor supply was abruptly stopped, and the furnace was allowed to cool naturally to room temperature with a flow of 200 sccm of Ar to remove gaseous residues.

The sapphire chip with MoS2 monolayers was then spin-coated with 50 nm thick PMMA, and 1 mm thick PDMS film was placed on top. The PDMS/PMMA/2D flakes stack was detached from the sapphire chip after 20 min immersion in DI water and was transferred to SiO2 (270 nm thick)/Si (500 μm thick) chips. The polymer layers were then removed in acetone. The SiO2/Si chip was heated to 95 °C, and the MoS2 monolayer flakes were picked up with a polycarbonate (PC) film, which was mounted on a curved PDMS layer attached to a glass microscope slide. Later, these flakes were aligned under a microscope on grayscale nanostructures fabricated by t-SPL and dry etch-based transfer and pressed against the grayscale nanostructures. Flakes were transferred with the PC film layer after heating the substrate to 180 °C. The PC film was later dissolved in chloroform for 1 hour.

AFM, SEM and Raman spectroscopy

In addition to in-situ metrology of written patterns during t-SPL, AFM topography characterization was performed with Bruker FastScan AFM (ScanAsyst mode). ScanAyst auto control was used as a feedback system, and the step size in topography imaging was set to 20 nm. To compare the average peak-to-peak depth amplifications, AFM topography characterization on patterned SiO2 or Si3N4 was performed with Bruker FastScan AFM (ScanAsyst mode, ScanAyst auto control feedback, and step size of 20 nm) in the same way as for PPA. For data visualization and surface profile characterization, the scanning-probe analysis software Gwyddion (version 2.59) was used. Data plotting and Fourier transforms of patterns were performed in MATLAB (version R2020b). RMS surface roughnesses on flat areas are quantified according to the mean value of the region of interest. RMS surface roughnesses on sinusoidal areas are calculated by substracting the mean sinusoidal profile of the measured topographies over 140 lines in 2.8x2.8 μm2 area with 20 x 20 nm2 pixels.

AFM images on 2DMs were taken in PeakForce QNM® mode using the Multimode (Bruker) Scanhead and Nanoscope V controller (Bruker). ScanAsyst-Air cantilevers with a spring constant of 0.4 N/m were used, and peak forces were set to 350 pN. Quantitative mechanical characterizations were performed with 10 nN peak force setpoints.

The cross-sections of the final structures were examined with a dual-beam Focused Ion Beam/Scanning Electron Microscope (FIB/SEM) instrument (Zeiss CrossBeam 540). SEM images were obtained by InLens secondary-electron (SE) detector at 2 kV electron high tension (EHT), 5 mm working distance, and 300 pA probe current. Images were taken at 54° stage tilt and tilt correction was activated during imaging.

For the Raman spectra collection, a confocal Raman microscope system (inVia Qontor, Renishaw) coupled with an Olympus inverted optical microscope was utilized. The Raman spectra was collected by averaging 2 accumulations of 10 s laser exposure with an excitation wavelength of 532 nm. A grating of 3000 gr/mm was used for Raman characterization. To avoid damaging of the studied samples, the laser power was kept lower than 100 μW. The peak positions are extracted by fitting the curves with Lorentzian functions.

References

Tallents, G., Wagenaars, E. & Pert, G. Lithography at EUV wavelengths. Nat Photonics 4, 809–811 (2010).

Fan, D. & Ekinci, Y. Photolithography reaches 6 nm half-pitch using extreme ultraviolet light. J Micro/Nanolithogr MEMS, and MOEMS 15, 033505–033505 (2016).

Morgan, B., Waits, C. M., Krizmanic, J. & Ghodssi, R. Development of a deep silicon phase Fresnel lens using gray-scale lithography and deep reactive ion etching. J Microelectromech Syst 13, 113–120 (2004).

Waits, C., Morgan, B., Kastantin, M. & Ghodssi, R. Microfabrication of 3D silicon MEMS structures using gray-scale lithography and deep reactive ion etching. Sensors Actuators A: Phys 119, 245–253 (2005).

Kirchner, R., Guzenko, V. A. & Schift, H. Single-digit 6-nm multilevel patterns by electron beam grayscale lithography. Adv Opt Technol 8, 175–180 (2019).

Fallica, R., Kirchner, R., Schift, H. & Ekinci, Y. High-resolution grayscale patterning using extreme ultraviolet interference lithography. Microelectron Eng 177, 1–5 (2017).

Pires, D. et al. Nanoscale three-dimensional patterning of molecular resists by scanning probes. Science 328, 732–735 (2010).

Garcia, R., Knoll, A. W. & Riedo, E. Advanced scanning probe lithography. Nat Nanotechnol 9, 577–587 (2014).

Howell, S. T., Grushina, A., Holzner, F. & Brugger, J. Thermal scanning probe lithography-A review. Microsyst Nanoeng. 6, 21 (2020).

Albisetti, E. et al. Thermal scanning probe lithography. Nat Rev Methods Primers 2, 32 (2022).

Coulembier, O. et al. Probe-based nanolithography: self-amplified depolymerization media for dry lithography. Macromolecules 43, 572 (2010).

Knoll, A. W. et al. Probe-based 3-D nanolithography using self-amplified depolymerization polymers. Adv Mater. 22, 3361–3365 (2010).

Paul, P. C., Knoll, A. W., Holzner, F., Despont, M. & Duerig, U. Rapid turnaround scanning probe nanolithography. Nanotechnology 22, 275306 (2011).

Rawlings, C. D. et al. Control of the interaction strength of photonic molecules by nanometer precise 3D fabrication. Sci Rep 7, 1–9 (2017).

Holzner, F. et al. High density multi-level recording for archival data preservation. Appl Phys Lett. 99, 023110 (2011).

Cheong, L. L. et al. Thermal probe maskless lithography for 27.5 nm half-pitch Si technology. Nano Lett. 13, 4485–4491 (2013).

Lisunova, Y., Spieser, M., Juttin, R., Holzner, F. & Brugger, J. High-aspect ratio nanopatterning via combined thermal scanning probe lithography and dry etching. Microelectron Eng 180, 20–24 (2017).

Tang, S. W. et al. Replication of a tissue microenvironment by thermal scanning probe lithography. ACS Appli Mater Interfaces 11, 18988–18994 (2019).

Zheng, X. et al. Patterning metal contacts on monolayer MoS2 with vanishing Schottky barriers using thermal nanolithography. Nat Electron 2, 17–25 (2019).

Liu, X., Howell, S. T., Conde-Rubio, A., Boero, G. & Brugger, J. Thermomechanical nanocutting of 2D materials. Adv Mater 32, 2001232 (2020).

Conde-Rubio, A., Liu, X., Boero, G. & Brugger, J. Edge-contact MoS2 transistors fabricated using thermal scanning probe lithography. ACS Appl Mater Interfaces 14, 42328–42336 (2022).

Skaug, M. J., Schwemmer, C., Fringes, S., Rawlings, C. D. & Knoll, A. W. Nanofluidic rocking Brownian motors. Science 359, 1505–1508 (2018).

Hettler, S. et al. Phase masks for electron microscopy fabricated by thermal scanning probe lithography. Micron 127, 102753 (2019).

Cheng, B. et al. Ultra compact electrochemical metallization cells offering reproducible atomic scale memristive switching. Commun Phys 2, 28 (2019).

Lassaline, N. et al. Optical Fourier surfaces. Nature 582, 506–510 (2020).

Lassaline, N. et al. Freeform electronic and photonic landscapes in hexagonal boron nitride. Nano Lett 21, 8175–8181 (2021).

Gotsmann, B., Lantz, M. A., Knoll, A. & Dürig, U. Nanoscale thermal and mechanical interactions studies using heatable probes. Nanotechnology: Online 121–169 (2010) https://doi.org/10.1002/9783527628155.nanotech066.

Holzner, F. Thermal scanning probe lithography using polyphthalaldehyde. Ph.D. thesis, ETH Zurich (2013).

Lim, Y. et al. A field guide to azopolymeric optical fourier surfaces and augmented reality. Adv Funct Mater 31, 2104105 (2021).

Reda, F., Salvatore, M., Borbone, F., Maddalena, P. & Oscurato, S. L. Accurate morphology-related diffraction behavior of light-induced surface relief gratings on azopolymers. ACS Mater Lett 4, 953–959 (2022).

Wolf, H. et al. Sub-20 nm silicon patterning and metal lift-off using thermal scanning probe lithography. J Vac Sci Technol B Nanotechnol Microelectron: Mater Process Meas Phenom 33, 02B102 (2015).

Ryu Cho, Y. K. et al. Sub-10 nanometer feature size in silicon using thermal scanning probe lithography. ACS Nano 11, 11890–11897 (2017).

Marneffe, J.-Fd et al. Conversion of a patterned organic resist into a high performance inorganic hard mask for high resolution pattern transfer. ACS Nano 12, 11152–11160 (2018).

Lassaline, N. Generating smooth potential landscapes with thermal scanning-probe lithography. J Phys: Mater 7, 015008 (2023).

Min, J.-H., Hwang, S.-W., Lee, G.-R. & Moon, S. H. Redeposition of etch products on sidewalls during SiO2 etching in a fluorocarbon plasma. iv. effects of substrate temperature in a CF4 plasma. J Vac Sci Technol B Microelectron Nanometer Struct Process Meas Phenom 21, 2198–2204 (2003).

Ren, F., Pearton, S., Lothian, J., Abernathy, C. & Hobson, W. Reduction of sidewall roughness during dry etching of SiO2. J Vac Sci Technol B Microelectron Nanometer Struct Process Meas Phenom 10, 2407–2411 (1992).

Min, J.-H., Hwang, S.-W., Lee, G.-R. & Moon, S. H. Redeposition of etch products on sidewalls during SiO2 etching in a fluorocarbon plasma. i. effect of particle emission from the bottom surface in a CF4 plasma. J Vac Sci Technol A: Vac Surf Films 20, 1574–1581 (2002).

Martin, M. & Cunge, G. Surface roughness generated by plasma etching processes of silicon. J Vac Sci Technol B Microelectron Nanometer Struct Process Meas Phenom 26, 1281–1288 (2008).

Bruce, R. et al. Relationship between nanoscale roughness and ion-damaged layer in argon plasma exposed polystyrene films. J Appl Phys 107, 084310 (2010).

Lisunova, Y. & Brugger, J. Combination of thermal scanning probe lithography and ion etching to fabricate 3D silicon nanopatterns with extremely smooth surface. Microelectron Eng 193, 23–27 (2018).

William, P. et al. Parallelization of thermochemical nanolithography. Nanoscale 6, 1299–1304 (2014).

Chou, S. Y., Krauss, P. R. & Renstrom, P. J. Imprint of sub-25 nm vias and trenches in polymers. Appl Phys Lett 67, 3114–3116 (1995).

Schift, H. Nanoimprint lithography: 2D or not 2D? a review. Appl Phys A 121, 415–435 (2015).

Hoyt, J. et al. Strained silicon MOSFET technology. In Digest. International Electron Devices Meeting (IEEE, 2002).

Liu, T. et al. Crested two-dimensional transistors. Nat Nanotechnol 14, 223–226 (2019).

Liu, X. et al. Thermomechanical nanostraining of two-dimensional materials. Nano Lett 20, 8250–8257 (2020).

Li, Z. et al. Efficient strain modulation of 2D materials via polymer encapsulation. Nat Commun 11, 1151 (2020).

Cun, H. et al. Wafer-scale MOCVD growth of monolayer MoS2 on sapphire and SiO2. Nano Res 12, 2646–2652 (2019).

Chaste, J. et al. Intrinsic properties of suspended MoS2 on SiO2/Si pillar arrays for nanomechanics and optics. ACS Nano 12, 3235–3242 (2018).

Li, H. et al. Optoelectronic crystal of artificial atoms in strain-textured molybdenum disulphide. Nat Commun 6, 7381 (2015).

Conley, H. J. et al. Bandgap engineering of strained monolayer and bilayer MoS2. Nano Lett 13, 3626–3630 (2013).

Acknowledgements

The authors thank the Center of Micro/Nanotechnology (CMi) of EPFL for fabrication facilities and the Interdisciplinary Centre for Electron Microscopy (CIME) of EPFL for FIB and SEM facilities. We also thank Damien Bertrand, Leonardo Cele, Guillaume Pellerin, Fabienne Bobard, Dr. Lucie Navratilova, Dr. Cyrille Hibert and Prof. Francesc Perez-Murano for their support with fabrication processes and metrology. This work received funding from the European Research Council (ERC) under the European Union’s Horizon 2020 research and innovation program (Project MEMS4.0, ERC-2016-ADG, grant agreement No. 742685) and the EU’s H2020 framework program for research and innovation under grant agreement n. 101007417, NFFA-Europe Pilot Project. M.B. acknowledges the support of SNSF Eccellenza grant No. PCEGP2_194528, and support from the QuantERA II Programme that has received funding from the European Union’s Horizon 2020 research and innovation program under Grant Agreement No 101017733. G.F. and M.P. received funding through the European research council H2020 - UE Framework Programme for Research & Innovation (2014-2020); ERC-2017-CoG; InCell; Project number 773091, and the Swiss National Science Foundation through grant 200021_182562.

Author information

Authors and Affiliations

Contributions

B.E., A.C., X.L, G.B. and J.B. conceived and designed the experiments for t-SPL, dry etching, NIL, and 2D material strain. B.E., with the supervision of A.C., G.B. and J.B., performed t-SPL, dry etching and NIL experiments. A.C., J.P. and A.B. helped for dry etching experiments. B.E., G.B. and J.B. performed topography characterization and data analysis. X.L. and M.B. conceived and designed the experiments for 2D materials transfer and characterization. X.L. performed 2D material transfer. B.E., A.C. and X.L. performed Raman spectroscopy experiments. Z.W. and A.K. conceived and developed MoS2 growth process. Z.W., with the supervision of A.K., performed MoS2 growth. M.P. and G.F. conceived and performed AFM on 2D materials and data analysis. B.E., G.B. and J.B. wrote the manuscript with input from all the authors. J.B. coordinated and supervised the research. All authors contributed to discussions regarding the research.

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Erbas, B., Conde-Rubio, A., Liu, X. et al. Combining thermal scanning probe lithography and dry etching for grayscale nanopattern amplification. Microsyst Nanoeng 10, 28 (2024). https://doi.org/10.1038/s41378-024-00655-y

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41378-024-00655-y