Abstract

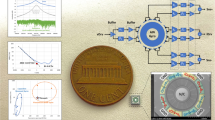

High-precision microelectromechanical system (MEMS) gyroscopes are significant in many applications. Bias instability (BI) is an important parameter that indicates the performance of a MEMS gyroscope and is affected by the 1/f noise of the MEMS resonator and readout circuit. Since the bandgap reference (BGR) is an important block in the readout circuit, reducing its 1/f noise is key to improving a gyroscope’s BI. In a traditional BGR, the error amplifier is applied to provide a virtual short-circuit point, but it introduces the main low-frequency noise sources. This paper proposes an ultralow 1/f noise BGR by removing the error amplifier and applying an optimized circuit topology. In addition, a simplified but accurate noise model of the proposed BGR is obtained to optimize the BGR’s output noise performance. To verify this design, the proposed BGR has been implemented in a 180 nm CMOS process with a chip area of 545 × 423 μm. The experimental results show that the BGR’s output integrated noise from 0.1 to 10 Hz is 0.82 μV and the thermal noise is 35 nV/√Hz. Furthermore, bias stability tests of the MEMS gyroscope fabricated in our laboratory with the proposed BGR and some commercial BGRs are carried out. Statistical results show that reducing the BGR’s 1/f noise can nearly linearly improve the gyroscope’s BI.

Similar content being viewed by others

Introduction

With the advantages of small size and high precision, high-performance MEMS gyroscopes are increasingly being applied in many applications, including inertial navigation, automobiles, and smartphones. In navigation applications, Bias instability (BI), the lowest bias error calculated by the Allan curve1, is a critical parameter used to indicate the performance of a MEMS gyroscope. The MEMS gyroscope’s BI is mainly determined by the 1/f noise of the MEMS resonator and readout circuit. With the development of MEMS resonators, readout circuit noise has become the bottleneck to improving BI2,3,4,5. Since the BGR is an important block in the readout circuit for providing a reference voltage, its 1/f noise is a key factor affecting the BI. Therefore, a low 1/f noise BGR is an attractive proposition for achieving a high-performance MEMS gyroscope.

Voltage-mode BGRs and current-mode BGRs are the two main kinds of BGRs. In current-mode BGRs, a current mirror is used to produce a current nearly invariant to temperature. However, the device mismatch and 1/f noise of the current mirror increase the BGR’s output noise. Therefore, compared with current-mode BGRs, voltage-mode BGRs are better candidates to achieve low noise6,7. A traditional voltage-mode BGR circuit is illustrated in Fig. 1a8. The error amplifier is applied to provide a virtual short-circuit point, but its 1/f noise is the main low-frequency noise source since it is multiplied by a large amplifying factor 1 + R3/R1 (usually more than 10). In previous studies, some methods have been proposed to reduce noise. A chopping technique with low-pass filters was applied in refs. 9,10, which modulates low-frequency noise to the high-frequency region and subsequently filters the noise using low-pass filters. However, modulators and filters increase power consumption and circuit complexity. An autozeroing technique11,12 was proposed to remove the offset and noise of the error amplifier. However, this is not appropriate for continuous-time applications. Lianxi Liu et al.13 proposed a noise suppression technique to reduce the amplifying factor. However, the factor is still greater than 1, and it cannot eliminate the offset and noise completely. Analog devices14 proposed a low-noise BGR topology based on dual-threshold junction field-effect transistor (JFET) technology. Since JFETs exhibit a better low-frequency noise performance than complementary metal-oxide-semiconductor field-effect transistors (CMOSFETs), BGRs based on JFETs can achieve low 1/f noise but require a special process.

This paper proposes an ultralow 1/f noise BGR for improving gyroscope performance. The simplified topology is illustrated in Fig. 1b. Compared with a traditional voltage-mode BGR, it removes the error amplifier to reduce the offset and 1/f noise. In addition, to further optimize the output noise performance, we present a simplified but accurate noise model of the proposed BGR and optimize the device parameters to suppress output noise. The noise measurement results verify the low 1/f noise characteristics of the proposed BGR. Furthermore, to verify the BGR’s effect on the gyroscope’s BI, with the proposed BGR and commercial BGRs, which have different output 1/f noise, a bias stability test of the MEMS gyroscope fabricated in our laboratory is carried out. The experimental results demonstrate the effect of reducing the BGR’s 1/f noise on improving the gyroscope’s BI.

Results

MEMS gyroscope

The block diagram of the MEMS gyroscope is illustrated in Fig. 2. With an angular velocity input, the MEMS gyroscope produces a capacitance variation ∆C due to the Coriolis force, and ∆C is proportional to the angular velocity. When ∆C is digitalized by the front-end circuit, the digital control circuit demodulates and compensates the digital information Dn and obtains the output angular velocity Ω.

The noise of readout circuits directly affects MEMS gyroscope performance, and the bias instability of MEMS gyroscopes is mainly contributed by the flicker noise in the readout circuit2. Since the BGR provides a reference voltage for the analog-to-digital converter in the front-end circuit, BGR flicker noise is a key factor affecting the bias instability of the MEMS gyroscope.

Basic principle of the proposed BGR

The BGR operates based on the characteristics of bipolar transistors. When bipolar transistors operate in the forward active region15, the base-emitter voltage VBE can be described as a function of the collector current IC and absolute temperature T.

where Vg0 is the extrapolated energy bandgap voltage at absolute zero, k is the Boltzmann constant, q is the electron charge, n is the constant process parameter, and VBE0 is the base-emitter voltage at T0 and Ic0. Since Vg0 > VBE0 + kT0/q × ln(Ic/Ic0), VBE can be nearly considered a complementary-to-absolute temperature term. The base-emitter voltage differential ΔVBE of two transistors, which have different emitter cross-sectional areas and operate at different current densities, can be expressed as (2).

where A1 and A2 are the emitter cross-sectional areas of the two transistors, and Ic1 and Ic2 are the collector currents of the two transistors. Therefore, VBE plus a voltage proportional to ΔVBE can eliminate the first-order temperature term and form a reference voltage approximately equal to Vg0, which is the basic principle of the BGR. In Fig. 1a, for traditional voltage-mode BGRs, an error amplifier composed of MOS transistors is applied to form a base-emitter voltage differential on R1. Furthermore, the amplifier can help traditional voltage-mode BGRs achieve a good power supply rejection ratio (PSRR) performance since it provides a negative feedback loop to reduce the effect of other signals on the output reference voltage. However, due to device mismatches and process variation, the error amplifier introduces input offset and 1/f noise, which is then amplified by a large factor (1 + R3/R1). Therefore, traditional voltage-mode BGRs are not appropriate for ultralow noise applications.

The specific schematic of the proposed BGR16 is illustrated in Fig. 3a. This design avoids applying an error amplifier to form a ΔVBE. In the BGR-core circuit, transistors Q1 and Q2 form a ΔVBE on R3. Neglecting the base current of bipolar transistors, the voltage on R1 is R1/R3 × ΔVBE. Therefore, the output reference voltage VREF is a VBE plus a voltage proportional to ΔVBE, and it can be expressed as (3).

where n is the emitter cross-sectional area ratio of Q2 versus Q1, r is the resistance ratio of R2 versus R1, Vc1 and Vc2 are the voltages on R1 and R2, A1 and A2 are the emitter cross-sectional areas of Q1 and Q2, and Ic1 and Ic2 are the collector currents of Q1 and Q2. By adjusting n, r, and the ratio of R1 and R3, the output voltage can be approximately equal to Vg0.

Resistors R1, R2, and R3 and transistors Q1, Q2, and Q3 form a negative feedback loop. The loop is applied to reduce the effect of other signal sources on the output voltage. In addition, the branch of Q5, R8 and R10 is utilized to produce another current IPTAT2 proportional to absolute temperature (PTAT). Then, IPTAT2 is duplicated to transistor Q3 by the current mirrors formed by transistors Q4 and Q5 and transistors Q6 and Q7. Consequently, the collector current of Q3 is directly affected by IPTAT2 rather than the supply voltage. Therefore, without an error amplifier, the negative feedback loop and the PTAT current IPTAT2 can help the BGR achieve good PSRR performance. The proposed BGR can remove the input offset and 1/f noise introduced by the error amplifier.

Due to the negative feedback loop and the source follower M1, the proposed BGR has characteristics of low output resistance and strong driving ability. A start-up circuit is applied to help the BGR work in a normal state. When the BGR is powered on, a current Icharge produced by transistor Q9 is injected into the BGR-core circuit. As transistors Q6, Q7, and M2 turn on and the BGR works normally, the base voltage of Q9 increases to a large value, and Q9 finally turns off.

1/f Noise suppression

Although an error amplifier is not applied in the design, the two current mirrors can also introduce low-frequency noise at node B in Fig. 3a. However, the 1/f noise introduced by bipolar transistors is much lower than that introduced by CMOS transistors. Furthermore, the topology can achieve an amplification factor of less than 1 to suppress the 1/f noise.

To analyze the amplification factor, a simplified circuit of the proposed BGR is illustrated in Fig. 3b, and the corresponding small-signal model is shown in Fig. 3c.

The amplification factor α is defined as the gain of the 1/f noise Vn,B at node B transferred to the output node. It can be expressed as (4).

According to Kirchhoff’s law, the 1/f noise at nodes A and C and the output reference transferred from node B can be expressed as (5), (6), and (7).

where gm1 and gm2 are the transconductances of Q1 and Q2, and rπ1, rπ2, and rπ3 are the input resistors of Q1, Q2 and Q3. Substituting (5), (6), (7) into (4), the amplification can be expressed as (8).

According to the characteristics of bipolar transistors presented in ref. 17,

Substituting (9), (10) into (8), α can be expressed as (11).

Therefore, α can be reduced by increasing rπ3, n, and r. According to (9), (10), rπ3 is inversely proportional to the collector current of Q3. When rπ3 is increased to a comparative resistor by reducing IPTAT2, (R2 + rπ3)/rπ3 is nearly equal to 1. In addition, since Vc1 roughly equals Vc2, large n and r can be applied to reduce α and ensure that α is much less than 1. Consequently, the design can apply a small current IPTAT2 and large n and r to effectively suppress the 1/f noise introduced by the two current mirrors.

Simplified but accurate output noise model

A cross-section of a typical npn bipolar transistor with parasitic resistors and capacitors is illustrated in Fig. 4a. Figure 4b presents the corresponding equivalent noise model. Since the low-frequency region is our focus and the noise model in Fig. 4b is quite complicated, the parasitic capacitors and small parasitic resistors are removed. The simplified noise model of the npn bipolar transistor is shown in Fig. 4c.

To further optimize the noise performance of this design, the effect of individual noise sources on output is analyzed. Since the noise of the two current mirrors is effectively suppressed, it is not included in the analysis. The small-signal model with RMS noise sources is presented in Fig. 5a to calculate the output noise of the proposed BGR. According to the theory proposed by ref. 18, the spectral density of individual noise sources in Fig. 5a is

where K1, K2, and K3 are process parameters inversely proportional to the device area, α1 and α2 are process constants in the range 0.5 to 2, Inc,i is the current noise due to the collector current, Inb,i is the current noise due to the base current and process, In,M1 is the current noise due to the drain current and process, βi is the current gain factor of transistor Qi, and gm,M1 is the transconductance of M1. Since every single noise source is uncorrelated, the contribution of all noise sources can be superposed directly to calculate the output reference noise.

According to Kirchhoff’s law, the total RMS output reference noise VREFnoise is as shown in (16).

The X factors in (16) are

where ro7 is the equivalent output resistor of Q7. Since the noise models of bipolar transistors are simplified to obtain the output noise model of the proposed BGR, to verify the accuracy of the noise model, output noise is calculated by Cadence and the expression in (17). The calculation of Cadence uses complex and accurate models of bipolar transistors. The simulation results are illustrated in Fig. 5b. Under different resistances of R1, the error of the simplified model is approximately 5%. Therefore, the simplified model is accurate and can be applied to analyze the noise performance of the proposed BGR.

Noise optimization

In the low-frequency region, 1/f noise is much more significant than thermal noise. Therefore, the thermal noise caused by resistors and bipolar transistors is not the main focus. In addition, since ro7 has a large resistance, X5 is much greater than 1, and the 1/f noise caused by M1 can be neglected.

According to (17)–(20), X3 > X4 > X2 > X1. Therefore, the noise caused by R3 needs to be the main focus. The 1/f noise caused by R3 to the output node can be expressed as (23).

where F is a factor that varies with n and r and K is a constant process parameter. Based on (24), the effect of noise by R3 on the output node is related to the factors n and r. Figure 5c shows the amplitude of F under different n and r. Large n and r can effectively reduce F and thus reduce the 1/f noise of the proposed BGR. Figure 5d shows the relationship between the amplification factor α and n × r, and large n and r can also effectively reduce α. Since n is the emitter cross-sectional area ratio of Q2 versus Q1, a large n means consuming a large chip area. A comparatively large r can cause a mismatch between R1 and R2 and thus introduce a high-order temperature term to deteriorate TC. Therefore, this design chooses n = 64 and r = 4 to obtain a low amplification factor α and optimize the output noise performance. Furthermore, polysilicon resistors have been chosen to implement this BGR due to the low process parameter K19.

Proposed BGR performance

The area of this BGR is 545 × 423 μm. The chip photo is shown in Fig. 6a, and Fig. 6b presents the test printed circuit board (PCB). Twenty samples from four wafers are utilized to carry out the temperature test. The temperature behaviors of the 20 chips are illustrated in Fig. 6d. Over a range from −40 to 125 °C, the best temperature coefficient (TC) is 14.61 ppm/°C, and the worst TC is 41.16 ppm/°C. Statistical results in Fig. 6e shows that the mean value of TC is 29.41 ppm/°C, and the standard deviation (1σ) is 6.77 ppm/°C. Process error is the main reason for TC deterioration. When the process error changes the designed ratio of R1 versus R3, ΔVBE cannot completely eliminate the first-order temperature term of VBE, and the residual first-order temperature term increases the TC.

a Chip photo of the proposed BGR. b Photo of the test PCB. c Noise performance test environment. d Temperature behavior of 20 tested chips. e Statistical results of the BGR temperature coefficient. f PSRR performance of the proposed BGR. g Load regulation performance of the proposed BGR. h Load regulation performance of the proposed BGR. i Noise performance of the proposed BGR. j Low-frequency noise performance of the proposed BGR, traditional voltage-mode BGR, and the BGR in ref. 13

The PSRR performance of the proposed BGR is tested from 0.5 Hz to 80 kHz, as shown in Fig. 6f. The PSRR is −90.97 dB at 0.5 Hz and −70.52 dB at 10 kHz. Even if there is no error amplifier, the proposed BGR can achieve good PSRR performance due to the negative feedback loop and the PTAT current. The BGR of a high PSRR can repress the noise source coupled with other instances in the MEMS gyroscope system, which is also important for a high-performance MEMS gyroscope. Figure 6g presents the load regulation performance of the proposed BGR. When the supply voltage varies from 2.8 to 5 V, the variation in output voltage is 0.12 mV, and the BGR line sensitivity is 0.004%/V.

Unlike other voltage-mode BGRs, this design can deliver a large load current. Figure 6h illustrates the relationship between the output voltage and load current. When the load resistor decreases to 100 Ω, the output current increases to 12.94 mA. Over the range of load current, the variation of the output voltage is 36.33 mV. However, when the load current continues to increase, the source follower M1 in Fig. 3a cannot sustain the output voltage anymore. Therefore, the proposed BGR can achieve a load regulation of ∆VREF/∆ILoad = 2.8 mV/mA up to 12.94 mA.

The noise performance test was carried out as shown in Fig. 6c. To reduce the effect of the supply voltage noise on the BGR output voltage, an ultralow noise battery is applied as the power supplier. Using the dynamic signal analyzer (HP35670A), the noise density spectrum of the proposed BGR is as shown in Fig. 6i. The thermal noise density of this BGR is 35 nV/√Hz. To calculate the low-frequency noise accurately, the low-frequency region noise density spectrum of this BGR is illustrated in Fig. 6j. The noise density at 1 Hz is 361.8 nV/√Hz. The work in ref. 13 also reduces the amplification factors, and its noise density at 1 Hz is 1.2 μV/√Hz. In addition13, it provides the simulation results of traditional voltage-mode BGR noise performance. Its noise density at 1 Hz is 11.5 μV/√Hz. Therefore, the proposed BGR in this paper further reduces the low-frequency noise compared to previous work. The integrated noise of this BGR from 0.1 Hz to 10 Hz is 0.82 μV.

Bias instability test results

To verify the effect of the BGR’s 1/f noise on the gyroscope’s BI, the proposed BGR and some commercial BGRs are utilized to carry out bias instability tests with the same MEMS gyroscope20. Figure 7a presents the die photo of the MEMS gyroscope. To eliminate the effect of environmental vibration on the gyroscope’s zero-rate output, the MEMS gyroscope is fixed on a hexahedron made of aluminum and placed on a marble table, as shown in Fig. 7b. The readout circuit of the gyroscope is illustrated in Fig. 7c, and different BGR swaps in through the switch circuit to provide a reference voltage.

a Die photo of the MEMS gyroscope. b Bias instability test environment. c Readout circuit of the MEMS gyroscope. d Allan variance curve with commercial BGR LTC6656. e Allan variance curve with commercial BGR REF3312. f Allan variance curve with commercial BGR MAX6001. g Allan variance curve with the proposed BGR. h The curve of BI versus BGR’s 1/f noise

At room temperature, the MEMS gyroscope’s output angular rate is recorded for 1 h at a sample rate of 10 Hz. The Allan variance is calculated from the sample data. The Allan variance curves with each BGR are illustrated in Fig. 7d–g. When the BGR’s low-frequency integrated noise (0.1 to 10 Hz) decreases from 6.37 to 0.82 μV, the bias instability of the MEMS gyroscope improves from 0.308°/h to 0.136°/h. The relationship between the BGR’s 1/f noise and the gyroscope’s BI is presented in Fig. 7h, which demonstrates that reducing the BGR’s 1/f noise can nearly linearly improve the gyroscope’s BI.

Discussion

The performance parameters of the proposed BGR and previously reported work are listed in Table 1. Obviously, by removing the error amplifier and optimizing the device parameters, the proposed BGR achieves a lower 1/f noise, which makes the proposed BGR suitable for high-precision applications, especially high-performance MEMS gyroscopes. However, the limitation of this BGR is a comparatively large TC since the BGR has no trimming circuits and high-order temperature compensation circuits. Lowering the TC needs to be studied in the future.

To verify the effect of BGR’s 1/f noise on the MEMS gyroscope’s BI, bias stability tests with the proposed BGR and commercial BGRs were carried out. The parameters of these BGRs are listed in Table 2. To avoid the influence of the BGR’s temperature drift on the gyroscope’s output, the proposed BGR and the chosen commercial BGR have approximate TC but different 1/f noise. The experimental setup is that different BGR swaps in through a switch circuit, and other parts in the circuit are the same. Furthermore, we repeat the bias stability tests to avoid the influence of the experimental setup and environmental interference. Statistical results demonstrate that when BGR’s integrated noise decreases from 6.48 to 0.82 μV, the gyroscope’s BI improves from 0.308°/h to 0.136°/h. Reducing the BGR’s 1/f noise can nearly linearly improve the gyroscope’s BI. Of course, the gyroscope’s BI cannot be reduced infinitely since it is also affected by other instances’ 1/f noise, such as the ADC. We will study to further improve the gyroscope’s BI in other aspects.

Materials and methods

In this paper, the parameters of this BGR are given as follows: R1 = 5 kΩ, R2 = 20 kΩ, R3 = 1.5 kΩ, R9 = R10 = R4 = R5 = 20 kΩ, R6 = 2.5 kΩ, R7 = 500 kΩ, M1 (L = 600 nm, W = 10 mm, finger = 16, multiplier = 32), M1 (L = 500 nm, W = 10 mm, finger = 8, multiplier = 1), n = 64. The proposed BGR has been implemented in a 180 nm CMOS process. The specific structure of the MEMS gyroscope is shown in ref. 20, and the MEMS gyroscope has been fabricated in a silicon-on-glass (SOG) process. The readout circuit illustrated in Fig. 7c is implemented by commercial instances. ADA4177, as a high-precision amplifier, is applied to achieve the C/V circuit and filters. AD7690 as the high-precision ADC and DAC8812 as the high-precision DAC are used.

References

IEEE standard for inertial sensor terminology. 1-26 (IEEE, 2001).

Li, Q. et al. 0.04 degree-per-hour MEMS disk resonator gyroscope with high-quality factor (510 k) and long decaying time constant (74.9 s). Microsyst. Nanoeng. 4, 32 (2018).

Zhao, Y. et al. A sub-0.1°/h bias-instability split-mode MEMS gyroscope with CMOS readout circuit. IEEE J. Solid-State Circuits 53, 2636–2650 (2018).

Rombach, S. et al. An interface ASIC for MEMS vibratory gyroscopes with a power of 1.6 mW, 92 dB DR and \(0.007^{\circ}/{\rm{s}}/\,{\sqrt{\rm{Hz}}}\) noise floor over a 40 Hz band. IEEE J. Solid-State Circuits 51, 1915–1927 (2016).

Balachandran, G. K., Petkov, V. P., Mayer, T. & Balslink, T. A 3-axis gyroscope for electronic stability control with continuous self-test. IEEE J. Solid-State Circuits 51, 177–186 (2016).

Chen, K., Petruzzi, L., Hulfachor, R. & Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C curvature-compensated CMOS bandgap reference circuit with a shared offset-cancellation method for internal amplifiers. IEEE J. Solid-State Circuits 56, 267–276 (2021).

Sanborn, K., Ma, D. & Ivanov, V. A sub-1-V low-noise bandgap voltage reference. IEEE J. Solid-State Circuits 42, 2466–2481 (2007).

Kuijk, K. E. A precision reference voltage source. IEEE J. Solid-State Circuits 8, 222–226 (1973).

Ge, G., Zhang, C., Hoogzaad, G. & Makinwa, K. A. A. A single-trim CMOS bandgap reference with a 3σ inaccuracy of ± 0.15% from -40°C to 125°C. IEEE J. Solid-State Circuits 46, 2693–2701 (2011).

Maderbacher, G. et al. 5.8 a digitally assisted single-point-calibration CMOS bandgap voltage reference with a 3σ inaccuracy of ±0.08% for fuel-gauge applications. In 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers 1–3. (IEEE, 2015).

Hunter, B. L. & Matthews, W. E. A ± 3 ppm/°C single-trim switched capacitor bandgap reference for battery monitoring applications. IEEE Trans. Circuits Syst. I: Regul. Pap. 64, 777–786 (2017).

Boo, J.-H. et al. A single-trim switched capacitor CMOS bandgap reference with a 3σ inaccuracy of +0.02%, −0.12% for battery-monitoring applications. IEEE J. Solid-State Circuits 56, 1197–1206 (2021).

Liu, L., Liao, X. & Mu, J. A 3.6 μVrms noise, 3 ppm/°C TC bandgap reference with offset/noise suppression and five-piece linear compensation. IEEE Trans. Circuits Syst. I: Regul. Pap. 66, 3786–3796 (2019).

Bowers, D. F. A 37 nV/√Hz 2.5 V reference based on dual-threshold JFET technology. In 2008 IEEE Bipolar/BiCMOS Circuits and Technology Meeting. (IEEE, 2008).

Widlar, R. J. New developments in IC voltage regulators. IEEE J. Solid-State Circuits 6, 2–7 (1971).

Zou, J. et al. A 442.1 nVpp 13.07 ppm/°C ultra-low noise bandgap reference circuit in 180 nm BCD process. In 2021 IEEE International Symposium on Circuits and Systems (ISCAS) 1–4. (IEEE, 2021).

Tsividis, Y. P. Accurate analysis of temperature effects in IC-VBE characteristics with application to bandgap reference sources. IEEE J. Solid-State Circuits 15, 1076–1084 (1980).

Gray, P. R. Analysis and Design of Analog Integrated Circuits 5th ed. (Wiley, 2009).

Brederlow, R., Weber, W., Dahl, C., Schmitt-Landsiedel, D. & Thewes, R. Low-frequency noise of integrated polysilicon resistors. IEEE Trans. Electron Devices 48, 1180–1187 (2001).

Zhang, T., Zhou, B., Yin, P., Chen, Z. & Zhang, R. Optimal design of a center support quadruple mass gyroscope (CSQMG). Sensors 16, 613 (2016).

Ji, Y., Lee, J., Kim, B., Park, H. & Sim, J. A 192-pW voltage reference generating bandgap–Vth with process and temperature dependence compensation. IEEE J. Solid-State Circuits 54, 3281–3291 (2019).

Vulligaddala, V. B., Adusumalli, R., Singamala, S. & Srinivas, M. B. A digitally calibrated bandgap reference with 0.06% error for low-side current sensing application. IEEE J. Solid-State Circuits 53, 2951–2957 (2018).

Wang, B., Law, M. K. & Bermak, A. A precision CMOS voltage reference exploiting silicon bandgap narrowing effect. IEEE Trans. Electron Devices 62, 2128–2135 (2015).

Acknowledgements

The authors would like to acknowledge support from the National Natural Science Foundation of China under grant No. 92164203.

Author information

Authors and Affiliations

Contributions

J.Z. proposed the BGR’s circuit topology and the noise model. Q.W. proposed the test methods and assisted in writing and correcting the manuscript. C.J. and H.L. conducted the noise performance test. H.G. and B.X. conducted the bias instability test, and B.Z. and R.Z. assisted in the correction of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zou, J., Wei, Q., Ju, C. et al. A 0.82 μVrms ultralow 1/f noise bandgap reference for a MEMS gyroscope. Microsyst Nanoeng 9, 48 (2023). https://doi.org/10.1038/s41378-023-00505-3

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41378-023-00505-3