Abstract

Nano-engineering III-nitride semiconductors offers a route to further control the optoelectronic properties, enabling novel functionalities and applications. Although a variety of lithography techniques are currently employed to nano-engineer these materials, the scalability and cost of the fabrication process can be an obstacle for large-scale manufacturing. In this paper, we report on the use of a fast, robust and flexible emerging patterning technique called Displacement Talbot lithography (DTL), to successfully nano-engineer III-nitride materials. DTL, along with its novel and unique combination with a lateral planar displacement (D2TL), allow the fabrication of a variety of periodic nanopatterns with a broad range of filling factors such as nanoholes, nanodots, nanorings and nanolines; all these features being achievable from one single mask. To illustrate the enormous possibilities opened by DTL/D2TL, dielectric and metal masks with a number of nanopatterns have been generated, allowing for the selective area growth of InGaN/GaN core-shell nanorods, the top-down plasma etching of III-nitride nanostructures, the top-down sublimation of GaN nanostructures, the hybrid top-down/bottom-up growth of AlN nanorods and GaN nanotubes, and the fabrication of nanopatterned sapphire substrates for AlN growth. Compared with their planar counterparts, these 3D nanostructures enable the reduction or filtering of structural defects and/or the enhancement of the light extraction, therefore improving the efficiency of the final device. These results, achieved on a wafer scale via DTL and upscalable to larger surfaces, have the potential to unlock the manufacturing of nano-engineered III-nitride materials.

Similar content being viewed by others

Introduction

III-nitride semiconductors have a crucial place in today’s optoelectronic and electronic devices1. In particular, III-nitride-based light-emitting diodes (LEDs) and laser diodes (LDs) have allowed efficiency breakthroughs in general illumination2,3, which was acknowledged by the Nobel Prize for physics in 2014 to the pioneer researchers Isamu Akasaki, Hiroshi Amano, and Shuji Nakamura “for the invention of efficient blue light-emitting diodes, which have enabled bright and energy-saving white light sources”4,5.

One key parameter to establish the performance of an LED is the external quantum efficiency (EQE), which represents the ratio of the number of charge carriers injected into the device to the number of photons emitted by the LED. The EQE is given by the product of the internal quantum efficiency (IQE) and light extraction efficiency (LEE). In III-nitride materials, where layers are grown on foreign substrates such as sapphire and silicon due to the limited availability and large cost of native substrates, the relatively high densities of defects generated during growth can have a dramatic impact on the IQE. In addition, the relatively large refractive index of III-nitride materials seriously limits the amount of light that can be extracted from the LED as the majority of photons will be trapped within the structure by total internal reflection. Nanostructuring these materials not only offers a route to improve the crystal quality and increase the light extraction6,7, but also provides an opportunity for further control of the overall device optoelectronic properties (e.g. wavelength range, lasing, doping)8,9, enabling novel functionalities and applications such as piezoelectric nanogenerators10, solar light harvesting11, water splitting12, single photon sources13, or intersubband devices14.

Compared with conventional 2D planar layers, 3D nanostructuring can, for example, reduce the dislocation density15,16, relieve the strain17, or improve the light extraction6,7. Nanostructuring can be implemented at various stages of the fabrication process of an LED device: at early stages prior to the growth of III-nitride layers, after the growth of an LED structure, or even at intermediate growth stages.

Patterning of substrates or III-nitride buffer layers has been widely used in early stages of the growth to reduce the formation of extended defects or block their propagation. Stripe micro-patterned sapphire and silicon substrates, with or without a dielectric mask, have been successfully exploited to achieve high-quality polar, semi-polar and non-polar layers with a process that is often referred to as ‘selective area growth’ (SAG) or ‘epitaxial lateral overgrowth’ (ELO) or a combination of both18,19. The geometrical shape of the pattern can also enhance light extraction by scattering or redirecting the light at the roughened substrate/III-nitride interface20. Finally, sub-micron-scale nanopatterned sapphire substrates (nano-PSS) can enhance crystal quality and light extraction21, whilst simultaneously reducing the buffer layer thickness with the benefit of further lowering production costs22.

Further improvement to enhance light extraction can be accomplished once the LED structure has been grown, either by texturing the surface of the LED23,24, shaping the LED chip25, or encapsulating the LED chip26. Surface texturing helps to break up the guided modes confined within the LED structure by creating a surface that randomizes the propagation of light and increases the probablility of photons escaping. Although surface roughening, either on the p-GaN top surface23, or at the n-side-up GaN surface24, has been successfully applied to increase light extraction, it provides poor control over the direction of the emitted light, resulting in Lambertian radiation patterns. Instead, the use of a periodic pattern provides a route to control the directionality27. In particular, photonic crystals, at the surface or embedded within the LEDs can increase the extraction efficiency, improve the directionality and enhance the IQE due to the Purcell effect28,29. In these architectures, the LED performance and directionality depends on the type, depth, filling factor and pitch of the photonic crystal along with the thickness of the epitaxial layers30.

III-nitride nanorod LEDs are an alternative to reducing the dislocation density and improving light extraction in 2D layers7,8,9. III-nitrides nanostructures can be fabricated via either a top-down or bottom-up approach. While the top-down approach typically involves nanopatterning and subsequent etching16,31, the bottom-up growth of nanostructures does not necessarily require a post-patterning process32. However, to control their position, height and size uniformity, and also to reach sufficiently homogenous optical properties, significant effort has focused on the SAG on patterned substrates or templates33,34.

Therefore, there are a number of different perspectives that provide a strong motivation for a nanolithography technique that is capable of nano-engineering III-nitride materials. However, a key requirement of the technique for its widespread use would be the capability to create large-scale nanopatterns at low cost, enabling a reduction of its impact on the overall fabrication cost. We have therefore explored Displacement Talbot lithography (DTL) as a fast and robust emerging patterning technique that can pattern rough and bowed wafers with features down to 100 nm on large areas, e.g. 4-inch wafers35. As a nanolithography process, it is considerably lower cost than electron beam lithography (EBL), and competes with nanoimprint lithography (NIL) and laser interference lithography (IL) as a wafer-scale process. However, it has advantages over both these latter processes, such as a low sensitivity to substrate surface defects, no issues with master lifetime, and a high system stability, which is of particular interest for the manufacture of nano-engineered semiconductors, including III-nitrides materials. To date, several reports using DTL have been published over the last few years, mainly focusing on resist patterning35,36,37,38, and the fabrication of metal nanoparticles39, high-aspect ratio Si nanostructures40 or high resolution gratings41.

This paper is the first comprehensive report on the use of DTL to successfully nano-engineer a wide range of III-nitride and related materials. After introducing the overall fabrication process, the DTL and extended D2TL nanopatterning capabilities are presented with the fabrication of nanoholes, nanodots, nanorings and nanolines in positive and/or negative resists. The resist patterns are transferred into dielectric or metal masks by etching or lift-off for use as a mask for bottom-up growth, top-down etching or a combination of both. Examples of such nano-engineering applied to III-nitride materials will be given, such as the bottom-up selective area growth of InGaN/GaN nanorods, the top-down etching of a variety of nanostructures from III-nitride template or LED structures, the top-down sublimation of high-aspect ratio GaN nanoholes and nanorods, and the hybrid top-down/bottom-up of AlN nanorod and GaN nanotubes. The fabrication of nanopatterned sapphire substrates and successful overgrowth and coalescence of an AlN layer will also be presented. Compared with the planar approach, these 3D nanostructures enable the reduction of defects and/or the enhancement of light extraction, therefore improving the efficiency of the final device.

Results and discussion

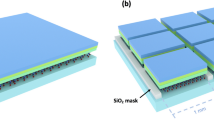

III-nitrides are robust materials that can be difficult to plasma etch. For example, III-nitrides etch at much slower rates than conventional III–V compound semiconductors42. They generally require a chlorine-based plasma and in some cases high temperatures42,43. Therefore, photoresists are unsuitable, especially when thinner resists are required to improve the resolution, a necessary requirement for nano-engineering. Instead, the use of a hard mask, either dielectric or metallic is preferred; in particular, a metal mask will be essential when deep etching or high-aspect-ratio nanostructures are desired43,44. Moreover, the selective area growth of III-nitride nanostructures requires inert and robust material such as SiNx, SiOx or TiNx15,33,34. The nanostructured dielectric layer enables enhanced adatom diffusion and preferential deposition of species on the III-nitride window. Therefore, one would ideally require a lithography method to fabricate equally well both dielectric and metal masks, which are required to nano-engineer III-nitrides. Figure 1 shows schematically the processing steps for these two mask types. More specific details of each fabrication step can be found in the ‘Materials and methods’ section.

a Coating of III-nitride wafer or substrate and DTL exposure of the resist. b, c, d For a bottom anti-reflective coating (BARC) layer hard-baked at 200 °C, the DTL pattern is first developed, then transferred via dry etching into the BARC and dielectric layer and cleaned. e, f, g For a BARC layer soft-baked at 150 °C, the DTL pattern is developed and used to create an undercut profile prior to metal evaporation and lift-off. h Dielectric mask for bottom-up growth. i Dielectric and metal mask for top-down etching. Pillars illustrated but other pattern/geometries achievable. j Combination of top-down etching and bottom-up growth

Displacement Talbot lithography

The Talbot effect, or self-imaging, is the effect of creating a periodic three-dimensional interference pattern when a periodic mask is illuminated by a coherent light45. The interference pattern reproduces itself when z is a multiple of the ‘Talbot length’. By displacing the wafer along the z-axis of illumination over integer spatial periods, the low depth of field of conventional Talbot lithography is overcome35. Figure 2a–d shows experimental patterns achieved for various doses in a positive resist for a 1-µm-pitch mask with a hexagonal arrangement of 550 nm diameter holes, which is shown in Fig. 2f. The nanohole openings increase in diameter from ~225 to ~425 nm with an increase in the exposure dose from 160 to 300 mJ/cm2. For doses >300 mJ/cm2, a secondary pattern of holes appears (Fig. 2c) and merges to create a nanoring pattern having an inner diameter of ~520 nm and a wall width of ~150 nm (Fig. 2d). Alternatively, using a negative resist creates arrays of nanodots (Fig. 2e). Our previous paper explores, by means of simulations and experiments, the resolution limit of DTL as a function of the resist employed, the configuration of the mask and the wavelength of illumination38.

Developed positive photoresist after classical DTL at a 160 mJ/cm2, b 300 mJ/cm2, c 480 mJ/cm2 and d 650 mJ/cm2. Developed negative photoresist after classical DTL at e 260 mJ/cm2. f 1 µm pitch 550 nm opening amplitude mask used to produce all the patterns presented in Fig. 2. Developed positive photoresist after D2TL for g three exposures, at x = 0, y = 0, x = 500 nm, y = 289 nm and x = 500 nm, y = 289 nm. h 3.4 µm continuous linear displacement. i triangular displacement j 250 nm radius circular displacement. k 500 nm radius circular displacement. l 750 nm radius circular displacement

The novel introduction of lateral displacements either during a single DTL exposure or between multiple exposures greatly extends the range of patterns achievable by a single mask. We call this technique ‘Double Displacement Talbot lithography’ (D2TL). Figure 2g–l shows examples of additional patterns in positive resist from the same mask. A reduction of the pitch from 1 µm to ~577 nm is obtained with multiple exposures. In Fig. 2g, the red dots represent the first exposure and the blue and green dots correspond to a second and third exposure. Continuous displacements during a single exposure can form nanogratings (via displacement along the x- or y-axis (Fig. 2h)), triangular features (via a triangular displacement (Fig. 2i)), or a wider range of circular features that cannot be obtained through simple DTL (via circular displacements of different radii (Fig. 2j–l)). The D2TL patterns presented in Fig. 2g–i represent a small sample of the D2TL capabilities, since the technique can also generate periodic arrays of complex features. Further technical details of D2TL are to be published separately46.

Therefore, for one mask configuration, a broad variety of features and configurations has been created via DTL and D2TL. Achieving the various patterns presented in Fig. 2 by NIL would require up to 11 masters. This highlights the tremendous flexibility of the technique to pattern large areas with a much lower fabrication cost than normally associated with other nanopatterning techniques.

Dielectric and metal mask for selective area growth and etching

Dielectric and metal masks can be produced from any of the previous nanopatterns presented in Fig. 2 or other configurations of the mask. Figure 3a–d presents various hexagonal arrays of periodic nanostructures transferred in a dielectric layer via inductively coupled plasma (ICP) etching. Arrays of nanoholes (Fig. 3a, b), nanorings (Fig. 3c) and nanodots (Fig. 3d) are successfully created on any dielectric layer, up to a thickness of 600–700 nm (Fig. 3d). Alternatively, metal masks are also fabricated via lift-off, as shown in Figs. 1e–g and 3e–i. Compared with dielectric material, metals generally possess a better selectivity to III-nitrides, which will facilitate deeper etching into the layer.

a 1 µm pitch nanoholes opening in 140 nm hydrogen silsesquioxane (HSQ). b Double periodicity of nanoholes opening in 30 nm HSQ, with a primary pattern of 1 µm pitch. c 1.5 µm pitch rings in 600 nm SiNx. d 1.5 µm pitch dots in 30 nm HSQ. e–g SEM cross-section image after exposure and development of the positive resist, after metal deposition and after lift-off. h SEM plan-view image of a hexagonal array of metal dots after lift-off. i Photograph of 2-inch GaN template with metal dot array on its surface

As DTL is a non-contact patterning technique, the fabrication of a dielectric mask or a metal mask is independent of the surface roughness of the III-nitride layer and the wafer bow. In contrast, contact patterning such as NIL can induce serious damage (e.g. cracks or fractures) on bowed and fragile wafers such as GaN on silicon. Hence, DTL provides a robust and reproducible fabrication process for selective area growth and top-down etching of III-nitrides at a wafer scale. Note that the fabrication process employed to create a dielectric or a metal mask can be easily transferred on any substrate (e.g. Si, Al2O3…) or other semiconductor materials (e.g. GaAs, InP, ZnO…).

Bottom-up selective area growth

Nanohole openings in a relatively thin dielectric layer are the most common configuration to perform selective area growth of nanostructures such as nanopyramids or nanorods7,8,15,33. Fig. 4 displays InGaN/GaN core-shell structures grown by MOVPE on patterned Ga-polar GaN on sapphire template. The initial nanopatterning performed via DTL allowed the successful control of the position, diameter and density of the nanorods while optimized MOVPE growth conditions enabled the vertical growth of nanostructures and additional control on the diameter15,47.

a SEM plan-view image and b tilted image of 4.2 µm height 800 nm diameter core-shell structure with three InGaN QWs. The inset in Fig. 4a displays the initial dielectric mask composed of 350 nm hole openings in 30 nm HSQ with a 1.5 µm pitch

The selective area growth of GaN nanorods and InGaN/GaN-based core-shell structures have been widely investigated over the past decades, with some promising results and properties, such as a low turn on voltage, low series resistance, short carrier lifetime48, the potential to achieve monolithic RGB emission49 and a control over the far-field emission pattern50, which is particularly attractive for specific applications such as solid state lighting, visible light communication or µ-LEDs. However, to commercialize these structures, the growth and device fabrication must be performed on a large wafer scale. Many reports employ EBL to pattern a dielectric mask7,8,15,47,49, which, despite the high resolution, often limits the area over which nanostructures can be grown. Alternatively, NIL and IL provide wafer-scale nanopatterning with reasonably high resolution7,8,33. However, NIL is sensitive to surface defects and the lifetime of the master is limited, whilst IL requires a high system stability. Here we demonstrate that DTL can be successfully used for such a purpose which could help to further reduce the cost of InGaN/GaN core-shell LEDs enabling manufacturing51,52.

Top-down fabrication of nanostructures

III-nitride dry etching

From the various DTL nanopatterns presented in Fig. 2, a broad range of III-nitride nanostructures have been obtained via chlorine-based ICP dry etching. Depending on the application targeted, the thickness, nature and configuration of the mask were optimized to achieve a wide range of periods and aspect ratios. Figure 5a–c presents arrays of GaN nanoholes, nanolines and nanorods. Figure 5d–f similarly shows arrays of AlN nanoholes, nanotubes and nanorods. Finally, Fig. 5g–i shows various nanopatterns transferred in visible and UV based III-nitride LED structures to form axial InGaN/GaN nanotubes, p-GaN/AlGaN nanopillars and AlGaN nanoholes with two periodic sizes. Nanostructures with a relatively high-aspect ratio can be achieved, such as those in Fig. 5c, f and g with values of 21.4, 7.8 and 2.2, respectively. Note that a difference in etch rate is commonly observed between III-nitride materials and explained by the higher binding energy of AlN compared with GaN and InN53. This will lead to a decrease of the etch rate with an increase in Al content54.

a Plan-view SEM image of ~600 nm depth GaN nanoholes. b 45° tilt SEM image of ~800 nm depth GaN nanolines (bottom) and related GaN grating couplers (top). c 10° tilted SEM image of ~3 µm height GaN nanorods after ICP dry etch (inset) and KOH-based wet etch at 60 °C. d Plan-view SEM image of ~150 nm depth AlN nanoholes. Inset shows a cross-section along one single nanohole. e Plan-view SEM image of ~800 nm height AlN nanotubes. f 45° tilt SEM image of ~1.8 µm height AlN nanorods after ICP dry etch and AZ400K wet etch at RT and associated photograph of 2-inch AlN nanorod template in inset. g 45° tilt SEM image of ~2.4 µm height axial InGaN/GaN nanotubes. h Plan-view SEM image of ~100 nm depth p-GaN/AlGaN nanopillars at the surface of an AlGaN based UV LED. i Plan-view SEM image of double periodicity of nanoholes at the surface of an AlGaN based UV LED with a ~250 nm depth

A common feature of the nanostructures presented in Fig. 5a–g is the presence of a relatively straight sidewall profile, regardless of the nature of the mask or of the III-nitride material. The sidewall profile of the nanostructures can be tuned by changing the plasma properties such as the pressure, the temperature, the RF power and ICP power. More details on the etching recipes and the impact of the plasma properties can be found in the ‘Materials and methods’ section and previous publications43,44,55. It is also possible to further tune the dimensions and profile of the nanostructures by further wet etching the nanostructure in a KOH-based solution. Figure 5c shows GaN nanorods before and after wet etching. As already reported in the literature, KOH-based wet etching helps to remove plasma etch damage, improves the sidewall profile and controls the geometry16,56.

These results also demonstrate the robustness of the DTL based fabrication process to high surface roughness such as pits (inset of Fig. 5a, e) or terraces (partially highlighted by a dash line in Fig. 5h). The AlN nanotubes in Fig. 5e were fabricated despite the high roughness of the initial template, as indicated on the top of the tubes after dry etching and the removal of the etch mask.

There are multiple purposes for creating nanostructures having various dimensions, geometry and filling factor. Firstly, light extraction can be improved by nano-texturing the surface of LEDs with shallow nanostructures. The nano-textured AlGaN based UVB LED surfaces presented in Fig. 5h, i will not only scatter the light and improve light extraction but also reduce the absorption within the thin top p-GaN layer that is commonly needed in UVB LEDs to get a low resistance contact. Secondly, light extraction can also be improved and directionality controlled by creating photonic crystals from dense arrays of nanoholes and nanopillars, even to the extent of achieving lasing28,29,57. Indeed, the use of multiple exposures via D2TL (Fig. 2g) is a promising approach to attain the small pitches required for photonic crystals at short wavelengths on a wafer scale. Thirdly, III-nitride photonic circuits can be created by combining grating couplers comprising dense arrays of nanolines (top SEM image in Fig. 5b) with other nano/microstructures58,59. Fourthly, the emission across the visible or the UV spectrum can be tuned by engineering the strain in an embedded active region through the control of the nanorod diameter60. Finally, nanolaser cavities, where the light is confined either between the top and bottom facet or within the circumference of the structure, can be constructed from high-aspect-ratio nanostructures such as the rods and tubes (Fig. 5c, f, g)55,56.

GaN selective area sublimation

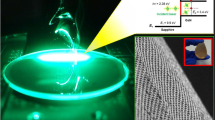

Sublimation has been recently proposed as a simple top-down route to form nanostructures such as nanorods, nanopyramids, InGaN quantum discs or nanoporous material from GaN-based material without introducing the damage that occurs in dry etching61,62,63. By protecting the GaN surface with a thermally resistant dielectric layer and then annealing the sample under vacuum and sufficiently high temperatures, selective area sublimation of GaN can be carried out through the apertures of the mask. Figure 6 displays top-down selective area sublimation experiments performed on a Ga-polar GaN-on-sapphire template with various nanopatterns etched into a 50 nm thick SiNx mask. After 3 h of sublimation within a UHV chamber and SiNx removal in buffered oxide etch (BOE), 1 µm height nanoholes are obtained (Fig. 6a, b) while 4 µm height nanorods are attained after 10 h. As expected, the initial DTL pattern provides highly organised nanostructures at a wafer scale (see inset in Fig. 6a). Both the nanoholes and the nanorods show relatively straight sidewall profiles and a horizontal to vertical sublimation rate of 2–3% due to the high thermal stability of non-polar GaN planes in vacuum.

a SEM plan-view image of 1 µm height holes in GaN. b SEM plan-view and cross-section (inset) images of double periodicity holes in GaN of ~1 µm height. c SEM-tilted image of 4-µm height 100–400-nm-diameter GaN nanorods. Inset in (a) shows a 2-inch GaN wafer during the sublimation process with one configuration of nanohole per quarter

By comparing top-down approaches, selective area sublimation provides vertical sidewalls, no etching damage, and a perfect mask selectivity, enabling the formation of high-aspect ratio nanoholes or nanorods with a very thin dielectric mask. However, sublimation is sensitive to structural defects64, occurs not only vertically but also laterally, and is only suitable for GaN and InGaN materials; not AlGaN with more than 10% Al65. Therefore, although promising for photonic applications and the nanostructuring of GaN materials62,63,65,66, ICP dry etching provides more flexibility on the type of materials that can be patterned and on the nanostructure profile.

Combined top-down/bottom-up processing

The hybrid top-down/bottom-up approach combines the fabrication of highly-uniform and organized nanostructures, such as those presented in Figs. 5 and 6, with an additional regrowth step, similar to the selective area growth in Fig. 4. Depending on the growth conditions, the initial pattern configuration and the dimensions of the nanostructures, the regrowth of III-nitride material can lead either to the formation of a planar 2D layer or to the formation of 3D nanostructures with well-defined crystallographic facets. The latter is presented in Fig. 7 where images are shown of AlN regrowth performed on AlN etched nanorods (Fig. 7a), and of GaN regrowth on GaN etched nanotubes for two growth conditions (Fig. 7b and c). For some growth conditions16,44,67,68, coalescence is inhibited, and straight and smooth non-polar sidewall facets are formed for both GaN and AlN (Fig. 7a, b). For different growth conditions, coalescence is induced, for example to create dense arrays of nanopyramidal pits from the top of GaN nanotubes (Fig. 7c).

a SEM cross-section image of AlN nanorods after AlN MOVPE regrowth. b SEM cross-section image of GaN nanotubes after GaN MOVPE regrowth. c SEM plan-view image of an array of GaN nanopyramidal pits after GaN MOVPE regrowth. Both inset SEM images in (b) and (c) show a cleaved cross-section in the middle of the tube

As the growth of AlN nanorods by selective area growth has yet to be achieved due to the high sticking coefficient and the low diffusion length of Al atoms69, the combination of top-down etching and bottom-up MOVPE growth represents a reliable approach to fabricate uniform and homogenous arrays of AlN nanorods, as shown in Fig. 7a. These are of particular interest for the subsequent growth of deep-UV core-shell structures70. The ability to fabricate further geometries, such as nanotubes (Fig. 7b) or nanopyramidal pits (Fig. 7c) opens the possibility to grow active regions such as quantum wells on specific facets or quantum dots in preferential locations. Therefore, compared with conventional MOVPE selective area growth alone, the combination of top-down etching and bottom-up regrowth enables the exploration of a broader range of nano-light-emitting architectures.

III-nitride growth can also be performed on nanostructured foreign substrates following the same fabrication process as for III-nitrides. Nanopatterned sapphire substrates (nPSS) have been obtained on 2-inch wafers either with an array of nanoholes (Fig. 8a) or nanopillars (Fig. 8b). These features are uniform across the 2-inch wafer (Fig. 8b), with a flat top c-plane preserved after fabrication (inset in Fig. 8a, b). Figure 8c shows the growth and successful coalescence of AlN layers carried out on the pillar-nPSS wafer, following growth conditions previously reported22.

a 45° tilt SEM image of nanoholes in sapphire substrate with an inset in a high-magnification cross-section image of the Al2O3 nanohole. b 45° tilt SEM image of nanopillars in sapphire substrate with an inset in a photograph of a 2-inch nPSS and a high magnification cross-section image of the Al2O3 nanopillars. c SEM cross-section image of 6-µm-thick AlN layer grown on nanopillar patterned sapphire substrate

Compared with wet etching of sapphire, which is facet dependent and thus limited in depth for small features, the combination of a thick dielectric and/or metal mask with chlorine-based top-down dry etching enable to tune both, the etch depth and sidewall profile. While the NIL process becomes less trivial for thick resist, the use of DTL allows the patterning of thick resist at the nanoscale and thus, to create thick SiNx mask.

By improving the crystal quality of the layers and the light extraction of the final device21,22, the nanostructuring of a sapphire substrate is of particular interest to improve the efficiency of DUV LEDs71. The use of DTL/D2TL constitutes a reliable and cost effective option to create nPSS with a broad range of configurations.

Conclusions

This work demonstrates the high potential of DTL for the large-scale nano-engineering of III-nitride materials for numerous optoelectronic applications as a fast, robust and scalable process. In particular, the novel and unique implementation of lateral planar displacement (D2TL) considerably extends the flexibility of the technique. As such, a broad variety of features and configurations have been obtained in positive and negative resist. DTL has been successfully used to create dielectric and metal masks, and to nano-engineer various III-nitride layers via selective area growth, selective area sublimation, top-down etching and hybrid top-down/bottom-up growth. The use of nanostructures or nano-textured surfaces is the key to achieve higher efficiency III-nitride LEDs mainly thanks to defect reduction and light extraction enhancement. It is also important to point out that the fabrication process can be transferred to any semiconductor materials such as other smaller band gap III–V materials (GaAs, InGaAs, InP…).

Despite the broad range of configurations and feature sizes already demonstrated in this paper, the capabilities of DTL in terms of resolution can be extended with a shorter wavelength illumination source. Recently, Eulitha demonstrated wafer-scale sub-wavelength features with a 266 nm source37. Therefore, by combining the D2TL approach with a shorter illumination wavelength, low pitches < 250 nm could be achieved on a wafer scale, which would be of major interest to create photonic crystals in III-nitride-based UV LEDs and further improve their efficiency71,72.

Materials and methods

DTL patterning

All DTL patternings have been performed on 2-inch wafers (Fig. 1a). A stack of two layers was spin-coated at 3000 rpm to obtain a ~270 nm bottom anti-reflective coating (BARC) (Wide 30 W—Brewer Science) layer thickness, followed by either a layer of high-contrast positive resist (Dow® Ultra-i 123 diluted with Dow® EC11 solvent) or a layer of negative resist (AZ® 15 NXT diluted with AZ® Edge Bead Remover (EBR) solvent with a 7:12 ratio by weight). The baking temperature is a critical parameter for the BARC processing as it determines the rate at which the BARC develops. A bake at 150 °C enables a wet-developable process and thus to create an undercut profile (Fig. 1e and 3e). A bake at 200 °C fully cures the BARC, making it insoluble in a developer (Fig. 1b). DTL (PhableR 100, Eulitha) was then used to expose the resist with a coherent 375 nm light source with an energy density of 1 mW.cm−2 (Fig. 1a). Various masks have been employed: two hexagonal amplitude masks, one with a 1.5 μm pitch with 800 nm diameter circular openings, and another with a 1 μm pitch with 550 nm openings, and two phase mask, one with a 500 nm pitch with 300 nm diameter circular openings, and another with lines spaced by 800 nm with a 62% filling factor. The Talbot length associated with those masks is 8.81 μm, 3.80 μm, 750 nm and 3.21 μm, respectively. Details of the calculation can be found in other publications35. The initial gap between the mask and the wafer was set to 150 μm. A Gaussian velocity integration was applied and eight Talbot lengths travel distance has been chosen to assure a homogenous integration on several Talbot motifs. After a certain exposure time (which defines the exposure dose), the sample was baked for 1 min 30 s at 120 °C on a hot plate. The wafer with a positive resist was developed in MF-CD-26 for 90–240 s (depending on the mask fabrication), the one with a negative resist in AZ 726 for 30 s. Finally, the wafer was rinsed with deionized water and dried with nitrogen.

Dielectric mask fabrication

Materials such as hydrogen silsesquioxane (HSQ) and silicon nitride (SiNx) were used as a dielectric mask. Prior to DTL patterning, HSQ was spin-coated on 2-inch wafers at 3000 rpm and baked from 150 to 450 °C in 100 °C increments or SiNx was deposited by plasma enhanced chemical vapour deposition (PECVD). The patterns created in the resist by DTL/D2TL (Figs. 1b and 2a–l) were transferred into the dielectric material (Figs. 1c and 3a–d) via an inductively coupled plasma (ICP) dry etch system (Oxford Instruments System 100 Cobra). The experiments were performed with a CHF3 chemistry of 25 sccm, a temperature set to 20 °C, a pressure of 8 mTorr, 50 W RF power and 300 W ICP source power, resulting in a etch rate of ~50 nm/min. The etching time was adjusted as a function of the thickness of the dielectric mask. The resulting transferred pattern was then cleaned in a piranha solution (H2SO4:H2O2 3:1) and oxygen plasma (Fig. 1d).

Metal mask fabrication

The undercut profile created in the BARC (cured at 150 °C) after exposure and development (Figs. 1e and 2e) was employed as a lift-off layer. Two-hundred nanometers of Ni was deposited via e-beam evaporation to produce metal masks in the circular openings at the surface of the wafer (Figs. 1f and 2f). Subsequent lift-off was achieved by soaking the wafer in MF-CD-26 developer. Finally, wafers were cleaned in a 2 min reactive-ion etching (RIE) oxygen plasma to remove any BARC residue (Figs. 1g and 2g–i).

Bottom-up growth of GaN nanorods

The selective area growth of InGaN/GaN core-shell nanorods has been carried out in a showerhead MOCVD reactor. The GaN core has been grown under continuous flow mode with the following conditions: A carrier gas mixture of N2 and H2 with H2/N2 = 2, a temperature of 1200 °C, a total reactor pressure of 100 mbar, and the TMGa and NH3 flow rates fixed at 80 sccm. Other details about the growth conditions and optimization can be found in previous publications15,47. On the GaN nanorods, five periods of InGaN/GaN QWs have been deposited using standard QW growth conditions, TMIn, TEGa and NH3 have been used as precursors, pressure has been fixed at 400 mbar and the growth temperature set between 850 and 980 °C for QWs and GaN barriers, respectively.

Top-down etching of III-nitride materials

An ICP dry etch system was used to create nanostructures in various materials including GaN, AlN, III-nitride LEDs structures and sapphire substrates. In the case of III-nitrides, the experiments were performed with a Cl2/Ar chemistry of 50/10 sccm, a temperature of 150 °C, a pressure set between 9 and 15 mTorr, a RF power set between 80 and 120 W, and 800 W ICP source power. More details can be found in previous publications16,43,44,55. For sapphire substrates, the experiments were performed with a Cl2/BCl3/Ar chemistry of 5/50/5 sccm, a temperature of 5 °C, a pressure of 8 mTorr, 100 W RF power and 600 W ICP source power. Finally, the masks were etched away in aqua-regia solution (HCl:HNO3, 3:1) for metal masks, and in BOE 5:1 for dielectric masks.

Sublimation of III-nitride materials

The samples used for the selective area sublimation were grown on 2-inch c-plane (0001) sapphire substrates by MOCVD in a 7 × 2-inch close-coupled showerhead Aixtron reactor. A 2 µm non-intentionally doped GaN layer was first grown followed by a 2 µm Si-doped (5 × 1018 cm−3) GaN layer. The first 2 µm of GaN are undoped in order to favour the coalescence of the layer after an initial 3D growth mode to reduce the threading dislocation density. DTL was used to pattern a SiNx or a SiOx dielectric mask with, respectively, holes (Fig. 3b) or dots (Fig. 3d). The samples were annealed under vacuum in a MBE chamber during 3 h at 910 °C and 10 h at 940 °C for the samples with the hole pattern and the dot pattern, respectively. More details can be found in previous publications61,62,63.

Hybrid top-down/bottom-up

The III-nitride bottom-up regrowth was carried out in a 1 × 2″ horizontal Aixtron MOVPE reactor. The growth conditions for AlN faceting on nanorod were the following: a temperature of 1100 °C, a pressure of 20 mbar, 10 sccm in TMAl flow rate, 4000 sccm in NH3 flow rate, and H2 as the carrier gas. GaN regrowth was performed at a temperature of 920 °C (Fig. 7b) or 820 °C (Fig. 7c), a pressure of 100 mbar, 8 sccm in TMGa flow rate, 2800 sccm in NH3 flow rate, and H2 as the carrier gas. More details can be found in previous publications16,44,67,68.

AlN overgrowth on nanopillar-nPSS was done in an AIX2400G3HT MOVPE planetary reactor with a capability of 11 × 2-inch wafers with standard TMAl and NH3 precursors. Pressure was fixed at 50 mbar and H2 served as carrier gas. A 50-nm-thick nucleation layer was deposited at 980 °C with a V/III ratio of 4000. After nucleation, the temperature was increased to 1380 °C with a V/III ratio of 30, followed by a decrease to 1180 °C with the same V/III ratio. More details on the growth process can be found in a previous publication22.

SEM imaging

Scanning electron microscopy (SEM) was used to monitor the fabrication process and investigate the morphology and dimensions of the structures, using a Hitachi S-4300 SEM.

References

Zhou, C. et al. Review—The current and emerging applications of the III-nitrides. ECS J. Solid State Sci. Technol. 6, Q149–Q156 (2017).

Nakamura, S. et al. The Blue Laser Diode: GaN Based Light Emitters and Lasers (Springer, Berlin, Heidelberg, 1997).

Bergh, A. A. Blue laser diode (LD) and light emitting diode (LED) applications. Phys. Stat. Sol. (A) 201, 2740–2754 (2004).

Amano, H., Sawaki, N., Akasaki, I. & Toyoda, Y. Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer. Appl. Phys. Lett. 48, 353–355 (1986).

Nakamura, S., Senoh, M. & Mukai, T. High‐power InGaN/GaN double‐heterostructure violet light emitting diodes. Appl. Phys. Lett. 62, 2390–2392 (1993).

Zhmakin, A. I. Enhancement of light extraction from light emitting diodes. Phys. Rep. 498, 189–241 (2011).

Alias, M. S. et al. Review of nanophotonics approaches using nanostructures and nanofabrication for III-nitrides ultraviolet-photonic devices. J. Nanophotonics 12, 043508 (2018).

Li, S. & Waag, A. GaN based nanorods for solid state lighting. J. Appl. Phys. 111, 071101–071123 (2012).

Zhao, S., Nguyen, H. P. T., Kibria, M. G. & Mi, Z. III-Nitride nanowire optoelectronics. Prog. Quantum Electron. 44, 14–68 (2015).

Gogneau, N. et al. From single III-nitride nanowires to piezoelectric generators: new route for powering nomad electronics. Semicond. Sci. Technol. 31, 103002 (2016).

Chatterjee, U., Park, J. H., Um, D. Y. & Lee, C. R. III-nitride nanowires for solar light harvesting: a review. Renew. Sustain. Energy Rev. 79, 1002–1015 (2017).

Wang, D. F. et al. Wafer-level photocatalytic water splitting on GaN nanowire arrays grown by molecular beam epitaxy. Nano Lett. 11, 2353–2357 (2011).

Holmes, M. J., Choi, K., Kako, S., Arita, M. & Arakawa, Y. Room-temperature triggered single photon emission from a III-nitride site-controlled nanowire quantum dot. Nano Lett. 14, 982 (2014).

Lahnemann, J., Ajay, A., Den Hertog, M. I. & Monroy, E. Near-infrared intersubband photodetection in GaN/AlN nanowires. Nano Lett. 17, 6954–6960 (2017).

Coulon, P.-M. et al. Dislocation-filtering and polarity in the selective area growth of GaN nanowires by continuous-flow MOVPE. Appl. Phys. Express 9, 015502 (2016).

Coulon, P.-M. et al. Hybrid top-down/bottom-up fabrication of highly uniform and organized faceted AlN nanorod scaffold. Materials 11, 1140 (2018).

Hugues, M. et al. Strain evolution in GaN nanowires: from free-surface objects to coalesced templates. J. Appl. Phys. 114, 084307 (2013).

Beaumont, B., Vennéguès, P. & Gibart, P. Epitaxial Lateral overgrowth of GaN. Phys. Stat. Sol. (B) 227, 1–43 (2001).

Vennéguès, P. Defect reduction methods for III-nitride heteroepitaxial films grown along nonpolar and semipolar orientations. Semicond. Sci. Tech. 27, 024004 (2012).

Wuu, D. S. et al. Enhanced output power of near-ultraviolet InGaN-GaN LEDs grown on patterned sapphire substrates. IEEE Photonics Technol. Lett. 17, 288–290 (2005).

Su, Y. K. et al. Pattern-size dependence of characteristics of nitride-based LEDs grown on patterned sapphire substrates. J. Cryst. Growth 311, 2973–2976 (2009).

Hagedorn, S., Knauer, A., Mogilatenko, A., Richter, E. & Weyers, M. AlN growth on nano-patterned sapphire: a route for cost efficient pseudo substrates for deep UV LEDs. Phys. Stat. Sol. (A) 213, 3178–3185 (2016).

Huh, C., Lee, K. S., Kang, E. J. & Park, S. J. Improved light-output and electrical performance of InGaN-based light-emitting diode by microroughening of the p-GaN surface. J. Appl. Phys. 93, 9383–9385 (2003).

Fujii, T. et al. Increase in the extraction efficiency of GaN-based light-emitting diodes via surface roughening. Appl. Phys. Lett. 84, 855–857 (2004).

David, A. et al. High light extraction efficiency in bulk-GaN based volumetric violet light-emitting diodes. Appl. Phys. Lett. 105, 231111 (2014).

Ma, M. et al. Effects of the refractive index of the encapsulant on the light-extraction efficiency of light-emitting diodes. Opt. Express 19, A1135–A1140 (2011).

Fox, S., O’Kane, S., Lis, S. & Allsopp, D. Designing InGaN/GaN nano‐LED arrays for étendue‐limited applications. Phys. Stat. Sol. (C.) 12, 456–459 (2015).

Oder, T. N., Shakya, J., Lin, J. Y. & Jiang, H. X. III-nitride photonic crystals. Appl. Phys. Lett. 83, 1231 (2003).

Wierer, J. J., David, A. & Megens, M. M. III-nitride photonic-crystal light-emitting diodes with high extraction efficiency. Nat. Photon 3, 163–169 (2009).

David, A., Benisty, H. & Weisbuch, C. Optimization of light-diffracting photonic-crystals for high extraction efficiency LEDs. J. Disp. Tech. 3, 133–148 (2007).

Wang, T. et al. Fabrication and optical investigation of a high-density GaN nanowire array. Appl. Phys. Lett. 86, 103103 (2005).

Alloing, B. & Zúñiga-Pérez, J. Metalorganic chemical vapor deposition of GaN nanowires: from catalyst-assisted to catalyst-free growth, and from self-assembled to selective-area growth. Mater. Sci. Semicond. Process. 55, 51–58 (2016).

Hersee, S. D., Sun, X. Y. & Wang, X. The controlled growth of GaN nanowires. Nano Lett. 6, 1808–1811 (2006).

Kishino, K., Sekiguchi, S. & Kikuchi, A. Improved Ti-mask selective-area growth (SAG) by rf-plasma-assisted molecular beam epitaxy demonstrating extremely uniform GaN nanocolumn arrays. J. Cryst. Growth 311, 2063 (2009).

Solak, H. H., Dais, C. & Clube, F. Displacement Talbot lithography: a new method for high-resolution patterning of large areas. Opt. Express 19, 10686–10691 (2011).

Solak, H. H., Dais, C., Clube, F. & Wang, L. Phase shifting masks in Displacement Talbot Lithography for printing nano-grids and periodic motifs. Microelectron. Eng. 143, 74–80 (2015).

Wang, L., Clube, F., Dais, C., Solak, H. H. & Gobrecht, J. Sub-wavelength printing in the deep ultra-violet region using Displacement Talbot Lithography. Microelectron. Eng. 161, 104–108 (2016).

Chausse, P. J. P., Le Boulbar, E. D., Lis, S. D. & Shields, P. A. Understanding resolution limit of displacement Talbot lithography. Opt. Express 27, 5918 (2019).

Le-The, H. et al. Large-scale fabrication of highly ordered sub-20 nm noble metal nanoparticles on silica substrates without metallic adhesion layers. Microsyst. Nanoengineering 4, 4 (2018).

Wilbers, J. G. E. et al. 3D-fabrication of tunable and high-density arrays of crystalline silicon nanostructures. J. Micromech. Microeng. 28, 044003 (2018).

Chen, H. et al. Refined grating fabrication using Displacement Talbot Lithography. Microelectron. Eng. 189, 74–77 (2018).

Shul, R. J. et al. High-density plasma etch selectivity for the III–V nitrides. Solid State Electron 42, 2269–2276 (1998).

Le Boulbar, E. D., Lewins, C. J., Allsopp, D. W. E., Bowen, C. R. & Shields, P. A. Fabrication of high-aspect ratio GaN nanostructures for advanced photonic devices. Microelectron. Eng. 153, 132–136 (2016).

Coulon, P.-M. et al. Hybrid top-down/bottom-up fabrication of regular arrays of AlN nanorods for deep-UV core-shell LEDs. Phys. Stat. Sol. (B) 255, 1700445 (2018).

Patorski, K. The self-imaging phenomenon and its applications. Prog. Opt. 27, 1–108 (1989).

Chausse, P., Le Boulbar, E., Coulon, P.-M. & Shields, P. A. ‘Double’ Displacement Talbot Lithography: fast, wafer-scale, direct-writing of complex periodic nanopatterns. (Submitted).

Coulon, P.-M. et al. Selective area growth of Ga‐polar GaN nanowire arrays by continuous‐flow MOVPE: A systematic study on the effect of growth conditions on the array properties. Phys. Stat. Sol. (B) 252, 1096–1103 (2015).

Koester, R. et al. High-speed GaN/GaInN nanowire array light-emitting diode on silicon (111). Nano. Lett. 15, 2318–2323 (2015).

Nami, M. et al. Tailoring the morphology and luminescence of GaN/InGaN core–shell nanowires using bottom-up selective area epitaxy. Nanotechnology 28, 025202 (2016).

Yanagihara, A., Ishizawa, S. & Kishino, K. Directional radiation beam from yellow-emitting InGaN-based nanocolumn LEDs with ordered bottom-up nanocolumn array. Appl. Phys. Express 7, 112102 (2014).

Pougeoise, E. & Dussaigne, A. Opto-electric device has microwires or nanowires semiconductor and process for its manufacturing. FR2995729B1 (2016).

Konsek, S., Ohlsson, J., Martynov, Y. & Hanberg, P. J. Nanostructured L. E. D. US9595649B2 (2017).

Costales, A., Blanco, M. A., Pendas, A. M., Kandalam, A. K. & Pandey, R. Chemical bonding in group III nitrides. J. Am. Chem. Soc. 124, 4116–4123 (2002).

Shah, A. P., Laskar, M. R., Rahman, A. A., Gokhale, M. R. & Bhattacharya, A. Inductively coupled plasma–reactive ion etching of c- and a-plane AlGaN over the entire Al composition range: effect of BCl3 pretreatment in Cl2/Ar plasma chemistry. J. Vac. Sci. Technol. A 31, 061305 (2013).

Coulon, P.-M. et al. Optical properties and resonant cavity modes in axial InGaN/GaN nanotube microcavities. Opt. Express 25, 28246–28257 (2017).

Li, Q. et al. Single-mode GaN nanowire lasers. Opt. Express 20, 17873–17879 (2012).

Wright, J. B. et al. Multi-colour nanowire photonic crystal laser pixels. Sci. Rep. 3, 2982 (2013).

Liu, Q. et al. Freestanding GaN grating couplers at visible wavelengths. J. Opt. 17, 045607 (2015).

Tabataba-Vakili, F. et al. Blue microlasers integrated on a photonic platform on silicon. ACS Photonics 5, 3643–3648 (2018).

Chung, K., Sui, J., Demory, B., Teng, C. & Ku, P. Monolithic integration of individually addressable light-emitting diode color pixels. Appl. Phys. Lett. 110, 111103 (2017).

Damilano, B., Vézian, S., Brault, J., Alloing, B. & Massies, J. Selective area sublimation: a simple top-down route for GaN-based nanowire fabrication. Nano. Lett. 16, 1863–1868 (2016).

Damilano, B., Vézian, S. & Massies, J. Photoluminescence properties of porous GaN and (Ga,In)N/GaN single quantum well made by selective area sublimation. Opt. Express 25, 33243 (2017).

Damilano, B. et al. Top-down fabrication of GaN nano-laser arrays by displacement Talbot lithography and selective area sublimation. Appl. Phys. Express 12, 045007 (2019).

Grandjean, N. et al. GaN evaporation in molecular-beam epitaxy environment. Appl. Phys. Lett. 74, 1854–1856 (1999).

Arita, M., Kako, S., Iwamoto, S. & Arakawa, Y. Fabrication of AlGaN two-dimensional photonic crystal nanocavities by selective thermal decomposition of GaN. Appl. Phys. Express 5, 126502 (2012).

Mitsunari, T., Tanikawa, T., Honda, Y., Yamaguchi, M. & Amano, H. AlN/air distributed Bragg reflector by GaN sublimation from microcracks of AlN. J. Cryst. Growth 370, 16–21 (2013).

Le Boulbar, E. D. et al. Facet recovery and light emission from GaN/InGaN/GaN core-shell structures grown by metal organic vapour phase epitaxy on etched GaN nanorod arrays. J. Appl. Phys. 114, 094302 (2013).

Girgel, I. et al. Investigation of indium gallium nitride facet-dependent nonpolar growth rates and composition for core–shell light-emitting diodes. J. Nanophotonics 10, 016010 (2016).

Banal, R. G., Funato, M. & Kawakami, Y. Surface diffusion during metalorganic vapor phase epitaxy of AlN. Phys. Stat. Sol. (C) 6, 599–602 (2009).

Coulon, P.-M., Kusch, G., Martin, R. W. & Shields, P. A. Deep UV emission from highly ordered AlGaN/AlN core–shell nanorods. ACS Appl. Mater. Interfaces 10, 33441–33449 (2018).

Kneissl, M., Seong, T., Han, J. & Amano, H. The emergence and prospects of deep-ultraviolet light-emitting diode technologies. Nat. Photonics 13, 233–244 (2019).

Kashima, Y. et al. High external quantum efficiency (10%) AlGaN based deep-ultraviolet light-emitting diodes achieved by using highly reflective photonic crystal on p-AlGaN contact layer. Appl. Phys. Express 11, 012101 (2018).

Acknowledgements

The authors would like to acknowledge financial support of the EPSRC, UK via Grant No. EP/M015181/1, “Manufacturing nano-engineered III-nitrides”. This work has been supported by the technology facility network RENATECH and the French National Research Agency (ANR) through the project NAPOLI (ANR-18-CE24-0022), and the “Investissements d’Avenir” program GaNeX (ANR-11-LABX-0014). This work was partially supported by the German Federal Ministry of Education and Research (BMBF) through the consortia project “Advanced UV for Life” under contract 03ZZ0134B and by the German Research Foundation (DFG) within the Collaborative Research Center Semiconductor Nanophotonics (CRC 787). This publication is supported by multiple data sets, which are openly available at https://doi.org/10.15125/BATH-00696.

Author information

Authors and Affiliations

Contributions

P.-M.C. conceived the experimental work, supervised by P.A.S. P.-M.C. carried out the DTL patterning, dielectric and metal mask fabrication, ICP dry etching, MOVPE regrowth experiment on etched nanostructures, and related SEM characterization. P.C. carried out the D2TL patterning. B.D. and S.V. performed the sublimation experiments by MBE and related SEM characteization. B.A. grew the InGaN/GaN core-shell structure via bottom-up MOVPE. S.W. and S.H. overgrew AlN layers on nPSS. J.E. grew the UV LED structure. R.A. carried out the fabrication of AlN nanotubes. All of the authors contributed in analysing and writing the results.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Coulon, PM., Damilano, B., Alloing, B. et al. Displacement Talbot lithography for nano-engineering of III-nitride materials. Microsyst Nanoeng 5, 52 (2019). https://doi.org/10.1038/s41378-019-0101-2

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41378-019-0101-2

This article is cited by

-

Large Dense Periodic Arrays of Vertically Aligned Sharp Silicon Nanocones

Nanoscale Research Letters (2022)

-

Tripling the light extraction efficiency of a deep ultraviolet LED using a nanostructured p-contact

Scientific Reports (2022)

-

Tunneling-induced Talbot effect

Scientific Reports (2021)

-

Strain-induced yellow to blue emission tailoring of axial InGaN/GaN quantum wells in GaN nanorods synthesized by nanoimprint lithography

Scientific Reports (2021)

-

Influence of the reactor environment on the selective area thermal etching of GaN nanohole arrays

Scientific Reports (2020)