Abstract

With the fast development of artificial intelligence (AI), Internet of things (IOT), etc, there is an urgent need for the technology that can efficiently recognize, store and process a staggering amount of information. The AlScN material has unique advantages including immense remnant polarization, superior temperature stability and good lattice-match to other III-nitrides, making it easy to integrate with the existing advanced III-nitrides material and device technologies. However, due to the large band-gap, strong coercive field, and low photo-generated carrier generation and separation efficiency, it is difficult for AlScN itself to accumulate enough photo-generated carriers at the surface/interface to induce polarization inversion, limiting its application in in-memory sensing and computing. In this work, an electro-optic duplex memristor on a GaN/AlScN hetero-structure based Schottky diode has been realized. This two-terminal memristor shows good electrical and opto-electrical nonvolatility and reconfigurability. For both electrical and opto-electrical modes, the current on/off ratio can reach the magnitude of 104, and the resistance states can be effectively reset, written and long-termly stored. Based on this device, the “IMP” truth table and the logic “False” can be successfully reproduced, indicating the huge potential of the device in the field of in-memory sensing and computing.

Similar content being viewed by others

Introduction

With the fast development of artificial intelligence (AI), Internet of things (IOT), etc, there is an urgent need for the technology that can efficiently recognize, store and process a staggering amount of information1,2,3,4,5,6. Traditional data processing based on Von Neumann architecture generally separates the sensing, storage and computing units, and thus massive data will be transported among the units, causing the bottleneck of storage wall7,8. The in-memory sensing and computing devices, wherein an optical signal can be detected and stored for calculation and the calculated results can be re-stored in the same unit, are promising to break the bottleneck9. The memristors can realize the in-memory computing and numerous materials can be applied to prepare memristors including two-dimensional materials like transition metal sulfides, inorganic phase change materials like oxides and perovskites, and ferroelectric materials like In2Se310,11,12,13,14,15,16,17,18,19,20. Moreover, some of the memristors are photosensitive, which can be implemented to in-memory sensing and computing14,17,18,21.

Although the above materials provide terrific opportunities for realizing in-memory sensing and computing, the material scale, stability, and quality cannot be effectively guaranteed at present from the real application perspective. To choose a photosensitive and storable material that is compatible with the current mainstream semiconductor materials and processes is of great significance for the concept implementation of in-memory sensing and computing. As a ferroelectric material, AlScN has unique advantages including immense remnant polarization and superior thermal stability22,23, which is a good storage material. Moreover, the AlScN is very easy to integrate with III-nitrides, which are very mature in terms of both material and device fabrication process, due to their similar element composition and crystal structure. Recently, great progress has been made for AlScN materials, such as the ultrathin AlScN memristor, and the scalable CMOS back-end-of-line-compatible AlScN-based ferroelectric transistor by wafer level fabrication process24,25,26,27,28,29,30.

However, because of the large band-gap, strong coercive field, and low photo-generated carrier generation and separation efficiency23,31, it is difficult for the AlScN itself to accumulate enough photo-generated carriers at the surface/interface to induce polarization inversion18,32,33. Hence, it is necessary to construct a photosensitive AlScN memristor for in-memory sensing and computing. As a representative of the third generation semiconductors, GaN presents excellent photoelectric characteristics such as direct band-gap, strong ultraviolet absorption, and high carrier mobility, and is widely applied to detection, light-emission and optoelectronic integration34,35,36,37,38. Besides, as mentioned above, AlScN is easy to integrate with GaN to form hetero-structure due to their similar element composition and crystal structure. Moreover, GaN can form strong polarization hetero-structure with AlScN because it possesses strong spontaneous and piezoelectric polarization, providing great space for built-in field regulation. Thus, to combine the ferroelectric AlScN with photosensitive GaN to form hetero-structure is promising to realize high performance memristor, taking advantages of the high industrial maturity of III-nitrides to promote the in-memory sensing and computing.

Here, we fabricate a two-terminal nonvolatile and reconfigurable III-nitride based electro-optic duplex memristor. The device is an n-GaN/i-GaN/AlScN hetero-structure based Schottky diode, in which the i-GaN and AlScN determine the photosensitive and storage characteristics, respectively. For both electrical and opto-electrical modes, the current on/off ratio can reach the order of 104, and the resistance states can be effectively reset, written and long-termly stored. At electrical mode, the resistance state change originates from the ferroelectric polarization inversion of the AlScN layer in the hetero-structure, which influences the depletion region width and electron transport barrier height of the device. At opto-electrical mode, the memory window can be controlled by the illuminating light intensity due to the photoconductive effect of the i-GaN layer and the photoinduced electron transport barrier reduction effect, which can regulate the partial bias applied to the AlScN layer. Based on this device, the material implication (IMP) truth table and the logic “False” can be successfully reproduced, indicating the huge potential of our device in the field of in-memory sensing and computing.

Results

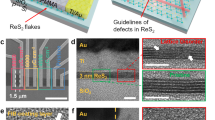

To fully utilize the photosensitive property of the GaN material and the ferroelectric property of the AlScN material, a hetero-structure composed of undoped GaN/AlScN (i-GaN/AlScN) is designed. The i-GaN layer thickness is ~300 nm and the AlScN layer thickness is ~60 nm. The hetero-structure is grown on a thick n-type GaN/sapphire template by metal-organic chemical vapor deposition (MOCVD) and magnetron sputtering, respectively, to form the n-GaN/i-GaN/AlScN heterojunction (see “Materials and methods” section). Figure 1a exhibits the bright field (BF) scanning transmission electron microscope (STEM) image along <11-20> direction and its corresponding Al, Sc, Ga, N element X-ray energy dispersive spectroscopy (EDS) mappings of the i-GaN/AlScN hetero-structure. It can be clearly seen that the hetero-structure indeed contains GaN and AlScN layers and the AlScN layer thickness is actually ~60 nm39.

a BF-STEM image and corresponding Al, Sc, Ga, N element EDS mappings of the i-GaN/AlScN hetero-structure. b HR-BF-STEM image near the GaN/AlScN interface. c HR-HADDF-STEM image of the area marked by the white box I in (b). d Enlarged HR-HADDF-STEM images of the areas marked by the white box II–VII in (b, c) and their corresponding atomic arrangement. All STEM images are captured along <11-20> direction. e, f Scanning PFM phase and amplitude images of the epilayer after applying a bias of +10 V and −10 V, respectively. g XRD 2theta scanning for the GaN/AlScN epilayer and the reference GaN template

To investigate the crystal structure of the hetero-structure, high-resolution (HR) BF-STEM image along <11-20> direction near the interface is captured as shown in Fig. 1b, from which we can observe that the i-GaN layer has a relatively regular atomic arrangement, while the upper AlScN layer has a relatively chaotic atomic arrangement. To further confirm the atomic arrangement of the AlScN layer, a HR high-angle annular dark-field (HAADF) STEM image along <11-20> direction, as shown in Fig. 1c, is taken in the area marked by the while box I in Fig. 1b. It can be seen that there are obvious grain boundaries. Figure 1d shows the enlarged HR-HAADF-STEM images of the areas marked by the while boxes II–VII in Fig. 1b, c and their corresponding atomic arrangement, successively. The i-GaN layer is strictly c-oriented (Fig. 1d II), while different areas of the AlScN layer show different lattice orientations. The area III (Fig. 1d III) is c-oriented, the area IV is c deviating a-b oriented (Fig. 1d IV), and the areas V ~ VII are c deviating b-a oriented with different deviation angles (Fig. 1d V–VII), respectively. These results demonstrate that the i-GaN layer has strict c-oriented single crystal structure, while the AlScN layer has polycrystalline structure with c-preferred orientation, which is mainly determined by the growth methods.

To verify the ferroelectricity of the prepared AlScN layer, the piezoelectric force microscope (PFM) domain writing test is conducted on the n-GaN/i-GaN/AlScN heterojunction. The scanning PFM phase and amplitude images after applying a bias of +10 V and −10 V are shown as Fig. 1e, f, respectively. Clear boundaries between different applying bias areas are observed in the images, demonstrating that different applying bias corresponds different ferroelectric polarization directions, and further indicating that the polarization direction of the AlScN layer can be changed by the applied bias within ±10 V, implying the potential to manufacture a memory device of the grown hetero-structure. The X-ray diffraction (XRD) 2theta scanning is employed to estimate the Sc content. As shown in Fig. 1g, the diffraction curve of the GaN/AlScN epi-wafer exhibits obvious peaks near 34.5° and 36.0°, which reflect the GaN (0002) plane and the AlScN (0002) plane, respectively23. Accordingly, the c lattice constant of the AlScN layer can be roughly calculated to be 4.9854 Å, from which the Sc content can be estimated to be about 34%40,41. In addition, the very wide full width at half maximum (FWHM) of the 2theta scanning curve further indicates the c-preferred polycrystalline structure of the AlScN epilayer, as discussed above.

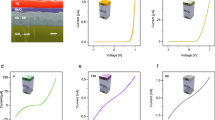

Standard III-nitride based device fabrication process is employed to make the memristor (see “Materials and Methods” section). The schematic diagram of the device is shown in Fig. 2a. In reality, the device is a typical GaN/AlScN hetero-structure based Schottky diode. Figure 2b shows the current-voltage (IV) hysteresis loops of the device with different initial applied voltage from 0 V to −10 V, from which the memristor characteristics is displayed. Anticlockwise IV hysteresis is observed, which is due to the ferroelectric polarization inversion of the AlScN layer42. The higher the initial reverse bias, the higher the current explosion voltage and thus the wider the memory window, and even at an reverse bias of 10 V, the current explosion voltage is still not saturated. This result indicates that applying reverse bias to the device can induce the ferroelectric polarization inversion of the AlScN layer while an reverse bias of 10 V can not fully polarize the AlScN layer. Nonetheless, the bias of −10 V can still reset the device to high resistance state (HRS).

a Schematic diagram of the device. b IV hysteresis loops with initial scanning voltage from 0 to −10 V. c Schematic diagram of the variation of the AlScN ferroelectric polarization and device energy band with the applied bias. d IV hysteresis loops after electric pulse of −10 V from 10 μs to 1 s. e, f Retention properties of the device with rectangular electric reset and write pulses of –10 V and 7 V and read bias of 5 V. Pulse widths for reset, write and read are 1 s, 1 s, and 5 s, respectively. Storage time is 1000 s without bias. g Cyclically program and erase for the device with rectangular write and reset pulses of 7 V and −10 V and read bias of 5 V. Pulse widths for reset, write and read are 2 s, 2 s, and 5 s, respectively

Figure 2c displays the schematic diagrams of the energy band structure and the polarization of the device at different stage in the IV hysteresis loop. In the initial case, corresponding to the process ① in Fig. 2b, reverse bias upward polarizes the AlScN layer, and negative polarization charges at the i-GaN/AsScN interface are induced, significantly increasing the electron potential barrier height φB. The high barrier will impede the electron transport through the depletion region, and place the device in the HRS. With the increase of forward bias, corresponding to the process ② in Fig. 2b, the depletion region width shortens and the bias applied on the AlScN layer increases, resulting in weaker polarization in the AlScN layer and thus lower the φB. The current changes from drift to diffusion and gradually increases. When the bias further increases, the electric field in the AlScN layer exceeds the coercive field, causing ferroelectric polarization inversion. The polarization direction of the AlScN layer changes downward and the interface polarization charges change from negative to positive, thus reducing the φB. Due to the reduction of the depletion region width and the φB, the device inverts to low resistance state (LRS) and the current increases abruptly. As the bias reduces, corresponding to the process ③ and part of process ④ in Fig. 2b, since the ferroelectric polarization direction of the AlScN layer is not changed, the device keeps LRS. At 5 V bias, the HRS to LRS ratio (on/off ratio) can reach ~104. Further applying reverse bias, corresponding to part of the process ④ in Fig. 2b, the ferroelectric polarization in the AlScN layer undergoes inversion and the depletion region width and the φB again increase to the initial state. Eventually, the device returns to HRS and waits to enter the next cycle.

The IV hysteresis curves imply that the magnitude of the applied bias is crucial for the degree of the ferroelectric domain inversion in the AlScN layer, and the duration of the applied bias is crucial, too. Pulse bias of -10 V with different pulse widths is applied to initiate the device and the IV hysteresis curve under forward bias is measured to observe the memory window change, as shown in Fig. 2d. Before measurements, a bias pulse with magnitude of 7 V and width of 5 s is applied to polarize the AlScN layer to the same state. As is seen, with the increase of the pulse width from 10 μs to 1 s, the memory window gradually widens and the current explosion voltage increases from 6.4 V to 6.8 V. It proves that when the applied electric field exceeds the coercive field, the ferroelectric domain walls begin to move, but it will take a certain period to move sufficiently and then trigger polarization inversion. Nonetheless, a short pulse of 10 μs is sufficient to trigger partial polarization inversion of the AlScN layer and then to form wide enough memory window, indicating the huge application potential of the GaN/AlScN hetero-structure based Schottky diode type memristor.

Furthermore, to verify the storage performance of the device, retention properties at HRS and LRS are measured as shown in Fig. 2e, f, respectively. The reset and write electric rectangular pulses are set to be –10 V and 7 V and the read voltage is set to be 5 V, respectively, according to the IV hysteresis curves. Then the resistance state is stored for 1000 s at zero-bias. As is seen, the HRS and LRS can be effectively reset and write to the device, and resistance state can be successfully read after 1000 s zero-bias standing, demonstrating the good electrical nonvolatility. Figure 2g shows the cyclic programming and erasing process of the device, which exhibits good cycling characteristics and stability, demonstrating the good electrical reconfigurability.

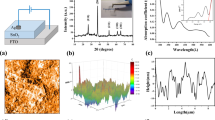

Since the GaN/AlScN hetero-structure based Schottky diode type memristor contains the GaN photosensitive material, it is very potential to employ light to control the memory characteristics for the device, namely realizing optically controlled memristor43,44,45,46. Therefore, the optical characteristics is measured by employing an ultraviolet (UV) light illumination using a light-emitting diode (LED) with a peak wavelength of 355 nm. The IV hysteresis curves in dark and under illumination with light intensity from 100 to 1000 μW cm−2 are shown in Fig. 3a. To ensure the consistency of the initial state of the device for each test, a rectangular pulse bias of −10 V and 5 s is applied to the device to polarize the AlScN layer. It is found that, compared to the dark state, the low-bias current under illumination is effectively increased and the photocurrent increases with the light intensity increasing. More importantly, compared to the dark state, the current explosion voltage is obviously reduced and continuously decreasing with the light intensity increasing. When the light intensity increases from 0 to 1000 μW cm−2, the current explosion voltage decreases from ~6.6 V to ~5 V. These results indicate that this device is optically controllable, as expected.

a IV hysteresis loops measured with different light intensity from 100 to 1000 μW cm−2. A 355 nm-LED is used as the light source. Before measurements, the device is reset to HRS by electric rectangular pulse of −10 V and 5 s. b Schematic diagrams of the variation of the AlScN ferroelectric polarization and device energy band under illumination. c, f Schematic diagrams of the device energy band at HRS and LRS under illumination, respectively. d, g IT curves at HRS and LRS under different pulse light intensity at 2 V working bias. e, h IT curves at HRS and LRS under different working bias at 300 μW cm−2 UV light illumination

Figure 3b schematically depicts the optical control mechanism of the device. If the device is working at a relatively low bias that is not high enough to trigger the AlScN ferroelectric polarization inversion (i), for example 4 V, even the UV illumination can produce electron-hole pairs, increase the i-GaN conductance, reduce the depletion region width, and reduce the φB, the photoinduced voltage increase upon the AlScN layer is still not high enough to trigger the inversion. Without the inversion, the device keeps HRS and the photoinduced current change is relatively small and cannot be stored (ii). If the device is working at a relatively high bias that is still not high enough to trigger the AlScN ferroelectric polarization inversion (i), for example 6 V, the photoinduced voltage increase upon the AlScN layer becomes high enough to trigger the inversion, inverting the device to LRS (iii). It is worth emphasizing that, even if the device works at a very low bias under which employing UV illumination cannot trigger the AlScN ferroelectric polarization inversion, the resistance state of the device is also related to the light intensity, due to the photoconductive effect and the φB variation.

At the HRS, as shown in Fig. 3c, the photo-generated carriers can effectively increase the i-GaN conductance, reduce the depletion region width, and reduce the φB, thus altering the current. If the applied bias and the illuminated light intensity cannot induce the AlScN ferroelectric polarization inversion, once the illumination is removed, the device will recover to its original HRS. After setting the device to HRS by applying an electric rectangular pulse of −10 V and 5 s, the time-dependent current (IT) curves under 2 V bias at an UV light pulse width of 1 s with different intensity, and the IT curves at an UV light pulse with width of 1 s and intensity of 300 μW cm−2 under different bias, are measured as shown in Fig. 3d, e, respectively. At the LRS, as shown in Fig. 3f, the photo-generated carriers will mainly influence the i-GaN conductance and the barrier width, thus altering the current. Similarly, if the applied bias and the illuminated light intensity cannot induce the AlScN ferroelectric polarization inversion, once the illumination is removed, the device will recover to its original LRS. After setting the device to LRS by applying an electric rectangular pulse of 7 V and 5 s, the IT curves under 2 V bias at an UV light pulse width of 1 s with different intensity, and the IT curves at an UV light pulse with width of 1 s and intensity of 300 μW cm−2 under different bias, are measured as shown in Fig. 3g, h, respectively. For both HRS and LRS, it is found that when the light is off, the current rapidly decrease, demonstrating the photoinduced resistance state change cannot be long-termly stored without the AlScN ferroelectric polarization inversion.

According to the analyses above, it is confirmed that at working bias below 4 V, the polarization of the AlScN layer in the device will not reverse even the illumination light intensity reaches 1000 μW cm−2. Although the UV light illumination can momentarily change the device resistance state, the resistance state cannot be long-termly stored. Based on the dark and light IV hysteresis curves, an applying bias of 5 V with an illumination intensity of 1000 μW cm−2 may induce the polarization inversion. Hence, we first preset the device to HRS and then apply 5 V continuous bias to the device, during which an UV light pulse with intensity of 1000 μW cm−2 and width of 1 s is illuminated on the device. The IT curve is shown in Fig. 4a. It is found that without illumination, the output current keeps low level, and once the device is illuminated, the output current first rises slowly and then suddenly increases near four orders of magnitude to 10−3 A. It takes about 0.27 s for the device to complete this change. Since the AlScN ferroelectric polarization can be partially reversed by a short electric rectangular pulse of 10 μs and −10 V, it can be speculated that the time for the AlScN ferroelectric polarization inversion only occupy a small portion of the total time for the resistance change of the device. Combining the IT curve, it can be deduced that most of the time is devoted to regulate the bias applied on the AlScN layer through the photoconductive effect and the φB variation. It is worth noting that the pulse light is provided by a LED driven by a pulse power supply, so the response speed of the LED and power supply may also affect the IT curve. When the light turns off, the output current still keeps 10−3 A, namely the device successfully stores the LRS.

a Time-resolved photoinduced polarization inversion process of the device at continuous voltage of 5 V and light pulse with width of 1 s and intensity of 1000 μW cm−2. b Opto-electrical programming process of the device. c Opto-electrical programming of the device for 100 cycles. During the programming, the write pulse light intensity and width are 1000 μW cm−2 and 1 s, and the read and reset voltages are 5 V and −10 V, respectively

Figure 4b shows the opto-electrical programming process of the device. During the process, the write pulse light intensity and width are 1000 μW cm−2 and 1 s, and the read and reset voltages are 5 V and −10 V, respectively. As is seen, the device can be effectively written and reset by the light pulse and the electric pulse, respectively, and the programming process is repeatable. Within 100 times of the write-read-reset-read process, the device exhibiting excellent repeatability, as shown in Fig. 4c, demonstrating the good opto-electrical nonvolatility and reconfigurability.

Table 1 compares the configuration, material, structure, memory mechanism and on/off ratio of some reported memristors in recent years. Currently, the memristors that can simultaneously be electrically and optically controlled are based on 2D or oxide semiconductors. Our device, based on III-nitrides, can realize the electro-optic duplex working mode and achieve an on/off ratio of 104 magnitude, which is relatively advanced. Moreover, different from the reported optically controlled ferroelectric memristors that require the interaction between the ferroelectric material itself and light to induce the polarization inversion, our device relies on the interaction between the other part of the structure and light to induce the ferroelectric part to generate polarization inversion, which provides a new direction for device structure design.

Thanks to the excellent nonvolatility and reconfigurability of our device at both electrical and opto-electrical modes, in-memory sensing and computing can be operated. Figure 5a schematically displays the realization of the in-memory IMP and False operation by two devices p and q and an external resistance s at electrical-electrical (E-E) (i), optical-electrical (O-E) (ii), and optical-optical (O-O) (iii) modes, respectively. It is worth noting that the conductivity of the resistance s needs to be at least one order of magnitude higher than that of the devices p and q at HRS and one order of magnitude lower than that of the devices p and q at LRS. The result is stored in the device q for all operations47,48. Figure 5b shows the forward IV hysteresis curves of the devices p and q in the dark and on illumination. Before the tests, both devices are reset by an electric rectangular pulse of −10 V, 1 s and the illumination light intensity is 1000 μW cm−2. The devices show similar optical and electrical properties to the above analyzed devices. Accordingly, the IMP operation biases Vcond and Vset can be set as 5.5 V and 7.0 V, the False operation bias Vreset can be set as −10 V, and the read bias can be set as 5.0 V, respectively.

Here, we take the O-E working mode for example, in which the devices p and q are optically and electrically controlled, respectively. The HRS and LRS represent the logic “0” and “1”. In this mode, a bias of 5.5 V needs to be applied to the device p. Hence, for the device p, the “light-off” and “light-on” represent the input of logic “0” and “1”, and for the device q, the “5.5 V write bias” and “7.0 V write bias” represent the input of logic “0” and “1”, respectively. If the devices p and q are written “0” and “0”, the device q will change to LRS after the IMP operation, obtaining the logic “1”. If the devices p and q are written “0” and “1”, the device q will keep LRS after the IMP operation, obtaining the logic “1”. If the devices p and q are written “1” and “0”, the device q will keep HRS after the IMP operation based on Ohm’s law and Kirchhoff’s law, obtaining the logic “0”. If the devices p and q are written “1” and “1”, the device q will keep LRS after the IMP operation, obtaining the logic “1”. Meanwhile, for all input conditions, the device q will change to HRS after the False operation. Figure 5c summaries all the inputs and outputs after the IMP and False operation based on the device connection types in Fig. 5a for all three working modes. The corresponding key working parameters are also listed. As is seen, the “IMP” truth table and the logic “False” are successfully reproduced. We know that IMP logic and False logic can form a complete logical set and all 16 logic operations can be realized through cascading. Since the basic IMP and False operations can be realized, more complex logic calculations can be completed.

Discussion

An electro-optic duplex memristor on a GaN/AlScN hetero-structure based Schottky diode has been realized. This two-terminal memristor shows good electrical and opto-electrical nonvolatility and reconfigurability. For both electrical and opto-electrical programming modes, the current on/off ratio can reach the magnitude of 104, and the resistance states can be effectively reset, written and long-termly stored. At electrical mode, the resistance state change originates from the ferroelectric polarization inversion of the AlScN layer in the hetero-structure, which influences the depletion region width and electron transport barrier height of the device. At opto-electrical mode, the memory window can be controlled by the illuminating light intensity due to the photoconductive effect of the i-GaN layer and the photo-generated carrier induced electron transport barrier reduction effect, which can regulate the partial bias applied to the AlScN layer. Based on this device, the “IMP” truth table and the logic “False” can be successfully reproduced, indicating the huge potential of our device in the field of in-memory sensing and computing.

Due to the demand surge of the in-memory sensing and computing, various types of memristors and photomemristors have been developed successively. Nonetheless, the device here still owns advantages over the reported devices. First, the device can realize pure-electrical and opto-electrical duplex working modes, and under both modes the device exhibits good programmable memory properties. Then, the device has a two-terminal configuration, which is of benefit to some large-scale integration applications. Next, taking advantage of the wide application range and high industrial maturity of III-nitrides, the device can move toward mass production and application more quickly. Finally, the device relies on the interaction between one part of the structure and the illuminating light to induce the other ferroelectric part to generate polarization inversion, providing a new device design conception of combining the photosensitive materials to ferroelectric materials.

However, we realize there is still room for improvement in this work. First, due to the sputtering growth method of the AlScN layer, polycrystalline ferroelectric domains are formed, affecting the large-scale uniformity and reliability. Second, the device can only realize the “0/1” binary calculation and storage, limiting its application range. We are now trying to solve the two problems. We believe the epitaxial technology for AlScN, such as the molecular beam epitaxy, can solve the polycrystalline ferroelectric domains problem. As for the multiple-state storage, in addition to realizing single crystal ferroelectric layer, to construct AlScN multiple hetero-structures may also take effect.

Materials and methods

Materials growth

The structure is grown on c-oriented sapphire substrate by MOCVD. During the growth, the TMGa and NH3 are used as the Ga and N precursors, the SiH4 is used as the n-doping sources, and the H2 is used as the carrier gas, respectively. First, the sapphire substrate is loaded to the growth chamber. Before the growth, the sapphire substrate is first thermally cleaned in a H2 and NH3 mixed gas atmosphere at 850 °C for 10 min to remove the surface contamination. Then, the temperature is increased to 900 °C to grow a GaN low-temperature nucleation layer of ~20 nm and further increased to 1080 °C to grow a GaN high-temperature buffer layer of ~1 μm. Next, an Si-doped n-type GaN contact layer of ~2 μm is grown to form an n-GaN/sapphire template. The electron concentration is ~2 × 1019 cm−3. After that, an unintentionally doped GaN layer (i-GaN) of ~300 nm is grown. Finally, the epi-wafer is unloaded from the MOCVD system and transferred to a RF-reactive magnetron sputtering system to grow an AlScN layer. A metal Al target and a metal Sc target are used as the Al and Sc sources, and the sputtering is in N2 atmosphere with the pressure of 0.7 Pa and temperature of 400 °C. The Al/Sc ratio is controlled by the target sputtering power. The AlScN layer is ~60 nm.

Device fabrication

The devices are made by standard III-nitrides semiconductor device fabrication process. First, an SiO2 mask is grown on the epi-wafer by a plasma enhanced chemical vapor deposition (PECVD) system at 300 °C. Then, the device mesa patterns are transferred to the SiO2 mask by lithography and reactive ion etching (RIE), sequentially. Then, the wafer is etched by an inductive coupling plasma (ICP) system to expose the n-GaN layer and the residual SiO2 mask is removed by the 10% buffered oxide etch (BOE) solution. Next, the electrode on n-GaN of Ti-20 nm/Al-80 nm/Ti-50 nm/Au-70 nm is deposited by e-beam evaporation and thermal evaporation. The n-electrode is annealed at 600 °C for 30 s in N2 to form better ohmic contact. Finally, the electrode on AlScN of Ni-20 nm/ Au-80 nm is deposited by e-beam evaporation and thermal evaporation, forming Schottky contact.

Characterizations and measurements

TEM-ready sample is prepared using the in situ focused ion beam (FIB) lift out technique on an FEI Dual Beam FIB/SEM. The sample is capped with sputtered C and e-Pt/I-Pt prior to milling. The TEM lamella is ~100 nm. The sample is imaged by an FEI Tecnai TF-20 FEG/TEM at 200 kV in bright-field (BF) STEM mode and HAADF-STEM mode. The STEM probe size is 1–2 nm in nominal diameter. EDS mappings are acquired on an Oxford INCA Bruker Quantax EDS system. The PFM images is measured by an Bruker Multimode 8 equipment. The PFM tip is applied with a bias of −10 V to scan a square region. At the center of the scanned region, a bias of +10 V is applied to scan a square region, causing different regions to undergo different polarization inversion process. A Bruck D8 discover HRXRD is employed to estimate the Al/Sc ratio and epilayer crystal quality. The IV and IT curves are recorded by a PDA FS-Pro 380 semiconductor analyzer. During the IV and IT measurements, the maximum current is limited to 10−3 A to protect the device. The UV light is provided by a commercial UV LED with a peak wavelength of 355 nm. The LED is driven by a DH1766 DC Power Supply.

References

Kyuma, K. et al. Artificial retinas—fast, versatile image processors. Nature 372, 197–198 (1994).

Funatsu, E. et al. An artificial retina chip with current-mode focal plane image processing functions. IEEE Trans. Electron Devices 44, 1777–1782 (1997).

Zhou, F. C. & Chai, Y. Near-sensor and in-sensor computing. Nat. Electron. 3, 664–671 (2020).

Jang, H. et al. In-sensor optoelectronic computing using electrostatically doped silicon. Nat. Electron. 5, 519–525 (2022).

Bai, B. et al. To image, or not to image: class-specific diffractive cameras with all-optical erasure of undesired objects. eLight 2, 14 (2022).

Luo, Y. et al. Computational imaging without a computer: seeing through random diffusers at the speed of light. eLight 2, 4 (2022).

Mennel, L. et al. Ultrafast machine vision with 2D material neural network image sensors. Nature 579, 62 (2020).

Cui, B. Y. et al. Ferroelectric photosensor network: an advanced hardware solution to real-time machine vision. Nat. Commun. 13, 1707 (2022).

Zhou, F. C. et al. Optoelectronic resistive random access memory for neuromorphic vision sensors. Nat. Nanotechnol. 14, 776 (2019).

Chen, J. et al. Polarized tunneling transistor for ultrafast memory. ACS Nano 17, 12374–12382 (2023).

Li, T. X. et al. Reconfigurable, non-volatile neuromorphic photovoltaics. Nat. Nanotechnol. 18, 1303–1310 (2023).

Long, X. et al. Ferroelectric electroresistance after a breakdown in epitaxial Hf0.5Zr0.5O2 tunnel junctions. ACS Appl. Electron. Mater. 5, 740–747 (2023).

Nath, S. K. et al. Harnessing metal/oxide interlayer to engineer the memristive response and oscillation dynamics of two-terminal memristors. Adv. Funct. Mater. 33, 2306428 (2023).

Hu, L. X. et al. All-optically controlled memristor for optoelectronic neuromorphic computing. Adv. Funct. Mater. 31, 2005582 (2021).

Zhu, L. Q. et al. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 5, 3158 (2014).

Yang, J. Q. et al. A Perovskite memristor with large dynamic space for analog-encoded image recognition. ACS Nano 16, 21324–21333 (2022).

Wang, L. et al. Exploring ferroelectric switching in α-In2Se3 for neuromorphic computing. Adv. Funct. Mater. 30, 2004609 (2020).

Xue, F. et al. Optoelectronic ferroelectric domain-wall memories made from a single van der Waals ferroelectric. Adv. Funct. Mater. 30, 2004206 (2020).

Li, X. et al. Multi-functional platform for in-memory computing and sensing based on 2D ferroelectric semiconductor α-In2Se3. Adv. Funct. Mater. 34, 2306486 (2024).

Yang, J. Y. et al. Reconfigurable radio-frequency high-electron mobility transistors via ferroelectric-based gallium nitride heterostructure. Adv. Electron. Mater. 8, 2101406 (2022).

Mukherjee, S. et al. Graphene-In2Se3 van der Waals heterojunction neuristor for optical in-memory bimodal operation. ACS Nano 17, 22287–22298 (2023).

Tsai, S. L. et al. Room-temperature deposition of a poling-free ferroelectric AlScN film by reactive sputtering. Appl. Phys. Lett. 118, 082902 (2021).

Wang, P. et al. Fully epitaxial ferroelectric ScAlN grown by molecular beam epitaxy. Appl. Phys. Lett. 118, 223504 (2021).

Schönweger, G. et al. In-grain ferroelectric switching in Sub-5 nm thin Al0.74Sc0.26N films at 1 V. Adv. Sci. 10, 2302296 (2023).

Guido, R. et al. Role of defects in the breakdown phenomenon of Al1-xScxN: from ferroelectric to filamentary resistive switching. Nano Lett. 23, 7213–7220 (2023).

Fu, H. L., Goodrich, J. C. & Tansu, N. Band alignment of ScAlN/GaN heterojunction. Appl. Phys. Lett. 117, 231105 (2020).

Fichtner, S. et al. AlScN: a III-V semiconductor based ferroelectric. J. Appl. Phys. 125, 114103 (2019).

Wang, D. et al. Ultrathin nitride ferroic memory with large ON/OFF ratios for analog in-memory computing. Adv. Mater. 35, 2210628 (2023).

Kim, K. H. et al. Scalable CMOS back-end-of-line-compatible AlScN/two-dimensional channel ferroelectric field-effect transistors. Nat. Nanotechnol. 18, 1044 (2023).

Ma, T. P. & Han, J. P. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron Device Lett. 23, 386–388 (2002).

Wang, D. et al. An epitaxial ferroelectric ScAlN/GaN heterostructure memory. Adv. Electron. Mater. 8, 2200005 (2022).

Mondal, S. et al. Reconfigurable self-powered deep UV photodetectors based on ultrawide bandgap ferroelectric ScAlN. APL Mater. 10, 121101 (2022).

Xu, K. et al. Optical control of ferroelectric switching and multifunctional devices based on van der Waals ferroelectric semiconductors. Nanoscale 12, 23488–23496 (2020).

Jiang, K. et al. Quantum engineering of non-equilibrium efficient p-doping in ultra-wide band-gap nitrides. Light Sci. Appl. 10, 69 (2021).

Guo, L. et al. Multiple-quantum-well-induced unipolar carrier transport multiplication in AlGaN solar-blind ultraviolet photodiode. Photonics Res. 9, 1907–1915 (2021).

Jiang, K. et al. Polarization-enhanced AlGaN solar-blind ultraviolet detectors. Photonics Res. 8, 1243–1252 (2020).

Zhang, L. D. et al. Demonstration of weak polarization electric field III-N LEDs based on polar plane. Laser Photonics Rev. 17, 2300400 (2023).

Chen, M. H. et al. GaN ultraviolet laser based on bound states in the continuum (BIC). Adv. Opt. Mater. 11, 2201906 (2023).

Liu, X. W. et al. Post-CMOS compatible aluminum scandium nitride/2D channel ferroelectric field-effect-transistor memory. Nano Lett. 21, 3753–3761 (2021).

Urban, D. F., Ambacher, O. & Elsässer, C. First-principles calculation of electroacoustic properties of wurtzite (Al,Sc)N. Phys. Rev. B 103, 115204 (2021).

Ambacher, O. et al. Wurtzite ScAlN, InAlN, and GaAlN crystals, a comparison of structural, elastic, dielectric, and piezoelectric properties. J. Appl. Phys. 130, 045102 (2021).

Yang, J. Y. et al. Reconfigurable physical reservoir in GaN/α-In2Se3 HEMTs enabled by out-of-plane local polarization of ferroelectric 2D layer. ACS Nano 17, 7695–7704 (2023).

Chen, J. et al. Highly sensitive and tunable self-powered UV photodetectors driven jointly by p-n junction and ferroelectric polarization. ACS Appl. Mater. Interfaces 12, 53957–53965 (2020).

Park, I. H. et al. Self-powered photodetector using two-dimensional ferroelectric Dion-Jacobson hybrid perovskites. J. Am. Chem. Soc. 142, 18592–18598 (2020).

Cao, F. R. et al. Polarized ferroelectric field-enhanced self-powered perovskite photodetector. ACS Photonics 5, 3731–3738 (2018).

Chen, J. et al. High-performance self-powered ultraviolet photodetector based on coupled ferroelectric depolarization field and heterojunction built-in potential. Adv. Electron. Mater. 7, 2100717 (2021).

Borghetti, J. et al. Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Fu, X. et al. Graphene/MoS2-xOx/graphene photomemristor with tunable non-volatile responsivities for neuromorphic vision processing. Light Sci. Appl. 12, 39 (2023).

Acknowledgements

This work is supported by the National Key R&D Program of China [2022YFB3605600]; National Natural Science Foundation of China [62121005, U22A2084]; Youth Innovation Promotion Association of CAS [2023223]; Natural Science Foundation of Jilin Province [20230101345JC, 20230101360JC, SKL202302026]; Young Elite Scientist Sponsorship Program by CAST [YESS20200182].

Author information

Authors and Affiliations

Contributions

Z.W.X. and K.J. designed the structures, fabricated the devices, measured the electrical and optical properties, analyzed the results and wrote the manuscript. S.L.Z. and J.W.B. helped to grow the GaN material, discussed the results. M.R.L. and S.P.L. helped to grow the AlScN materials, discussed the results. Y.C. and Y.P.J. helped to analyze the results. X.J.S. and D.B.L. proposed the idea, directed the materials growth, device fabrication, characterization, result analyses, manuscript writing and finally amended the manuscript.

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Xie, Z., Jiang, K., Zhang, S. et al. Nonvolatile and reconfigurable two-terminal electro-optic duplex memristor based on III-nitride semiconductors. Light Sci Appl 13, 78 (2024). https://doi.org/10.1038/s41377-024-01422-4

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41377-024-01422-4