Abstract

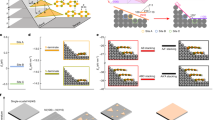

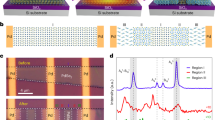

Silicon transistors are expected to have new gate architectures, channel materials and switching mechanisms in ten years’ time1,2,3,4. The trend in transistor scaling has already led to a change in gate structure from two dimensions to three, used in fin field-effect transistors, to avoid problems inherent in miniaturization such as high off-state leakage current and the short-channel effect. At present, planar and fin architectures using III–V materials, specifically InGaAs, are being explored as alternative fast channels on silicon5,6,7,8,9 because of their high electron mobility and high-quality interface with gate dielectrics10. The idea of surrounding-gate transistors11, in which the gate is wrapped around a nanowire channel to provide the best possible electrostatic gate control, using InGaAs channels on silicon, however, has been less well investigated12,13 because of difficulties in integrating free-standing InGaAs nanostructures on silicon. Here we report the position-controlled growth of vertical InGaAs nanowires on silicon without any buffering technique and demonstrate surrounding-gate transistors using InGaAs nanowires and InGaAs/InP/InAlAs/InGaAs core–multishell nanowires as channels. Surrounding-gate transistors using core–multishell nanowire channels with a six-sided, high-electron-mobility transistor structure greatly enhance the on-state current and transconductance while keeping good gate controllability. These devices provide a route to making vertically oriented transistors for the next generation of field-effect transistors and may be useful as building blocks for wireless networks on silicon platforms.

This is a preview of subscription content, access via your institution

Access options

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Ferain, I., Colinge, A. A. & Colinge, J.-P. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479, 310–316 (2011)

del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011)

Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010)

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011)

Radosavljevic, M. et al. Advanced high-k gate dielectric for high-performance short-channel In0.7Ga0.3As quantum well field effect transistors on silicon substrate for low power logic applications. IEDM Tech. Dig. 319–322 (2009)

Kim, S. H. et al. Electron mobility enhancement of extremely thin body In0. 7Ga0. 3As-on-insulator metal-oxide-semiconductor field-effect transistors on Si substrates by metal-oxide-semiconductor interface buffer layer. Appl. Phys. Exp. 5, 014201 (2012)

Wu, Y. Q. et al. 0.8-V supply voltage deep-submicrometer inversion-mode In0. 75Ga0. 25As MOSFET. IEEE Elec. Dev. Lett. 30, 700–702 (2009)

Radosavljevic, M. et al. Non-planar, multi-gate InGaAs quantum well field effect transistors with high-k gate dielectric and ultra-scaled gate-to-drain/gate-to-source separation for low power logic applications. IEDM Tech Dig. 126–129. (2010)

Radosavljevic, M. et al. Electrostatic improvement in 3-D tri-gate over ultra-thin body planar InGaAs quantum well field effect transistors with high-k gate dielectric and scaled gate-to-drain/gate-to-source separation. IEDM Tech. Dig. 765–768. (2011)

Wieder, H. H. Surface and interface barriers of In x Ga1−x As binary and ternary alloys. J. Vac. Sci. Technol. B 21, 1915–1919 (2003)

Takato, H. et al. Impact of surrounding gate transistor (SGT) for ultra-high-density LSI’s. IEEE Trans. Electron. Dev. 38, 573–578 (1991)

Gu, J. J. et al. First experimental demonstration of gate-all-around III–V MOSFETs by top-down approach. IEDM Tech. Dig. 769–772. (2011)

Tomioka, K., Yoshimura, M. & Fukui, T. Vertical In0. 7Ga0. 3As nanowire surrounding-gate transistors with high-k gate dielectrics on Si substrate. IEDM Tech. Dig. 773–776. (2011)

Xuan, Y. et al. Submicrometer inversion-type enhancement-mode InGaAs MOSFET with atomic-layer-deposited Al2O3 as gate dielectric. IEEE Elec. Dev. Lett 28, 935–938 (2007)

Ishii, H. et al. High electron mobility metal-insulator-semiconductor field-effect transistors fabricated on (111)-oriented InGaAs channels. Appl. Phys. Exp. 2, 121101 (2009)

Kim, D.-H. et al. 50-nm E-mode In0. 7Ga0. 3As PHEMTs on 100-nm InP substrate with f max > 1 THz. IEDM Tech. Dig. 692–695. (2010)

Furukawa, Y. et al. Control of N content of GaPN grown by molecular beam epitaxy and growth of GaPN lattice matched on Si(100) substrate. Jpn. J. Appl. Phys. 41, 528–532 (2002)

Tomioka, K., Motohisa, J., Hara, S. & Fukui, T. Control of InAs nanowire growth directions on Si. Nano Lett. 8, 3475–3480 (2008)

Tomioka, K. et al. Selective-area growth of vertically aligned GaAs and GaAs/AlGaAs core-shell nanowires on Si(111) substrate. Nanotechnology 20, 145302 (2009)

Noborisaka, J. et al. Electrical characterization of InGaAs nanowire-top-gate field-effect transistors by selective-area metal organic vapor phase epitaxy. Jpn. J. Appl. Phys. 46, 7562–7568 (2007)

Rehnstedt, C. et al. Vertical InAs nanowire wrap gate transistors on Si substrate. IEEE Trans. Electron. Dev. 55, 3037–3041 (2008)

Tanaka, T. et al. Vertical surrounding gate transistors using single InAs nanowires grown on Si substrates. Appl. Phys. Exp. 3, 025003 (2010)

Wernersson, L.-E., Thelander, C., Lind, E. & Samuelson, L. III–V nanowires—extending a narrowing road. Proc. IEEE 98, 2047–2060 (2010)

Ghalamestani, S. G. et al. Uniform and position controlled InAs nanowires on 2′′ Si substrate for transistor applications. Nanotechnology 23, 015302 (2012)

Mimura, T., Hiyamizu, S., Fujii, T. & Nanbu, K. A new field-effect transistor with selectively doped GaAs/n-Al x Ga1−x As heterojunctions. Jpn. J. Appl. Phys. 19, L225–L227 (1980)

Tan, I.-H., Snider, G. L., Chang, L. D. & Hu, E. L. A self-consistent solution of Schrodinger-Poisson equations using nonuniform mesh. J. Appl. Phys. 68, 4071–4076 (1990)

Takagi, S., Toriumi, A., Iwase, M. & Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: part I—effects of substrate impurity concentration. IEEE Trans. Electron. Dev. 41, 2357–2362 (1994)

ITRS. International Technology Roadmap for Semiconductorshttp://www.itrs.net/Links/2011ITRS/Home2011.htm (ITRS, 2011)

Galindo, P. L. et al. The peak pairs algorithm for strain mapping from HRTEM images. Ultramicroscopy 107, 1186–1193 (2007)

Acknowledgements

We thank J. Motohisa, S. Hara, K. Hiruma, T. Hashizume and T. Waho for discussions. We especially thank Y. Hori for instructing us on the current–voltage measurement. This work was financially supported by a Grant-in-Aid for Scientific Research from MEXT and the Japan Science and Technology Agency – PRESTO programme.

Author information

Authors and Affiliations

Contributions

K.T. designed the experiments, made the nanowires by metal–organic vapour phase epitaxy, fabricated the device and analysed all of the data. T.F. planned and supervised the study. M.Y. helped in the epitaxy experiments. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Supplementary information

Supplementary Information

This file contains Supplementary Text and Data and Supplementary Figures 1-8. (PDF 1235 kb)

Rights and permissions

About this article

Cite this article

Tomioka, K., Yoshimura, M. & Fukui, T. A III–V nanowire channel on silicon for high-performance vertical transistors. Nature 488, 189–192 (2012). https://doi.org/10.1038/nature11293

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/nature11293

This article is cited by

-

Controlled formation of three-dimensional cavities during lateral epitaxial growth

Nature Communications (2024)

-

Cryogenic multiplexing using selective area grown nanowires

Nature Communications (2023)

-

Waveguide coupled III-V photodiodes monolithically integrated on Si

Nature Communications (2022)

-

Creation of unexplored tunnel junction by heterogeneous integration of InGaAs nanowires on germanium

Scientific Reports (2022)

-

Observation of polarity-switchable photoconductivity in III-nitride/MoSx core-shell nanowires

Light: Science & Applications (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.