Abstract

Strain engineering has been utilized to overcome the limitation of geometric scaling in Si-based thin-film transistor (TFT) technology by significantly improving carrier mobility. However, current strain engineering methods have several drawbacks: they generate atomic defects in the interface between Si and strain inducers, they involve high-cost epitaxial depositions and they are difficult to apply to flexible electronics with plastic substrates. Here, we report the formation of a strained Si membrane with oxidation-induced residual strain by releasing a host Si substrate of a silicon-on-insulator (SOI) wafer. The construction of the suspended Si/SiO2 structures induces >0.5% tensile strain on the top Si membrane. The fabricated TFTs with strained Si channels are transferred onto plastics using a roll-based transfer technique, and they exhibit a mobility enhancement factor of 1.2–1.4 compared with an unstrained Si TFT.

Similar content being viewed by others

Introduction

A critical path in the development of advanced silicon electronics involves a reduction in the dimensions of device geometries such as the channel thickness, channel length and gate dielectric thickness to increase the operating speed with lower power consumption and the density of integration in circuits.1, 2, 3, 4 Continued performance improvement through geometric scaling has faced increasingly difficult challenges.5, 6 Recent research focused on this issue has explored strain engineering that can increase the charge carrier mobility by creating tensile strain in Si with a capping stressor film,7 local stressors under channel8 or embedded source/drain stressors.9, 10 In particular, the introduction of an Si1−xGex buffer layer with a large lattice constant represented by an epitaxial template can successfully generate biaxial tensile strain in Si.11, 12 The Si1−xGex virtual buffer layer allows the fabrication of wafer-scale strained Si membranes13, 14 and approximate doubling of the mobility enhancement factors of electrons in Si layers for fast, flexible electronic device applications.15, 16, 17 However, the process for introducing the Si1−xGex buffer leads to undesirable misfit dislocations and interdiffusion of Ge in the Si/SiGe interface and requires uniform growth of the Si1−xGex layer with precisely controlled composition of Si and Ge, which is challenging.18, 19, 20, 21

Here, we present a new strain engineering approach to induce a biaxial tensile strain to the active Si device layer without using an additional epitaxial stressor layer. In this approach, the tensile strain in Si is naturally created in the process of etching and physical transfer for building flexible Si devices with high performance on plastic substrates. A strained Si nanomembrane is fabricated by releasing the bilayer of Si and SiO2 from the host Si layer of a silicon-on-insulator (SOI) wafer. The oxidation-induced compressive strain in the SiO2 layer of the SOI wafer is activated by forming a suspended structure via the etching of the host Si that leads to planar expansion of the Si/SiO2 bilayer and resultantly induces biaxial tensile strain in the top Si layer. The extent of strain sharing depends on the relative thicknesses of the two layers. The transfer step is inevitably required for the proposed Si devices that well fits this approach to flexible electronics. After transferring the strained Si membrane to the plastic substrate, the fabricated Si devices exhibited a 20–40% greater charge carrier mobility. The strained Si membrane can benefit from the well-established SOI electronics and offers an important advantage over the conventional method that uses a Si1−xGex stressor layer.

Experimental procedure

Fabrication of strained Si transistors

The schematic illustrations of whole fabrication steps for strained Si thin-film transistors (TFTs) are displayed in Supplementary Figure S1. SOI wafer was used to fabricate the Si TFTs. The SOI wafer was composed of 0.43–1.5 μm top Si, 1 μm SiO2 and bulk Si. A top Si layer of SOI wafer was n+ doped to form ohmic contacts with the source and drain electrodes of the TFTs by implantation with phosphorus (dose=5 × 1015 cm−2, energy=15 KeV). Si layers outside the device parts were etched using SF6 plasma by reactive-ion etching to prohibit the interference of currents flowing into each device. A SiO2 dielectric layer (70 nm) was grown by a thermal oxidation process at 900 °C for 39 min. An opening process was performed to make a via hole between the sources and drains of the Si and electrodes by wet etching of SiO2. Cr/Au layers with thicknesses of 5 and 95 nm, respectively, were deposited by thermal evaporation and defined as source/drain and gate electrodes by photolithography.

Roll-based transfer processes

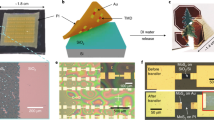

Patterns of ribbons with a length of 610 μm and a width of 160 μm were formed using AZ33XT (10 μm) followed by a hard baking process at 115 °C for 3 min. A lateral dry etching process using an inductively coupled plasma reactive-ion etcher (SF6, 130 sccm, 50 mTorr, 35 min) was carried out to remove the bulk Si underneath the buried oxide (BOX) layer to form suspended device ribbons. A roll transfer process was then used to carry out the reliable transfer of suspended device ribbons with precise control of the transfer load. Roll transfer equipment generally consists of a roller, a load cell, a z-axis actuator and a transfer plate as shown in Supplementary Figure S2. The inset shows the schematic illustration of the roll transfer system. The roller is parallel to the transfer plate, and its vertical motion is controlled by two z-axis actuators. The exact load applied to the devices is accurately measured by the load cell and is controlled by the input system connected to the actuators. The transfer processes are mainly divided into two steps: picking step and placing step. In the picking step, large-area suspended device arrays held onto the transfer plate by vacuum were placed in contact with the roller that was covered by a polydimethylsiloxane film with an optimized contact load. Suspended device arrays were detached from the wafer and attached to polydimethylsiloxane by van der Waals adhesion force. In this procedure, the angular displacement of the roller was synchronized with the in-plane displacement of the transfer plate to prohibit device arrays from being misaligned by shear stress. In the placing step, the target substrate should be held onto the second transfer plate. Contact between device arrays attached to the roller and a target substrate was made with the optimized load. Adhesives such as NOA 63 (Norland Products Inc., Cranbury, NJ, USA) and SU-8 2005 (Microchem Corp., Newton, MA, USA) were coated on the surface of the target substrate to facilitate a larger adhesion force between the devices and the target substrate than that between the devices and the roller. Through the rolling steps with the synchronized motion of the roller and the plate at 90 °C, picked devices were transferred onto a target substrate. The resultant devices realized by the roll-based transfer technique are shown in Supplementary Figure S3. Large-area device arrays including ∼3000 devices in 4 × 4 cm scale were transferred onto plastics with robust operation.

Results and discussion

Figure 1a illustrates the application of self-sustained biaxial tensile strain to Si/SiO2 ribbon arrays suspended on a wafer by releasing residual compressive stress confined in SiO2. An SOI wafer with a top Si (100) layer of various thicknesses on a BOX layer was used to fabricate strained Si ribbons. A large volume expansion accompanies the oxidation process of Si to form the BOX layer because the molar volume of SiO2 is larger than that of Si. However, the volumetric expansion of SiO2 is constrained because it is bonded to the underlying Si handle wafer, and hence a high residual compressive stress of 0.2–6 GPa is biaxially developed in the BOX layer.22, 23, 24, 25, 26 Etching out of the underlying handle Si leads to a biaxial expansion of the BOX and, as a result, creates biaxial tensile strain in the top Si ribbon that is tightly bonded to the BOX. The tensile strain in the Si is determined by equilibrating the force between the Si and the SiO2. The suspended ribbons are anchored on both edges, and hence the biaxial tensile stress in the ribbons generally generates a boat shape because of buckling (Figure 1b).27, 28 The extent and distribution of strain can be evaluated by analyzing the degree of buckling and the deformed shape.29

(a) A schematic of the processes used to apply tensile strain to a Si ribbon. (b) A scanning electron microscope (SEM) image of suspended Si/SiO2 ribbons after removing bulk Si. Visualized height profiles of the suspended Si/SiO2 ribbon (c) measured by white light interferometer (left) and (d) simulated by finite element method (FEM; right). (e) Height profiles of the center part of suspended Si/SiO2 ribbons along the longitudinal direction. The black solid curve is for the measured height profile by white light interferometry, and the red solid curve is for the simulated one by finite element analysis (FEA), respectively. BOX, buried oxide; PET, polyethylene terephthalate; SOI, silicon-on-insulator.

Figure 1c presents the result of a three-dimensional height profile of the suspended Si/SiO2 ribbon measured by white light interferometry. The deformation of the ribbon was evaluated by measuring the change of transverse and longitudinal length in the Si and SiO2 regions. Based on the dimensions of the suspended ribbon (Supplementary Figure S4), the residual stress in the BOX layer and the average tensile strain applied to the suspended Si layer were estimated to be 854 MPa and 0.318%, respectively (Supplementary Note S1). To confirm these results, finite element analysis was carried out on a model of the suspended Si/SiO2 ribbon under the same conditions (Supplementary Note S2); the simulated three-dimensional profile of the suspended ribbon (Figure 1d) was analogous to the measured one. The distance between the center and the edge of the ribbon along the longitudinal direction was 23.89 μm in the simulated profile and 26.05 μm in the measured ribbon (Figure 1e).

Figure 2a presents finite element analysis results of the distribution of in-plane principal strain on a suspended Si/SiO2 ribbon. The contour map of strain shows that a tensile strain of ∼0.310% is uniformly applied to the whole area of the table-shaped Si on SiO2. This measurement agrees with the result of the height profile measurement (0.318%). The distribution of strain along the x and y axes of a ribbon are displayed in Figures 2b and c, respectively, showing different average values of tensile strain (ɛx, avg=0.207%, ɛy, avg=0.271%) with a nonuniform distribution. This is because the ribbon is longitudinally and asymmetrically linked to the anchors and constrained by the rigid edges while being transversely free without any constraint (Supplementary Figure S5).

Raman spectroscopy was used to measure the distribution of the induced strain in a suspended Si ribbon, and the results were compared with the results above. The strain in the Si was directly calculated by observing the shift of a strong Raman peak near 520 cm−1.30, 31 Figure 3a presents the contour mapping image of Raman shift for unstrained Si on an unetched region and a strained, suspended Si ribbon that displays a clearly distinguished, uniform strain distribution on two regions. Raman peaks of unstrained Si and strained Si were observed at 520.46 and 517.98 cm−1, respectively. This image shows good agreement with the simulated one shown in Figure 2a. Figure 3b shows Raman spectra that illustrate the change in strain at different conditions: bulk, anchored, suspended and transferred Si. Raman peaks of bulk and anchored Si appeared at 520.46 cm−1, and peaks of suspended and transferred Si ribbons were observed at 517.98 and 518.22 cm−1, respectively. Based on the Raman peak of unstrained Si (520.46 cm−1), those of the suspended and transferred ribbons were downshifted (Δω) by 2.48 and 2.24 cm−1 with a tensile strain (ɛSi) of 0.316 and 0.286%, respectively, given by31

(a) A contour map of Raman peaks in a suspended Si ribbon. (b) Raman spectra of bulk Si (black), Si anchor (red), suspended Si (blue) and transferred Si (green). (c) Raman spectra of suspended Si ribbons with various thicknesses ranging from 0.43 to 1.5 μm. (d) Calculated and measured strain levels according to the thickness of the top Si layer in a suspended Si/SiO2 ribbon.

In Equation (1), b is the strain shift coefficient of the Si–Si phonon mode on strained Si, −784±4 cm−1. Although uniform tensile strain was distributed in the transferred ribbon (Supplementary Figure S6), a slight decrease in the strain value of the Si ribbon may be created during the transfer to a polyethylene terephthalate (PET) substrate.32 When an Si/SiO2 ribbon is transferred to the PET substrate, it is heated to ∼100 °C to cure the polymer adhesive and improve the bonding strength between the ribbon and the substrate. A cooling process after heating can induce a slight compressive strain on the ribbon because of the higher thermal expansion coefficient (α) of the PET substrate (αPET=5.9 × 10−5 K−1) than that of Si/SiO2 (αSi=2.6 × 10−6 K−1, α = 0.35 × 10−6K−1). However, we observed that transferred ribbons maintained their original state without detectable deformation in Raman shift for 28 days (Supplementary Figure S7).

The tensile strain applied to the Si layer is controllable by adjusting the stiffness ratio of Si and SiO2 because the residual strain from the bottom SiO2 layer is more effectively transferred to the thinner Si layer. To assess the effects of the thickness ratio, Si/SiO2 ribbons with different Si thicknesses (0.43–1.5 μm) and a constant thickness of SiO2 (∼1 μm) were transferred to a foreign substrate, and the induced tensile strain was measured by Raman spectroscopy (Figure 3c). The specific Raman peak of unstrained, bulk Si at 520.46 cm−1 showed larger downshifts as Si thickness decreased from 2.17 cm−1 for 1.5 μm-thick Si (ɛSi=0.277%) to 4.70 cm−1 for 0.43 μm-thick Si (ɛSi=0.568%; Figure 3d). The measured strain values are in good agreement with those obtained from finite element analysis (Supplementary Note S3). Ultimately, the strain level can be achieved up to 1% as predicted by the calculation.

A primary purpose for applying tensile strain in Si is to improve its electronic properties; the strain reduces carrier scattering and the effective transport mass of electrons.33, 34 The roll-based transfer approach of a strained Si layer can effectively provide important benefits to the development of high-performance strained Si TFTs for large-area flexible electronic applications.15, 16, 17, 35 Figure 4a shows the key fabrication steps for a strained Si TFT array on a flexible PET film using an automated roll transfer method. All device processes, including doping, oxidation and metallization, were performed on SOI wafers with different top Si thicknesses of 0.43–1.5 μm through a similar method to the conventional process.36, 37 After measuring the pristine characteristics of the device on a wafer, the device array (∼3000 transistors on a 4 × 4 cm area) was printed on a PET substrate after undergoing the etching and roll transfer processes (Supplementary Figures S2 and S3). As seen in the magnified image, the surface of a strained Si TFT transferred onto a PET substrate looks smooth and clean because the distortion induced by the anchors was relieved by the sliding on the polydimethylsiloxane stamp (Supplementary Figure S8). In addition, no cracks were observed in the transferred devices, particularly on the SiO2 layer. Thus, it is determined that the thin SiO2 in the device is stable under the strain level of 0.5% because it forms a good interface with the Si through strong covalent bonds.

(a) Schematics of the steps to fabricate the strained Si thin-film transistors (TFTs) onto a polyethylene terephthalate (PET) substrate including suspending steps of devices by undercut etching and transfer steps using roll-based transfer printing. (b) An illustration of the cross-sectional view of the strained Si TFT on the PET substrate. PDMS, polydimethylsiloxane.

In contrast to the Si/SiO2 ribbon, the induced strain of the Si channel in the TFT can be affected by additional layers, such as a dielectric layer, and electrodes that are required to produce a top-gated TFT structure (Figure 4b). The top SiO2 dielectric layer (∼70 nm) grown thermally on Si can induce strain on the Si, as with the bottom SiO2, and also increase the applied strain on the Si by reducing the overall Si thickness. In contrast, a metal electrode (∼100 nm) deposited on the SiO2/Si can attenuate the straining effect of the top SiO2 layer on the Si layer. It was calculated that the top-gated structures induce a slight increase in tensile strain applied to the Si layer compared with pristine Si/SiO2 ribbons (from 0.277 to 0.292% for 1.5 μm-thick Si and from 0.568 to 0.584% for 0.43 μm-thick Si). These values indicate that the effect of the two additional layers is not great (Supplementary Note S4).

The strained Si devices transferred onto PET displayed significant improvement in device characteristics as shown in Figure 5. The drain current (Id), compared with that of the unstrained device on a rigid wafer, increased by 16.8% for 1.5 μm-thick Si. Id then gradually increased with decreasing thickness of the Si, and for 0.43 μm-thick Si, Id was 30.5% greater than that of the unstrained rigid wafer (Figure 5a). The on/off ratio (>105) was unaffected by the Si thickness. Id−Vg characteristics also exhibited clear increases in drain currents in both linear and saturation regions, indicating the effects of strong strain in thin Si devices (Figure 5b). The average effective mobility, μFE, of unstrained Si TFTs on a wafer before the transfer was calculated as 440.2±84.9 cm2 V−1 s−1 (Supplementary Figures S9 and S10 and Supplementary Note S5). The mobility of the strained Si devices on PET substrates increased from 520.7±77.3 to 604.1±87.4 cm2 V−1 s−1 with decreasing thickness of the Si (Figure 5c and Supplementary Figure S11). The mobility of strained Si TFTs improved by 20–40% over unstrained Si TFTs owing to the tensile strain of 0.292–0.584% without a serious increase in the gate leakage current (Supplementary Figure S12). The degree of this enhancement agrees well with the theoretical calculation based on the electronic properties of biaxially strained silicon (Figure 5d and Supplementary Note S6).34 The performance of strained Si TFT would be saturated at 40% with a higher level of tensile strain.40

(a) Transfer characteristics of the Si thin-film transistor (TFT) on a wafer and strained Si TFT with various Si thicknesses (0.43–1.5 μm) on a polyethylene terephthalate (PET) substrate on a linear scale (line, left y axis) and a log scale (dash, right y axis) for a channel width of 100 μm and length of 10 μm at a drain voltage of 0.1 V. (b) Output characteristics of the Si TFT on a wafer and strained Si TFT with various Si thicknesses (0.43–1.5 μm) on a PET substrate at gate voltages from 0 V (bottom) to 4 V (top). (c) Mobility enhancement of strained Si TFTs with various Si thicknesses (0.43–1.5 μm) compared with unstrained Si TFTs. (d) Normalized change of mobility of strained Si TFTs with various Si thicknesses (0.43–1.5 μm). The red dot curve indicates the calculated results.

In addition, the enhanced mobility and threshold voltages exhibit a similar tendency as the channel length increased from 10 to 30 μm (Supplementary Figures S13−S15). We measured the device performance for 28 days to confirm the stability of strained Si devices after transferring them to a plastic substrate. The strained Si TFTs exhibited stable operation and no strain relaxation under general environmental conditions for the entire duration of the experiment (Supplementary Figure S16) because the residual strain in the Si devices was induced by the underlying SiO2 layer rather than the PET substrate that has time-dependent relaxation.38

Figure 6a shows the transfer characteristics of Si TFTs with 1.5 μm thickness on PET substrates under various strains. Uniaxial strains between −0.4 and 0.4% were applied by bending the flexible substrates along the channel direction. Drain currents in the on-state gradually increased with increasing bending strain. This mechanically applied uniaxial strain induced an additional reduction in the effective mass and charge scattering of electrons along the channel direction.39, 40 As expected, a tensile bending strain of 0.4% led to a 21% increase in mobility (from 537.57 to 652.1 cm2 V−1 s−1). In contrast, a compressive strain of 0.4% led to a 10% decrease in mobility because of an opposite influence on the Si channel. This change in mobility against the external strain shows that the TFTs were operating in a stable manner. Even after the repeated bending test to a tensile strain of 0.4%, during which the TFT was bent 2000 times, the strained Si devices were unscathed without failure (Figure 6b). Thus, these devices demonstrate reliable operation under repeated bending.

Uniaxial strain effects on electrical properties of strained Si thin-film transistors (TFTs) under bending. (a) Transfer characteristics of strained Si TFTs with a 1.5-μm-thick top Si layer under various bending strains. (b) The change in carrier mobility of strained Si TFTs under bending strain and after cycling tests.

Conclusion

Biaxial tensile strain was residually generated in the Si layer of a Si/SiO2 structure by utilizing the oxidation-induced volumetric strain of the BOX layer in SOI wafers. The induced strain was analyzed by measuring the mechanically stretched configuration of the suspended Si/SiO2 ribbons by Raman spectroscopy and white light interferometry and confirmed by finite element analysis. The tensile strain in transferred Si TFTs was induced from 0.292 to 0.584%, depending on the thickness ratio of the bilayer of Si and SiO2. Because the biaxial tensile strain applied to the Si channel reduced the intervalley scattering and effective mass of electrons, the suspended and transferred Si TFTs showed a 19–40% increase in carrier mobility as compared with the unstrained devices on a bulk wafer. Furthermore, realization of large-area, strained Si device arrays (4 cm × 4 cm) were demonstrated by a roll-based transfer onto a plastic substrate.

In conclusion, improved electrical performance was demonstrated in thin Si TFTs on a flexible substrate by strain engineering without relying on the epitaxial stressor, and this process is compatible with the roll-based transfer methods with high productivity. This approach shows promise for strain-engineered large-area flexible electronics with high performance and productivity.

References

Yu, B., Chang, L., Ahmed, S., Wang, H., Bell, S., Yang, C.-Y., Tabery, C., Ho, C., Xiang, Q., King, T.-J., Bokor, J., Hu, C., Lin, M.-R. & Kyser, D. FinFET scaling to 10 nm gate length. Tech. Dig. Int. Electron Devices Meet. 251–254 (2002).

Ieong, M., Doris, B., Kedzierski, J., Rim, K. & Yang, M. Silicon device scaling to the sub-10-nm regime. Science 306, 2057–2060 (2004).

Green, M. L., Gusev, E. P., Degraeve, R. & Garfunkel, E. L. Ultrathin (SiO2 and Si-O-N gate dielectric layers for silicon microelectronics: understanding the processing, structure, and physical and electrical limits. J. Appl. Phys. 90, 2057–2121 (2001).

Robertson, J. High dielectric constant gate oxides for metal oxide Si transistors. Rep. Prog. Phys. 69, 327–396 (2006).

Frank, D. J., Dennard, R. H., Nowak, E., Solomon, P. M., Taur, Y. & Wong, H.-S. P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89, 259–288 (2001).

Meindl, J. D., Chen, Q. & Davis, J. A. Limits on silicon nanoelectronics for terascale integration. Science 293, 2044–2049 (2001).

Ito, S. Mechanical stress effect of etch-stop nitride and its impact on deep submicron transistor design. Tech. Dig. Int. Electron Devices Meet. 247–250 (2000).

Nanver, L. K., Jovanović, V., Biasotto, C., Moers, J., Grützmacher, D., Zhang, J. J., Hrauda, N., Stoffel, M., Pezzoli, F., Schmidt, O. G., Miglio, L., Kosina, H., Marzegalli, A., Vastola, G., Mussler, G., Stangl, J., Bauer, G., van der Cingel, J. & Bonera, E. Integration of MOSFETs with SiGe dots as stressor material. Solid-State Electron. 60, 75–83 (2011).

Ang, K.-W., Lin, J., Tung, C.-H., Balasubramanian, N., Samudra, G. S. & Yeo, Y.-C. Strained n-MOSFET with embedded source/drain stressors and strain-transfer structure (STS) for enhanced transistor performance. IEEE Trans. Electron Devices. 55, 850–857 (2008).

Chui, K.-J., Ang, K.-W., Madan, A., Wang, H., Tung, C.-H., Wong, L.-Y., Wang, Y., Choy, S.-F., Balasubramanian, N., Li, M. F., Samudra, G. & Yeo, Y.-C. Source/drain germanium condensation for P-channel strained ultra-thin body transistors. Tech. Dig. Int. Electron Devices Meet. 493–496 (2005).

Fischetti, M. V. & Laux, S. E. Band structure, deformation potentials, and carrier mobility in strained Si, Ge, and SiGe alloys. J. Appl. Phys. 80, 2234–2252 (1996).

Lee, M. L., Fitzgerald, E. A., Bulsara, M. T., Currie, M. T. & Lochtefeld, A. Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 97, 011101 (2005).

Roberts, M. M., Klein, L. J., Savage, D. E., Slinker, K. A., Friesen, M., Celler, G., Eriksson, M. A. & Lagally, M. G. Elastically relaxed free-standing strained-silicon nanomembranes. Nature 5, 388–393 (2006).

Scott, S. A. & Lagally, M. G. Elastically strain-sharing nanomembranes: flexible and transferable strained silicon and silicon-germanium alloys. J. Phys. D Appl. Phys. 40, R75–R92 (2007).

Yuan, H.-C., Ma, Z., Roberts, M. M., Savage, D. E. & Lagally, M. G. High-speed strained-single-crystal-silicon thin-film transistors on flexible polymers. J. Appl. Phys. 100, 013708 (2006).

Sun, L., Qin, G., Seo, J. H., Celler, G. K., Zhou, W. & Ma, Z. 12-GHz thin-film transistors on transferrable silicon nanomembranes for high-performance flexible electronics. Small 6, 2553–2557 (2010).

Zhou, H., Seo, J. H., Paskiewicz, D. M., Zhu, Y., Celler, G. K., Voyles, P. M., Zhou, W., Lagally, M. G. & Ma, Z. Fast flexible electronics with strained silicon nanomembranes. Sci. Rep. 3, 129 (2013).

LeGoues, F. K. The effect of strain on the formation of dislocations at the SiGe/Si interface. MRS Bull 21, 38–44 (1996).

Gallas, B., Hartmann, J. M., Berbezier, I., Abdallah, M., Zhang, J., Harris, J. J. & Joyce, B. A. Influence of misfit and threading dislocations on the surface morphology of SiGe graded-layers. J. Cryst. Growth 201/202, 547–550 (1999).

Koester, S. J., Rim, K., Chu, J. O., Mooney, P. M. & Ott, J. A. Effect of thermal processing on strain relaxation and interdiffusion in Si/SiGe heterostructures studied using Raman spectroscopy. Appl. Phys. Lett. 79, 2148–2150 (2001).

Azuma, Y., Usami, N., Ujihara, T., Sazaki, G., Murakami, Y., Miyashita, S., Fujiwara, K. & Nakajima, K. Growth of SiGe bulk crystal with uniform composition by directly controlling the growth temperature at the crystal-melt interface using in situ monitoring system. J. Cryst. Growth 224, 204–211 (2001).

EerNisse, E. P. Stress in thermal SiO2 during growth. Appl. Phys. Lett. 35, 8–10 (1979).

Stan, G., Krylyuk, S., Davydov, A. V. & Cook, R. F. Compressive stress effect on the radial elastic modulus of oxidized Si nanowires. Nano Lett. 10, 2031–2037 (2010).

Moselund, K. E., Dobrosz, P., Olsen, S., Pott, V., De Michielis, L., Tsamados, D., Bouvet, D., O'Neill, A. & Ionescu, A. M. Bended gate-all-around nanowire MOSFET: a device with enhanced carrier mobility due to oxidation-induced tensile stress. Tech. Dig. Int. Electron Devices Meet. 191–194 (2007).

Hay, R. S. Developments in Strategic Materials and Computational Design III, (John Wiley & Sons, Inc., Hoboken, NJ, USA, 2012).

Seike, A., Tange, T., Sugiura, Y., Tsuchida, I., Ohta, H., Watanabe, T., Kosemura, D., Ogura, A. & Ohdomari, I. Strain-induced transconductance enhancement by pattern dependent oxidation in silicon nanowire field-effect transistors. Appl. Phys. Lett. 91, 202117 (2007).

Resnik, D., Aljančič, U., Vrtačnik, D., Možek, M. & Amon, S. Mechanical stress in thin film microstrures on silicon substrate. Vacuum 80, 236–240 (2005).

Moselund, K. E., Najmzadeh, M., Dobrosz, P., Olsen, S. H., Bouvet, D., De Michielis, L., Pott, V. & Ionescu, A. M. The high-mobility bended n-channel silicon nanowire transistor. IEEE Trans. Electron Device 57, 866–876 (2010).

Gunnars, J. & Wiklund, U. Determination of growth-induced strain and thermo-elastic properties of coatings by curvature measurements. Mater. Sci. Eng. 336, 7–21 (2002).

Wolf, I. D. Micro-Raman spectroscopy to study local mechanical stress in silicocn integrated circuits. Semicond. Sci. Technol. 11, 139–154 (1996).

Wong, L. H., Wong, C. C., Liu, J. P., Sohn, D. K., Chan, L., Hsia, L. C., Zang, H., Ni, Z. H. & Shen, Z. X. Determination of Raman phonon strain shift coefficient of strained silicon and strained SiGe. Jpn. J. Appl. Phys. 44, 7922–7924 (2005).

Rochat, G., Leterrier, Y., Fayet, P. & Månson, J.-A. E. Stress controlled gas-barrier oxide coatings on semi-crystalline polymers. Thin Solid Films 484, 94–99 (2005).

Sun, Y., Thompson, S. E. & Nishida, T. Physics of strain effects in semiconductors and metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 101, 104503 (2007).

Yu, D., Zhang, Y. & Liu, F. First-principles study of electronic properties of biaxially strained silicon: effects on charge carrier mobility. Phys. Rev. B 78, 245204 (2008).

Sharma, B. K., Jang, B., Lee, J. E., Bae, S.-H., Kim, T. W., Lee, H.-J., Kim, J.-H. & Ahn, J.-H. Load-controlled roll transfer of oxide transistors for stretchable electronics. Adv. Funct. Mater. 23, 2024–2032 (2013).

Kim, T.-i., Jung, Y. H., Chung, H.-J., Yu, K. J., Ahmed, N., Corcoran, C. J., Park, J. S., Jin, S. H. & Rogers, J. A. Deterministic assembly of releasable single crystal silicon-metal oxide field-effect devices formed from bulk wafers. Appl. Phys. Lett. 102, 182104 (2013).

Chung, H.-J., Kim, T.-i, Kim, H.-S., Wells, S. A., Jo, S., Ahmed, N., Jung, Y. H., Won, S. M., Bower, C. A. & Rogers, J. A. Fabrication of releasable single-crystal silicon-metal oxide field-effect devices and their deterministic assembly on foreign substrates. Adv. Funct. Mater. 21, 3029–3036 (2011).

Kubat, J., Rigdahl, M. & Selden, R. Internal stresses and activation volumes from the stress relaxation behavior of polyethylene at low deformations. J. Appl. Polym. Sci. 20, 2799–2809 (1976).

Chen, F., Euaruksakul, C., Liu, Z., Himpsel, F. J., Liu, F. & Lagally, M. G. Conduction band structure and electron mobility in uniaxially strained Si via externally applied strain in nanomembranes. J. Phys. D Appl. Phys. 44, 325107 (2011).

Yu, D., Zhang, Y. & Liu, F. First-principles study of electronic properties of biaxially strained silicon: Effects on charge carrier mobility. Phys. Rev. B 78, 245204 (2008).

Acknowledgements

This work was supported by the National Creative Research Laboratory (2015R1A3A2066337) through the National Research Foundation of Korea (NRF) and the Research Program of Korea Institute of Machinery and Materials (SC 1090).

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Competing interests

The authors declare no conflict of interest.

Additional information

Supplementary Information accompanies the paper on the NPG Asia Materials website

Supplementary information

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Lee, W., Hwangbo, Y., Kim, JH. et al. Mobility enhancement of strained Si transistors by transfer printing on plastic substrates. NPG Asia Mater 8, e256 (2016). https://doi.org/10.1038/am.2016.31

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/am.2016.31

This article is cited by

-

Si nanomebranes: Material properties and applications

Nano Research (2021)