Abstract

A new technique is proposed for the activation of low temperature amorphous InGaZnO thin film transistor (a-IGZO TFT) backplanes through application of a bias voltage and annealing at 130 °C simultaneously. In this ‘electrical activation’, the effects of annealing under bias are selectively focused in the channel region. Therefore, electrical activation can be an effective method for lower backplane processing temperatures from 280 °C to 130 °C. Devices fabricated with this method exhibit equivalent electrical properties to those of conventionally-fabricated samples. These results are analyzed electrically and thermodynamically using infrared microthermography. Various bias voltages are applied to the gate, source, and drain electrodes while samples are annealed at 130 °C for 1 hour. Without conventional high temperature annealing or electrical activation, current-voltage curves do not show transfer characteristics. However, electrically activated a-IGZO TFTs show superior electrical characteristics, comparable to the reference TFTs annealed at 280 °C for 1 hour. This effect is a result of the lower activation energy, and efficient transfer of electrical and thermal energy to a-IGZO TFTs. With this approach, superior low-temperature a-IGZO TFTs are fabricated successfully.

Similar content being viewed by others

Introduction

Transparent and flexible electronics are attracting interest for their potential application in next generation electronics including paper displays, wearable computers, and roll-up devices1. Amorphous InGaZnO thin film transistors (a-IGZO TFTs) have been extensively studied as their field-effect mobility (>10 cm2 V−1 s−1) is greater than a-Si equivalents (~1 cm2 V−1s−1), and the processing temperatures required are lower than for a-Si (~350 °C), and polycrystalline Si (~500 °C) TFTs2,3,4. Despite the stated advantages of a-IGZO TFTs, the low thermal resistance of flexible substrates can complicate processing. Sputtered a-IGZO TFTs have been reported to require an additional 300 °C annealing process after deposition of the a-IGZO active layers to obtain sufficient semiconductor properties and transfer characteristics5. Oxide films are deposited during the sputtering process, and defect sites are formed from high energy ion bombardment. These defects act as scattering centers or charge carrier traps, leading to degradation of the electrical characteristics of a-IGZO TFTs6,7,8,9. In, Ga, Zn, and O atoms require an activation energy (Ea) sufficient to rearrange the metal oxide structure through high temperature annealing. Without activation through the annealing process, the sputtered a-IGZO layer does not have semiconducting characteristics. However, flexible plastic substrates with a low-glass transition temperature are not suitable for high temperature treatment10,11. The thermal budget is proportional to the annealing temperature, time, and area. For a 46 inch full-HD panel, only 0.66% of the panel area comprises the final active layer. The conventional activation process is wasteful as the entire panel is annealed, and over 99% of the active layer is etched after activation. Therefore, it is essential to develop an efficient, localized, low-temperature activation method to practically realize flexible electronics. However, previous researches on low-temperature activation such as UV annealing and high pressure annealing cannot overcome the same limitation, either. Here, we demonstrate a technique for the selective annealing of oxide films, using biased electrodes, to fabricate an a-IGZO backplane at 130 °C as shown in Fig. 1a. The electrical characteristics and chemical properties of electrically activated a-IGZO TFTs (EATs) were also investigated. Thermodynamic and electrical analysis of the a-IGZO channel will be used to explore the mechanisms of electrical activation.

Results

The electrical characteristics of thermally activated TFTs (TATs) and electrically activated TFTs (EATs)

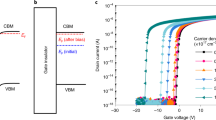

Figure 2d shows the transfer characteristics of the samples annealed at several temperatures (80–280 °C) for 1 hour. The a-IGZO TFTs annealed at 280 °C (TATs, sample number 1) exhibited sufficient transfer characteristics, such as field-effect mobility (μFET); it is known that annealing at temperatures around 300 °C is required to control the properties of AOS films and TFTs12.

Schematic illustration of (a) a-IGZO TFT, (b) conventional activation via thermal annealing at 280 °C on hotplate for 1 hour, (c) electrical activation. Transfer characteristics of the a-IGZO TFTs, (d) annealed at 80, 130, 180, 230, and 280 °C, (e) non-activated (electrical) and (f) activated (electrical) samples.

Figure 2e shows the transfer characteristics of the non-activated (electrical) TFTs (VG (−50) VDS (0)_1, VG (−50) VDS (0)_2, VG (−50) VDS (−50), VG (−50) VDS (+50), VG (−50) VDS (+100), VG (0) VDS (0)_1, VG (0) VDS (0)_2, VG (0) VDS (+50), VG (+50) VDS (0)_1, VG (+50) VDS (0)_2, and VG (+50) VDS (−50)_0.5 h). Figure 2f shows the transfer characteristics of EATs (VG (0) VDS (−50), VG (0) VDS (+100), VG (+50) VDS (−50), VG (+50) VDS (+50), VG (+50) VDS (+100), and VG (+50) VDS (−50)_2 h). A non-activated (thermal) TFT (NAT) that was annealed at 130 °C for 1 hour without an applied bias in Fig. 2d and the EATs were annealed at the same temperature, but only the EATs demonstrated activated transfer characteristics.

The EATs passed a low current for negative VG, and a high current for positive VG, suggesting semiconductor characteristics. In contrast, the NAT demonstrated metallic characteristics for all tested gate biases.

Despite the low fabrication temperature, the μFET, on/off ratio, Von, subthreshold swing (SS), and maximum trapped charge density (Nmax) of the EATs was similar to the TAT, as shown in Table 1. μFET was obtained from the saturation region of the IDS–VDS curves (VDS ≥ VGS−VT) using the equation

where Ci and VT are the gate capacitance and threshold gate voltage respectively13. Figure S1 (Supplementary Information) shows a comparison of a-IGZO TFTs (TAT, VG (−50) VDS (−50), VG (−50) VDS (+50), VG (−50) VDS (+100), VG (0) VDS (−50), VG (0) VDS (+50), VG (0) VDS (+100), VG (+50) VDS (−50), VG (+50) VDS (+50), VG (+50) VDS (+100), and VG (+50) VDS (−50)_2 h) in terms of SS and μFET, and the optimized conditions were determined by observation of improvements in these factors. The optimized sample conditions were VG = 50 V, VS = 0 V, and VD = −50 V. The optimized EAT (sample number 14, VG (+50) VDS (−50)) characteristics were slightly better than the TAT: μFET increased from 9.90 to 10.66 cm2 V−1 s−1, and SS decreased from 0.42 to 0.36 shown in Table 1.

Thermodynamic analysis of EATs

Infrared microthermography was used to investigate the heating between the source and drain electrodes. The measurement concept and experimental details are described in ref. 14. The maximum temperature change (∆Tmax) measured in the TFT channel of each sample is given Table 1. Figure 3a shows an image of VG (+50) VDS (−50), and Fig. 3b–d shows the TFT temperature distribution during the electrical activation process (VG = 50 V). It can be seen that the annealing is focused in the predetermined channel regions. Self-heating occurs during the electrical activation process due to the high drain current, increasing the temperature of the channel region15,16,17.

Infrared microthermography results.

(a) Optical microscope image of a-IGZO TFT (sample number 14, VG (+50) VDS (−50)) Temperature distribution when VS = 0, VD = −50 V, and (b) VG = +50 V (sample number 14, VG (+50) VDS (−50)) VG = 0 V (sample number 9, VG (0) VDS (−50)) and (d) VG = −50 V (sample number 4, VG (−50) VDS (−50)). (e) ∆Tmax in the channel of a-IGZO TFTs under VG = −50, 0, and +50 V conditions. (f) ∆Tmax in the channel of a-IGZO TFT (sample number 14, VG (+50) VDS (−50)) as a function of ID. The inset graph shows ∆Tmax versus the square of ID under the same condition.

Figure 3e shows ∆Tmax of the a-IGZO channel when Vg = −50 V, 0 V, and 50 V. ∆Tmax was seen to increase with |VDS| for each VG condition. When VDS = 0 V, no drain current flows, so Joule heating did not occur. Joule heating increased with the drain current that originates from VG in accordance with Equation 1. A high positive VG attracts more electron carriers, and generates heat. Negative VG repels electrons, and results in the least Joule heating.

Joule heating is the process by which the flow of an electric current through a conductor produces heat. According to Joule’s first law, the amount of heat released is proportional to the square of the current such that

where R is the resistance of the material, and t is the duration of the current flow18. Based on the Equation (2), the amount of Joule heat increases as the material is low resistive (low oxygen concentration in oxide) and more current flows in the same voltage condition.

For a system with N particles, its thermal energy Uthermal energy is

where k is the Boltzmann constant, f is the number of degrees of freedom, and T is absolute temperature19. During the electrical activation process, the temperature of the a-IGZO channel increased. If we assume that a system is a-IGZO TFT, its thermal energy can be changed as follow from the Equation 3.

According to the first law of thermodynamics, the change in internal energy of a system (U) is equal to the heat (Q) added to the system minus the work (W) done by the system20,21,22,23.

If we assume that no work is done by an a-IGZO channel, the variation in energy will be the heat energy added to the channel.

In our assumption, the increase in temperature of an a-IGZO channel is attributed to the heat generated by current flow

We can rewrite the Equation 7 by using Equations 2 and 4,

We assumed that N, f, k, R, and t are constant values, and T (temperature) changed by ID (current) flowed.

Therefore, it can be expected that the temperature change will be proportional to the square of the drain current, and the temporal behavior of the samples is in agreement with our expectations as shown in Fig. 3f, from which the following equation can be extrapolated.

which states the relationship between the temperature change and drain current in the case of VG = 50, VS = 0, and VD = −50 V. Also, this equation matches well with the data from VG (+50) VDS (−50).

XPS and SE analysis of before (as-deposited) and after electrical activation

Figure 4a shows the valence band offsets (EFV = EF − EV) between the Fermi level (EF) and the valence band maximum (EV) using XPS data. Optical bandgap energies (Eg) were derived from the SE data, as shown in Fig. 4b. The conduction band offsets (ECF = EC − EF) between the Fermi energy level (EF) and the conduction band minimum (EC) were calculated using the valence band offsets and bandgap energies. Figure 4c shows the band alignments measured before (as-deposited) and after the electrical activation process, and the ECF results are given in Table S2 (Supplementary Information). The results indicate that the electrical characteristics of a-IGZO films vary with the carrier concentration. According to semiconductor physics theory, the electron concentration (n) can be described by the following equation:

where Nc is the effective density of states at the conduction band edge. This equation shows that n increases exponentially as ECF decreases. EF before electrical activation is located near EC, and therefore pre-activation EATs with relatively small ECF values have metallic properties due to the excessive n of the a-IGZO active layer. The EF of post-activation EATs is separated from EC, suggesting that the ECF of the EAT is increased after the electrical activation process, resulting in semiconductor characteristics with appropriate n in the a-IGZO active layer.

Figure 5a,b shows the O 1s peaks from XPS analysis for a-IGZO TFTs before (as-deposited) and after electrical activation, respectively. XPS data are calibrated using the C 1s peak centered at 284.8 eV, and the O 1s peaks were deconvolved into two peaks. The lower binding energy peak represents a metal oxide lattice without oxygen vacancy, centered at 530 ± 0.1 eV. The higher binding energy peak is related to non-lattice oxygen, and is centered at 531.9 ± 0.3 Ev24. The peak is the remaining peak sum after subtraction of the lattice oxygen peak from the total, and includes the peaks of oxygen vacancy and hydroxyl groups. In comparison with pre-activated EATs, EATs have more lattice oxygen (increased from 67.7% to 84.2%) and less non-lattice oxygen (decreased from 32.3% to 15.8%). This result of increased lattice oxygen indicates that electrical activation decomposes the weak metal oxide bonds, and rearranges atoms to form a chemical atomic network. Therefore, XPS and SE results demonstrate that electrical activation of a-IGZO TFT is effectively achieved24,25,26.

Discussion

Based on results of electrical, thermodynamic and chemical analysis, we have compared and analyzed electrically activated samples in various voltage bias conditions (VG, VS, and VD) so that we can suggest mechanisms of electrical activation. Thermal energy sufficient for channel activation should be generated and selectively transferred to the channel area. Joule heating is caused by the motion of particles that form the current (typically electrons) and the ions that form the body of the conductor. Charged particles are accelerated by an electric field, and the increase in the kinetic vibration energy of colliding ions is transferred from the power supply (Fig. 6a).

The polarity of VG, and the electrical potential between the three electrodes must be considered. The polarity of VG produces a Coulombic force. As VG is made more positive, more carriers accumulate in the channel, causing a temperature increase (Fig. 6b). Therefore, the optimized VG condition is at 50 V. For example, VG (+50) VDS (−50) experienced a temperature increase greater than that of VG (−50) VDS (−50), resulting from VG = 50 V, although both devices had the same absolute voltages of VG, VS, and VD.

During the electrical activation process, the device temperature reached 58 °C, depending on various bias conditions. However, similar temperature increases occur when the signs and values of the applied voltages differed, as is clearly shown in Table S1 for VG (0) VDS (−50) and VG (+50) VDS (+50). Therefore, the potential differences |VDS|, VGS, and VGD are also important. As discussed previously, |VDS| is required to be greater than 50 V (Fig. 6c). In addition, a potential difference of at least 50 V is needed between VGS or VDS. For example, VG (0) VDS (−50) and VG (+50) VDS (+50) could be electrically activated as they had the same |VDS| of 50 V. VGD of VG (0) VDS (−50) was 50 V, and VGS of VG (+50) VDS (+50) was 50 V. Other samples could be activated if they had potential differences of more than 50 V including |VDS|.

In addition to an increase in substrate temperature, Ea is reduced by applying a bias during electrical activation. The activation temperature was decreased from 280 °C to 130 °C, a difference of 150 °C. However, the maximum temperature increase from Joule heating is 54 °C, suggesting that electrical activation may not be achieved by Joule heating alone. The a-IGZO layer comprises numerous electrons, protons, and ions of In, Ga, Zn, and O. Figure 7a shows how the charged particles experience attractive or repulsive forces, depending on the applied electric field. Therefore, external force is applied to the a-IGZO layer. As more external energy is added to the a-IGZO system, it transitions from a low-energy state to a metastable state27. This increase in the free energy of an a-IGZO system results in a decreased Ea (Ea’ in Fig. 7b). The electric field is analogous to a chemical catalyst that lowers Ea. However, a catalyst does not change the free energies of the original reactant or products; rather, the reactant energy and the product energy are maintained while Ea is altered. In contrast, electrical activation changes the free energy of the reactant, which is an a-IGZO film before activation. The activation of the chemical reaction by an applied electric field is controlled by the bias voltage. The electrical energy compensates for the insufficient thermal energy at low temperatures, so that the annealing temperature can be decreased without degradation of the electrical characteristics.

Conventional high temperature annealing heats all parts of the substrate, wasting a large amount of thermal energy in the active layer, which is etched away after activation. The selective electrical activation method enables efficient annealing focused on the predetermined areas defined in Fig. 1a. Simultaneous electrical and thermal treatment of the active layer induces localized Joule heating between the source and drain, resulting in no annealing of the peripheral areas outside of the channel region.

Through this novel technique, unwanted thermal damage of plastic substrates can be avoided when fabricating a-IGZO TFTs. Therefore, this new approach overcomes some limitations of the high temperature fabrication process required for conventional a-IGZO TFTs, and will enable the fabrication of large-area flexible display technology28.

A new technology for low temperature activation of the a-IGZO channel layer was developed, utilizing electrical energy in addition to thermal energy. The a-IGZO TFTs activated at low temperature (130 °C) exhibited superior electrical characteristics. Thermodynamic and electrical analysis showed that electrical activation may be promoted by two mechanisms. Ea is reduced with an applied electric field, and sufficient energy is provided by the sum of the electrical and thermal energies. The relationship between the self-heating effect and the local activation was discussed based on results from infrared microthermography. The annealing effect was focused in the channel region, and the temperature of the other areas was lower. As a result, this low temperature activation technique reduces 99% of the thermal budget by decreasing the anneal temperature and area. Electrical activation does not require the development of new equipment as existing facilities used for bias temperature stress testing can be used. This technique allows the use of inexpensive flexible substrates that have a low glass-transition temperature. Therefore, this research demonstrates the possibility of electric field-aided fabrication of a-IGZO TFTs at low temperatures, reducing fabrication costs and providing a great benefit to the flexible electronics community.

Methods

Fabrication of a-IGZO TFTs

a-IGZO TFTs were fabricated with an inverted staggered structure on a heavily doped p-type Si wafer with a 120-nm-thick layer of thermally grown SiO2. A 40-nm-thick a-IGZO active layer was deposited by radio frequency sputtering on the cleaned Si substrate using an IGZO target (In2O3:Ga2O3:ZnO = 1:1:1 mol%) at room temperature for 5 minutes. The 200-nm-thick aluminum source and drain electrodes were deposited by thermal evaporation, the channel region was defined with a width (W) of 1,000 μm, and a length (L) of 150 μm. Figure 2a shows a schematic of the a-IGZO TFTs. The conventional thermally activated TFTs (TATs, sample number 1) used as a reference were annealed at 280 °C for 1 hour in air, after the source and drain electrodes were patterned as shown in Fig. 2b. For clarity, the high-temperature annealing process described above will be referred to as ‘thermal activation’. A constant DC voltage was applied to the gate, drain, and source electrodes of the EATs for 1 hour. The samples were located inside a dark probe box to block light and fabricated at 130 °C, with the biases specified in Table S1. An illustration and photograph of the bias process are shown in Figs 1c and 2d. Figure 1b is a photograph of a-IGZO TFTs fabricated on the PI substrate. Figure 1c indicates that electrical activation on flexible substrates is feasible.

Electrical, thermal, and chemical measurements

Electrical characteristics were measured in a dark box under ambient conditions using a semiconductor parameter analyzer (HP 4156C, Hewlett Packard, Palo Alto, CA, USA). TFT measurements were conducted by varying the gate voltage (VGS) from −30 V to 30 V, with a fixed drain voltage (VDS) of 10.1 V. High-resolution infrared microthermographic analysis was used to study localized heating of the samples, and the chemical composition of each film was analyzed with depth profile X-ray photoelectron spectroscopy (XPS). Spectroscopic ellipsometry (SE) was used for TFT band alignment.

Additional Information

How to cite this article: Lee, H. et al. Electric Field-aided Selective Activation for Indium-Gallium-Zinc-Oxide Thin Film Transistors. Sci. Rep. 6, 35044; doi: 10.1038/srep35044 (2016).

References

Kim, H. et al. Solution-processed bottom-emitting polymer light-emitting diodes on a textile substrate towards a wearable display. J. Inf. Disp. 16, 179–184 (2015).

Snell, A. J. et al. Application of amorphous silicon field effect transistors in addressable liquid crystal display panels. Appl. Phys. 24, 357–362 (1981).

Yamauchi, N. & Reif, R. Polycrystalline silicon thin films processed with silicon ion implantation and subsequent solid-phase crystallization: theory, experiments, and thin-film transistor applications. Appl. Phys. 75, 3235–3257 (1994).

Nag, M. et al. High performance a-IGZO thin-film transistors with mf-PVD SiO2 as an etch-stop-layer. J. Inf. Disp. 22, 23–28 (2014).

Seo, D. K. et al. Drastic improvement of oxide thermoelectric performance using thermal and plasma treatments of the InGaZnO thin films grown by sputtering. Acta Mater. 59, 6743–6750 (2011).

Zheng, Z. W., Cheng, C. H. & Chen, Y. C. Low operation voltage InGaZnO thin film transistors with LaAlO3 gate dielectric incorporation. ECS J. Solid State Sci. Technol. 2, N179–N181 (2013).

Yabuta, H. et al. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 89, 112123–112123 (2006).

Ross, R. C. & Messier, R. Microstructure and properties of rf-sputtered amorphous hydrogenated silicon films. J. Appl. Phys. 52, 5329 (1981).

Noh, H.-K., Chang, K. J., Ryu, B. & Lee, W.-J. Electronic structure of oxygen-vacancy defects in amorphous In-Ga-Zn-O semiconductors. Phys. Rev. B 84, 115205 (2011).

Wang, C. et al. User-interactive electronic skin for instantaneous pressure visualization. Nat. Mater. 12, 899–904 (2013).

Sekitani, T. & Someya,T. Stretchable, large-area organic electronics. Adv. Mater. 22, 2228–2246 (2010).

Kamiya, T., Nomura, K. & Hosono, H. Origins of high mobility and low operation voltage of amorphous oxide TFTs: electronic structure, electron transport, defects and doping. J. Disp. Technol. 5, 468–483 (2009).

Jeong, S.-K. et al. Dual active layer a-IGZO TFT via homogeneous conductive layer formation by photochemical H-doping. Nanoscale Res. Lett. 9, 619–627 (2014).

Chang, K. S. et al. Precise temperature mapping of GaN-based LEDs by quantitative infrared micro-thermography. Sensors 12, 4648–4660 (2012).

Ro, J.-S. & Hong, W.-E. Joule-heating-induced annealing by applying electric field directly to intrinsic silicon film. Jpn. J. Appl. Phys. 45, L1142–L1145 (2006).

Hong, W.-E. et al. Supergrains produced by lateral growth using Joule-heating induced crystallization without artificial control. Appl. Phys. Lett. 96, 052105 (2010).

Kim, D. H. et al. Thermal deformation of glass backplanes during Joule-heating induced crystallization process. Vacuum 85, 847–852 (2011).

Prokhorov, A. M. et al. Joule–Lenz law. (Great Soviet Encyclopedia, 1972).

Schroeder, D. V. An Introduction to Thermal Physics. (Addison-Wesley, 1999).

Guggenheim, E. A. Thermodynamics. An Advanced Treatment for Chemists and Physicists, seventh edition. (Elsevier Science, 1985).

Charles, K. & Hervert, K. Thermal Physics, second edition. (Macmillan, 1980).

Adkins, C. J. Equilibrium Thermodynamics, second edition (McGraw-Hill, 1968).

Gerogy, L. & David, J. Understanding Non-equilibrium Thermodynamics. Foundations, Applications, Frontiers. (Springer, 2008).

Jeong, S. et al. Role of gallium doping in dramatically lowering amorphous-oxide processing temperatures for solution-derived indium zinc oxide thin-film transistors. Adv. Mater. 22, 1346–1350 (2010).

Tak, Y. J. et al. Activation of sputter-processed indium-gallium-zinc oxide films by simultaneous ultraviolet and thermal treatments. Scientific reports 6, 21869 (2016).

Kim, W.-G. et al. High-pressure Gas Activation for Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistors at 100°C. Scientific reports 6, 23039 (2016).

Langer, J. S. Statistical theory of the decay of metastable states. Ann. Phys. 54, 258–275 (1969).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (No. 2011-0028819) and Samsung Display.

Author information

Authors and Affiliations

Contributions

H.L. and Y.J.T. concept and study design; H.L., J.W.P. and J.C. conducted experiments; H.L., Y.J.T. and C.B.J. analyzed the results; T.S.J. and W.-G.K. gave advice; K.S.C. and H.J.K. supervised; H.L. wrote the manuscript; All authors reviewed the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Lee, H., Chang, K., Tak, Y. et al. Electric Field-aided Selective Activation for Indium-Gallium-Zinc-Oxide Thin Film Transistors. Sci Rep 6, 35044 (2016). https://doi.org/10.1038/srep35044

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep35044

This article is cited by

-

Solid–liquid phase transition induced electrocatalytic switching from hydrogen evolution to highly selective CO2 reduction

Nature Catalysis (2021)

-

Electron-blocking by the potential barrier originated from the asymmetrical local density of state in the oxide semiconductor

Scientific Reports (2017)

-

Impact of transient currents caused by alternating drain stress in oxide semiconductors

Scientific Reports (2017)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.