Abstract

Solution processed fullerene (C60) molecular floating gate layer has been employed in low voltage nonvolatile memory device on flexible substrates. We systematically studied the charge trapping mechanism of the fullerene floating gate for both p-type pentacene and n-type copper hexadecafluorophthalocyanine (F16CuPc) semiconductor in a transistor based flash memory architecture. The devices based on pentacene as semiconductor exhibited both hole and electron trapping ability, whereas devices with F16CuPc trapped electrons alone due to abundant electron density. All the devices exhibited large memory window, long charge retention time, good endurance property and excellent flexibility. The obtained results have great potential for application in large area flexible electronic devices.

Similar content being viewed by others

Introduction

The next-generation electronic systems are expected to be light, flexible and portable for applications in integrated circuits (ICs), organic light emitting diodes (OLEDs), solar cells, radio frequency identification (RFID) tags and so on1,2,3,4,5,6,7,8,9. Memory is an essential part of electronic systems for data processing, storage and communication; however, currently available inorganic memories are not compatible with flexible substrates. Thus new approaches to develop flexible memory are necessary to realize large area flexible electronics. Tremendous efforts have been made towards developing high-density, high-speed and nonvolatile memory devices10,11,12,13,14,15. Among many types of nonvolatile memory, transistor-based flash memory with nano-segmented floating gate architecture have attracted huge interest due to the massive memory capacity and advanced fabrication technology16. The stored charges are located in the potential well of the blocking and tunnelling dielectric layers, resulting in nonvolatile memory operations. If the charge storage layers are made up of thin films, any dielectric defects would leak the stored charges and degrade the retention property of the device. Therefore, a monolayer consists of well-separated nanoparticles could be a best choice to store the charges. On this regard, multidisciplinary efforts have been taken in recent years to fabricate metal nanocrystal based floating gate layer, including thermal evaporation17,18, electrostatic self-assembly19,20, micro-contact printing21 and synthesis in block copolymer22,23. However, nanoparticle assembly and morphology of the nanoparticle film should be controlled carefully to avoid nanoparticle-to-nanoparticle charge tunnelling. One solution to the problem is to utilize alternate charge storage elements with high charge-carrier binding energies and large area densities. Molecular materials, which are on the order of nanometer or even sub-nanometer in size, represent such idealized candidates with high charge density storage sites24. Among them, C60, the most common buckyball clusters in fullerene family, are of great interest due to their potential applications in electronic devices using their semiconducting features25,26. Most of the reports on C60 are based on time-consuming vacuum sublimation process, which is not compatible with large area roll-to-roll fabrication method27. A facile solution processing method to obtain the floating gate layer should be favorable for technological applications. C60 derivatives have gained a lot of attention in transistors, photovoltaic devices and memory cells due to their high solubility in organic solvent28,29,30,31,32,33. However, the synthesis of C60 derivatives are still complicated and expensive; meanwhile their electronic performances are not as good as pristine C6034. Pristine C60 is reasonably soluble in organic solvents which could pave a way for solution processed molecular gated flexible flash memories. The preparation of defined density of molecular charge trapping elements via simple solution process remains challenging.

In this work, we demonstrate a simple approach for the preparation of C60 molecular floating gate layer on a flexible substrate. The coverage of the molecular floating gate or the density of molecular charge trapping layer is facilely controlled by spin-coating method in a single step. We systematically study the charge trapping mechanism of the C60 floating gate under ambient conditions. Flash memory transistors with air-stable p-type pentacene and n-type copper hexadecafluorophthalocyanine (F16CuPc) as semiconductors have been fabricated. The pentacene device exhibited a memory window of 4 V with both hole and electron trapping ability, while the F16CuPc device trapped electrons alone with a memory window of 2 V. All the devices exhibited charge retention larger than 104 s with good cell-to-cell uniformity. The electrical performances of all the devices are well-maintained even after 500 programming/erasing cycles and did not degrade substantially upon bending.

Results

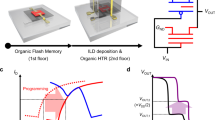

Device struture and operation mechanism

The overall fabrication of the memory transistor is illustrated schematically in Figure 1a. Atomic layer deposited aluminum oxide (Al2O3) was selected as the blocking dielectric layer on top of the silver (Ag) gate electrode on flexible poly(ethylene terephthalate) (PET) substrate. The atomic layer deposition technique allows for a high quality, defect-free dielectric layer with good barrier properties at low substrate temperature. Al2O3 has been demonstrated as a promising high-k dielectric candidate to minimize gate leakage current and achieve low voltage operation in thin film memory transistors35,36,37,38. C60 was spin-coated over the Al2O3 and then thermally annealed at 120°C for 10 min. A thin layer of poly(4-vinylphenol) (PVP) was then spin-coated onto the C60 layer using orthogonal solvents in order to prevent the dissolution of the C60 layer. A detailed description of the fabrication process is given in the experimental section. PVP possesses high resistivity and thermal stability, and has been demonstrated as a good polymer dielectrics19. In our designed dielectric system, PVP has relatively low dielectric constant (4.7) compared with Al2O3 (7)39,40. According to the equation E1 = Vg/(d1 + d2 (ε1/ε2)), where εi are the dielectric constants and di are the thicknesses of the two dielectric layers, the applied electrical field in PVP layer (E1) is relatively stronger than in Al2O3 layer. Therefore, this system enables efficient charge transfer from the semiconductor layer to charge trapping layer through the tunnelling dielectric layer. Due to their good stabilities in ambient, pentacene and F16CuPc were chosen as the p-type and n-type semiconductor to investigate the charging mechanism of the C60 floating gate layer. Figure 1b illustrates the chemical structures of the organic small molecular materials used in this study. Figure 1c displays the atomic force microscopy (AFM) image of the C60 film spin-coated at 1000 rpm. The C60 film exhibited a surface morphology of separated islands, which is favorable for charge storage. The surface morphology of the C60 film spin-coated through high speed is also analyzed and shows relatively low densities (see supporting information Figure S1). Previous studies have shown that the memory capacity is dependent on the charge trapping element density, while the memory window increases with enhanced trapping sites36. Therefore, unless otherwise mentioned, all the memory devices are based on a C60 layer resulting from the low spin-coating speed (1000 rpm).

Electrical performance of p-type memory device

To investigate the trapping capability of C60 in the p-type memory device, we first fabricated a transistor with pentacene as the semiconductor layer. The schematic representation of the tunnelling of charge carriers in pentacene device is illustrated in Figure 2a. The holes are tunnelled through the PVP layer from the highest occupied molecular orbital (HOMO) of pentacene to C60 layer while electrons are tunnelled from the lowest unoccupied molecular orbital (LUMO) of pentacene to C60 trapping layer. It should be noted that intrinsic hole density is higher than electron density in pentacene41,42. Figure 2b shows the electrical characteristics of the pentacene memory device before and after applying the negative gate pulses (−5 V for 100 ms). The electrical properties were found to be uniform by examining different devices. The memory transistors show a hole mobility of about 5 × 10−2 cm2 V−1 s−1 and current on/off ratio of about 103 while the transistors without C60 possess a mobility of about 0.1 cm2 V−1 s−1. The slightly decreased mobility can be attributed to the increased surface roughness when introducing the C60 layer under PVP. The applied electrical field is about 1.1 MV/cm in the tunnelling PVP layer, which is appropriate for efficient charge injection. The high mobility of C60 can guide fast charge distribution and assist the charging process when the charge injection is non-uniform across the C60 layer. The trend of the transfer curves reveals a typical hole trapping behavior indicating holes are injected from pentacene channel into C60 Layer through PVP by the application of the electric field. The trapped holes in C60 layer screened the channel and resulted in decreasing the effective gate electric field. In order to analyze the charging effect of the dielectric system, we also fabricated the device without C60 layer (see supporting information Figure S2). Almost negligible charging and discharging is observed in PVP/Al2O3 stack layers, therefore the charge carriers should mostly be trapped in C60 Layer. The electrical characteristics of the memory devices before and after applying the positive gate pulses (5 V for 100 ms) are shown in Figure 2c. The results indicate that electron trapping also occurs using C60 as the floating gate. In addition, pentacene has instrinsic electron mobility which makes them available to be trapped. This observation is interesting as most of the flash memory devices are based on single charge carrier trapping mechanism17,43. At the same electrical field, the amount of stored holes is more than the electrons according to the equation Q = C × ΔVth where Q is the stored charges, C is the capacitance of the dielectrics and ΔVth is the threshold voltage shift. The Vth as a function of bias time is summarized in Figure 2d. The Vth shift increases with increased programming operation time, both in hole and electron charging process. Furthermore, Vth reach certain saturated values after long bias time, which is similar with metal nanoparticle floating gate memory21,44. During the charging process, the charge carriers (holes or electrons) trapped in the C60 layer can increase the capacitive coupling effect thus limited amount of trapped charge carriers are available at certain gate bias. In addition, the saturation rate of hole trapping process is observed to be quicker than electron trapping process. This may be attributed to the high hole mobility than electron mobility in pentacene45.

(a) Energy band diagram of the pentacene based memory device. (b) Transfer characteristics of the memory transistor before and after negative gate bias. (c) Transfer characteristics of the memory transistor before and after positive gate bias. Inset: Optical imgae of the flexible memory device. (d) Threshold voltage with respect to the gate bias time.

With the property of trapping both holes and electrons, the memory window of the pentacene devices could be further enhanced. Figure 3a and 3b show the electrical characteristics of the two states (The state after positive gate bias 5 V for 1 s is denoted as ON state and the state after negative gate bias −5 V for 1 s is denoted as OFF state). The memory window (Vth shift) can reach about 4 V and the maximum ON/OFF current ratio is about 1.5 × 103. This result is better than previously reported low voltage memory with conventional charge trapping layers such as evaporated metal layer and self-assembled nanoparticles20,35. It should be noted that the memory window depends strongly on the applied gate bias and lager bias could lead to larger memory windows21. Here we kept the applied voltage not exceeding 5 V to ensure the low voltage operation of the memory. The operation mode of the memory transistor has been reproducibly and reversely switched from one state to another state. The endurance properties of the pentacene device were studied by repeated application of gate bias pulses of ±5 V. Figure 3c illustrates the pulse sequence in the test. The ON and OFF state is well maintained for more than 500 cycles as shown in Figure 3d. In addition, we performed the data retention experiment on the devices and Figure 3e illustrates the test pulse sequence. In between the different measurement points, the devices are kept without applying any gate biases. The retention capability is shown in Figure 3f. The memory window is maintained at 82.1% for 104 s, which is comparable with previously reported low voltage organic memory devices3,20,35. In our device, the high energy barrier height of C60 surrounded by PVP suppresses the charge transport between each C60 island. At the same time, charge leakage from C60 to the semiconductor channel is effectively prohibited by the PVP tunnelling layer46,47,48. Therefore, the charge carriers (holes and electrons) are confined at the C60 floating gate49. Overall, both the positive part and negative part of the memory windows are suitable for the use as nonvolatile storage media.

(a) Transfer curve (IDS − VGS) of the pentacene memory at ON and OFF state on log scale. (b) Transfer curve (|IDS|1/2 − VGS) of the pentacene memory at ON and OFF state on linear scale. (c) Test pulse sequence for the endurance test. (d) Endurance characteristics of the pentacene device as a function of bias cycles. (e)Test pulse sequence for the retention test. (f) Data retention capability as a function of time.

Electrical performance of n-type memory device

We further explore the trapping capability of C60 in n-type memory device, in which F16CuPc is selected as the semiconductor layer. Figure 4a depicts the energy band diagram of charge carrier tunnelling in F16CuPc based device. Figure 4b shows the electrical characteristics of F16CuPc memory device before and after applying a positive gate pulse (5 V for 100 ms). The electrons tunnelled from F16CuPc channel into the C60 Layer through PVP, resulting in a decreased effective gate electrical field. Such a destructive electrical field leads to a reduced channel conductance, and the transfer curves shift towards the positive direction. The F16CuPc device without C60 layer is also fabricated and almost no charging effect of the dielectric system is observed (see supporting information Figure S3). The memory transistors show an electron mobility of about 1.8 × 10−3 cm2 V−1 s−1 and current on/off ratio of about 102 while the F16CuPc transistors without C60 show a mobility of about 3 × 10−3 cm2 V−1 s−1. Further applying a negative gate pulse (−5 V for 100 ms) do not induce a negative shift of the transfer curves, which might be originated from the extremely low hole mobility of F16CuPc50. It is understood that available minority carrier (hole) density in F16CuPc is much lower than the minority carrier (electron) density in pentacene. Therefore, we found both electron and hole trapping in pentacene based devices where as only electrons are trapped in F16CuPc based devices. The Vth with respect to the bias time is summarized in Figure 4d. The Vth shift towards more positive direction with prolonged bias, suggesting that additional charge carrier is brought to the molecular floating gate with increased bias time. The saturated level is also be observed here, demonstrating both trapped holes and electrons would cause capacitive coupling in the C60 floating gate.

(a) Energy band diagram of the F16CuPc based memory device. (b) Transfer characteristics of the memory transistor before and after positive gate bias. (c) Transfer characteristics of the memory transistor before and after negative gate bias. (d) Threshold voltage as a function of the gate bias time.

Figure 5a and 5b show the electrical characteristics of the F16CuPc memory device at two states (The high conductance state is denoted as ON state and the low conductance state is denoted as OFF state). The memory window is about 2 V and the maximum ON/OFF current ratio is about 7 × 102. Continuous application of gate bias pulses of ±5 V for 1 s is carried out to measure the endurance properties as illustrated in Figure 5c. The ON and OFF state has been well maintained for more than 500 cycles as shown in Figure 5d. The test pulse sequence for the data retention test in F16CuPc device is illustrated in Figure 5e. The ON state and OFF state is well separated with respect to the elapsed time as shown in Figure 5f. About 19.2% of the memory window is lost after a retention time of 104 s. The storage ability of the memory is comparable to recently reported memory devices based on n-type semiconductors51,52.

(a) Transfer curve (IDS − VGS) of the F16CuPc memory at ON and OFF state on log scale. (b) Transfer curve (|IDS|1/2 − VGS) of the F16CuPc memory at ON and OFF state on linear scale. (c) Test pulse sequence for the endurance test. (d) Endurance characteristics of the F16CuPc device with respect to the number of bias operations. (e)Test pulse sequence for the retention test. (f) Data retention capability with respect to the elapsed time.

Bending stability of the memory devices

In addition to the reliable memory operations, the bending stability is another important parameter to examine the reliability of the flexible devices. The organic/inorganic bilayer dielectric structure used in our device can reduce the possibility of cracking or delamination during repetitive bending53. Flexibility tests using cyclic bending were performed both in tensile and compressive mode with a bending radius of 10 mm. Figure 6a shows the schematic diagram of the bended device in a compressive state and Figure 6b illustrates the tensile state. The strain can be estimated from the equation D/2R, where D is the thickness of the substrate and R is the bending radius54. The bending tests were done up to 500 times to confirm the flexibility of both the pentacene and F16CuPc devices. Figure 6c and 6d show the memory window as a function of compressive bending cycles. Figure 6e and 6f show the memory window as a function of tensile bending cycles. These results confirm that all the devices exhibit stable programmable properties with good mechanical flexibility.

(a) Schematic illustration of the device at compressive state. (b) Schematic illustration of the device at tensile state. (c) Memory window of the pentacene device with respect to compressive bending cycles. (d) Memory window of the F16CuPc device with respect to compressive bending cycles. (e) Memory window of the pentacene device with respect to tensile bending cycles. (f) Memory window of the F16CuPc device with respect to tensile bending cycles.

Discussion

The high mobility of C60 can guide fast charge distribution and assist the charging process when the charge injection is non-uniform across the C60 layer. For the pentancene based p-type semiconductor devices, the trend of the transfer curves shows a typical hole trapping behavior indicating holes are injected from pentacene channel into C60 Layer through PVP by the application of the electric field. Due to intrinsic electron mobility as minority carriers, electron trapping also occurs using C60 as the floating gate in pentacene based devices. In addition, due to the high intrinsic hole mobility of holes than electrons in pentacene, the saturation rate of hole trapping process is observed to be quicker than electron trapping process. For the pentacene based devices, both the positive part and negative part of the memory windows are suitable for the use as nonvolatile storage media. On the other hand, for the devices based on n-type semiconductor F16CuPc, available minority carrier (hole) density is much lower than the minority carrier (electron) density in pentacene. Therefore, only electrons are trapped in F16CuPc based devices. The electrons tunnelled from F16CuPc channel into the C60 Layer through PVP, resulting in a decreased effective gate electrical field which leads to a reduced channel conductance, and the transfer curves shift towards the positive direction. During the charging process, due to the increased capacitive coupling between the trapped charge carriers (holes or electrons) in the C60 layer limited amount of trapped charge carriers are available at certain gate bias for both pentacene and F16CuPc based devices.

Although metal nano-floating gate have been widely investigated as the charge trapping layer in flash memories, they are still suffering from poor processability to implement them in printing technology. The solution processed molecular materials should be a choice for large area printable electronics. On the other hand, unlike conventional metal or metal nanoparticle based memory device, the trapping capability of C60 will be of great importance to realize functional nonvolatile memory. Since molecular materials can be functionlized to obtain multifunctional properties, it is important to understand the working mechanism of such molecular floating gate devices. The C60 floating gates showed ambipolar trapping behavior in the pentacene based memories and unipolar trapping behavior in the F16CuPc based memories. The approach to trap both holes and electrons in memory devices is an important to achieve large memory window and other electrically variable properties.

Our fabrication methods including the fabrication of C60 molecular floating gate layer and PVP tunneling dielectric layer are solution-processed. The simplified fabrication steps and low temperature processing method is quite promising for flexible electronics. The sucessful adopting of this structure on flexible substrates demonstrates that this method is mass-producible to construct innovative large area electronics.

In conclusion, we have demonstrated that solution processed C60 could be an excellent candidate for molecular floating gate in flexible flash memories. By adopting C60 as the charge trapping layer in both pentacene and F16CuPc memory transistors, reliable p-type and n-type memory devices has been achieved. All these devices show large memory window, long retention time, good endurance properties and excellent mechanical flexibilities. More importantly, our results show that the use of molecular floating gate for the realization of new organic flash memory devices offers a promising route for the future development of advanced organic electronics.

Methods

Materials

PVP (average Mw ~25,000), C60 (99.5%), pentacene (sublimated grade) and F16CuPc (sublimated grade) were purchased from Aldrich. PET substrates were cut from commercially available PET films. All chemicals and solvents were used without further purification in the experiment.

Device fabrication

PET substrate was cleaned in an ultrasonic bath with detergent, acetone, and isopropanol prior to processing. 20 nm Ag film was thermally evaporated as the gate electrode. 40 nm Al2O3 layer was deposited using a Savannah 100 ALD system at a substrate temperature of 80°C. C60 was dissolved in 1,2,4-trichlorobenzene (TCB) (10 mg ml−1) and spin-coated at different speeds on the Al2O3 layer with subsequent annealing for 10 min at 120°C in a nitrogen environment. After that, the PVP film was fabricated by spin-coating the prepared solution (5 mg ml−1 in isopropanol). The resulted film was annealed at 100°C for 1 hour in a vacuum oven and the thickness was about 20 nm. 40 nm pentacene or 25 nm F16CuPc were thermally deposited as the semiconductor layer at a rate of 0.1 to 0.2 Å s−1. The substrate temperature was always kept at room temperature when depositing the p-type and n-type semiconductor films. Gold (Au) electrodes were employed as the source and drain contacts for both p-channel and n-channel memory transistors. 40 nm Au films were thermally evaporated through a shadow mask at a rate of 0.2 Å s−1, with a channel length to channel width ratio of 50 μm/1000 μm.

Characterization

The morphology of the C60 layer was investigated by AFM (Veeco Multi mode). The thicknesses of the deposited films were measured by an ellipsometer. The electrical characteristics of the memory transistors were measured using a Keithley 2612 source meter. All measurements were conducted in atmospheric environment with a relative humidity of 60% and a temperature of 25°C.

References

Forrest, S. R. The path to ubiquitous and low-cost organic electronic appliances on plastic. Nature 428, 911–918 (2004).

Sekitani, T. et al. Organic Nonvolatile Memory Transistors for Flexible Sensor Arrays. Science 326, 1516–1519 (2009).

Rogers, J. A., Someya, T. & Huang, Y. Materials and Mechanics for Stretchable Electronics. Science 327, 1603–1607 (2010).

Zhang, L. et al. Large-area, flexible imaging arrays constructed by light-charge organic memories. Sci. Rep. 3, 1080 (2013).

Ortiz, R. P., Facchetti, A. & Marks, T. J. High-k Organic, Inorganic, and Hybrid Dielectrics for Low-Voltage Organic Field-Effect Transistors. Chem. Rev. 110, 205–239 (2010).

Huang, X. et al. Graphene-Based Materials: Synthesis, Characterization, Properties, and Applications. Small 7, 1876–1902 (2011).

Sun, J., Zhang, B. & Katz, H. E. Materials for Printable, Transparent, and Low-Voltage Transistors. Adv. Funct. Mater. 21, 29–45 (2011).

Di, C.-a., Zhang, F. & Zhu, D. Multi-Functional Integration of Organic Field-Effect Transistors (OFETs): Advances and Perspectives. Adv. Mater. 25, 313–330 (2013).

Chang, H.-C., Lee, W.-Y., Tai, Y., Wu, K.-W. & Chen, W.-C. Improving the characteristics of an organic nano floating gate memory by a self-assembled monolayer. Nanoscale 4, 6629–6636 (2012).

Yang, Y. et al. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 3, 732 (2012).

Cho, B., Song, S., Ji, Y., Kim, T.-W. & Lee, T. Organic Resistive Memory Devices: Performance Enhancement, Integration, and Advanced Architectures. Adv. Funct. Mater. 21, 2806–2829 (2011).

Lee, J. H., Yew, S. C., Cho, J. & Kim, Y. S. Effect of redox proteins on the behavior of non-volatile memory. Chem. Commun. 48, 12008–12010 (2012).

Yu, W. J., Chae, S. H., Lee, S. Y., Duong, D. L. & Lee, Y. H. Ultra-Transparent, Flexible Single-walled Carbon Nanotube Non-volatile Memory Device with an Oxygen-decorated Graphene Electrode. Adv. Mater. 23, 1889–1893 (2011).

Burkhardt, M. et al. Concept of a Molecular Charge Storage Dielectric Layer for Organic Thin-Film Memory Transistors. Adv. Mater. 22, 2525–2528 (2010).

Tseng, C.-W., Huang, D.-C. & Tao, Y.-T. Electric Bistability Induced by Incorporating Self-Assembled Monolayers/aggregated Clusters of Azobenzene Derivatives in Pentacene-Based Thin-Film Transistors. ACS Applied Materials & Interfaces 4, 5483–5491 (2012).

Leong, W. L. et al. Towards printable organic thin film transistor based flash memory devices. J. Mater. Chem. 21, 5203–5214 (2011).

Baeg, K.-J., Noh, Y.-Y., Sirringhaus, H. & Kim, D.-Y. Controllable Shifts in Threshold Voltage of Top-Gate Polymer Field-Effect Transistors for Applications in Organic Nano Floating Gate Memory. Adv. Funct. Mater. 20, 224–230 (2010).

She, X.-J., Liu, C.-H., Zhang, J.-Y., Gao, X. & Wang, S.-D. Elucidation of ambient gas effects in organic nano-floating-gate nonvolatile memory. Appl. Phys. Lett. 102, 053303 (2013).

Kim, S.-J. & Lee, J.-S. Flexible Organic Transistor Memory Devices. Nano Lett. 10, 2884–2890 (2010).

Zhou, Y., Han, S.-T., Xu, Z.-X. & Roy, V. A. L. The strain and thermal induced tunable charging phenomenon in low power flexible memory arrays with a gold nanoparticle monolayer. Nanoscale 5, 1972–1979 (2013).

Han, S.-T. et al. Microcontact Printing of Ultrahigh Density Gold Nanoparticle Monolayer for Flexible Flash Memories. Adv. Mater. 24, 3556–3561 (2012).

Leong, W. L. et al. Non-Volatile Organic Memory Applications Enabled by In Situ Synthesis of Gold Nanoparticles in a Self-Assembled Block Copolymer. Adv. Mater. 20, 2325–2331 (2008).

Wei, Q. et al. Additive-Driven Assembly of Block Copolymer–Nanoparticle Hybrid Materials for Solution Processable Floating Gate Memory. ACS Nano 6, 1188–1194 (2012).

Paydavosi, S. et al. Performance Comparison of Different Organic Molecular Floating-Gate Memories. Nanotechnology, IEEE Transactions on 10, 594–599 (2011).

Haddon, R. C. et al. C[sub 60] thin film transistors. Appl. Phys. Lett. 67, 121–123 (1995).

Virkar, A. et al. The Role of OTS Density on Pentacene and C60 Nucleation, Thin Film Growth, and Transistor Performance. Adv. Funct. Mater. 19, 1962–1970 (2009).

Irimia-Vladu, M. et al. Vacuum-Processed Polyaniline–C60 Organic Field Effect Transistors. Adv. Mater. 20, 3887–3892 (2008).

Anthopoulos, T. D. et al. Air-Stable n-Channel Organic Transistors Based on a Soluble C84 Fullerene Derivative. Adv. Mater. 18, 1679–1684 (2006).

Brabec, C. J. et al. Polymer–Fullerene Bulk-Heterojunction Solar Cells. Adv. Mater. 22, 3839–3856 (2010).

Ryu, S.-W. et al. Fullerene-Derivative-Embedded Nanogap Field-Effect-Transistor and Its Nonvolatile Memory Application. Small 6, 1617–1621 (2010).

Chen, L.-M., Hong, Z., Li, G. & Yang, Y. Recent Progress in Polymer Solar Cells: Manipulation of Polymer:Fullerene Morphology and the Formation of Efficient Inverted Polymer Solar Cells. Adv. Mater. 21, 1434–1449 (2009).

Park, B., Choi, S., Graham, S. & Reichmanis, E. Memory and Photovoltaic Elements in Organic Field Effect Transistors with Donor/Acceptor Planar-Hetero Junction Interfaces. J. Phys. Chem. C 116, 9390–9397 (2012).

Cho, B. et al. Nonvolatile Analog Memory Transistor Based on Carbon Nanotubes and C60 Molecules. Small 9, 2283–2287 (2013).

Sung, C.-F. et al. Flexible Fullerene Field-Effect Transistors Fabricated Through Solution Processing. Adv. Mater. 21, 4845–4849 (2009).

Kaltenbrunner, M. et al. Anodized Aluminum Oxide Thin Films for Room-Temperature-Processed, Flexible, Low-Voltage Organic Non-Volatile Memory Elements with Excellent Charge Retention. Adv. Mater. 23, 4892–4896 (2011).

Zhou, Y., Han, S.-T., Xu, Z.-X. & Roy, V. A. L. Low voltage flexible nonvolatile memory with gold nanoparticles embedded in poly(methyl methacrylate). Nanotechnology 23, 344014 (2012).

Han, S.-T. et al. Layer-by-Layer-Assembled Reduced Graphene Oxide/Gold Nanoparticle Hybrid Double-Floating-Gate Structure for Low-Voltage Flexible Flash Memory. Adv. Mater. 25, 872–877 (2013).

Myung, S., Park, J., Lee, H., Kim, K. S. & Hong, S. Ambipolar Memory Devices Based on Reduced Graphene Oxide and Nanoparticles. Adv. Mater. 22, 2045–2049 (2010).

Zhou, Y. et al. Low temperature processed bilayer dielectrics for low-voltage flexible saturated load inverters. Appl. Phys. Lett. 98, 092904 (2011).

Zhou, Y., Han, S.-T., Xu, Z.-X. & Roy, V. A. L. Polymer-nanoparticle hybrid dielectrics for flexible transistors and inverters. J. Mater. Chem. 22, 4060 (2012).

Masatoshi, K. & Yasuhiko, A. Pentacene-based organic field-effect transistors. Journal of Physics: Condensed Matter 20, 184011 (2008).

Cheng, Y. C. et al. Three-dimensional band structure and bandlike mobility in oligoacene single crystals: A theoretical investigation. J. Chem. Phys. 118, 3764–3774 (2003).

Dao, T. T., Matsushima, T. & Murata, H. Organic nonvolatile memory transistors based on fullerene and an electron-trapping polymer. Org. Electron. 13, 2709–2715 (2012).

Lee, J.-S. et al. Multilevel Data Storage Memory Devices Based on the Controlled Capacitive Coupling of Trapped Electrons. Adv. Mater. 23, 2064–2068 (2011).

Singh, T. B. et al. High-Performance Ambipolar Pentacene Organic Field-Effect Transistors on Poly(vinyl alcohol) Organic Gate Dielectric. Adv. Mater. 17, 2315–2320 (2005).

Han, S.-T., Zhou, Y., Xu, Z.-X., Roy, V. A. L. & Hung, T. F. Nanoparticle size dependent threshold voltage shifts in organic memory transistors. J. Mater. Chem. 21, 14575–14580 (2011).

Rani, A., Song, J.-M., Lee, M. J. & Lee, J.-S. Reduced graphene oxide based flexible organic charge trap memory devices. Appl. Phys. Lett. 101, 233308 (2012).

Lee, P. F. & Dai, J. Y. Memory effect of an organic based trilayer structure with Au nanocrystals in an insulating polymer matrix. Nanotechnology 21, 295706 (2010).

Debucquoy, M., Rockelé, M., Genoe, J., Gelinck, G. H. & Heremans, P. Charge trapping in organic transistor memories: On the role of electrons and holes. Org. Electron. 10, 1252–1258 (2009).

Tang, Q., Li, H., Liu, Y. & Hu, W. High-Performance Air-Stable n-Type Transistors with an Asymmetrical Device Configuration Based on Organic Single-Crystalline Submicrometer/Nanometer Ribbons. J. Am. Chem. Soc. 128, 14634–14639 (2006).

Leong, W. L. et al. Micellar poly(styrene-b-4-vinylpyridine)-nanoparticle hybrid system for non-volatile organic transistor memory. J. Mater. Chem. 19, 7354–7361 (2009).

Chou, Y.-H., Lee, W.-Y. & Chen, W.-C. Self-Assembled Nanowires of Organic n-Type Semiconductor for Nonvolatile Transistor Memory Devices. Adv. Funct. Mater. 22, 4352–4359 (2012).

Seol, Y. G., Noh, H. Y., Lee, S. S., Ahn, J. H. & Lee, N.-E. Mechanically flexible low-leakage multilayer gate dielectrics for flexible organic thin film transistors. Appl. Phys. Lett. 93, 013305 (2008).

Suo, Z., Ma, E. Y., Gleskova, H. & Wagner, S. Mechanics of rollable and foldable film-on-foil electronics. Appl. Phys. Lett. 74, 1177–1179 (1999).

Acknowledgements

We acknowledge grants from City University of Hong Kong's Applied Research Grant Project no. 9667072.

Author information

Authors and Affiliations

Contributions

Y.Z. performed the experiments and wrote the paper. S.T.H., Y.Y., L.B.H., L.Z. and J.H. assisted with the experiments, discussed the results and commented on the manuscript. V.A.L.R. supervised the project and finalized the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Supplementary information

Supplementary Information

Supporting information (DOC 588 kb)

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/

About this article

Cite this article

Zhou, Y., Han, ST., Yan, Y. et al. Solution processed molecular floating gate for flexible flash memories. Sci Rep 3, 3093 (2013). https://doi.org/10.1038/srep03093

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep03093

This article is cited by

-

Photo-reactive charge trapping memory based on lanthanide complex

Scientific Reports (2015)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.