Abstract

In this paper, high-performance indium gallium oxide (IGO) thin-film transistor (TFT) with a double-gate (DG) structure was developed using an atomic layer deposition route. The device consisting of 10-nm-thick IGO channel and 2/48-nm-thick SiO2/HfO2 dielectric was designed to be suitable for a display backplane in augmented and virtual reality applications. The fabricated DG TFTs exhibit outstanding device performances with field-effect mobility (μFE) of 65.1 ± 2.3 cm2V−1 s−1, subthreshold swing of 65 ± 1 mVdec−1, and threshold voltage (VTH) of 0.42 ± 0.05 V. Both the (μFE) and SS are considerably improved by more than two-fold in the DG IGO TFTs compared to single-gate (SG) IGO TFTs. Important finding was that the DG mode of IGO TFTs exhibits the nearly temperature independent μFE variations in contrast to the SG mode which suffers from the severe remote Coulomb scattering. The rationale for this disparity is discussed in detail based on the potential distribution along the vertical direction using technology computer-aided design simulation. Furthermore, the DG IGO TFTs exhibit a greatly improved reliability with negligible VTH shift of − 0.22 V under a harsh negative bias thermal and illumination stress condition with an electric field of − 2 MVcm−1 and blue light illumination at 80 °C for 3600 s. It could be attributed to the increased electrostatic potential that results in fast re-trapping of the electrons generated by the light-induced ionization of deep level oxygen vacancy defects.

Similar content being viewed by others

Introduction

Amorphous oxide semiconductors (AOSs), such as indium–gallium–zinc–oxide (IGZO) and indium–gallium–zinc–tin–oxide (IGZTO), are widely used in display backplane technology for large-area active matrix-liquid crystal display (AMLCD) and -organic light emitting diodes (AMOLED) due to the remarkable electrical characteristics, such as reasonable field-effect mobility (µFE) of > 10 cm2V−1 s−1, ultralow off-currents of < 10−18 Aμm−1, and steep switching characteristics1,2,3,4,5,6,7,8,9,10,11,12. However, the emerging augmented and virtual reality (AR/VR) headsets requiring display backplanes with ultrahigh resolution (≥ 2000 ppi) are fabricated using Si CMOS backplanes unlike the traditional flat panel displays, such as mobile and television, where the AOS thin-film transistors (TFTs) have been successfully implemented13. To achieve such an ultrahigh resolution using the AOS TFTs, the facile integration process and architecture of submicron scale AOS TFTs should be developed on the glass substrate. Furthermore, their lower on-current (ION) compared to Si transistors makes it more challenging to utilize the AOS TFTs for AR/VR applications.

In this context, several approaches have been proposed to ensure high mobility AOS TFTs, such as heterojunction structures using quasi-two-dimensional electron gas (q2DEG)5,11, crystallization10,12, hydrogen doping7, and multi-gate architecture14,15,16,17,18,19. Amongst, adopting the multi-gate architecture, such as double-gate (DG), tri-gate and gate-all-around (GAA), is considered promising due to the outstanding current boosting ability. In practice, Mativenga et al. reported that IGZO TFTs with DG structure reveal seven times higher ION than those with single gate (SG) structure due to the bulk accumulation15. In addition to the current boosting, it was also confirmed that the DG structure greatly enhances a reliability for positive gate-bias thermal stress (PBTS) duration16. More importantly, the multi-gate structure is highly advantageous for overcoming short-channel effects (SCEs). Note that the natural length (λ) which determines the minimum gate length can be described as follows19,20:

where tch, tox, εch, εox, and N are the thickness and dielectric constants of the bulk channel and dielectric layer, and the effective gate number, respectively. As such, the λ can be reduced by increasing not only the dielectric permittivity (κ) but also the N. For these reasons, the multi-gate structure as well as the high-κ gate dielectric have been adopted for the continual scaling down of Si transistors in the semiconductor industry8. Likewise, the AOS TFT based on them should be intensively investigated for its diverse potential applications.

In this study, high-performance IGO TFTs with the DG structure were developed using atomic layer deposition (ALD). Mostly, previous AOS TFTs with the DG structure have been fabricated using the sputtering method for the channel layer deposition. However, it is unsuitable for the three-dimensional (3D) muti-gate architecture due to its poor step coverage21,22. In contrast, the ALD-derived gate/channel stack employed in this work offers excellent step coverage and thickness controllability, which is highly suitable for the 3D structure such as GAA and channel-all-around (CAA) etc23,24. The choice of 10-nm-thick IGO as a channel layer is due to its low effective electron mass and high µFE10. 2-/48-nm-thick high-κ SiO2/HfO2 dielectric films were used as a gate dielectric layer. That is, the λ was designed to be approximately 12.3 nm, which is expected to allow for a short channel length of ≤ 100 nm without the noticeable SCEs25. An important finding in this study is that the IGO TFTs with the DG structure exhibit the remote Coulomb scattering (RCS)-free transporting mechanism unlike those with the SG structure where the RCS and polar phonon scattering significantly occur26. This disparity can be explained by the concept of bulk accumulation, which was demonstrated through technology computer-aided design (TCAD) simulation. This phenomenon helps the Fermi-level (EF) reach the conduction band edge (ECB) rapidly, greatly improving both the µFE and subthreshold swing (SS) in the DG TFTs. Finally, the photo-bias stability of DG IGO TFTs was found to be superior to that of SG IGO TFTs even under negative bias thermal and illumination stress (NBTIS), which could be attributed to the increased electrostatic potential by the DG structure which greatly promotes the re-trapping of electrons originating from light illumination-induced oxygen vacancy (VO) ionization.

Methods

Preparation of semiconducting and dielectrics films

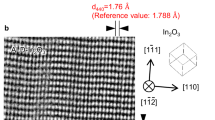

Semiconducting oxide film

10-nm-thick IGO thin-films as a channel layer were grown by plasma-enhanced ALD (PEALD) (NexusBe Co. Ltd.). The liquid metal precursors [3-(dimethylamino)propry]-dimethyl indium (DATI) and trimethyl gallium (TMG) were used as the In and Ga precursor, respectively. The DATI canister was heated to approximately 80 °C to provide a sufficient vapor pressure while the TMG canister was kept at room temperature. Each precursor was injected into the source line where high-purity Ar gas (99.999%) was used as a carrier gas for precursor delivery. O2 plasma was used as an oxidant, which was provided by applying an electric field (plasma power = 150 W) to the Ar/O2 mixed gas.

Dielectric film

Hafnium oxide (HfO2) and silicon oxide (SiO2) films were deposited by the PEALD (iSAC Research, South Korea). The metal precursors used for Hf and Si were diisopro-pylamino silane (DIPAS) and tetrakis ethylmethylamino hafnium (TEMAHf), respectively. The TEMAHf canister was heated to approximately 110 °C to provide a sufficient vapor pressure while the DIPAS canister was kept at room temperature. Likewise, each precursor was carried and purged by high-purity Ar gas.

Film characterizations

The thickness of channel and dielectric films was measured using spectroscopic ellipsometry (Ellipso Technology Co.). The chemical properties of channel and dielectric films were examined through depth-profiling of X-ray photoelectron spectroscopy (XPS) (K-Alpha + , Thermo Fisher Scientific Co.) with an X-ray source of monochromatic Al Kα at 1486.6 eV.

Device characterizations

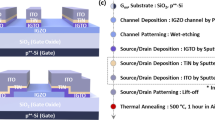

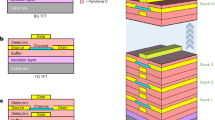

The DG IGO TFTs were fabricated on thermally grown SiO2/Si substrate. 50-nm-thick indium-in oxide (ITO) films were deposited by DC magnetron sputtering at room temperature as bottom gate (BG) electrodes. The cation composition ratio is 9:1 (In:Sn). The BG electrodes were patterned through a conventional photolithography and wet etching process. Then, 2-/48-nm-thick SiO2/HfO2 gate dielectric stacks were grown by the PEALD at 250 °C. Note that the ultrathin SiO2 acts as an interfacial stabilizer. Subsequently, 10-nm-thick IGO thin-films were deposited by PEALD at 150 °C, followed by patterning using the photolithography and wet etching process. Next, 50-nm-thick ITO was deposited as source/drain (S/D) electrodes. The S/D electrodes were patterned by the standard photolithography with wet etching process, followed by postdeposition annealing (PDA) at 400 °C in ambient air for 1 h. The fabricated TFTs have the channel width (W) and length (L) of 60 and 30 µm, respectively. To fabricated the DG TFTs, the same gate dielectric stacks were deposited onto the underlying BG TFTs and annealed at 400 °C in ambient air for 1 h. Contact holes were formed by reactive ion etching (RIE). Top gate (TG) electrodes were deposited and patterned using the same method with the BG electrodes. Finally, the fabricated TFTs were annealed at 250 °C in ambient air for 1 h. Figure 1 shows a cross-sectional device schematic, an optical top view image, and the entire fabrication process.

Results and discussion

Electrical properties of DG IGO TFTs

Electrical performances of IGO TFTs were evaluated using transfer characteristics at drain-to-source voltage (VDS) of 10 V. Note that the μFE under a saturation region was calculated using the following equation:

where ID, VGS, and Cox are the drain current, the gate voltage, and, the dielectric capacitance per unit area, respectively. The VTH and SS were determined using linear extrapolation of ID0.5 versus VGS (see Figure S1) and the equation SS = dVGS/dlog(ID), respectively. Before covering the electrical characteristics, it should be noted that TG (BG) mode means that the input gate voltage is applied to the top (bottom) gate with a floating state of bottom (top) gate. DG mode denotes that the top gate is electrically wired to the bottom gate. BG IGO TFTs with HfO2 gate dielectric (48 nm) have the reasonable µFE of 18.1 ± 1 cm2V−1 s−1, SS of 130 ± 5 mVdec−1, VTH of 0.22 ± 0.2 V and current modulation ratio (ION/OFF) of ~ 109 (Figure S2a and Table S1). It sufferes from the clock-wise hysteresis of 0.3 V, indicating the free electron carrier trapping into the HfO2 dielectric. Insertion of 2-nm-thick SiO2 interfacial layer between the IGO and HfO2 films greatly mitigates the operational hysteresis (0.05 V) in the resulting IGO TFTs (Figure S2b). Simultaneously, the µFE and SS are improved to 24.7 ± 0.7 cm2V−1 s−1 and 110 ± 5 mVdec−1, respectively, while the comparable ION/OFF is maintained (also see Table S1). TG IGO TFTs have almost the same device performances with the reasonable µFE of 25.8 ± 0.5 cm2V−1 s−1, SS of ~ 134 ± 5 mVdec−1, VTH of 0.82 ± 0.1 V and ION/OFF ratio of ~ 1010 (Fig. 2a and Table 1). Meanwhile, DG IGO TFTs exhibit significantly improved device performances with µFE of 65.2 ± 2.3 cm2V−1 s−1, SS of 65 ± 1 mVdec−1, VTH of 0.42 ± 0.05 V, and ION/OFF of ~ 1010. The enhancement in the µFE can be explained by a bulk accumulation conduction mechanism, which could occur when the depth of band bending is larger than half of the channel thickness (tch)15. The greatly improved SS in the DG mode is attributed to the increased electrostatic potential enabling the EF to rapidly rise toward the ECB, which can be experimentally demonstrated through the VGS-dependent change of activation energy (EA) (Fig. 2c): the falling rate (FR), defined as ǀΔEA/ΔVGSǀ, was extracted to 1.13 eVV−1 in the DG mode, which is twice as high as the SG mode (~ 0.6 eVV−1). This higher FR also indicates fast transition from trap-limited conduction to percolation conduction. This improved electron transport can be also observed in the output characteristics, which have a fivefold higher ID than the SG mode (Fig. 2b). The detailed output characteristics can be seen in Figure S3.

One thing we should identify is which scattering mechanism, phonon scattering or RCS, dominantly affects the electron transport in the IGO TFTs with SiO2/HfO2 gate dielectrics. The dominant scattering mode can be distinguished by the differential function for temperature (T) of Matthiessen’s rule as follows:

where α, β, and γ are the positive constants independent of T. A negative value in the 1/µFE-T curve indicates that the RCS is dominant26. The larger absolute values, the greater scattering effect. SG IGO TFTs with the 48-nm-thick HfO2 gate dielectric have the high negative slope of − 15.4 (see Figure S2b and Table S1). It indicates the dominance of RCS, which is greatly mitigated by inserting 2-nm-thick SiO2. The extracted slope values are − 7.1 ~ − 7.8 in the TG and BG IGO TFTs with the 2-/48-nm-thick SiO2/HfO2, respectively (Fig. 2d). More importantly, it is further reduced down to − 1.2 in the DG TFTs, which implies that the RCS effect revealed in the SG TFTs (either BG or TG) greatly diminishes (Fig. 2d and Table 1). That is, it could be possible that the RCS-free zone is formed and contributes to the improvements in the electrical characteristics in the DG IGO TFTs.

Chemical and dielectric properties of SiO2/HfO2

Chemical states of the SiO2/HfO2 film stack were examined through XPS analysis to investigate the possible origin of RCS in the SG IGO TFTs. Figure 3a,b show the deconvoluted O 1s XPS spectra into five bases, corresponding to oxygen bonded to fully coordinated metal ions (Hf–O: 530.0 ± 0.1 eV, Hf–O–Si: 531.5 ± 0.1 eV, Si–O: 533.0 ± 0.1 eV) and under-coordinated oxygen related to oxygen vacancies (VO: 531.0 ± 0.1 eV), and impurity oxygen species (532.0 ± 0.1 eV)27,28,29,30. In the bulk region of HfO2, the Hf–O related peak is dominant (~ 91.3%). Meanwhile, hafnium silicate (Hf–O–Si) related sub-peak becomes dominant (~ 87.0%) in the SiO2/HfO2 interfacial area, indicating that the Hf element diffuses into the ultrathin SiO2 film during thermal annealing process. The increase in the Hf–O–Si bond can be partially attributed to the strong binding nature of Si resulting in second neighbor effect30. To double-check the formation of Hf–O–Si layer, Si 2p and Hf 4f XPS spectra were also analyzed as shown in Figure S4. In the interfacial area, the main subpeak in the Si 2p spectra appears at 103 eV, which implies the Hf–O–Si formation29,31. The blue-shift of Hf 4f XPS spectra which occurs at the interface also indicates the strong bond formation of Hf–O–Si (Figure S4c)32.

The chemical properties are anticipated to affect their dielectric properties. The dielectric permittivity (κ) of SiO2, HfO2 and SiO2/HfO2 film stack was characterized by fabricating metal–insulator–metal (MIM) capacitors. The capacitances of MIM capacitors with SiO2 (8 nm) and HfO2 (48 nm) films were investigated through capacitance-frequency measurements. The κ values are obtained to 3.9 and 18.0 for the SiO2 and the HfO2, respectively (Fig. 4a). Using these values, the κ of the 2-/48-nm-thick SiO2/HfO2 can be estimated using the following equation:

where tHS, tHf, and tSi are physical thickness of SiO2/HfO2, HfO2, and SiO2, respectively, and κHS, κHf, and κSi are the corresponding films’ κ values. While the value calculated from the Eq. (4) is 15.7, the κHS value of SiO2/HfO2 extracted from the capacitance measurements is 16.5 (Fig. 4b). This disparity supports that the ultrathin SiO2 is converted to the hafnium silicate with the substantially higher permittivity (κ ~ 12)29,33 during the thermal annealing process. Reduced hysteresis and higher µFE for the IGO TFTs with the SiO2/HfO2 could be attributed to the less interfacial trap density of hafnium silicate than the HfO2 film.

Figure 5a,b show schematic band diagrams to understand the RCS effect on electron transport during SG mode and DG mode, respectively. As the VGS increases, the energy band of IGO with a number of subgap trap states (NT) bends downward. Note that the depth of band bending, which is often defined as the screening length, is inversely proportional to the concentration of NT34,35. Given that the depth of VGS-driven band bending is less than Tch, most of the free electrons exist only near the channel/gate dielectric interface (Fig. 5a). In this context, the electron transport is hampered by the RCS in the SG mode. In contrast, the free electrons can be distributed throughout the entire channel for the DG mode (Fig. 5b), because the VGS-driven band bending occurs at both sides. As a result, the RCS-free zone can be formed via the bulk accumulation in the DG IGO TFTs, improving the electron transport.

TCAD simulation and NBTIS reliability of DG IGO TFTs

Our interpretation on basis of screening length versus Tch relation was confirmed by performing the TCAD simulation. The band structure, the density gradient quantum effect model, the remote Coulomb/phonon scattering models and the subgap density of states (DOS) were incorporated into SILVACO ATLAS. More accurate subgap density of interface states (Dit) was extracted by unified subthreshold coupling factor technique36,37. Figure 6a shows comparison of Dit distributions for different driving mode of TFTs, which were modelled by using two exponential functions as follows:

where Ntail, Ndeep, kTtail and kTdeep are the density of acceptor-like tail states, the acceptor-like deep states (Ndeep), the characteristic energy of tail states, and the characteristics energy of deep states, respectively. The parameters are summarized in Table 2. It was confirmed that the DG mode possesses a lower Dit compared to to the SG mode, even if the DG TFTs have physically two interfaces. This Dit reduction can be understood as a result reflected by the RCS-free zone as discussed earlier. Figure 6b,c show the energy level and the current density depending on the driving mode. It was confirmed that the EF is closely located to the ECB throughout the entire channel due to the bulk accumulation in the DG mode unlike the SG mode. As a result, the drain-current density in the DG mode is significantly higher than the SG modes, which also can be seen in Fig. 6d–f that show the cross-sectional drain-current density contours. Overall, these results demonstrate that the electron transport is greatly improved by the bulk region, the RCS-free zone, in the DG mode, which affirms the relatively minor influence of interfacial effects compared to the SG mode. Note that the simulated transfer characteristics for each driving mode is well matched with the experimental results (Figure S5). The detailed parameters of the materials and structures used in TCAD are summarized in Table S2.

Finally, negative gate bias illumination stress (NBIS) reliability was investigated for the different driving modes under the external stress conditions with an electric field of − 2 MVcm−1 (VGS − VTH = − 10 V) and the green light illumination of 0.3 mWcm−2 (λ = 533 nm, 2.3 eV). The representative stress time-dependent transfer characteristics during the NBIS duration can be seen in Figure S6. It was confirmed that there are parallel shifts without involving the stretch-out of subthreshold ID region regardless of the driving mode, suggesting that there is no noticeable defect creation during the NBIS duration. More importantly, the VTH shift (ΔVTH) is remarkably reduced in the DG mode (Fig. 7a). While the BG (TG) IGO TFTs show an inferior NBIS instability with the ΔVTH of − 4.5 (− 3.6) V, respectively, after 3600 s, the DG TFTs exhibit the negligible ΔVTH. Furthermore, the DG IGO TFTs reveal the outstanding reliability with the ΔVTH of − 0.22 V even under the NBTIS with the blue light illumination of 64 µWcm−2 (λ = 463 nm, 2.7 eV) at 80 ℃ (Fig. 7b). These highly improved reliabilities could be related to the electron generation by the light illumination-driven transition from deep-level neutral VO defects to VO2+ states38,39,40. In detail, the photo-induced VO2+ defects and free electron carriers are separated by the negative gate bias during the NBIS duration. In the SG mode, the photo electrons are repelled in the direction opposite to the biased gate electrode and accumulated. As a result, they greatly increase the electron concentration of IGO (Fig. 7c), deteriorating the NBIS reliability. Meanwhile, in the DG mode, the photo electrons cannot be accumulated at one side, which results in significant shrinkage of the electron transverse path, leading to fast re-trapping (Fig. 7d). For this reason, the electron concentration does not increase in the DG mode, showing the high reliabilities even under the light illumination.

It is noteworthy that the electrical characteristics of DG IGO TFTs obtained in this study is comparable to state-of-the-art DG AOS TFTs. The µFE and SS values of DG AOS TFTs with different gate dielectric materials are summarized in benchmarking graphs (Fig. 8)40,41,42,43,44,45,46,47,48,49. These promising performances of fabricated DG IGO TFTs should be attributed to (1) the usage of a high-quality ALD-derived IGO and high-κ HfO2 dielectric films, (2) RCS-free device design on basis of bulk accumulation mode.

Conclusion

In this study, high-performance DG IGO TFTs were fabricated using PEALD. The SG IGO TFTs with 2-/48-nm-thick SiO2/HfO2 exhibited the moderate device performances with µFE of 24.7 cm2V−1 s−1, SS of 110 mVdec−1, and ION/OFF of ~ 109. Importantly, the DG IGO TFTs revealed greatly improved device performances with µFE of 65.2 ± 2.3 cm2V−1 s−1, SS of 65 ± 1 mVdec−1, and ION/OFF of ~ 1010. This disparity can originate from the bulk accumulation, the formation of RCS-free zone, because the electron transport via the RCS-free zone helps the EF reach the ECB rapidly. This elucidation was supported through TCAD simulation. Finally, it was confirmed that the DG IGO TFTs show the photo-bias stability much superior to the SG IGO TFTs, which can be attributed to the fast re-trapping of the photo electrons released from deep-level VO defects. It should be emphasized that even if this study focuses on effects of the DG structure on the IGO TFTs, the obtained results can be applicable to more advanced multi-gate AOS TFTs.

Data availability

The datasets used and/or analyzed during the current study available from the corresponding author on reasonable request. Correspondence and requests for materials should be addressed to J.K.J. (email: jkjeong@hanyang.ac.kr).

References

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492. https://doi.org/10.1038/nature03090 (2004).

Kim, B. K. et al. Polycrystalline indium gallium tin oxide thin-film transistors with high mobility exceeding 100 cm2/Vs. IEEE Electron Device Lett. 42, 347–350. https://doi.org/10.1109/LED.2021.3055940 (2021).

Choi, C. H. et al. High-performance indium gallium tin oxide transistors with an Al2O3 gate dielectric deposited by atomic layer deposition at a low temperature of 150 °C: Roles of hydrogen and excess oxygen in the Al2O3 dielectric film. ACS Appl. Mater. Interfaces 13, 28451–28461. https://doi.org/10.1021/acsami.1c04210 (2021).

Cho, M. H., Choi, C. H., Seul, H. J., Cho, H. C. & Jeong, J. K. Achieving a low-voltage, high-mobility IGZO transistor through an ALD-derived bilayer channel and a hafnia-based gate dielectric. ACS Appl. Mater. Interfaces 13, 16628–16640. https://doi.org/10.1021/acsami.0c22677 (2021).

Seul, H. J. et al. Improvement in carrier mobility through band-gap engineering in atomic-layer-deposited In-Ga-Zn-O stacks. J. Alloys Compd. 903, 163876. https://doi.org/10.1016/j.jallcom.2022.163876 (2022).

Kim, M. J., Park, H. J., Yoo, S., Cho, M. H. & Jeong, J. K. Effect of channel thickness on performance of ultrathin body IGZO field-effect transistors. IEEE Trans. Electron Devices 69, 2409–2416. https://doi.org/10.1109/TED.2022.3156961 (2022).

Lee, J. et al. Hydrogen-doping-enabled boosting of the carrier mobility and stability in amorphous IGZTO transistors. ACS Appl. Mater. Interfaces 14, 57016–57027. https://doi.org/10.1021/acsami.2c18094 (2022).

Kim, T. et al. Progress, challenges, and opportunities in oxide semiconductor devices: A key building block for application from display backplanes to 3D integrated semiconductor chips. Adv. Mater. https://doi.org/10.1002/adma.202204663 (2023).

Cho, M. H. et al. Comparative study of atomic layer deposited indium-based oxide transistors with a fermi energy level-engineered heterojunction structure channel through a cation combinatorial approach. ACS Appl. Mater. Interfaces 14, 18646–18661. https://doi.org/10.1021/acsami.1c23889 (2022).

Park, H. Y. et al. Improvement in performance of indium gallium oxide thin film transistor via oxygen mediated crystallization at a low temperature of 200 °C. Ceram. Int. 48, 12806–12812. https://doi.org/10.1016/j.ceramint.2022.01.151 (2022).

Cho, M. H., Choi, C. H. & Jeong, J. K. High-performance indium-based oxide transistors with multiple channels through nanolaminate structure fabricated by plasma-enhanced atomic layer deposition. ACS Appl. Mater. Interfaces 15, 19137–19151. https://doi.org/10.1021/acsami.3c00038 (2023).

Kim, G.-B. et al. High mobility IZTO thin-film transistors based on spinel phase formation at low temperature through a catalytic chemical reaction. Small Methods 7, 2201522. https://doi.org/10.1002/smtd.202201522 (2023).

Na, J.-S., Hong, S.-K. & Kwong, O.-K. A 4410-ppi resolution pixel circuit for high luminance uniformity of OLEDoS microdisplays. IEEE J. Electron Devices Soc. 7, 1026–1032. https://doi.org/10.1109/JEDS.2019.2935766 (2019).

Chen, T.-L. et al. Enhanced current drive of double-gate a-IGZO thin-film transistors. IEEE Electron Device Lett. 34, 417–419. https://doi.org/10.1109/LED.2013.2238884 (2013).

Mativenga, M., An, S. & Jang, J. Bulk accumulation a-IGZO TFT for high current and turn-on voltage uniformity. IEEE Electron Device Lett. 34, 1533–1535. https://doi.org/10.1109/LED.2013.2284599 (2013).

Park, J. et al. Effect of positive bias stress on the back-gate voltage-modulated threshold voltage in double-gate amorphous InGaZnO thin-film transistors. IEEE Electron Device Lett. 34, 1878–1881. https://doi.org/10.1109/LED.2022.3206340 (2022).

More Moore-International Roadmap for Devices and Systems (IRDS), Available: https://irds.ieee.org/images/files/pdf/2022/2022IRDS_MM.pdf (2022).

Herrera, F. Á., Mattausch, M., Iizuka, T., Kilkuchihara, H., Hirano, Y. & Mattausch, H. J. Modeling of short-channel effect on multi-gate MOSFETs for circuit simulation. In 2020 International Symposium on Devices, Circuits and Systems (ISDCS), 1−4. https://doi.org/10.1109/ISDCS49393.2020.9263000 (2020).

Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316. https://doi.org/10.1038/nature10676 (2011).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53. https://doi.org/10.1038/s41586-021-03339-z (2021).

Cho, M. H. et al. Comparative study on performance of IGZO transistors with sputtered and atomic layer deposited channel layer. IEEE Trans. Electron Devices 66, 1783–1788. https://doi.org/10.1109/TED.2019.2899586 (2019).

Kim, H.-R. et al. Comparative studies on vertical-channel charge-trap memory thin-film transistors using In-Ga-Zn-O active channels deposited by sputtering and atomic layer deposition. Nanotechnology 31, 435702. https://doi.org/10.1088/1361-6528/aba46e (2020).

Duan, X. et al. Novel VERTICAL CHANNEL-ALL-AROUND (CAA) In-Ga-Zn-O FET for 2T0C-DRAM with high density beyond 4F2 by monolithic stacking. IEEE Trans. Electron Devices 69, 2196–2202. https://doi.org/10.1109/TED.2022.3154693 (2022).

Bai, Z. et al. Low frequency noise of channel-all-around (CAA) InGaZnO field effect transistors. IEEE Electron Device Lett. 43, 2117–2120. https://doi.org/10.1109/LED.2022.3216609 (2022).

Yan, R.-H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710. https://doi.org/10.1109/16.141237 (1992).

Park, J.-S., Jeong, J. K., Mo, Y. G. & Kim, S. Impact of high-κ TiOx dielectric on device performance of indium-gallium-zinc oxide transistors. Appl. Phys. Lett. 94, 042105. https://doi.org/10.1063/1.3075612 (2009).

Zhang, Y. et al. Aqueous-solution-driven HfGdOx gate dielectrics for low-voltage-operated a-InGaZnO transistors and inverter circuits. J. Mater. Sci. Technol. 50, 1–12. https://doi.org/10.1016/j.jmst.2020.03.007 (2020).

Avis, C., Kim, Y. G. & Jang, J. Solution processed hafnium oxide as a gate dielectric for low-voltage oxide thin-film transistors. J. Mater. Chem. 22, 17415–17420. https://doi.org/10.1039/c2jm33054g (2012).

Lee, S., Yun, D.-J., Rhee, S.-W. & Yong, J. Atomic layer deposition of Hafnium silicate film for high mobility pentacene thin film transistor applications. J. Mater. Chem. 19, 6857–6864. https://doi.org/10.1039/b908216f (2009).

Wang, H., Hg, K. L., Zhan, N., Poon, M. C. & Kok, C. W. Interface bonding structure of hafnium oxide prepared by direct sputtering of hafnium in oxygen. J. Vac. Sci. Technol. B 22, 1094–1100. https://doi.org/10.1116/1.1740764 (2004).

Torchynska, T., Macotela, L. G. V., Khomenkova, L., Gourbilleau, F. & Rojas, L. L. Annealing impact on emission and phase varying of Nd-doped Si-rich-HfO2 films prepared by RF magnetron sputtering. J. Mater. Sci. Mater. Electron. 31, 4587–4594. https://doi.org/10.1007/s10854-020-03010-9 (2020).

Wang, H. et al. Study of reactions between HfO2 and Si in thin films with precise identification of chemical states by XPS. Appl. Surf. Sci. 257, 3440–3445. https://doi.org/10.1016/j.apsusc.2010.11.042 (2011).

Lee, J.-C., Oh, S.-J., Cho, M., Hwang, C. S. & Jung, R. Chemical structure of the interface in ultrathin HfO2/Si films. Appl. Phys. Lett. 84, 1305–1307. https://doi.org/10.1063/1.1645984 (2004).

Park, J.-S., Jeong, J. K., Chung, H.-J., Mo, Y.-G. & Kim, H. D. Electronic transport properties of amorphous indium-gallium-zinc oxide semiconductor upon exposure to water. Appl. Phys. Lett. 92, 072104. https://doi.org/10.1063/1.2838380 (2008).

Zhou, X. et al. Oxygen adsorption effect of amorphous InGaZnO thin-film transistors. IEEE Electron Device Lett. 38, 465–468. https://doi.org/10.1109/LED.2017.2666881 (2017).

Jun, S. et al. Unified subthreshold coupling factor technique for surface potential and subgap density-of-states in amorphous thin film transistors. IEEE Electron Device Lett. 34, 641–643. https://doi.org/10.1109/LED.2013.2248116 (2013).

Lee, S., Nathan, A., Ye, Y., Guo, Y. & Robertson, J. Localized tatil states and electron mobility in amorphous ZnON thin film transistors. Sci. Rep. 5, 13467. https://doi.org/10.1038/srep13467 (2015).

Ji, K. H. et al. Comprehensive studies of the degradation mechanism in amorphous InGaZnO transistors by the negative bias illumination stress. Microelectron. Eng. 88, 1412–1416. https://doi.org/10.1016/j.mee.2011.03.069 (2011).

Song, J. H., On, N., Du, B., Kim, H. D. & Jeong, J. K. Dynamics of threshold voltage instability in IGZO TFTs: Impact of high pressurized oxygen treatment on the activation energy barrier. IEEE Trans. Electron Devices 63, 1054–1058. https://doi.org/10.1109/TED.2015.2511883 (2016).

Mativenga, M., Haque, F., Billah, M. M. & Um, J. G. Origin of light instability in amorphous IGZO thin-film transistors and its suppression. Sci. Rep. 11, 14618. https://doi.org/10.1038/s41598-021-94078-8 (2021).

Lee, J. et al. High field effect mobility, amorphous In-Ga-Sn-O thin-film transistor with no effect of negative bias illumination stress. IEEE Electron Device Lett. 40, 1443–1446. https://doi.org/10.1109/LED.2019.2931089 (2019).

Chakraborty, W., Ye, H., Grisafe, B., Lightcap, I. & Datta, S. Low temperature budget (<250 ℃) dual-gate amorphous indium tungsten oxide (IWO) thin-film transistor for monolithic 3−D integration. IEEE Trans. Electron Devices 67, 5336–5342. https://doi.org/10.1109/TED.2020.3034063 (2020).

Rabbi, M. H. et al. Extremely stable dual gate coplanar amorphous InGaZnO thin film transistor with split active layer by N2O annealing. IEEE Electron Device Lett. 41, 1782–1785. https://doi.org/10.1109/LED.2020.3034119 (2020).

Her, J., Min, W. K., Shin, C. S., Jeong, H. & Park, J. K. A new pixel circuit with selectively synchronized dual-gated IGZTO TFTs for AMOLED displays. IEEE Trans. Electron Devices 69, 5568–5573. https://doi.org/10.1109/TED.2022.3201059 (2022).

Lu, W., Zhu, Z., Chen, K., Liu, M., Kang, B.-M., Duan, X., Niu, J., Liao, F., Dan, W., Wu, X.-S., Son, J., Xiao, D.-Y., Wang, G.-L., Yoo, A., Cao, K.-Y., Geng, D., Lu, N., Yang, G., Zhao, C., Li, L. & Liu, M. First demonstration of dual-gate IGZO 2T0C DRAM with novel read operation, one bit line in single cell, ION = 1500 µA/µm@VDS = 1 V and retention time>300s. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), 26.4.1−26.4.4. https://doi.org/10.1109/IEDM45625.2022.10019488 (2022).

Liu, W.-S., Hsu, C.-H., Jiang, Y., Lai, Y.-C. & Kuo, H.-C. Improving device characteristics of dual-gate IGZO thin-film transistors with Ar-O2 mixed plasma treatment and rapid thermal annealing. Membranes 12, 1–15. https://doi.org/10.3390/membranes12010049 (2022).

Priyadarshi, S. et al. High-performance dual gate amorphous InGaZnO thin film transistor with top gate to drain offset. IEEE Electron Device Lett. 43, 56–59. https://doi.org/10.1109/LED.2021.3128940 (2022).

Yang, J., Park, H., Kim, B., Cho, Y.-H. & Park, S.-H.K. Active-matrix micro-light-emitting diode displays driven by monolithically integrated dual-gate oxide thin-film transistors. J. Mater. Chem. C 10, 9699–9706. https://doi.org/10.1039/d2tc01905a (2022).

Kong, H. et al. Effect of dual gating on electrical characteristics of amorphous indium–tin–gallium–zinc-oxide TFTs. Electron. Lett. 59, 1–3. https://doi.org/10.1049/ell2.12890 (2023).

Acknowledgements

This work was supported by the National Research Foundation (NRF) Grant funded by the Korean government (NRF-2022M3H4A6A01035636, 2022M3H4A1A04068923) and the Technology Innovation Program (1415178807, Development of Industrial Intelligent Technology for Manufacturing, Process, and Logistics) funded By the Ministry of Trade, Industry & Energy (MOTIE, Korea). This work was also supported by Institute of Information & communications Technology Planning & Evaluation (IITP) under the artificial intelligence semiconductor support program to nurture the best talents (IITP-2023-RS-2023-00253914) grant funded by the Korea government.

Author information

Authors and Affiliations

Contributions

C.H.C. and J.K.J. designed this work. C.H.C., T.K. and J.K.J. wrote the main text. C.H.C. fabricated and characterized the devices. M.J.K., G.-B.K. and J. E. O. assisted the preparation of TCAD simulation and oxide films by PEALD. All author discussed the results and commented on the manuscript. The project was supervised by J.K.J.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Choi, C.H., Kim, T., Kim, M.J. et al. Double-gate structure enabling remote Coulomb scattering-free transport in atomic-layer-deposited IGO thin-film transistors with HfO2 gate dielectric through insertion of SiO2 interlayer. Sci Rep 14, 7623 (2024). https://doi.org/10.1038/s41598-024-58330-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-58330-1

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.