Abstract

This letter presents a new single-stage common ground type nine-level (9L) switched-capacitor inverter topology with single-phase operation. The primary objective of this topology is to reduce the leakage current, voltage boosting, and maintain the voltage across the switched capacitors. The output voltage (vo) can be boosted up to two times the input voltage (vin). The various modes of operations are explained in detail, and the simulation results are provided to illustrate the effectiveness of the proposed topology. Next, the experimental results are obtained from a 500 W prototype setup and tested under different scenarios such as load variations, input voltage, and modulation index. Both simulation and experimental results have a good agreement regarding efficiency and performance. Finally, a detailed comparative study is performed with other recent 9L switched-capacitor inverters to prove the merits of the proposed topology.

Similar content being viewed by others

Introduction

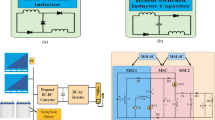

In recent years, the switched capacitor inverters (SCIs) have been paid more attention due to their inherent voltage boosting capability and higher number of output voltage levels. Such inverters are more suitable for medium voltage applications, including distributed power generation systems1. The remarkable advantages of SCI topologies are: (1) lower number of active components, (2) floating capacitor (FC) voltages are either balanced by additional sensor/circuits or inherently balanced (so-called self-balanced), and (3) voltage boosting ability which further reduces the size or eliminates the front dc/dc converter for renewable energy applications. The two-level SCI has challenges such as high total harmonics distortion and large size of LC filter. To overcome these issues, the combination of switched-capacitor and multilevel inverter (SCMLI) is introduced in1,2,3 as multilevel inverters are very popular due to their reduced switch stress, better harmonic performance, lower losses, and reduced filter requirement2,3,4,5,6,7,8,9,10,11,12,13. A new generalized structure SCMLI topology with a higher number of output voltage levels is proposed in2,3. These topologies are suitable for applications with strict harmonic requirements. Still, the total switch count is high with a voltage gain of 1:n (vin:vout), and each capacitor voltage rating is equal to vin. There are several SCMLI topologies in the literature with a number of output voltage levels ranging from 4-level to generalized n-level. However, the number of output voltage levels in this paper is 9L, as found in4,5,6,7,8,9,10. These topologies have a common output voltage gain of 1:2 and need two floating capacitors (FCs) to generate a 9L output voltage waveform. However, each topology has its pros and cons. For example, more components are needed in4, whereas authors in5 have successfully reduced the switch count, and both the topologies produce the voltage gain of 1:2.

Another topology, which needs eight unidirectional switches and two RB-IGBTs, is proposed in6, and eight switches, two diodes, and three capacitors are used in7. A new topology with seven unidirectional switches, two diodes, and capacitors is used in8, but this topology also needs additional two RB-IGBT switches. However, in these topologies, the voltage gain is two, and most of the switch voltage rating is equal to the maximum output voltage. To reduce the voltage stress on the switches, two new topologies are presented in9,10 with voltage stress of vin, but the number of the semiconductor device is considerably high. Due to the leakage current, none of those mentioned above topologies are suitable for transformerless solar PV applications.

In recent years significant research efforts have been given in the development of transformerless inverter (TLI) topologies for photovoltaic application due to the elimination of leakage current11,12,13,14. A new five-level transformerless inverter with a reduced switch count is presented in11. However, this topology has a large filter requirement due to lower output voltage levels. To address this issue, a 9-level (9L) TLI is proposed in12 but does not have voltage gain, and the number of ON state switches is high at each level. Moreover, this topology's input voltage requirement is significantly higher due to reduced dc-bus utilization. Another novel 9L-TLI topology is proposed in13, which has full dc-bus utilization. The buck-boost converters are integrated with a series connection of four dc-link capacitors to achieve the nine-level output voltage. However, the dc-link capacitors are not balanced, leading to unsymmetrical stepped waveforms at the load. In this reference, it may be noted that the common connection between the load side ground terminal and the source side negative terminal eliminates the leakage current and is called the common ground connection14. Recent 9L SCMLI topologies with boosting are presented in15,16,17. However, they fail to reduce leakage current. Moreover, the topologies presented in18,19,20 share a common ground with eradicating leakage current. The18 presents a new common ground in the three-level inverter. The capacitor acts as a virtual dc source in the negative half cycle. If the capacitor fails, the topology will not generate the negative half cycle, and the entire system will fail. However, if any capacitor fails in the proposed topology, the magnitude of the output voltage and step size will be reduced, but the operation will continue.

Motivated by the above discussion, this paper presents a new common ground type (CGT) inverter with a reduced total power component. The proposed topology is an improved version of10. The proposed topology successfully reduces the number of power components, achieving a low voltage rating of FCs and low power loss with a maximum of ~ 97.2% of efficiency. It is important to note that the proposed topology reduces leakage current due to common grounding, which is missing in the existing 9L SCMLI inverter topologies2,3,4,5,6,7,8,9,10,11,12,13.

Proposed TL-9L inverter topology

Description of proposed topology

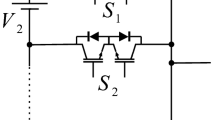

A detailed explanation of the circuit diagram and the modes of operations are discussed for the proposed TL-9L inverter. A detailed explanation of the circuit diagram and the modes of operations are discussed for the proposed CGT-T9L inverter. Figure 1 shows the circuit diagram of the proposed 9L inverter topology. It can be observed from Fig. 1 that it has a single dc source with three FCs (C1, C2, and C3) rated at voltage vin /2 (C2, and C3) and vin, (C1). The proposed topology uses ten switches (S1, S2, S3, S4, S5, S6, S7, S8, S9, and S10) and three diodes (D1, D2, and Da). The capacitor C1 is connected in such a way that it gets charged when S1 is turned ON. The series-connected capacitors C2 and C3 are connected with switches S7, S8, and S9/S10. The switch pairs S7, and S8 should not be turned ON simultaneously to avoid the short circuit of the series-connected capacitor branch. Likewise, the switch pairs (S1, S2), (S3, S6, S4), and (S3, S5, S4) should not be turned ON simultaneously. The midpoint of C2 and C3 is connected with S9 and S10. It may be observed that the switches S7, S8, and S9/S10 form a T-type leg which also serves as one of the terminals of the load, i.e., node a. The load terminal is directly connected to the negative terminal of the dc source i.e., node n.

Modes of operation with pulse generation scheme

Figure 2a–i shows the sub-circuit diagram of the various modes of operation, showing the path of the charging current and load current. The capacitor C1 gets charged in all the positive levels and the first level of the negative half cycle. A few modes are explained below to understand the working principle of the whole topology.

In Fig. 2, three different color lines are shown, which illustrate the current path of the proposed circuit diagram during (1) the charging of the capacitors, (2) the current path for unity power factor, and (3) the current path in either lagging or leading power factor.

Mode + vin/2 In this mode, the FC C1 and the series-connected capacitor branch (C2 and C3) are charged simultaneously up to the vin. The switch S9/S10 is turned ON and the load voltage is equal to + vin/2, as shown in Fig. 2a.

-

The closed path for charging C1-C3 is shown as: \(v_{in} \to S_{1} \to \uparrow C_{1} \to S_{3} \to D_{1} \uparrow C_{2} \uparrow C_{3} \to D_{2} \to S_{4} \to D_{a} \to v_{in}\)

-

The closed current path for load is shown as: \(v_{in} \to S_{1} \to S_{3} \to D_{1} \to D_{2} \to S_{9} S_{10} \to Load \to v_{in}\)

Mode + vin In this mode, all the FCs charge simultaneously, and the load voltage equals + vin, as shown in Fig. 2b.

-

The closed path for charging of C1-C3 is shown as: \(v_{in} \to S_{1} \to \uparrow C_{1} \to S_{3} \to D_{1} \uparrow C_{2} \uparrow C_{3} \to D_{2} \to S_{4} \to D_{a} \to v_{in}\)

-

The closed current path for load is shown as: \(v_{in} \to S_{1} \to S_{3} \to D_{1} \to D_{2} \to S_{7} \to Load \to v_{in}\)

Mode + 3vin/2 In this mode, FC C3 discharges, but FC C1 charges. The load voltage is equal to + 3 vin/2, as shown in Fig. 2c.

-

The closed current path for charging of C1 is shown as: \(v_{in} \to \uparrow C_{1} \to D_{a} \to v_{in}\)

-

The closed current path for load is shown as: \(v_{in} \to S_{1} \to S_{3} \downarrow C_{3} \to S_{9} S_{10} \to v_{in}\)

Mode + 2vin In this mode, the FC C2 and C3 get discharged, and the load voltage is equal to + 2 vin, as shown in Fig. 2d.

-

The closed current path for charging of C1 is shown as: \(v_{in} \to \uparrow C_{1} \to D_{a} \to v_{in}\)

-

The closed current path for load is shown below: \(v_{in} \to S_{1} \to S_{3} \downarrow C_{3} \to S_{7} \to v_{in}\)

Mode + 0vin During this mode, all the FCs are charging, and the load voltage is equal to + 0 vin, as shown in Fig. 2e.

-

The closed path for charging C1–C3 is shown below: \(v_{in} \to S_{1} \to \uparrow C_{1} \to S_{3} \to D_{1} \uparrow C_{2} \uparrow C_{3} \to D_{2} \to S_{4} \to D_{a} \to v_{in}\)

The explanation of the various modes for the negative half cycle is similar, and the corresponding turned-on switches for each voltage level and charging and discharging state of the capacitors are given in Table 1. Further, as shown in Fig. 2, the proposed topology can operate in both real and reactive power. The conventional level-shifted SPWM (LSPWM), as shown in Fig. 3a, and the PWM logic functions, as shown in Fig. 3b, are used in the proposed topology to generate the 9L output voltage. The reference voltage (Vref) is compared with the triangular carrier waveform (Carr 1–Carr 8) and produces the pulses. The simple logic functions are used to generate the desired pulses for the switches. Since the maximum output voltage of the proposed inverter is two times higher than the vin, it generates the 9L stepped voltage waveform with each step of vin/2.

Determination of capacitance and power analysis

Determination of capacitance

The proposed topology employs three capacitors, labeled C1, C2, and C3. These capacitors play a vital role in boosting the input voltage. Thus, the output voltage is equal to 2 vin, and each step has a voltage of vin/2. The switching capacitor C1 is charged to its maximum input voltage, while the flying capacitors C2 and C3 are charged to 50% of the input voltage. Consequently, the capacitance value selection of these capacitors is more critical to achieving the 9L output voltage. In addition, it affects the inverter's ripple loss, size, and total cost. As seen in Fig. 3a, the switched capacitor C1’s capacitance value was calculated using the longest discharging time of capacitors. The capacitances are estimated by using a maximum of 10% capacitor ripple voltage.

The capacitor C1 is discharged during all the negative levels (− 0.5 vin, − vin, − 1.5 vin, − 2 vin) as shown in Fig. 3a. The time duration t is estimated as follows,where 2π is the output voltage waveform's period. The predicted charge on the capacitor C1 under resistive load for the LDC period is:

The current load value of the proposed topology for the purely resistive load can be expressed as,

From Eqs. (3) and (4), the charge on the capacitor C1 is estimated as,

The optimal capacitance value of capacitors C1 when the load is entirely resistive may be calculated as follows:

When the load is resistive-inductive (RL), the load current is expressed as \(I_{O} (t) = I_{mx} \sin (wt - \psi ) \,\).

At resistive-inductive (RL) loading conditions, the charge on capacitor C1 is approximated as follows:

The optimal capacitance value of capacitors C1 under resistive-inductive (RL) loading may be calculated as follows:

The size of flying capacitors C2 and C3 are estimated as,

where Imx is the maximum load current, fs is the switching frequency, and ΔVC is the voltage ripple.

Power loss analysis

Switching, conduction, driver circuit, and ripple loss are used to compute inverter power loss19. IGBT switching loss occurs when its anti-parallel diode is off (9)

Switching loss during the IGBT is OFF, and Diode is ON as expressed in (10)

The conduction losses are always high due to the long conduction period, and this can be calculated by using (11)

where ‘VCE’ is the collector and emitter voltage of IGBT, i.e. blocking voltage, 'VF' forward voltage of the diode, 'Io' is the load current, and 'tr' rise time, td(ON) and td(OFF) is turn ON, and OFFF delay and 'tf' is fall time of an IGBT. 'RCE(on)' is the on-state resistance of an IGBT, 'd' is the duty cycle of the IGBT, and 'Ts' is the switching period.

Further, the gate driver loss is very small and negligible. However, the calculation of the gate driver loss is given in (12)

where the 'QB' is charge at the base terminal, 'VBE' biasing voltage to the IGBTs, and fs switching frequency. The energy loss across the capacitor during the charging is expressed as \(E_{Cap} = \left( {{1 \mathord{\left/ {\vphantom {1 2}} \right. \kern-\nulldelimiterspace} 2}} \right)\left\{ {C \times \left( {\Delta V} \right)^{2} } \right\}\). C2 and C3 charge twice per half-cycle, whereas C1 charges four times. Average capacitor cycle loss is \(E_{Rip} = 2f_{o} (E_{Cap} )\). Thus, the total across the capacitors in the complete cycle is \(E_{Rip} = 2f_{o} (E_{C2} + E_{C3} ) + 4f_{o} (E_{C1} )\).

Results and discussion

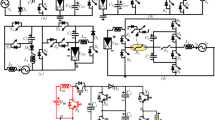

The performance of the proposed topology is validated in MATLAB / Simulink software tool and a laboratory-built hardware prototype. The input DC source voltage is kept at 100 V. The voltage and capacitance value of FC C1 is respectively 100 V and 2700 µF. Similarly, the voltage and capacitance values of FCs C2 and C3 are 50 V/2700 µF, respectively. The capacitance values are designed per the process given in14, where the maximum voltage ripple is chosen as less than 5% with a 2.5 kHz switching frequency. The two resistive-inductive loads are used with R = 100 Ω, L = 50 mH, and R = 50 Ω, L = 100 mH. The output voltage and current waveform with these two loads are given in Fig. 4a. The corresponding capacitor ripple voltage is given in Fig. 4b for C2 and C3 and Fig. 4c for C1. Further, the simulation result of each FCs current is shown in Fig. 5a–d, and the loop inductor current is shown in Fig. 5d.

For experimental validation for 500 W prototype model was rigged up with the DC Source taken from a three-phase rectifier (600 V, 100A), the capacitors C1-2200 µF/100 V (ALS30A222DA100) and C2, C3-1700 µF/50 V (SLPX332M050C1P3). A little higher value of capacitance is chosen due to practical considerations like suppressing the effect of unnecessary parasitic wiring inductance. Here, the power electronics devices are chosen as IGBTs (600 V, 73 A) SKM75GB63D from Semikron. The diode (200 V, 30 A) HER3003 from DC Components is used where only a single diode is used in the proposed topology as given in Table 2. A notable drawback of the switched capacitor circuits is the high inrush current. In this paper, a current limiting inductor is used to reduce the inrush current. The inductor size is small and can limit the inrush current to an allowable value14. The mathematical expression for the current limiting inductor is given in (13).

where the il,in is the maximum inrush current or loop current during the charging of the FCs. Lin is inductance value and Cf is FC capacitance value. ic is charging current i.e. FC current which is usually four to five times higher than the load current. For the suppression of inrush current the loop inductor value is chosen as ~ 20 A for Ll,in = 40 μH based on (1). The experimentally obtained output voltage and current waveforms for R = 50 Ω, L = 100 mH (peak current (Ipeak) = ∼ 3.3 A) with power factor of 0.85 and R = 100 Ω, L = 50 mH (Ipeak = ∼ 1.9 A) with power factor of 0.99 is presented in Fig. 6a,b, respectively, and they confirm that the peak of the output voltage is 200 V which is two times higher than the input voltage. Most of the loads are dynamic behavior, so it is necessary to evaluate the proposed topology for different loading condition.

Figure 7a shows the continuous load change from R = 100 Ω to 55 Ω with constant L = 50 mH, and in Fig. 7b, the capacitor current for load change is presented. As explained earlier, in SCMLI topologies, the inrush current is a big challenge addressed in the proposed topology using the loop inductor. The current flowing through the FCs is presented in Fig. 7b.

It can be observed from Fig. 7b that the inrush current or the FC current is significantly reduced in the proposed topology but the inrush current is a little higher than the calculated value. However, the inductor (Lin) reduced the maximum inrush current four times less than the without inductor current. In order to show the performance of the proposed topology during modulation, index variations are tested, and the corresponding waveform is shown in Fig. 8. Further, the various experimental results for step input change (80–100 V) with FCs voltages are shown in Fig. 9. The blocking voltage and current of switches (S3 and S4) as shown in Fig. 10a, and capacitor voltage for load changing is presented in Fig. 10b. The voltage stress on the switches is equal to the vin, whereas other topologies presented in Table 3 show the voltage stress is two and four times higher than the vin. Most of the SCMLI topology with boosting ability circuits have higher current stress than the conventional inverter. It can be limited by inserting the small inductor in the capacitor charging path, but it is worth mentioning that the voltage boosting ability without any additional circuit is achieved. The comparison of the proposed TL-9L inverter topology with other recent 9L SCMLIs is presented in Table 3. It can be observed that the number of power components count is considerably low in the TL-9L inverter. However, it may also be observed from Table 2 that a few existing topologies have fewer switches compared to the proposed topology.

However, the proposed topology is addressed the leakage current problem entirely as it is of common ground type and these features are not available in any other 9L inverters presented in the given literature. Apart from this, the proposed topology can address the inrush current issue despite being a boost-capable switched capacitor type. It may be noted that none of the existing switched capacitor type 9L inverters3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,19,20 have this advantage. The power loss breakdown of the individual components of the proposed topology is given in Fig. 11a. Due to the charging current, the losses are high in FCs and the IGBTs carrying the charging current. The simulation efficiency of the proposed topology is 97.4%, with a total loss of 13 W for ~ 500 W output power. However, in the experimental setup, the measured efficiency is ~ 95.8% for the unity power factor, as shown in Fig. 11b, with an approximate total power loss of ~ 21 W. The experimental efficiency is measured using the Fluke 434-II power quality meter. The photo of the scaled-down experiment setup is shown in Fig. 11c.

Conclusion

This paper has presented a new TL-9L inverter topology width that reduced the total number of power components. The discussion confirms that the proposed topology requires a lower number of power components. The performance of the proposed topology is analyzed in both simulation and scaled experimental setup.

The simulation and experimental results are well in good agreement. The various results have proved the proposed topology has self-voltage balancing and boosting ability. Also, the proposed topology can withstand any sudden changes at the load side or input voltage changes. The power loss breakdown is given for 500 W with maximum efficiency of ~ 95.8%. The comparison between the proposed topology and similar recently developed topologies also shows the merits of the proposed topology in terms of component count and efficiency, which can consider a great advantage with respect to the available solutions for PV fed AC Microgrid Applications.

Data availability

The datasets analyzed during the current study are available from the corresponding author on reasonable request.

References

Sathik, M. J., Sandeep, N. & Blaabjerg, F. High gain active neutral point clamped seven-level self-voltage balancing inverter. IEEE Trans. Circ. Syst. II Express Briefs 67(11), 2567–2571 (2020).

Hinago, Y. & Koizumi, H. A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans. Ind. Electron. 59(2), 878–887 (2012).

Roy, T. & Sadhu, P. K. A step-up multilevel inverter topology using novel switched capacitor converters with reduced components. IEEE Trans. Ind. Electron. 68(1), 236–247 (2021).

Barzegarkhoo, R., Moradzadeh, M., Zamiri, E., Madadi Kojabadi, H. & Blaabjerg, F. A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans. Power Electron. 33(8), 6738–6754 (2018).

Naik, B. S., Suresh, Y., Venkataramanaiah, J. & Panda, A. K. A hybrid nine-level inverter topology with boosting capability and reduced component count. IEEE Trans. Circ. Syst. II Express Briefs 68(1), 316–320 (2021).

Siddique, M. D. et al. A new single-phase single switched-capacitor based nine-level boost inverter topology with reduced switch count and voltage stress. IEEE Access 7, 174178–174188 (2019).

Lin, W., Zeng, J., Hu, J. & Junfeng, L. Hybrid nine-level boost inverter with simplified control and reduced active devices. IEEE J. Emerg. Sel. Top. Power. Electron. 9(2), 2038–2050 (2021).

Daula Siddique, M., Mekhilef, S., Padmanaban, S., Memon, M. A. & Kumar, C. Single phase step-up switched-capacitor based multilevel inverter topology with SHEPWM. IEEE Trans. Ind. Appln. 57(3), 3107–3119 (2021).

Sathik, M. J. & Krishnasamy, V. Compact Switched Capacitor Multilevel Inverter (CSCMLI) with self-voltage balancing and boosting ability. IEEE Trans. Power Electron. 34(5), 4009–4013 (2019).

Sathik, M. J., Sandeep, N., Almakhles, D. & Blaabjerg, F. Cross Connected Compact Switched-Capacitor Multilevel Inverter (C3-SCMLI) topology with reduced switch count. IEEE Trans. Circ. Syst. II Express Briefs 67(12), 3287–3291 (2020).

Buticchi, G., Barater, D., Lorenzani, E., Concari, C. & Franceschini, G. A nine-level grid-connected converter topology for single-phase transformerless PV systems. IEEE Trans. Ind. Electron. 61(8), 3951–3960 (2014).

Phanikumar, C., Roy, J. & Agarwal, V. A hybrid nine-level, 1-φ grid connected multilevel inverter with low switch count and innovative voltage regulation techniques across auxiliary capacitor. IEEE Trans. Power Electron. 34(3), 2159–2170 (2019).

Dhara, S. & Somasekhar, V. T. A nine-level transformerless boost inverter with leakage current reduction and fractional direct power transfer capability for PV applications. IEEE J. Emerg. Sel. Top. Power. Electron. https://doi.org/10.1109/JESTPE.2021.3074701 (2021).

Sathik, M. J. et al. Experimental validation of new self-voltage balanced 9L-ANPC inverter for photovoltaic applications. Sci. Rep. 11(5067), 1–1 (2021).

Siddique, M. D. & Mekhilef, S. A new configuration of nine-level boost inverter with reduced component count. Prime-Adv. Electr. Eng. Electron. Energy. 1, 100010 (2021).

Iqbal, A., Siddique, M. D., Reddy, B. P. & Maroti, P. K. Quadruple Boost Multilevel Inverter (QB-MLI) topology with reduced switch count. IEEE Trans. Power Electron. 36(7), 7372–7377 (2021).

Siddique, M. D. et al. Single-phase boost switched-capacitor based multilevel inverter topology with reduced switching devices. IEEE J. Emerg. Selected Topics Power Electron. https://doi.org/10.1109/JESTPE.2021.3129063 (2021).

Gu, Y. et al. Transformerless inverter with virtual dc bus concept for cost-effective grid-connected PV power systems. IEEE Trans. Power Electron. 28(2), 793–805 (2013).

Barzegarkhoo, R. et al. Nine-level nine-switch common-ground switched-capacitor inverter suitable for high-frequency AC-microgrid applications. IEEE Trans. Power Electron. 37(5), 6132–6143 (2022).

Anand, V., Singh, V. & Ali, J. S. M. Dual boost five-level switched-capacitor inverter with common ground. IEE Trans. Circ. Syst. Express Briefs. https://doi.org/10.1109/TCSII.2022.3169009 (2022).

Acknowledgements

The authors would like to acknowledge the support of Prince Sultan University for paying the Article Processing Charges (APC) of this publication. This work was supported by the Renewable Energy Laboratory (REL), College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia.

Author information

Authors and Affiliations

Contributions

All authors have contributed equally to the work. M.J.S. wrote the main manuscript text and prepared the figures, tables and developed the experimental hardware setup. D.J.A. validated the experimental results, reviewed the paper and corrected the grammatical mistakes. All authors contributed to and have approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Almakhles, D.J., Sathik, M.J. Single-phase transformerless nine-level inverter with voltage boosting ability for PV fed AC microgrid applications. Sci Rep 12, 13442 (2022). https://doi.org/10.1038/s41598-022-16057-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-16057-x

This article is cited by

-

A single-phase, nine-level switched-capacitor-based inverter

Journal of Power Electronics (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.