Abstract

Due to the low cost and the scaling capability of Si substrate, InAlN/GaN high-electron-mobility transistors (HEMTs) on silicon substrate have attracted more and more attentions. In this paper, a high-performance 50-nm-gate-length InAlN/GaN HEMT on Si with a high on/off current (Ion/Ioff) ratio of 7.28 × 106, an average subthreshold swing (SS) of 72 mV/dec, a low drain-induced barrier lowing (DIBL) of 88 mV, an off-state three-terminal breakdown voltage (BVds) of 36 V, a current/power gain cutoff frequency (fT/fmax) of 140/215 GHz, and a Johnson’s figure-of-merit (JFOM) of 5.04 THz V is simultaneously demonstrated. The device extrinsic and intrinsic parameters are extracted using equivalent circuit model, which is verified by the good agreement between simulated and measured S-parameter values. Then the scaling behavior of InAlN/GaN HEMTs on Si is predicted using the extracted extrinsic and intrinsic parameters of devices with different gate lengths (Lg). It presents that a fT/fmax of 230/327 GHz can be achieved when Lg scales down to 20 nm with the technology developed in the study, and an improved fT/fmax of 320/535 GHz can be achieved on a 20-nm-gate-length InAlN/GaN HEMT with regrown ohmic contact technology and 30% decreased parasitic capacitance. This study confirms the feasibility of further improvement of InAlN/GaN HEMTs on Si for RF applications.

Similar content being viewed by others

Introduction

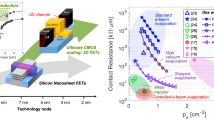

InAlN/GaN high-electron-mobility transistors (HEMTs) on silicon substrate have attracted more and more attentions due to the low cost and the scaling capability of Si substrate1,2,3,4. Li et al. demonstrated an InAlN/GaN HEMT on Si with a gate length (Lg) of 55 nm and a source-drain spacing (Lsd) of 175 nm5 using n++-GaN regrowth source/drain contacts. The device presents a maximum drain current (Id, max) of 2.8 A/mm, a peak extrinsic transconductance (gm) of 0.66 S/mm, and a current/power gain cutoff frequency (fT/fmax) of 250/204 GHz. Xie et al. reported that a record fT of 310 GHz was achieved on an InAlN/GaN HEMT on Si with a 40-nm gate length6. Cui et al. demonstrated an 80-nm-gate-length InAlN/GaN HEMT on Si with a record high on/off current (Ion/Ioff) ratio of 1.58 × 106, a steep subthreshold swing (SS) of 65 mV/dec, and a fT of 200 GHz, resulting in a record high fT × Lg = 16 GHz µm7. Chowdhury et al. demonstrated a complementary logic circuit (an inverter) on a GaN-on-Si platform with a record maximum voltage gain of 27 V/V at an input voltage of 0.59 V with VDD = 5 V8. Xie et al. reported an InAlN/GaN HEMT on Si with a fT of 210 GHz and a three-terminal off-state breakdown voltage (BVds) of 46 V, leading to a record high Johnson’s figure-of-merit (JFOM = fT × BVds) of 8.8 THz V9. Then et al.reported the high fT/fmax of 190/300 GHz was achieved on the e-mode high-k InAlN/GaN transistor on 300 mm Si substrate10.

However, to the best of our knowledge, the highest fT/fmax of 454/444 GHz and 348/340 GHz were achieved on 20-nm-gate-length AlN/GaN HEMT11 and 27-nm-gate-length InAlN/GaN HEMTs on SiC12, respectively. Although excellent performances have been demonstrated, InAlN/GaN HEMTs on Si still presents much room to be improved compared with GaN HEMTs on SiC substrate. The InAlN barrier can be grown lattice-matched to GaN when the In component is 17%, which makes it easier grow than AlN on GaN13. The InAlN/GaN heterostructure also exhibits higher quantum well polarization-induced charge than AlGaN/GaN heterostructure, resulting in higher channel electron density and drain current14,15. In addition, compared with AlGaN/GaN, a thinner InAlN barrier in InAlN/GaN HEMTs not only can offer higher frequency performance with an improved device transconductance, but also can suppress the short-channel effect with the reduced gate-to-channel distance16,17. Hence, exploring the possible limiting factors of InAlN/GaN HEMTs on Si is significant to further improve the device performance. In this paper, high-performance InAlN/GaN HEMTs on Si are demonstrated. The extrinsic and intrinsic parameters of devices with different gate lengths are extracted and the scale behavior of InAlN/GaN HEMTs on Si is predicted. It presents that a fT/fmax of 230/327 GHz can be achieved when Lg scales down to 20 nm with the technology developed in the study, and an improved fT/fmax of 320/535 GHz can be achieved on a 20-nm-gate-length InAlN/GaN HEMTs with regrowth ohmic contact technology and 30% decreased parasitic capacitance. This confirms the feasibility of further improvement of InAlN/GaN HEMTs on Si for RF applications.

Experiment

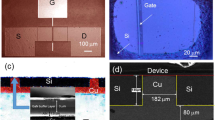

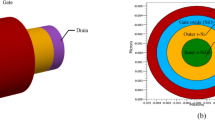

Figure 1a shows the lattice-matched In0.17Al0.83N/GaN heterostructure, which is grown on a Si substrate by metalorganic chemical vapor deposition (MOCVD). The epitaxial layer structure consists of a 2-nm GaN cap layer, an 8-nm In0.17Al0.83N barrier layer, a 1-nm AlN interlayer, a 15-nm GaN channel layer, a 4-nm In0.12Ga0.88N back-barrier layer, and a 2-μm undoped GaN buffer layer18. The electron sheet concentration and electron mobility measured by Hall measurements were 2.28 × 1013 cm−2 and 1205 cm2/V s, respectively.

(a) Schematic of fabricated InAlN/GaN HEMT; (b) Detailed device fabrication steps; (c) a plan-view scanning electron microscopy (SEM) image of the InAlN/GaN HEMT with a gate head length (Lhead) of 400 nm and a source-drain spacing (Lsd) of 600 nm; (d) A SEM image of T-shaped gate structure depicting a gate footprint of 50 nm.

Figure 1b shows the detailed device fabrication steps. The device fabrication started with mesa isolation using Cl2/CH4/He/Ar inductively coupled plasma etching. Then Ti/Al/Ni/Au stack was deposited and annealed at 850 °C for 40 s in N2 to form the alloyed ohmic contacts. The ohmic contact resistance is 0.3 Ω mm. An oxygen plasma treatment was then applied to form the oxide layer on top of the InAlN layer, which can effectively reduce the gate leakage current and improve RF erformance19,20,21,22. Finally, a Ni/Au T-shaped gate with a gate width (Wg) of 2 × 20 µm was fabricated by electron beam lithography. Figure 1c shows a plan-view scanning electron microscopy (SEM) image of the InAlN/GaN HEMT with a gate head length (Lhead) of 400 nm and a source-drain spacing (Lsd) of 600 nm. Figure 1d shows a SEM image of T-shaped gate structure depicting a gate footprint of 50 nm.

Results and discussion

DC performance

The DC current–voltage (I–V) measurements are carried out by using an Agilent B1500A semiconductor parameter analyzer. Figure 2a shows the output characteristic of the InAlN/GaN HEMT with a 50-nm gate length. The device on-resistance (Ron) extracted at gate-source (Vgs) of 0 V and drain-source voltage (Vds) between 0 and 0.5 V is 1.33 Ω·mm. The gate-to-channel distance tbar (including a 2-nm GaN, an 8-nm InAlN, and a 1-nm AlN) is 11 nm. Since Lg is 50 nm, the device presents an aspect ratio (Lg/tbar) of 4.5. Due to the low Lg/tbar, the short-channel effects (SCEs) start to appear when Vds is larger than 5 V and Vgs is between − 4 to − 1 V. At Vgs = 1 V, drain current (Id) in saturation region presents a decrease with increased Vds, an indication of the thermal effect.

Figure 2b shows the transfer characteristic with the extracted extrinsic transconductance (gm) of the InAlN/GaN HEMT with a 50-nm gate length at Vds = 10 V. The maximum saturation drain current (Id, max) is 2.01 A/mm at Vgs = 1 V and Vds = 10 V. The gm perk (gm, peak) is 493 mS/mm. To the best of our knowledge, the record high Id, max of 2.8 A/mm and gm,peak of 660 mS/mm were achieved on a 55-nm-gate-length InAlN/GaN HEMT on Si with regrowth technology and Lsd of 175 nm5. The lower Id and gm,peak in this study result from the regrowth-free technology and the larger source-drain spacing (Lsd = 600 nm).

Figure 3a shows the transfer and gate current (Ig) characteristics in semi-log scale of the InAlN/GaN HEMT with a 50-nm gate length at Vds = 5 V and 10 V, respectively. At Vds = 10 V, the device off-current (Ioff) is 2.76 × 10–7 A/mm and the Ion/Ioff ratio is 7.28 × 106, which are higher than the record reported values (Ioff of 7.12 × 10–7 A/mm and Ion/Ioff ratio of 1.58 × 106) achieved from the InAlN/GaN HEMT on Si7. An average subthreshold swing (SS) of 72 mV/dec over more than two orders of Id is extracted from the transfer curve. The drain-induced barrier lowering (DIBL) of 88 mV/V is extracted at Id = 10 mA/mm between Vds = 10 V and Vds = 5 V, which is the lowest value among the reported GaN HEMTs on Si. The lowest DIBL value suggests a suppressed SCEs for the sub-100 nm gate-length device. Figure 3b shows the off-state three-terminal breakdown characteristic of the 50-nm InAlN/GaN HEMT measured at Vgs = − 8 V. The device features a BVds of 36 V at a drain leakage current of 1 mA/mm.

RF performance

The device RF performance is measured with a frequency range from 1 to 65 GHz. The network analyzer is calibrated using a two-port short/open/load/through method. On-wafer open and short structures is used to eliminate the effects of parasitic elements. Figure 4a shows the current gain (|h21|2), unilateral gain (U), and the maximum stable gain (MSG) as a function of frequency at Vds = 10 V, Vgs = − 3 V after de-embedding. fT/fmax of 140/215 GHz for the InAlN/GaN HEMT with a 50-nm gate length is obtained by extrapolation of |h21|2 with a − 20 dB/dec slope. An (fT × fmax)1/2 of 173 GHz is obtained, which is the highest record value among the reported InAlN/GaN HEMTs on Si with regrowth-free ohmic contact technology. To the best of our knowledge, a high (fT × fmax)1/2 of 226 GHz (fT/fmax = 250/204 GHz) was achieved on a 55-nm InAlN/GaN HEMT on Si5, and a high (fT × fmax)1/2 of 239 GHz (fT/fmax = 190/300 GHz) was demonstrated on the e-mode high-k InAlN/GaN MISHEMTs with Lg of 50 nm10. The ohmic contact regrowth technology was used in both reported devices. Here for our device, the alloyed ohmic resistance (RC: 0.3 Ω mm) is higher than the reported regrowth ohmic contact resistance (RC: 0.05 Ω mm)5. This presents a high potential for the RF performance improvement by further decreasing the ohmic contact resistance. Due to fT/fmax of 140/215 GHz, products of fT × Lg and fmax × Lg of 7.0 and 10.75 GHz·µm are achieved, respectively. Although neither passivation nor field plate technology is used, the 140-GHz InAlN/GaN HEMT with an BVds of 36 V presents a Johnson’s figure-of-merit (JFOM = fT × BVds) of 5.04 THz·V. Figure 4b shows the measured fT and fmax of the 50-nm InAlN/GaN HEMT as a function of Vgs. Both fT and fmax show a gradual decrease compared with their peak values, presenting a good device linearity.

Equivalent circuit model

The classical 16-element equivalent-circuit model is used for the InAlN/GaN HEMT, as shown in Fig. 5a23,24. Based on this model, the device extrinsic and intrinsic parameters are extracted in Table 123,24,25. The slight discrepancy between the simulated and measured S-parameter values is observed in Fig. 5b, verifying the accuracy of the extracted extrinsic and intrinsic parameters. The fT and fmax can be calculated using23,26

where Gm and G0 are the intrinsic transconductance and drain-source conductance, respectively; Cgs and Cgd are the gate-source and gate-drain parasitic capacitance, respectively; Rs, Rd, Rg, and Ri are the parasitic source access resistance, drain access resistance, gate electrode resistance, and input resistance, respectively.

The calculated fT/fmax = 145/218 GHz is very close to the value (fT/fmax = 140/215 GHz) extracted by the extrapolation of |h21|2 with a − 20 dB/dec slope, which confirms the excellent RF performance. The high intrinsic transconductance/drain-source conductance (Gm/G0) ratio of 10.6 contributes to the high fmax.

Scaling behavior

The InAlN/GaN HEMTs with Lg between 50 and 350 nm are fabricated. Figure 6a shows the measured fT/fmax of the InAlN/GaN HEMTs with different Lg at Vgs = − 3 V and Vds = 10 V. The devices with Lg of 50, 70, 100, 150, 250, and 350 nm present fT/fmax of 140/215, 135/205, 120/170, 90/160, 60/136, 36/128 GHz, respectively. fT × Lg and fmax × Lg are obtained in Fig. 6b. A fT × Lg peak of 15 GHz µm is achieved on the 250-nm-gate-length InAlN/GaN HEMT with a fT of 135 GHz. fmax × Lg presents a decrease from 44.8 GHz µm (Lg = 350 nm) to 10.75 GHz µm (Lg = 50 nm). The decrease of both fT × Lg and fmax × Lg as Lg scales down means that the effect of parasitic parameters is more pronounced, thus hindering the improvement of fT and fmax. Due to the large head length of T-shaped gate (Lhead = 400 nm), the transistors features higher fmax and fmax × Lg.

To shed more light on the scaling behavior, the extrinsic and intrinsic parameters of these devices are further extracted using the equivalent circuit model discussed above. Cgs can be separated to two parts: gate-source intrinsic capacitance (Cgs,int) and gate-source extrinsic capacitance (Cgs, ext). It means Cgs = Cgs,int + Cgs,ext27. Cgd can also be written as Cgd = Cgd,int + Cgd,ext. Figure 7 shows the extracted Cgs and Cgd as a function of Lg. Both Cgs and Cgd present a linear dependence upon Lg. By linear fitting, the Cgs,ext and Cgd, ext are obtained from Cgs and Cgd at Lg = 0 nm27, as shown in Fig. 7. Here Cgs,ext of 93.05 fF/mm and Cgd,ext of 97.65 fF/mm are determined, respectively.

The total delay (τ) of transistors can be written as27,28

Here τ is partitioned into three components: transit time (τt), parasitic charging delay (τext), and parasitic resistance delay (τpar).

τt is the transit time under the gate region. It is related to the gate length as well as the electron velocity (ve) under the gate region, and can be calculated by27,28

τext is parasitic charging delay through Cgs,ext as well as Cgd,ext, and can be written as27,28

τpar is parasitic resistance delay mainly associated with Rs as well as Rd, and can be written as27,28

Figure 8 plots τt and ve as a function of Lg calculated from (3). As Lg decreases, τ shows a monotonous drop, which corresponds to the increased fT. With decreased Lg, ve increases to a maximum value of 1.08 × 107 cm/s (at Lg = 150 nm) and then drop to 0.80 × 107 cm/s (at Lg = 50 nm). Figure 9 shows the extracted Gm and G0 from the equivalent-circuit model as a function of Lg. G0 shows an increase with decreased Lg. The dependence of Gm and ve on Lg present the same trend. Based on (3), because Cgsi and Cgdi linearly depends on Lg, we conclude that the change of Gm is attributed to ve difference. The same trend of Gm and ve on Lg is also observed in InAs HEMTs and result from the short channel effect29,30,31.

Figure 10 exhibits the calculated τt, τext, and τpar using (3)–(5). τext and τpar is almost unchanged. Conversely, τt decreases with decreased Lg and dominates the total delay in all devices. This makes it possible to decrease delay and improve fT through downscaling of device gate length. However, for the device with Lg below 100 nm, the effect of τext and τpar become non-negligible. The ratios of (τext + τpar)/τt are 39% and 40% for the InAlN/GaN HEMTs with Lg of 70 and 50 nm, respectively. This means the parasitic capacitance and resistance significantly hampers further Lg scaling benefits in RF performance of sub-100 nm InAlN/GaN HEMTs.

Therefore, downscaling and decreasing parasitic resistances as well as capacitances are very important for further improving device performance of InAlN/GaN HEMTs on Si. Figure 11 plots the calculated fT and fmax based on the model and the extracted parameters (Blue-line in Fig. 11), which shows a good agreement with the measured results. In terms of the electron velocity saturation, the electron velocity of the InAlN/GaN HEMTs with Lg < 50 nm is assumed to be the same as that with Lg = 50 nm. With the obtained ve, τt can be obtained using (3), τext is parasitic charging delay through Cgs,ext and Cgd,ext, and both are the constant as shown in Fig. 7. τpar is mainly associated with Rs and Rd, which are independent on Lg. As shown in Fig. 10, τext and τpar present slight change with Lg. So here τpar of the device with Lg = 50 nm is used during the model calculation. Then fT can be calculated with the obtained τt, τext and τpar by using (2). When Lg decrases from the 50–20 nm, the T-shaped gate head length of 400 nm is unchanged, so the effect of the small gate length variation on Rg and Ri is miminal. Hence Rg and Ri of device with Lg of 50 nm are used. Cgd is extracted from the linear fitting in Fig. 7b and then fmax is obtained using (1). The model results present that fT/fmax of 230/327 GHz can be achieved when Lg scales down to 20 nm with the technology developed in the study. To decrease the parasitic resistance, the regrowth ohmic contact can be used. Here Rs (0.30 Ω mm), Rd (0.32 Ω mm), and Gm (573 mS/mm) are changed to 0.10 Ω mm, 0.08 Ω mm, and 620 mS/mm5. Then new model results with regrowth technology are plotted (Green-line in Fig. 11) and a fT/fmax of 265/397 GHz is achieved on the device with a 20-nm gate length. Optimizing the detailed structure of T-shaped gate can decrease Cgs and Cgd. Hence when 30% decreasing of Cgs and Cgd is added into the model, new results (Red-line in Fig. 11) are plotted and an improved fT/fmax of 320/535 GHz on 20-nm-gate-length InAlN/GaN HEMT is demonstrated. These values are comparable to the 27-nm InAlN/GaN HEMTs on SiC with fT/fmax of 348/340 GHz, suggesting the possibility of further improvement of InAlN/GaN HEMTs on Si.

Conclusions

In summary, high-performance 50-nm InAlN/GaN HEMT on Si with an Ion/Ioff ratio of 7.28 × 106, a SS of 72 mV/dec, a DIBL of 88 mV/V, a BVds of 36, a fT/fmax of 140/215 GHz, and a JFOM of 5.04 THz V are demonstrated. The extrinsic and intrinsic parameters of transistors with different Lg are extracted and the scaling behavior of InAlN/GaN HEMTs on Si is demonstrated. Based on extracted model, a fT/fmax of 320/535 GHz can be achieved on a 20-nm-gate-length InAlN/GaN HEMT with regrowth ohmic contact technology and 30% decreased parasitic capacitance. This study confirmes the feasibility of further improvement of InAlN/GaN HEMTs on Si for RF applications.

Data availability

The datasets supporting the conclusions of this article are included in the article.

Abbreviations

- HEMT:

-

High-electron-mobility transistor

- I on/I off :

-

On/off current ratio

- SS:

-

Subthreshold swing

- DIBL:

-

Drain-induced barrier lowing

- BV ds :

-

Off-state three-terminal breakdown voltage

- f T/f max :

-

Current/power gain cutoff frequency

- JFOM:

-

Johnson’s figure-of-merit

- g m :

-

Extrinsic transconductance

- MOCVD:

-

Metalorganic chemical vapor deposition

- SEM:

-

Scanning electron microscopy

- I d :

-

Drain current

- I g :

-

Gate current

- L g :

-

Gate length

- L sd :

-

Source-drain spacing

- V gs :

-

Gate-source voltage

- V ds :

-

Drain-source voltage

- R on :

-

On-resistance

- SCEs:

-

Short-channel effects

- |h21|2 :

-

Current gain

- U:

-

Unilateral gain

- MSG:

-

Maximum stable gain

References

Chen, K. J. et al. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron Devices 64, 779–795 (2017).

Ishida, M., Ueda, T., Tanaka, T. & Ueda, D. GaN on Si technologies for power switching devices. IEEE Trans. Electron Devices 60, 3053–3059 (2013).

Lee, H.-S., Ryu, K., Sun, M. & Palacios, T. Wafer-level heterogeneous integration of GaN HEMTs and Si (100) MOSFETs. IEEE Electron Device Lett. 33, 200–202 (2012).

Minko, A. et al. AlGaN-GaN HEMTs on Si with power density performance of 1.9 W/mm at 10 GHz. IEEE Electron Device Lett. 25, 453–455 (2004).

Li, L. et al. GaN HEMTs on Si with regrown contacts and cutoff/maximum oscillation frequencies of 250/204 GHz. IEEE Electron Device Lett. 41, 689–692 (2020).

Xie, H. et al. Deeply-scaled GaN-on-Si high electron mobility transistors with record cut-off frequency fT of 310 GHz. Appl. Phys. Express 12, 126506 (2019).

Cui, P. et al. High-performance InAlN/GaN HEMTs on silicon substrate with high fT× Lg. Appl. Phys. Express 12, 104001 (2019).

Chowdhury, N. et al. Regrowth-free GaN-based complementary logic on a Si substrate. IEEE Electron Device Lett. 41, 820–823 (2020).

Xie, H. et al. CMOS-compatible GaN-on-Si HEMTs with cut-off frequency of 210 GHz and high Johnson’s figure-of-merit of 8.8 THz· V. Appl. Phys. Express 13, 026503 (2020).

Then, H. W. et al. Gallium nitride and silicon transistors on 300 mm silicon wafers enabled by 3-D monolithic heterogeneous integration. IEEE Trans. Electron Devices 67, 5306–5314 (2020).

Tang, Y. et al. Ultrahigh-speed GaN high-electron-mobility transistors with fT/fmax of 454/444 GHz. IEEE Electron Device Lett. 36, 549–551 (2015).

Schuette, M. L. et al. Gate-recessed integrated E/D GaN HEMT technology with fT/fmax>300GHz. IEEE Electron Device Lett. 34, 741–743 (2013).

Dadgar, A. et al. High-sheet-charge–carrier-density Al In N∕ Ga N field-effect transistors on Si (111). Appl. Phys. Lett. 85, 5400–5402 (2004).

Kuzmík, J. Power electronics on InAlN/(In) GaN: Prospect for a record performance. IEEE Electron Device Lett. 22, 510–512 (2001).

Gonschorek, M., Carlin, J.-F., Feltin, E., Py, M. & Grandjean, N. High electron mobility lattice-matched Al In N∕ Ga N field-effect transistor heterostructures. Appl. Phys. Lett. 89, 062106 (2006).

Yue, Y. et al. InAlN/AlN/GaN HEMTs with regrown ohmic contacts and fT of 370 GHz. IEEE Electron Device Lett. 33, 988–990 (2012).

Jessen, G. H. et al. Short-channel effect limitations on high-frequency operation of AlGaN/GaN HEMTs for T-gate devices. IEEE Trans. Electron Devices 54, 2589–2597 (2007).

Cui, P. et al. Effects of N2O surface treatment on the electrical properties of the InAlN/GaN high electron mobility transistors. J. Phys. D Appl. Phys. 53, 065103 (2020).

Chung, J. W., Roberts, J. C., Piner, E. L. & Palacios, T. Effect of gate leakage in the subthreshold characteristics of AlGaN/GaN HEMTs. IEEE Electron Device Lett. 29, 1196–1198 (2008).

Chung, J. W., Kim, T.-W. & Palacios, T. Advanced gate technologies for state-of-the-art fT in AlGaN/GaN HEMTs. In 2010 International Electron Devices Meeting, 30.2.1–30.2.4 (2010).

Lee, D. S. et al. 245-GHz InAlN/GaN HEMTs with oxygen plasma treatment. IEEE Electron Device Lett. 32, 755–757 (2011).

Wang, R. H. et al. 210-GHz InAlN/GaN HEMTs with dielectric-free passivation. IEEE Electron Device Lett. 32, 892–894 (2011).

Bouzid-Driad, S. et al. AlGaN/GaN HEMTs on silicon substrate with 206-GHz fmax. IEEE Electron Device Lett. 34, 36–38 (2013).

Crupi, G. et al. Accurate multibias equivalent-circuit extraction for GaN HEMTs. IEEE Trans. Microw. Theory Tech. 54, 3616–3622 (2006).

Campbell, C. F. & Brown, S. A. An analytic method to determine GaAs FET parasitic inductances and drain resistance under active bias conditions. IEEE Trans. Microw. Theory Tech. 49, 1241–1247 (2001).

Chung, J. W., Hoke, W. E., Chumbes, E. M. & Palacios, T. AlGaN/GaN HEMT With 300-GHz fmax. IEEE Electron Device Lett. 31, 195–197 (2010).

Kim, D.-H., Brar, B. & Del Alamo, J. A. f T= 688 GHz and f max= 800 GHz in L g= 40 nm In 0.7 Ga 0.3 As MHEMTs with g m_max> 2.7 mS/µm. In 2011 International Electron Devices Meeting, 13.6. 1–13.6. 4 (2011).

Lee, D. S. et al. 300-GHz InAlN/GaN HEMTs with InGaN back barrier. IEEE Electron Device Lett. 32, 1525–1527 (2011).

Endoh, A., Watanabe, I., Kasamatsu, A. & Mimura, T. Monte Carlo simulation of InAs HEMTs considering strain and quantum confinement effects. J. Phys. Conf. Ser. 454, 012036 (2013).

Kim, D.-H. & Del Alamo, J. A. Logic performance of 40 nm InAs HEMTs. In 2007 IEEE International Electron Devices Meeting, 629–632 (2007).

Kim, T.-W., Kim, D.-H. & del Alamo, J. A. 30 nm In0.7 Ga0.3 As Inverted-Type HEMTs with reduced gate leakage current for logic applications. In 2009 IEEE International Electron Devices Meeting (IEDM), 1–4 (2007).

Funding

This work was supported in part by the NASA International Space Station under Grant 80NSSC20M0142, and in part by Air Force Office of Scientific Research under Grant FA9550-19-1-0297, Grant FA9550-21-1-0076 and Grant FA9550-22-0126.

Author information

Authors and Affiliations

Contributions

P.C. and Y.Z. contributed to the research design, experiment measurements, data analysis, and manuscript preparation. All authors reviewed this manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Cui, P., Zeng, Y. Scaling behavior of InAlN/GaN HEMTs on silicon for RF applications. Sci Rep 12, 16683 (2022). https://doi.org/10.1038/s41598-022-21092-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-21092-9

This article is cited by

-

Exploration on the impact of barrier thickness, gate recess, and lateral scaling on AlGaN/GaN SRL HEMT on silicon for future RF power electronics

Journal of Materials Science: Materials in Electronics (2024)

-

Device Optimization of T-shaped Gate and Polarized Doped Buffer-Engineered InAlN/GaN HEMT for Improved RF/Microwave Performance

Arabian Journal for Science and Engineering (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.