Abstract

Space division multiplexing using multicore fibers is becoming a more and more promising technology. In space-division multiplexing fiber network, the reconfigurable switch is one of the most critical components in network nodes. In this paper we for the first time demonstrate reconfigurable space-division multiplexing switching using silicon photonic integrated circuit, which is fabricated on a novel silicon-on-insulator platform with buried Al mirror. The silicon photonic integrated circuit is composed of a 7 × 7 switch and low loss grating coupler array based multicore fiber couplers. Thanks to the Al mirror, grating couplers with ultra-low coupling loss with optical multicore fibers is achieved. The lowest total insertion loss of the silicon integrated circuit is as low as 4.5 dB, with low crosstalk lower than −30 dB. Excellent performances in terms of low insertion loss and low crosstalk are obtained for the whole C-band. 1 Tb/s/core transmission over a 2-km 7-core fiber and space-division multiplexing switching is demonstrated successfully. Bit error rate performance below 10−9 is obtained for all spatial channels with low power penalty. The proposed design can be easily upgraded to reconfigurable optical add/drop multiplexer capable of switching several multicore fibers.

Similar content being viewed by others

Introduction

The communication capacity over standard single mode fibers has been approaching the theoretical limit1. In order to further increase the communication capacity over fibers to satisfy the huge capacity demand in future, space division multiplexing (SDM) using multicore fibers (MCFs) has shown to be a promising technology2,3,4,5. In order to facilitate the deployment of SDM technologies, it is crucial to develop devices that can provide additional network functionalities, such as fan-in/fan-out devices6,7,8,9, MCF amplifiers10,11, add/drop modules and switches12,13,14,15, etc. MCF switching is one of the most important functionalities at reconfigurable optical add/drop multiplexers (ROADMs) in future SDM systems. Recently, an array of wavelength-selective switches (WSSs) has also been proposed to implement a ROADM for MCFs communication systems16. Flexible architectures using free-space switching based on Micro Electro Mechanical Systems (MEMS) mirrors or on Liquid Crystal on Silicon (LCOS) pixel arrays have also been demonstrated16,17. In addition, all-optical nonlinear switching in MCFs has also been demonstrated using high-power ultrashort laser pulses18. Nevertheless, all these solutions are quite complex with high insertion losses. In order to reduce the insertion loss, flexural acoustic waves have also been used for switching in MCFs19. However, all current demonstrations are non-integration solutions, and integrating multiple functionalities, e.g. MCF couplers, MCF switches, add/drop on the SOI platform is highly desirable for an MCF system. Integration is a very promising solution because it can take advantage of complementary metal–oxide–semiconductor (CMOS) compatible fabrication process and support massive production, resulting in ultra-compact and powerful silicon chips for MCF systems with potentially low-cost.

In this paper, we for the first time demonstrate reconfigurable switching between the cores of an MCF using a novel silicon photonic integrated circuit (PIC), which is fabricated on a silicon-on-insulator platform with buried Al mirror. The silicon PIC integrates grating coupler array based MCF couplers and a 7 × 7 switch. Thanks to the Al mirror, ultra-high coupling efficiency between the chip and MCFs is achieved, and the insertion loss of the silicon PIC is as low as 4.5 dB, with low channel dependent loss lower than 2.5 dB and low crosstalk lower than −35 dB. The good performances in terms of low insertion loss and low crosstalk are obtained for the whole C-band. We further demonstrate core switching of the MCFs in different switching configurations when each core is carrying independent 1 Tb/s data. Bit error rate (BER) performance lower than 10−9 is achieved for switching all the cores with low power penalty. We further show that the proposed design can be easily upgraded by adding more MZIs into the switching matrix for switching of multicore fibers and realization of more complex MCF ROADMs.

Results

Reconfigurable silicon PIC

The topology structure of the silicon PIC is depicted in Fig. 1, which consists of MCF coupler for MCF input and output respectively, and a reconfigurable 7 × 7 switch. A seven-core fiber is coupled to the input MCF coupler, which is further connected to the 7 × 7 switch composed of a Mach-Zehnder interferometer (MZI) arrays based switching matrix. After switching, the seven spatial channels are coupled to the output MCF through a second MCF coupler. In this scheme, any core of the input MCF can be reconfigurably switched to any core of the output MCF fiber. For example, by configuring the corresponding MZIs, the bar (solid line) switching configuration for the seven spatial channels (corresponding to different color) can be replaced by the cross (dash line) configuration.

Topology of the silicon PIC for core switch of MCFs.

A seven-core fiber is coupled to the input MCF coupler, which is connected to the MZI arrays based 7 × 7 switching matrix. After switching, the seven spatial channels are coupled to the output MCF through a second MCF coupler. By configuring the corresponding MZIs, the bar (solid line) switching configuration for the seven spatial channels can be freely tuned to cross (dash line) configuration.

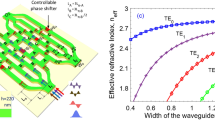

The whole silicon PIC is designed on a SOI platform with top silicon thickness of 250 nm. In order to simplify the fabrication process, single etched grating couplers based on photonic crystals6 are used for the MCF couplers20. From the topology of the silicon PIC, building blocks such as 2 × 2 multimode interferometers (MMIs) and cross intersections are used, and low insertion loss of those building blocks are critical to achieve low insertion loss of the whole silicon PIC. In order to fabricate the whole silicon PIC in the same process, the 2 × 2 MMIs and cross intersection are designed by three dimensional (3D) finite-difference time-domain method (FDTD) for single etch process. The cross intersection is based on two crossed MMIs, and the crosstalk is minimized by designing the self-image position on the cross point of the two MMIs21. In order to achieve ultra-high coupling efficiency, Al mirror is used below the grating coupler based MCF couplers. For this purpose, a new silicon-on-insulator platform with Al mirror dedicated for passive silicon photonics was fabricated first by flip-bonding method. The silicon dioxide layer between the top silicon layer and Al mirror is designed to be 1.6 μm, which is an optimum thickness for fully etched grating couplers on 250 nm silicon layer20. The silicon PIC was then fabricated on the new silicon-on-insulator platform by a single step of standard SOI processing, including e-beam lithography and inductively coupled plasma (ICP) etching, followed by extra steps of lithography and metal liftoff for fabrication of metallic heater. Figure 2(a) shows the fabricated silicon PIC, which is wire-bonded to a PCB board for flexible controlling by microprocessor. The detailed microscopy image of the silicon PIC is shown in Fig. 2(b). The 7 × 7 switch is built out by 57 Mach-Zehnder interferometric (MZI) structures, each incorporating a heater in one arm. Apodized grating coupler array with layout that corresponds to the cores of the MCF is used for MCF coupling6,18, as shown in Fig. 2(c). The reconfigurable switching is realized by a MZI matrix, where the tunability is realized by titanium (Ti) heaters22. Figure 2(d) and (e) show the fabricated 2 × 2 MMI and cross intersection used in the silicon PIC, respectively.

(a) Fabricated silicon PIC, which is wire-bonded to a PCB board. (b) Detailed microscopy image of the silicon PIC, which consists of (c) grating coupler array based MCF coupler, and switching matrix. The reconfigurability is realized by thermal tuning of heaters in the switching matrix. The inset of (c) shows the scanning electron microscopy (SEM) image of the apodized grating coupler. (d) and (e) Shows the SEM images of the 2 × 2 MMI and cross intersection used in the PIC.

The performance of the 2 × 2 MMI and heaters that are used in the PIC are tested by an asymmetrical MZI (AMZI) with the same heater design, as presented in Fig. 3(a). An extinction ratio larger than 35 dB with insertion loss as low as −0.04 dB is achieved indicating that similar insertion loss and extinction ratio will be obtained for a single MZI switch. In addition, around 5 V (corresponding to 25 mW) results in a phase shift of 2π, and power consumption for π phase shift is ~13 mW. A square waveform is applied to test the switching speed of the heater, and typical slow rising time (10% to 90%) and falling time (90% to 10%) of 66 μs and 27 μs are found, respectively. The performance of the cross intersection is tested by cascading different number N of intersections, and measuring the transmitted power. The results are exhibited in Fig. 3(b). An ultra-low insertion loss lower than 0.1 dB is achieved with ultra-low crosstalk lower than −45 dB.

(a) Characterization of AMZI (the upper-right inset) by applying different voltage in order to test performance the MZI switches and heaters. The lower-down inset shows the switched optical signal by electrical square waveform, indicating a switching time of 66 μs and 27 μs for rising and falling time. (b) Characterization of cross intersection by cascading different number of cross intersections, and measuring the corresponding crosstalk arm and transmitted power.

The effective area of each core of the MCF used in our experiment is 110 μm2 with core pitch of 49 μm. Considering that the mode mismatch between the MCF and standard single mode fiber (SSMF) is lower than 0.03 dB, the whole silicon PIC is then tested by coupling light to different input grating couplers through an SSMF, and measuring the output from the corresponding output grating couplers using SSMF. The MZI switches are in cross switching state by default without heating power. The SDM switch is first configured in bar configuration (core 1 at the input is connected to core 1 at the output, core 2 to core 2, etc.), 31 MZIs are configured consuming about 401 mW power. The heaters are separated away for at least 60 μm from the neighbor MZIs to decrease the heating crosstalk. A home-made Labview software was used to tune the corresponding heaters to maximum the transmission of the switched path while minimize the crosstalk. After configured, the configuration is very stable thanks to the stable on-chip phase control by heaters. Figure 4(a) shows the transmission and corresponding crosstalk for bar configuration. High transmission covering the whole C-band is obtained for all the switching paths with crosstalk lower than −30 dB. An extremely low insertion loss of 4.5 dB at 1546 nm is achieved. It should be noted that the insertion loss includes the coupling loss of the input and output MCF couplers, the waveguide propagation loss, and all losses by the MZIs and cross intersections. The channel dependent loss, which is defined as the transmission difference between different switching paths at the same wavelength, is lower than 2.5 dB for the whole C-band. By applying proper voltages to the corresponding heaters in the 7 × 7 switching matrix, the silicon PIC is tuned to cross switching configuration (core 1 at the input is connected to core 7 at the output, core 2 to core 6, etc.). 21 MZIs are configured consuming power of 272 mW. High transmission is still obtained for all switching paths with lowest insertion loss of 5.5 dB and 2.2 dB channel dependent loss. Low crosstalk (lower than −35 dB) is obtained for the whole C-band.

System experiment

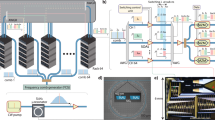

Figure 5 shows the system experimental setup. A wavelength division multiplexing (WDM) signal in the range from 1541.35 nm to 1560.61 nm consisting of 25 channels with a 100 GHz grid is used. Each channel is carrying 40 Gb/s on-off keying (OOK) modulated data, resulting in 1 Tb/s/channel traffic load. After modulation, the data is split to seven spatial channels, amplified and decorrelated using fibers with different length for each channel before loading the seven-core fiber. An on-chip fan-in device based on 3D inscribed waveguides is used for coupling to a 2-km seven-core fiber. After propagation, the seven-core fiber is coupled directly to the fabricated silicon PIC for spatial channel switching. The 7 × 7 switch, which is able to switch the different cores of the MCF, is controlled by a microcontroller allowing for individual control of each heater on the chip. A preliminary characterization is performed to determine the optimum values of the relevant heaters in order to establish data paths in bar and cross configurations. In order to receive the data from the switched cores at the output of the switch, an additional integrated fan-out device is used for spatial demultiplexing after which the data is amplified, wavelength de-multiplexed using a flat-top bandpass 100 GHz filter and passed to a 40 Gb/s receiver.

Experimental setup.

1 Tb/s OOK traffic load covering the C band is used as data. The data is split to seven beams (channels), amplified and decorrelated using fibers with different lengths. The seven channels are coupled to a 2-km seven-core fiber by a 3D inscribed waveguides based on-chip fan-in device. After transmission, the seven channels are coupled to the chip for switching. The switched seven spatial channels are coupled out to a 2m seven-core fiber again, and an additional integrated fan-out device is used for spatial demultiplexing after which the data is amplified, wavelength de-multiplexed and received in a 40 Gb/s receiver.

Figure 6a and b illustrate the output spectra of cores 4 and peak power fluctuation of different wavelength channels for all cores after the switch in the bar and cross configurations respectively. The performance of all channels in a single core in both configurations is shown in Fig. 6c. In both cases all channels exhibit similar performance with an average penalty of 3 to 4 dB compared to the average back-to-back (B2B) performance. The imperfect power equalization of the channels as well as the wavelength dependent crosstalk of the switch, which is due to polarization variation after transmission, contributes to the penalty variations. In order to confirm that similar performance is expected in all the switched cores, the receiver sensitivity (BER = 10−9) of one channel (1550.92 nm) is measured in all cores as shown in Fig. 6d. For both configurations, the performance in all cores is within 5 dB margin. The different insertion loss and crosstalk experienced by each core as a result of the coupling devices as well as the different crosstalk in the switching configurations contribute to this variation. The effect of crosstalk from switching can be seen as 5 dB variation in the sensitivity of the chosen channel in core 4, which in both configurations is switched in the same way. In order to precisely evaluate the impact of the crosstalk from switching, full BER curves are measured on the same channel in both configurations as shown in Fig. 6e and f. First, data is launched in only one core of the MCF and switched (i.e. w/o crosstalk) and then data is launched and switched in all cores simultaneously (i.e. w/crosstalk). There is around 1.5 dB and 1.2 dB penalty when only one core is loaded for bar and cross configurations respectively, which is due to crosstalk from other coupling devices used in the system. Loading and switching all cores results in about 0.4 dB and 2.9 dB additional penalty for bar and cross configurations, respectively. This indicates that some cores may suffer from higher crosstalk in some configurations.

Output spectrum of cores 4 and peak power fluctuations of different wavelength channels for all cores in (a) configuration bar and (b) configuration cross; (c) receiver sensitivity of all channels in a single core in both configurations and (d) receiver sensitivity of a single channel (1550.92 nm) in all cores in both configurations; BER results and eye diagrams of a single channel (1550.92 nm) in a single core w/o and w/crosstalk in (e) configuration bar and (f) configuration cross.

Discussion and Conclusions

It is observed that a single AMZI has an extinction ratio larger than 35 dB, indicating that similar extinction ratio should be obtained for MZIs in the switching matrix. The switching matrix of the silicon PIC is realized by cascading several MZIs, and as a result, an extinction ratio much larger than 35 dB to the spatial crosstalk should be obtained after the switch. The measured crosstalk of the silicon PIC is −30 dB, indicating that the heating power for some MZIs in the switching matrix may not be well optimized. Thus, further careful optimization of the heating power will greatly reduce the crosstalk, and therefore reduce the power penalty accordingly. In addition, polarization variation results in wavelength dependent sensitivity that can be greatly improved by polarization diversity technology23,24,25,26. The power consumption and switching speed are very important for optical fiber network nodes. In this work, the switching power for a single MZI is not very low, due to that a thick silicon dioxide layer is introduced between the silicon waveguide and the Ti heaters to avoid metallic loss. More efficient heater designs27,28,29,30 can be used to reduce the power consumption. The low switching speed in the current work may be attributed to the thick BCB bonding layer, which has relatively low thermal conductivity. The switching time can be improved by thinning down the BCB layer. On the other hand, improved design that directly integrates thermal heaters on silicon waveguide is a promising solution to provide fast switching speed31. Other heater materials, such as graphene can also be used as an efficient heater with fast switching time32.

The current device can be upgraded to switch two MCFs by adding more MZIs into the switching matrix, as shown in Fig. 7(a). MCF 1 and MCF 2 can be freely switched and routed to the corresponding output MCF. As an example, MCF 1 is switched to MCF 1 output on cross configuration through the solid line routing paths, and at the same time, MCF 2 is switched to MCF 2 output on bar configuration through the dash line routing paths. The same upgraded device can also be used as a real MCF ROADM module. As shown in Fig. 7(b), seven spatial channels from the input MCF can be dropped to the MCF drop output through solid line routing paths, and data can be added from the adding MCF to the MCF output through the dash line routing paths.

(a) Topology of a silicon switch device for switching of two MCFs. MCF 1 is switched to the output MCF 1 by cross configuration through solid line routing paths, and at the same time, MCF 2 is switched to output MCF 2 by bar configuration through dash line routing paths. (b) The device can also be used as a ROADM for MCFs. The seven channels of the input MCF can be dropped to the MCF drop output through solid routing paths, and the data can be added simultaneously from an add MCF to the MCF output through dash routing paths.

We achieved very high performance in the C band. The transmission drops in L band because of the limited coupling bandwidth of the grating coupler, as shown in Fig. 4. In order to increase the bandwidth, one has to increase the coupling bandwidth of the grating coupler. First, one could use hybrid silicon/silicon nitride (Si/Si3N4) platform, where silicon waveguide can be an efficient heating sensitive element for effective phase tuning, and Si3N4 grating couplers33 or Si3N4-on-SOI dual-level grating coupler with 100 nm coupling bandwidth34 can be used to couple with MCF. In addition, subwavelength structure can be used to extend the bandwidth as well to over 100 nm35,36. We have addressed this point in the discussion section.

In the optical fiber networks nowadays, WDM and polarization division multiplexing (PDM) has been widely investigated. Thus, it is important that SDM should be compatible with WDM and PDM. In order to be compatible with polarization division multiplexing, a solution is to use two-dimensional grating coupler37 as polarization splitter/combiner for coupling with each core. As shown in Fig. 8(a), the two orthogonal polarizations, i.e. s- and p- polarized light, from each core is split. The s- and p- polarized spatial channels can be freely switched independently in the switching matrix. After switching, the s- and p- polarized channels are recombined by the polarization combiner, and coupled to the corresponding cores of the multicore fiber. Figure 8(a) shows a scheme to realize cross-configuration for both s- and p- polarized channels (core 1 at the input is connected to core 7 at the output, core 2 to core 6, etc.). When the same switching configuration is deployed for both s- and p-polarization channels, polarization diversity switch is formed to realize polarization independent SDM switch38. Similar strategy can be utilized to realize compatibility with wavelength division multiplexing, as presented in Fig. 8(b). The WDM channels from each core are first wavelength demultiplexed. The spatial channels at the same wavelength are switched through the corresponding reconfigurable SDM switching matrix proposed in the manuscript. After switching, the spatial channels at each wavelength are assigned to the corresponding wavelength multiplexer. The switched spatial WDM channels are multiplexed and coupled to the corresponding core of the multicore fiber.

(a) PDM compatible SDM switching. The s- and p- polarized spatial channels split from each core is freely switched independently in the switching matrix. After switching, the s- and p- polarized channels are recombined by the polarization combiner, and coupled to the corresponding cores of the multicore fiber. Here cross-configuration is deployed for both s- and p- polarized channels realizing polarization diversity based polarization independent SDM switch. (b) WDM compatible SDM switching. The WDM channels from each core are first wavelength demultiplexed. The spatial channels at the same wavelength are switched through the corresponding reconfigurable SDM switching matrix, and assigned to the corresponding wavelength multiplexer. The switched spatial WDM channels are multiplexed and coupled to the corresponding core of the multicore fiber.

Our current SDM switching is for spatial dimension in cores of MCF. Future SDM technology based high-capacity fiber communication would take advantage of spatial dimension in both mode and core of a fiber3. Thus SDM switching for multicore few-mode fibers (FMF) is important. The grating coupler array based few-mode multiplexer for FMF has been demonstrated on SOI platform39,40. By incorporating the few-mode multiplexer with our proposed switching matrix, switching for FMF-MCF could be realized. But one has to consider the modal coupling during FMF transmission, and dedicated design of FM-MCF with low modal crosstalk is required.

The cost is one of the most important factors for silicon photonics. The cost may increase based on our current fabrication process using flip-bonding method, even though our yield of flip-bonding is quite good. The cost could be reduced by introducing Al mirror during SOI wafer fabrication. In addition, the fully etched grating coupler design also helps reducing the cost, since the whole silicon integrated circuit is fabricated in a single step of e-beam lithography-based nano-fabrication process.

In summary, we have designed and fabricated a novel silicon PIC for MCF switching. The silicon PIC is fabricated on a novel SOI platform with Al mirror. Low insertion loss with high extinction ratio and low crosstalk is obtained over a large bandwidth. We have demonstrated BER performance lower than 10−9 when transmitting 1 Tb/s/core in a 2-km MCF and switching all the cores in different configurations using the silicon PIC, constituting a first demonstration of an integrated device with this functionality. The proposed device can be upgraded to support additional features such as switching several MCFs and thus providing true MCF ROADM functionalities, which will be extremely useful for future MCF networks.

Methods

Silicon-on-insulator wafer with Al mirror

The silicon-on-insulator wafer with buried Al mirror was fabricated by flip-bonding method. A silicon dioxide layer with optimum thickness of 1.6 μm was first deposited by plasma-enhanced chemical vapor deposition (PECVD) on the commercial SOI wafer, which has 250 nm thick top silicon layer on 3 μm thick buried oxide layer. Al mirror was sputtered by e-beam afterwards. After that, a second layer of silicon dioxide with 500 nm thickness was deposited. The SOI wafer and a carrier silicon wafer are then both spun with 500 nm benzocyclobutene (BCB) layer, and the SOI wafer was then flip-bonded to the carrier silicon wafer. The bonded wafers are put into an oven for BCB hard curing. The substrate of the SOI wafer was then removed by dry etching. The new silicon-on-insulator with Al mirror was finally obtained by buffered hydrofluoric acid (BHF) wet etching of the buried oxide layer of the original SOI wafer.

Silicon PIC fabrication

The silicon PIC circuit was fabricated on the new silicon-on-insulator wafer with Al mirror. A single step of standard SOI processing, including e-beam lithography and inductively coupled plasma (ICP) etching was first used to fabricate the whole silicon PIC simultaneously. A 1500 nm thick layer of SiO2 was then deposited on top of the chip. The chip surface was then polished, and the top SiO2 was thinned down to 1 μm accordingly. The 1 μm is used as an isolation layer from the Ti heaters fabricated later to avoid potential optical losses. Afterwards, the 100 nm thick titanium heaters are formed by e-beam lithography followed by metal deposition and liftoff process. Then the thick Au/Ti contact layer was fabricated by UV lithography followed by metal deposition and liftoff process. The chip was then cleaved and wire-bonded to a PCB board for test.

Additional Information

How to cite this article: Ding, Y. et al. Reconfigurable SDM Switching Using Novel Silicon Photonic Integrated Circuit. Sci. Rep. 6, 39058; doi: 10.1038/srep39058 (2016).

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

Essiambre, R.-J., Kramer, G., Winzer, P. J., Foschini, G. J. & Goebel, B. “Capacity limits of optical fiber networks”. J. Lightwave Technol. 28, 662–701 (2010).

Richardson, D. J., Fini, J. M. & Nelson, L. E. “Space division multiplexing in optical fibers”. Nature Photon. 7, 354–362 (2013).

Van Uden, R. G. H. et al. “Ultra-high-density spatial division multiplexing with a few-mode multicore fibre”. Nature Photon. 8, 865 (2014).

Takara, H. et al. “1.01-Pb/s (12 SDM/222 WDM/456Gb/s) crosstalk-managed transmission with 91.4-b/s/Hz aggregate spectral efficiency”. In European Conference on Optical Communication (ECOC), Amsterdam, Netherlands. Optical Society of America (OSA), paper Th.3.C.1 (16–20 September, 2012).

Kobayashi, T. et al. “2 × 344 Tb/s propagation-direction interleaved transmission over 1500-km MCF enhanced by multi-carrier full electricfield digital back-propagation”. In European Conference on Optical Communication (ECOC), London, UK. Institution of Engineering and Technology (IET) (doi: 10.1049/cp.2013.1691), paper PD3.E.4 (22–26 September, 2013).

Ding, Y. et al. “On-chip grating coupler array on the SOI platform for fan-in/fan-out of MCFs with low insertion loss and crosstalk”. Opt. Express 23, 3292–3298 (2015).

Sakaguchi, J. et al. “19-core fiber transmission of 19 × 100 × 172-Gb/s SDMWDM- PDM-QPSK signals at 305 Tb/s”. In Optical Fiber Communication Conference/National Fiber Optic Engineers Conference (OFC/NFOEC), Los Angeles, CA, USA. Optical Society of America (OSA), paper PDP5C.1 (4–8 March, 2012).

Abe, Y., Shikama, K., Yanagi, S. & Takahashi, T. “Low-loss physical-contact-type fan-out device for 12-core multicore fiber”. In European Conference on Optical Communication (ECOC), London, UK. Institution of Engineering and Technology (IET) (doi: 10.1049/cp.2013.1560), paper P.1.7 (22–26 September, 2013).

Thomson, R. R. et al. “Ultrafast laser inscription of a 121-waveguide fan-out for astrophotonics”. Opt. Lett. 37, 2331–2333 (2012).

Jin, C. et al. “Efficient annular cladding amplifier with six, three-mode cores”. In European Conference on Optical Communication (ECOC), Valencia, Spain. Institute of Electrical and Electronics Engineers (IEEE) (doi: 10.1109/ECOC.2015.7341680), paper PDP.2.1 (September 27–October 1, 2015).

Abedin, K. S. et al. “Cladding-pumped erbium-doped multicore fiber amplifier”. Opt. Express 20, 20191–20200 (2012).

Suzuki, K. et al. “Ultra-compact 8 × 8 strictly-non-blocking Si-wire PILOSS switch”. Opt. Express 22, 3887–3894 (2014).

Chen, L. & Chen, Y.-K. “Compact, low-loss and low-power 8 × 8 broadband silicon optical switch”. Opt. Express 20, 18977–18985 (2012).

Saito, K. et al. “Multi-core fiber based pluggable add/drop link using rotational connector”. In Optical Fiber Communication Conference (OFC), Los Angeles, CA, USA. Optical Society of America (OSA), paper M2B.2 (22–26 March, 2015).

Fontaine, N. K. et al. “Heterogeneous space-division multiplexing and joint wavelength switching demonstration”. In Optical Fiber Communication Conference (OFC), Los Angeles, CA, USA. Optical Society of America (OSA), paper Th5C.5 (22–26 March, 2015).

Ryf, R. “SDM components and MIMO experiments in multimode and multicore fibers”. In European Conference on Optical Communication (ECOC), Cannes, France. Institute of Electrical and Electronics Engineers (IEEE) (doi: 10.1109/ECOC.2014.6964244) paper Th.2.1.1 (21–25 September, 2014).

Nelson, L. et al. “Spatial superchannel routing in a two-span ROADM system for space division multiplexing”. J. Lightwave Technol. 32(4), 783–789 (2014).

Liu, M. & Chiang, K. S. “Nonlinear switching of ultrashort pulses in multicore fibers”. IEEE J. Sel. Top. Quantum Electron. 47(12), 1499–1505 (2011).

Fernandes, G. M., Muga, N. J., Rocha, A. M. & Pinto, A. N. “Switching in multicore fibers using flexural acoustic waves”. Opt. Express 23, 26313–26325 (2015).

Ding, Y., Peucheret, C., Ou, H. & Yvind, K. “Fully etched apodized grating coupler on the SOI platform with −0.58 dB coupling efficiency”. Opt. Lett. 39, 5348–5350 (2014).

Xu, F. & Poon, A. W. “Silicon cross-connect filters using microring resonator coupled multimode-interference-based waveguide crossings”. Opt. Express 16, 8649–8657 (2008).

Ding, Y., Ou, H., Xu, J. & Peucheret, C. “Silicon photonic integrated circuit mode multiplexer”. IEEE Photon. Technol. Lett. 25, 648–651 (2013).

Ding, Y., Huang, B., Ou, H., Da Ros, F. & Peucheret, C. “Polarization diversity DPSK demodulator on the silicon-on-insulator platform with simple fabrication”. Opt. Express 21, 7828–7834 (2013).

Kim, S.-H. et al. “Compact 2 × 2 polarization-diversity Si-wire switch”. Opt. Express 22, 29818–29826 (2014).

Suzuki, K. et al. “Polarization-rotator-free polarization-diversity 4 × 4 Si-Wire Optical Switch”. IEEE Photon. Journ. 8, 0600707 (2016).

Tanizawa, K. et al. “Off-chip polarization-diversity 4 × 4 Si-wire optical switch with digital DGD compensation”. IEEE Photon. Technol. Lett. 28(4), 457–460 (2016).

Geng, M. et al. “Four-channel reconfigurable optical add-drop multiplexer based on photonic wire waveguide”. Opt. Express 17, 5502–5516 (2009).

Dong, P. et al. “Thermally tunable silicon racetrack resonators with ultralow tuning power”. Opt. Express 18, 20298–20304 (2010).

Dong, P. et al. “Low power and compact reconfigurable multiplexing devices based on silicon microring resonators”. Opt. Express 18(10), 9852–9858 (2010).

Gan, F. et al. “Maximizing the thermo-optic tuning range of silicon photonic structures”. In Photonics in Switching (PS), San Francisco, CA, USA. Institute of Electrical and Electronics Engineers (IEEE) (doi: 10.1109/PS.2007.4300747) paper TuB3.3 (19–22 August, 2007).

Watts, M. R. et al. “Adiabatic resonant microrings (ARMs) with directly integrated thermal microphotonics”. In Conference on Quantum electronics and Laser Science Conference (CLEO/QELS), Baltimore, Maryland USA. Optical Society of America (OSA), paper CPDB10 (May 31–June 5, 2009).

Gan, S. et al. “A highly efficient thermo-optic microring modulator assisted by graphene”. Nanoscale 7, 20249–20255 (2015).

Doerr, C. R. et al. “Wide bandwidth silicon nitride grating coupler”. IEEE Photon. Technol. Lett. 22, 1461–1463 (2010).

Sacher, Wesley D. et al. “Wide bandwidth and high coupling efficiency Si3N4-on-SOI dual-level grating coupler”. Opt. Express 22, 10938–10947 (2014).

Zhong, Q. et al. “Focusing-curved subwavelength grating couplers for ultra-broadband silicon photonics optical interfaces”. Opt. Express 22, 18224–18231 (2014).

Chen, X. et al. “Wideband subwavelength gratings for coupling between silicon-on-insulator waveguides and optical fibers”. Opt. Lett. 37, 3483–3485 (2012).

Pathak, S., Vanslembrouck, M., Dumon, P., Van Thourhout, D. & Bogaerts, W. “Compact SOI-based polarization diversity wavelength de-multiplexer circuit using two symmetric AWGs”. Opt. Express 20, B493–B500 (2012).

Tanizawa, K., Suzuki, K., Ikeda, K., Namiki, S. & Kawashima, H. “Novel polarization diversity without switch duplication of a Si-wire PILOSS optical switch”. Opt. Express 24, 6861–6868 (2016).

Ding, Y., Ou, H., Xu, J. & Peucheret, C. “Silicon photonic integrated circuit mode multiplexer”. IEEE Photon. Technol. Lett. 25, 648–651 (2013).

Koonen, A. M. J., Chen, H., van den Boom, H. P. A. & Raz, O. “Silicon photonic integrated mode multiplexer and demultiplexer”. IEEE Photon. Technol. Lett. 24, 1961–1964 (2012).

Acknowledgements

This work is supported by the Danish Council for Independent Research (DFF-1337-00152 and DFF-1335-00771) and the ECFP7 grant no. 619572, COSIGN. We would like to thank Optoscribe for providing the integrated fan-out device.

Author information

Authors and Affiliations

Contributions

Yunhong Ding proposed the idea, designed and fabricated the silicon photonic integrated circuit. Yunhong Ding, Valerija Kamchevska, Feihong Ye, Rameez Asif, and Michael Galili implemented the system experiment. Kjeld Dalgaard designed the microcontroller board. Simon Gross and Michael J. Withford provided the 3D waveguide based MCF coupler. Toshio Morioka provided the MCF. Yunhong Ding and Leif Katsuo Oxenløwe supported the project. Yunhong Ding, Valerija Kamchevska, Michael Galili, Toshio Morioka, and Leif Katsuo Oxenløwe discussed the results and contributed to the writing of the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Ding, Y., Kamchevska, V., Dalgaard, K. et al. Reconfigurable SDM Switching Using Novel Silicon Photonic Integrated Circuit. Sci Rep 6, 39058 (2016). https://doi.org/10.1038/srep39058

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep39058

This article is cited by

-

Design and performance analysis of lithium niobate waveguide-based serial parity generator and checker

Journal of Optics (2023)

-

Petabit-per-second data transmission using a chip-scale microcomb ring resonator source

Nature Photonics (2022)

-

Silicon chip-scale space-division multiplexing: from devices to system

Science China Information Sciences (2018)

-

On-chip silicon polarization and mode handling devices

Frontiers of Optoelectronics (2018)

-

Space division multiplexing chip-to-chip quantum key distribution

Scientific Reports (2017)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.