Abstract

Slime mould Physarum polycephalum is a single cell visible by the unaided eye. Let the slime mould span two electrodes with a single protoplasmic tube: if the tube is heated to approximately ≈40 °C, the electrical resistance of the protoplasmic tube increases from ≈3 MΩ to ≈10,000 MΩ. The organism’s resistance is not proportional nor correlated to the temperature of its environment. Slime mould can therefore not be considered as a thermistor but rather as a thermic switch. We employ the P. polycephalum thermic switch to prototype hybrid electrical analog summator, NAND gates and cascade the gates into Flip-Flop latch. Computing operations performed on this bio-hybrid computing circuitry feature high repeatability, reproducibility and comparably low propagation delays.

Similar content being viewed by others

Introduction

Slime mould Physarum polycephalum is a large single celled organism1 whose amorphous body is able to form complex, optimised networks of protoplasmic tubules between spatially distributed nutrient sources. It has been demonstrated that the organism’s natural foraging behaviour may be characterised as distributed sensing, concurrent information processing, parallel computation and decentralized actuation2,3,4,5. The ease of culturing and experimenting with P. polycephalum makes this slime mould an ideal substrate for real-world implementations of unconventional sensing and computing devices2. A range of hybrid electronic devices have recently been implemented as experimental working prototypes. They include self-routing and self-repairing wires6, electronic oscillators7, chemical sensor8, tactical sensor9, low pass filter10, colour sensor11, memristor12,13, robot controllers14,15, opto-electronic logical gates16, electrical oscillation frequency logical gates17, FPGA co-processor18, Shottky diode19 and transistor13.

Several challenges still remain towards fabricating functionally useful slime mould computing devices. For example, the live substrate’s inherent variability renders cascading of various varieties of logical gate too unreliable for constructing complex computing circuitry. We detail here the creation of laboratory prototypes of functional, reliable electrically-coupled discrete and sequential logical devices that utilise slime mould as circuit elements. This was achieved through characterising bioelectrical output of slime mould protoplasmic tubes in response to an insulting stimulus—localised heating. This rationale was based on the principle that the organism is able to isolate portions of its body (transiently and permanently) in response to harmful stimuli by ceasing the rhythmic movements of cytoplasm through certain anatomical regions—which usually serves to distribute the contents of the cell and contribute to the production of motive force—hence isolating them from metabolically active regions of the cell. Isolated protoplasmic tubes have a significantly higher electrical resistance than their unaltered counterparts20, which provides a basis for distinguishing between logical states when monitoring bioelectrical activity.

Results and Discussion

Response of P. polycephalum to heat

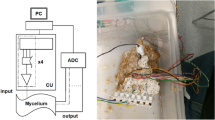

The resistance of a protoplasmic tube was found to increase when exposed to temperatures exceeding approximately 25 °C. The glass tube temperatures of a H-tube device (Fig. 1) exceeding 70 °C (69.3 ± 0.6 °C when heating element current was set to 1.3A) (Fig. 2a) were found cause irreparable damage to protoplasmic tubes. Heat input of approximately 40 °C (0.8A) was found to be the most appropriate compromise between response speed whilst causing negligible damage to the organism (Fig. 2a), because it allowed the slime mould to reform promptly and be re-stimulated repeatedly over duty cycles extending for approximately 3000s. Figure 2b shows the voltage drop and resistance responses of a H-tube to heating to this degree: response times were found to be 190 ± 9s (which is relatively rapid for Physarum computing devices16,17,21) and were independent to holding times at this value, although reforming times were found to be proportional to holding time (Fig. 3).

Response time and reforming time of H-tube depending on the applied current and the holding time.

(a) Response time of H-tube 1 under 0.8 A current. (b) H-tube 1 reforming times (0.8 A). (c) Response time of H-tube 2 under 1.3 A current. (d) H-tube 2 reforming times (1.3 A). Shown data are averages and all dashed lines represent for the standard deviation (n = 3).

The resistance of a resting H-tube was found to be stable with an average of 2.27 ± 0.30 MΩ for the 20 mm distance covered by a protoplasmic tube. Under heat-stimulation, the resistance values of a H-tube fluctuated significantly with some peaking at 300,000 MΩ. However, without taking into account these bursts, the average resistance was 9,450 ± 5,000 MΩ, usually fluctuating between 7,000 and 15,000 MΩ. Despite this variability, the values attained were sufficient to reliably distinguish between resting and stimulated states.

It was found, however, that for each H-tube to respond promptly to heat simulation, it was required to have had previous exposure to such a stimulus: this apparently adaptive response was conditioned into each experimental organism by exposing it to heat generated by a 0.9 A current until a positive response was measured, after which the temperature was maintained for 300 s in order to enhance reproducibility between different organisms. We considered this phase as an entrainment of P. polycephalum towards heat stimulation. P. polycephalum changes its resistance in response to heat. Therefore it can be regarded as a living thermistor. Its response to heat-stimulation only occurred if the temperature increased over a threshold specific to the physiological state of P. polycephalum (thickness and number of protoplasmic tubes), however. Since P. polycephalum resistance was not proportional to temperature, it cannot be considered as a ‘pure’ thermistor, but as a thermic switch. The mechanisms behind the temperature sensitivity and the resistive variations are yet to be determined, although historical literature indicates the synthesis of heat-shock proteins in response to temperatures exceeding 32 °C22 presumably allow the organism to acclimatise to such stimuli.

Boolean logical gates

Two-ways analogue NAND logic

To balance the response and reforming time in response to heat stimulation, the duty-cycle of the setup was as follows: resting condition for 10 min (no current), stimulated conditions for 8 min (5 + 3 mins; 0.8 A; Fig. 4a). Under the applied running conditions, both of the tested setups (H-tube1 and H-tube2) demonstrated reproducible and stable response behaviour to heat stimulation (Fig. 5). With a reforming time of 10 min, the resistance reached by the H-tubes was of ≈25 MΩ. The resistance of the H-tube under stimulation was of ≈10,000 MΩ.

Even though these resistances were high, the difference was sufficient for the behaviour to be interpreted as a NAND logic: outputs (voltage) are high when input (current) configuration is 〈0, 0〉, 〈0, 1〉, 〈1, 0〉; the outputs are low when input (current) configuration is 〈1, 1〉 (0 = no current, 1 = current applied to heating element). As it is an analogue setup, the high outputs comprise three levels: 〈0, 0〉 condition results in the highest voltage output value; 〈0, 1〉, 〈1, 0〉 conditions have a voltage outputs comprised between high and low outputs and are defined as medium outputs. However, because both H-tubes had comparable physiological states, their respective resistance responses were varying at similar levels. Therefore, the 〈0, 1〉 and 〈1, 0〉 conditions had equivalent voltage output Q and could not be deduced from the OpAmp output: 419 ± 7.5 mV 432 ± 23.5 mV, respectively. Nonetheless, results demonstrate that the H-tube response to heat could be interpreted as analogue NAND logic, with a duty cycle of 18 min whereby the response and reforming times were balanced (Fig. 5).

Three-ways analogue NAND logic

Due to the limitations of the measuring equipment (c.a. +/−2250 mV) and to the need for a sufficient spread of various output voltages, the third H-tube was not connected to the same OpAmp as the two first ones: the two first H-tubes were connected to one OpAmp, the output of which was then connected to a second OpAmp in parallel to the third H-tube. However, this setup was equivalent to a three inputs OpAmp system adapted to the data logging apparatus (Fig. 4b).

In order to have a specific output voltage for each logic combination, the H-tubes chosen for the three-way NAND gate had different physiological states (i.e. thickness and number of protoplasmic tubes; see resulting voltage from Input currents = 0 in Table 1). Results confirmed that when the organism had different physiological states the voltage output levels were specific to each logical combination (Kruskal-Wallis test, p < 0.0001; Table 1). Indeed, each of the 〈0, 0, 1〉, 〈0, 1, 0〉, 〈1, 0, 0〉, 〈1, 1, 0〉, 〈0, 1, 1〉, 〈1, 0, 1〉 conditions had different medium voltage outputs Q (Table 1). Therefore, the voltage outputs could be interpreted as analogue NAND logic with each inputs condition identifiable from the output voltage. Since different, each output could be routed to other components of a larger electronic setup.

Cascading logic gates

Tsuda et al. achieved the first ever P. polycephalum logic gate in 200421. This benchmark was based on the growth of a protoplasmic tube in a pre-determined, “programmable” physical environment whose topology and nutrient distribution dictated the manner of the organism’s growth: logical output was interpreted by the presence/absence of protoplasmic tubes in specific areas, equating to 1 and 0 respectively. This experimental setup had a time response ranging from 11 h to 18 h and gate cascading and re-programming were not achieved, as the use of chemical inputs renders such systems un-dynamic and un-reprogrammable. Whilst more dynamic systems have since been demonstrated—such as in16, where light was used as a reconfigurable input to a plasmodium to guide its migration between live electrodes and hence the organism played dual role of logical component and electrical conductor—these devices still suffer from extremely long propagation delays.

That is not to say that computation speed in slime mould logical devices cannot be improved; when the intrinsic flow variation of P. polycephalum’s cytoplasm streaming is employed as data, such as in17,23, wherein either the frequency change of oscillatory period of shuttle streaming upon stimulation (through light, heat and nutrient-based inputs) or the capacity of P. polycephalum to control its cytoplasm’s flow-path upon mechanical stimulation are used as logical values. These studies have reduced the computation time to the minute and second scale, 20–30 min and 54 s respectively. Moreover, these prototypes were not limited by the slime mould’s growth speed since they were employing an already existing protoplasmic network. However, both of these examples require an external interface (software or camera, respectively) to interpret the data outputs prior becoming the data input of the cascading gate. In comparison, the bio-logic gates developed here were employing data inputs and outputs of identical nature (electricity) and were not limited by a pre-programmed physical environment (H-tube are “reprogrammable”), by the growth speed of P. polycephalum (small but stable network of protoplasmic tubes), or by an external interface (gate can be cascaded one into the following one by a simple wire). The response time of the H-tubes was shown to be relatively short: from 94 to 360 s with 100% certainty in the data output. Since this “reprogrammable” setup had an analogue base, the computation speed could be increase simply by adjusting to lower levels the switching thresholds (resistance). Nonetheless, because of these characteristics the H-tubes were employed to test combinatorial cascades. The practical implementation of bio-logic computation was investigated with the AND and NAND logic gates.

AND to AND

The relay of the first gate was connected open to the coil of the second gate (Fig. 4c). In this context, when the voltage output of the first OpAmp was ≤10 mV the relay was switched to the closed position, thus heating the coil of one of the H-tubes in the cascading gate. Therefore, when the first gate was 〈1, 1〉, the following H-tube of the second gate became 1 (Fig. 6a). When the three H-tubes were switched to Current Input = 0, the propagation delay, for the H-tube B1 (first *, Fig. 6a) to switch to Current Input = 0, was of 18 ± 8 s. The propagation delay, for the output Q of the second AND gate (first **, Fig. 6a) to switch to Current Input = 0 after B1 switched to Current Input = 0, was of 62 ± 5 s. Thus, the overall propagation delay of the cascading AND gates was of 80 ± 5 s. The propagation delay, for the H-tube B1 (second *, Fig. 6a) to switch to Current Input = 1, was of 62 s ± 25 s. The propagation delay, for the H-tube B1 (second **, Fig. 6a) to switch to Current Input = 1, was of 78 s ± 19 s. The data shown in Fig. 6a are averages of three succeeding duty cycles. Therefore, the initial part of the graph illustrates the robustness of the setup resilience. In the case of an AND cascading into AND gate, the propagation of the information essentially depends on the response time of P. polycephalum to heat, whereas the reset of the setup is depending on the reforming time/speed of P. polycephalum.

Cascading logic gates illustrating the signal responses of the H-tubes to data inputs.

(a) Cascading AND gates. Error bars stand for the standard deviation (n = 3). (b) Cascading NAND gates. (c) Low SR NAND Gate Latch. The coloured sections indicate manual switching. The * represent the propagation delay of the first gate and ** the propagation delay of the second gate. In (a,b) the voltages of the gates (above 0 mV) are arbitrary values indicating when the coils were switched on. In (c) the curves above 0 mV are the measured voltages of the coils.

NAND to NAND

In the case of a NAND cascading into a NAND, the relay of the first gate was connected in closed position to the coil of one of the H-tube in the cascading gate (Fig. 4c). This implies that the coil was always under 0.8 A and that when the voltage output of the first OpAmp was ≤10 mV the relay was switch into open position. Set as such, the gate acted as a NAND: the coil of the cascading H-tube (B1) was a 0 only when the first gate had both inputs as 1.

A NAND gate cascading into a NAND gate implies that most of the time of the cascading input of the second NAND gate is under heat stimulation (B1, Fig. 6b). The propagation delay of Q′ was therefore longer when the computation was only dependent on the reforming time of B1 (c.a. B2 was 1; second * in Fig. 6b). After 85 min of heat stimulation the reforming speed of B1, even though 30% slower than at the start of the experiment, was yet sufficiently quick to be employed for computational purposes.

In this experiment the Undefined State of the Low SR NAND Gate Latch was not investigated, but all other states were with the following sequence, expressed as (S, R) = (Q, Q′): (1, 0) = (0, 1), (1, 1) = (0, 1), (0, 1) = (1, 0) and (1, 1) = (1, 0). All these conditions were maintained during 10 minutes. The propagation delay to pass from Reset (Q, Q′ = 0, 1) to Set state (Q, Q′ = 1, 0) was 240 ± 40 s (* in Fig. 6c). This propagation delay mainly depended on the reforming speed of S and the response time of Q. The propagation delay to pass from Set state to Reset state was 385 ± 55 s (** in Fig. 6c). This propagation delay mainly depended on the reforming speed of R and the response time of Q′.

As discussed previously (Fig. 3), the main limiting factor to a quicker propagation delay, in these setups, is the reforming speed of P. polycephalum after a heat stimulation. This reforming speed could be faster with a lower current input (i.e. lower temperatures), but then it would be the response time to heat that would become limiting. Another approach that could be pursued would be to have thinner (i.e. smaller diameter glass tube) and shorter (i.e. length of the glass tube) protoplasmic tubes.

Conclusions

The results presented demonstrate direct cascading setups employing the biological response of P. polycephalum to stimulation. In the present case, it was the response to heat that was exploited to build the hybrid gates with living slime mould. The full duty cycle, from the heat response to reforming, was of ±40–60 min. Besides, results have shown that in order to implement this heat stimulation as a data input in slime mould hybrid gates, the reforming time can be shorten by ≈75% for it to be balanced with the response time to stimulation. To exploit this heat response for implementing Boolean logic, P. polycephalum was employed as “heat-switch” connected in pair to a summing amplifier. Furthermore, as the input and output voltage levels were not compatible for cascading the gates, a comparator and a relay were employed. The resulting gate comprised two individuals of P. polycephalum, a summing amplifier, a comparator and a relay.

The present study reports AND to AND and NAND to NAND cascading gates, either as linear cascades or as a low SR NAND gate Flip-Flop latch. In the latter configuration, the propagation delays were of 240–380 ± 55 s. These gates were shown to be reliable and resilient, thus leading to the run of multiple duty cycles with the same setups, whilst producing reproducible results from one duty cycle to another. Our observation of an adaptive response which sensitises the organism to the application of heat stimuli is consistent with contemporary knowledge of the organism’s ability to periodic stimuli24. Therefore, the necessary entrainment stage of these devices’ operation could be interpreted as analogous to memory—like loading a program into the organism’s prior to it being run—but would require further investigation to decipher if this “adaptive memory” is not the simple consequence of any passive metabolite accumulation in the protoplasmic tubes.

Methods

Culturing Physarum polycephalum

P. polycephalum was kept in constant plasmodial growth phase by regular sub-culturing, 1–2 times per week, on non-nutritive agar plates (2%). These agar-containing Petri dishes comprised five blobs (≤5 mm diameter) of sterile porridge as food sources and were kept in dark at 22 ± 0.5 °C. When required, a subsample was employed to inoculate, under sterile conditions, sterile vessels specifically designed to apply heat to P. polycephalum protoplasmic tubes and measure its response (H-Tubes; see next paragraph). The porridge was prepared by adding 20 mL of deionised autoclaved water to 20 g of three-time autoclaved oat flakes. Once the mixture had set thickly, it was autoclaved once more. This thick texture allowed cutting small squares of the needed size and facilitate re-spiking/inoculation.

Experimental environment

An enclosed, heat-resistant, electrically insulative environment was designed to enable the growth of plasmodial tubules between two electrodes. This P. polycephalum heat switch device (H-tube) (Fig. 1) comprised of two 10 mm diameter 3D-printed wells, each holding 500 μl of sterile agar whose surface was levelled to the bottom of a 6 mm external diameter glass tube which connected the two wells. The glass tubes were 20 ± 0.3 mm in length and had a coil of 45 × 0.2 mm nickel wire wrapped about their centre, which functioned as a heating element. Pieces of sterile porridge were added in both wells and one of the two was inoculated with P. polycephalum. Both wells were then sealed with paraffin film. The bottom of each well was laid with aluminium tape, one end of which was accessible from the outside of the device, to serve as the signal carrier. Hence, when the organism propagated from one well to the other, it formed at least one protoplasmic tube between the wells, allowing for electrical measurements to be made non-invasively along the length of the organism. Measurements were performed with a PicoLog ADC-24 24-bit resolution data logger (Pico Technology, UK): input channels were set to ±2250 mV recording limits and were ground referenced. As there was significant discrepancy between the device’s internal resistance (1 MΩ) and that of the protoplasmic tubes (≈3 MΩ), a voltage follower was adapted into the signal path.

Response of P. polycephalum to heat

In preliminary experiments, H-tubes were exposed to a range of heat levels—adjusted by varying the current passing through the nickel wire—for differing periods of time whilst concurrently measuring bioelectrical activity of the constituent protoplasmic tube, in order to assess the organism’s electrical responses to the stimulus. The protoplasmic tube was loaded with −2.25 V and the voltage drop across the organism was monitored in response to heat changes; temperature of the glass tube was concurrently measured using a Fluke 87 V multimeter. This methodology was chosen in order to assess the optimum temperature for substantially affecting functionality of the protoplasmic tube—hence causing its resistance to raise to such a degree that the measured voltage drops significantly—that it reacts rapidly, but is not so damaged that it could not revert to a normal state once the insulting stimulus has been removed.

Hybrid circuitry

Design

The input states of the gates were set via the use of heater coils placed around the glass tubes the P. polycephalum were grown in (Fig. 1). A negative voltage of −2.25 V was applied to one end of these tubes which formed potential dividers in conjunction with 10 MΩ resistors. The resultant voltages derived were immediately buffered via unity gain amplifiers to remove any possible errors due to the impedance loading of the instrumentation (not shown on the circuit diagrams in Fig. 4). The buffered signals were then fed into a summing amplifier (OpAmp) with the gain set to minus a half of the summed input voltages (Fig. 4a). Due to the high resistivity of protoplasmic tubes, it was not possible to employ P. polycephalum as a data carrier. Hence, each device consisted of two electrical circuits: the first consisted of a voltage supply for loading the protoplasmic tubes with a constant −2.25 V and the second was the current source for the heating elements, which comprised the devices’ inputs; this prevented the devices being directly cascaded. To overcome this problem, the signal from the summing amplifier was passed onto a simple comparator circuit which controlled the heater supply of a P. polycephalum output tube via a transistor driven relay circuit, depending on the applied voltage and the threshold set via a potentiometer (Fig. 4c). The following devices were evaluated: OpAmp adder (summing amplifier), three-input OpAmp adder and variable-configuration logical gate comprised of an OpAmp adder and comparator relay, the circuits for which are shown in Fig. 4.

Analogue logical gates

A two-input NAND gate was constructed using the device detailed in Fig. 4a. Its functionality was as follows: outputs (current) are high and low when input (voltage) configuration is 〈0, 0〉, 〈1, 1〉, respectively, as with a conventional digital NAND gate. When only one input is high, however, the output voltage is a medium value between high and low. If logic levels are interpreted as high, i.e. above a certain threshold lying between the low and medium states, the output of the device is essentially equal to its digital equivalent, such that the output configuration is ¬(A.B). Evaluation of this gate was performed by setting the inputs to 〈0, 0〉, 〈0, 1〉, 〈1, 1〉 five times for 10, 5 and 3 minutes, respectively, without interruption in a single H-tube; the experiment was then repeated a further five times with the 5 minute phase in configuration 〈1, 0〉. Consequently, a three-input NAND gate was evaluated utilising the device shown in Fig. 4b. All possible combinations of input configuration were evaluated three times.

Cascading logic gates

The logical gate shown in Fig. 4c contained a comparator relay component for controlling heating elements, hence providing a coupling mechanism for cascading multiple gates. The logic level can be manually set as a voltage threshold with the integrated potentiometer. When viewed as a single logical gate, this device can be set up to function as AND or OR gates, plus their negated versions—NAND, NOR—via the switch for the heater supply: depending on whether the normally open or normally closed contacts of the relay were used, the NOT function was implemented. The following sequential logical circuits were constructed through cascading two gates:

-

AND to AND, such that ((A1.A2).B2) = (B1.B2) = Q.

-

NAND to NAND, such that ((A1.A2)′ B2)′ = (B1.B2)′ = Q′.

-

Low SR flip-flop (bistable) utilising two NAND gates, such that (S.R) = (Q.Q′).

Their evaluation was performed by subjecting them to repeated duty cycles.

Additional Information

How to cite this article: Walter, X. A. et al. On hybrid circuits exploiting thermistive properties of slime mould. Sci. Rep. 6, 23924; doi: 10.1038/srep23924 (2016).

References

Stephenson, S.-L., Stempen, H. & Hall, I. Myxomycetes: a handbook of slime molds. (Timber Press: Portland, Oregon,, 1994).

Adamatzky, A. In Physarum machines: computers from slime mould, vol. 74 (ed. Adamatzky, A. ) (World Sci. Ser. Nonlinear Sci. Ser. A, 2010).

Adamatzky, A. In Advances in Physarum machines: Sensing and computing with slime mould (ed. Adamatzky, A. ) (Springer, 2016).

Adamatzky, A. Tactile bristle sensors made with slime mold. IEEE Sens. J. 14(2), 324–332 (2014).

Adamatzky, A. A would-be nervous system made from a slime mold. Artif. Life 21(1), 73–91 (2015).

Adamatzky, A. Physarum wires: Self-growing self-repairing smart wires made from slime mould. Biomed. Eng. Let. 3(4), 232–241 (2013).

Adamatzky, A. Slime mould electronic oscillators. Microelectron. Eng. 124, 58–65 (2014).

Whiting, J., de Lacy Costello, B. & Adamatzky, A. Towards slime mould chemical sensor: Mapping chemical inputs onto electrical potential dynamics of Physarum polycephalum. Sens. Actuators B Chem. 191, 844–853 (2014).

Adamatzky, A. Slime mould tactile sensor. Sens. Actuators B Chem. 188, 38–44 (2013).

Whiting, J., de Lacy Costello, B. & Adamatzky, A. Transfer function of protoplasmic tubes of Physarum polycephalum. Biosystems 128, 48–51 (2015).

Adamatzky, A. Towards slime mould colour sensor: Recognition of colours by Physarum polycephalum. Org. Electron. 14(12), 3355–3361 (2013).

Gale, E., Adamatzky, A. & de Lacy Costello, B. Slime mould memristors. BioNanoScience 5(1), 1–8 (2013).

Tarabella, G. et al. A hybrid living/organic electrochemical transistor based on the Physarum polycephalum cell endowed with both sensing and memristive properties. Chem. Sci. 6(5), 2859–2868 (2015).

Gale, E. & Adamatzky, A. Translating slime mould responses: A novel way to present data to the public. In Advances in Physarum Machines, vol. 74 (ed. Adamatzky, A. ) 777–788 (Springer, 2016).

Tsuda, S., Zauner, K.-P. & Gunji, Y.-P. Robot control: From silicon circuitry to cells. Biologically Inspired Approaches to Advanced Information Technology pages 20–32 (2006).

Mayne, R. & Adamatzky, A. Slime mould foraging behaviour as optically coupled logical operations. Int. J. Neural. Syst. 44(3), 305–313 (2015).

Whiting, J., de Lacy Costello, B. & Adamatzky, A. Slime mould logic gates based on frequency changes of electrical potential oscillation. Biosystems 124, 21–25 (2014).

Mayne, R., Tsompanas, M.-A., Sirakoulis G. C.-H. & Adamatzky, A. Towards a slime mould-FPGA interface. Biomed. Eng. Lett. 5(1), 51–57 (2015).

Cifarelli, A., Dimonte, A., Berzina, T. & Erokhin, V. Non-linear bioelectronic element: Schottky effect and electrochemistry. Int. J. Unconv. Comput. 10(5–6), 375–379 (2014).

Mayne, R. & Adamatzky, A. Toward hybrid nanostructure-slime mould devices. Nano LIFE 5(01), 1450007 (2015).

Tsuda, S., Aono, M. & Gunji, Y.-P. Robust and emergent Physarum logical-computing. BioSystems 73, 45–55 (2004).

Wright, M. & Tollon, Y. Heat sensitive factor necessary for mitosis onset in Physarum polycephalum (temperature shift/heat shock/cycloheximide/ts mutant). Mol. Gen. Genet. 163, 91–99 (1978).

Adamatzky, A. & Schubert, T. Slime mold microfluidic logical gates. Mater. Today 17(2), 86–91 (2014).

Pershin, Y. V., La Fontaine, S. & Di Ventra, M. Memristive model of amoeba’s learning. Phys. Rev. E. 80, 021926 (2010).

Acknowledgements

The authors gratefully acknowledge the EU Commission seventh Framework Program for funding the PhyChip Project (FP7-ICT-2011-8/316366).

Author information

Authors and Affiliations

Contributions

A.A. developed the original concept of employing P. polycephalum as bio-logic gates. X.A.W. developed the concept—and designed the adequate prototype—of employing the response of P. polycephalum to heat as the data input. X.A.W., A.A. and I.H. have participated to the experimental designs. X.A.W. conducted the experiments, collected data and produced the figures and wrote the draft manuscript. X.A.W., I.H., R.M., I.A.I. and A.A. were involved in the data analysis and interpretation. X.A.W., I.H., R.M., I.A.I. and A.A. edited and approved the final manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Walter, X., Horsfield, I., Mayne, R. et al. On hybrid circuits exploiting thermistive properties of slime mould. Sci Rep 6, 23924 (2016). https://doi.org/10.1038/srep23924

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep23924

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.