Abstract

Nano-floating gate memory devices (NFGM) using metal nanoparticles (NPs) covered with an insulating polymer have been considered as a promising electronic device for the next-generation nonvolatile organic memory applications NPs. However, the transparency of the device with metal NPs is restricted to 60~70% due to the light absorption in the visible region caused by the surface plasmon resonance effects of metal NPs. To address this issue, we demonstrate a novel NFGM using the blends of hole-trapping poly (9-(4-vinylphenyl) carbazole) (PVPK) and electron-trapping ZnO NPs as the charge storage element. The memory devices exhibited a remarkably programmable memory window up to 60 V during the program/erase operations, which was attributed to the trapping/detrapping of charge carriers in ZnO NPs/PVPK composite. Furthermore, the devices showed the long-term retention time (>105 s) and WRER test (>200 cycles), indicating excellent electrical reliability and stability. Additionally, the fabricated transistor memory devices exhibited a relatively high transparency of 90% at the wavelength of 500 nm based on the spray-coated PEDOT:PSS as electrode, suggesting high potential for transparent organic electronic memory devices.

Similar content being viewed by others

Introduction

Recently, organic field-effect transistor (OFET) type memory devices have been regarded as a potential candidate for next-generation memory devices because of their advantages of high portability and flexibility, easily integrating structure, non-destructive read-out characteristics and single device structure1,2,3,4,5,6,7,8. Different from the conventional OFET9,10, the OFET memory incorporates a distinct charge-storage layer for electrical programmable function, such as ferroelectric materials11,12, nano-floating gate dielectric or polymer-based electret1,6,13,14,15,16,17. Among them, the nano- floating gate architecture have been considered as a promise path to obtain high performance memory devices2,4,18,19,20,21,22, because the spatially discrete floating-gate elements effectively act as a charge trapping site5,18.

In addition to excellent charge trapping capability, optical transparency is another desirable feature for OFET memory23,24,25,26. In general, electronic devices with optical transparency provide the advantages for transparent electronics, such as smart glass electronic devices and wearable displays. An embeddable transparent nonvolatile memory devices is strongly demanded to realize highly transparent integrated systems requiring information storage. Previously, Kim and his coworkers5 embedded Au NPs (NPs) into a polymer dielectric as a charge storage layer for transparent NFGM devices. However, the Au NPs possessed a strong absorption in the visible region due to their strong surface plasmon resonance effects2,4,20,21,27. The devices with the Au NPs showed the transparency of 67%, which was much lower than that of the devices without the Au NPs (86%). To improve the transparency, Jang et al. reported NFGM devices using single-layer graphene as active channel and thermal-deposited ultra-thin discontinuous Au layer (6.7 nm) as a charge trapping layer to obtain high transparency transistor memory (up to 80%)23. Nevertheless, the highly energy-consumed process, e.g. thermal evaporation process, need to be avoided for environmental issue13,28,29. Alternatively, solution-processed transparent charge trapping layers have the advantage of low-cost and large-area fabrication. Recently, semiconducting nanoscale materials such conjugated polymer nanoparticles28 or cobalt ferrite nanoparticles16 made from solution process have been used as nano-floating gate. The devices performance are comparable to that of Au NPs, which shows the potential of semiconductor as charge trapping sites.

Zinc oxide have been considered as one of the leading candidates for electronics30 because it offers inexpensive synthesis, high crystallinity, transparency and a wide direct band gap (−3.4 eV). ZnO possesses a high transparency over 95% in the visible region, beneficial to the development of transparent electronics. Moreover, its low-lying lowest unoccupied molecular orbital (LUMO) energy level tends to be a strong electron acceptor. ZnO NPs have been employed for organic memory applications. Hirschmann et al. employed the ZnO NPs modified by ligand as a charge storage layer in OFET memory31. Nevertheless, the memory device showed a poor electrical isolation capability and sustain for only a few minutes. Although ZnO NPs have potential as a charge storage layer for memory applications, the charge retention characteristics need to be further improved.

Herein, we blend the hole-trapping polymer, poly (9-(4-vinylphenyl) carbazole) (PVPK), with transparent ZnO NPs for the NFGM devices to improve their memory performance. The ZnO NPs were synthesized from low-cost solution-based hydrothermal method and modified with n-butylamine, which was favour for the dispersion of the NPs in mixing solvents (chloroform/methanol). PVPK is highly transparent in visible region and has a rigid carbazole moiety which could play a role of a hole-trapping site. Hole/electron storage behavior could be realized through the ZnO-polymer nanocomposite. Additionally, the data retention ability in our system could be significantly enhanced by the method of embedded nanoparticles in insulated polymer layer. For comparison, we also prepared ZnO NP-based memory devices using a common insulating polymer, polystyrene (PS). Precise control and optimization of the ZnO loading amount could tune the memory window and maximize the On/Off current ratios between the programmed and erased states at Vg = 0 V. The experimental results suggested that the fabricated memory devices with a relatively high transparency, large memory window, high on/off current ratio, and reliable long term stability for organic nonvolatile memory device applications.

Results and Discussion

Preparation of ZnO NPs and characterizations

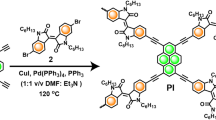

ZnO NPs were synthesized by hydrolysis and condensation of zinc acetate dihydrate by potassium hydroxide in methanol using a Zn2+: OH− ratio of 1:1.7 and n-butylamine as ligand (Fig. 1a)32. The ZnO NPs were dispersed in the polymer matrix using the mixing solvent system of chloroform and methanol at the ratio of 3:133. This process could prevent opaque thin film formation and lead to high transparency34. In X-ray diffraction pattern (See supporting information Figure S1), the peaks at 2θ = 31.72, 34.36, 36.18,47.44 and 56.5° are corresponding to the lattice planes (100), (002), (101), (102) and (110) of the hexagonal phase of ZnO35, respectively. This diffraction pattern indicates that the prepared ZnO NPs is the wurtzite crystal phase.

Sun et al. found that ZnO-PMMA composites without any ligand modification showed severe aggregation of ZnO NPs36. The ZnO NPs without being modified with the ligand show a quasi-spherical morphology and are severely aggregated with a diameter of 5.0–10.0 nm in PVPK matrix (Fig. 1b left). After modification with n-butylamine for ZnO NPs, the aggregation in the polymer matrix was suppressed (Fig. 1b right), indicating the significant impact of the ligand on the dispersion of ZnO nanocrystals. The less aggregation in the ligand-modified ZnO NPs may be attributed to the enhanced hydrophobicity of the nanocrystals, which improves the compatibility between the ZnO NPs and the polymer matrix34. Thus, the addition of n-butylamine to the nanocrystal solutions is critical to improve the optical properties Furthermore, the mixing solvent (chloroform/methanol) allows the nanocrystals to be dissolved in solution and ensuring the mixed solution of ZnO nanocrystals and PVPK to be homogenous, leading to the uniform composite films

Figure 1c shows the optical transmittance of the ZnO, PS, 20 wt%, 30 wt% ZnO/PS, PVPK, 20 wt% and 30 wt% ZnO/PVPK film. The film thickness was around 30–40 nm for each polymer nanocomposite. As shown in Fig. 1c, the samples showed high transparency from 380 to 780 nm, indicating that the ZnO nanoparticle composition does not affect the optical transmittance of the nanocomposite. This may be attributed to the well-dispersed NPs and less aggregation of the ZnO NPs. Note that the transmittance of spin-coated ZnO thin film is lower compared to those of others, which could be due to the light scattering of high-density NPs aggregated on the substrate surface.

To deeply understand the influence of the ZnO NPs and PVPK, we first studied the device performance and memory behavior of ZnO embedded in polystyrene (PS) matrix. PS is a common insulating dielectric materials without any specific functional groups for charge trapping, which is good polymer matrix to understand the memory behavior of ZnO NPs. Sequentially, the device behavior of the ZnO NPs/PVPK blends were investigated. The detailed results and discussion are shown in the following paragraphs.

Memory Devices Using ZnO/PS composites as Charge-Storage Layer

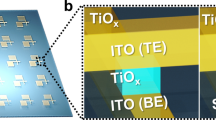

Figure 2a,b show an image and schematic illustration of the device structures, respectively. To prepare a transparent transistor, a thin-thickness (ca. 30 nm) pentacene crosslinked poly (4-vinylphenol) (cPVP) were used as a charge-transport layer and a dielectric layer, respectively. Poly(3,4-ethylenethiophene)-poly(styrenesulfonate) (PEDOT:PSS) transparent electrode was prepared by spray coating the solution through the shadow mask37. Figure 2a shows the image of the fabricated transparent memory device, which is as transparent as an ITO glass. The transmittance for the device at the wavelength of 500 nm is 90% and the average transparency of 85% over the range from 400 to 800 nm. The device shows a reduced transmittance (around 70%) at the wavelength of 670 nm, which is mainly contributed from the absorption of 30-nm-thick pentacene. This transmittance can be significantly improved when reducing the thickness of the pentacene film. Additionally, the surface morphology of these polymer nanocomposites were investigated using AFM techniques. The AFM images of the electret suggest that the composite film of ZnO/PS or ZnO/PVPK has a relatively smooth surface with the roughness below 2 nm (See supporting information Figure S2).

The transfer characteristics of the OFET memory devices using the ZnO/PS composite are shown in Fig. 3 and the detailed transfer characteristics are summarized in Table 1. The transfer curves exhibit a typical p-type accumulation mode with a good current modulation. The field-effect mobility (μ) values of the devices in the saturation region using the film with different ZnO composition (0, 10, 20 and 30 wt%), denoted as PS, ZnOPS10, ZnOPS20, ZnOPS30 are 0.32, 0.36, 0.58 and 0.62 cm2 V−1 s−1, respectively. The corresponding threshold voltages (Vth) are in the range from −9 V to −10 V and the Ion/Ioff current ratios range from 105 to 106, respectively. Intriguingly, it has been observed that the mobility values are enhanced with the increased ZnO amounts. However, there is no significant change from the surface structure of pentacene from AFM (Figure S3), indicating the grain sizes and morphology of pentacene do not dominate the mobility enhancement. Therefore, we believe that the enhanced hole mobility may be attributed to the n-type ZnO nanoparticles blended in the electret, leading to an increased carrier density fulfilling defects in the channel. Similar mobility enhancement have been observed in our previous PCBM nanocomposite system 7 . Additionally, the off current is also increased with the increment of the ZnO loading. This may indicate the small amounts ZnO at interface causing the doping effects on pentacene layer1,7. The Ion/Ioff current ratio is up to 106 indicating their potential applications as high performance transistor memory devices. The transistor memories are extended from the regular transistor and operated by the appropriate pulse of the gates voltage. Based on the shifting of transfer curves, high- and low-conductance states at Vg = 0 V can be switched and denoted as two different output signals (0 and 1). Herein, when programming with a positive Vg pulse (+70 V for 1 s), the onset of the transfer curve shifts to a more positive region and leads to a high-conductance state (ON state) at zero gate voltage (Vg = 0 V), which serves as a “writing” process. In contrast, once a reverse bias is applied (−70 V for 1 s), the transfer curve moves to the negative direction and results in a low-conductance state (OFF state) at Vg = 0 V, serving as the “erasing” process. Figure 3b shows the positive and negative shifts of the transfer curves (where Vds = −50 V) for the OFET memory devices prepared from different ZnO blending amounts. When we apply the writing process, the entire transfer curves using ZnOPS10, ZnOPS20 and ZnOPS30 as the charge storage layer shift to the positive direction with threshold voltages of 12.27, 17.54 and 21.99 V, respectively, leading to the high drain current (ON state) at Vg = 0 V. In the erasing process, the transfer curves substantially move to the negative direction for ZnOPS10, ZnOPS20 and ZnOPS30 with threshold voltages of −10.87, −10.21 and −9.27 V respectively. The drain current is dramatically reduced to 6.54 × 10−12 A at Vg = 0 V in the OFF state. Due to no obvious Vth shifting for pure PS dielectric was observed, the memory windows of the nanocomposite devices are mainly contributed from ZnO NPs. The large Vth shift in the positive direction strongly suggests the increase of stored charges with enhancing the ZnO composition. The above effect can be attributed to the transfer of charge carrier from semiconductor into the dielectric, which is controlled by the applied gate voltage and known as a tunneling process. The Vth of the erasing curves is very close for different composition of ZnO NPs, indicating that the ZnO amount does not affect hole trapping. Therefore, we conclude that the trapped electrons are mainly controlled in the ZnO NPs in the forward direction and then detrapped in the backward direction. The memory window (∆Vth) is increased with the increments of ZnO NPs, memory window for ZnOPS10, ZnOPS20and ZnOPS30 are 23.14, 27.75 and 31.26 V respectively. Note that the memory window is denoted as the Vth difference between the transfer curves through applying a writing and an erasing gate bias.

Memory Devices Using the ZnO/PVPK composite as Charge-Storage Layer

To increase the memory window of the ZnO-based floating-gate memory, the hole-trapping PVPK was used as the polymer matrix38. The transfer characteristics of the OFET memory devices based on ZnO/PVPK are shown in Fig. 4, the mobilities, the ON/OFF ratio (Ion/Ioff) and the Vth shifts are also summarized in Table 1. The film with different ZnO composition (0, 10, 20 and 30 wt%), denoted as PVPK, ZnOPVPK10, ZnOPVPK20, ZnOPVPK30. Figure 4a shows the electric characteristics of the device using PVPK and only the negative shift is observed. Figure 4b shows the ZnO/PVPK devices with the “electric bistability” behavior. Compared to that using PVPK (−4.50 V), the Vth of the nanocomposite after the writing process is shifted to a more positive direction with the values of 11.76 (ZnOPVPK10), 17.54 (ZnOPVPK20) and 21.99V (ZnOPVPK30). Compared to the writing process, the onset position of the erasing curves have inversed trend (−44.48 V for ZnOPVPK10), (−40.42 V for ZnOPVPK20) and (−37.27 V for ZnOPVPK30), as shown in Fig. 4b. The memory window can be improved over 40% from 36.66 V for PVPK to 56.24 V for 10 wt% ZnO. This suggests that the addition of ZnO NPs into PVPK could effectively enhance the electron trapping due to its strong-acceptor behavior. Figure S4 shows the drain current Id measured at Vds = − 50 V and Vg = 0 V after the application of different time of gate pulses from 10−4 to 101 s under each writing (at Vds = 0 V, Vg = 70 V) and erasing (Vds = 0 V, Vg = −70 V) conditions. The drain current gradually increased from the off-state by increasing the pulse time with a proper gate bias of Vg = 70 V during programming operation. A similar behavior was observed for the erased drain current. This indicates that at least 0.01 s switching time are typically required to fully switch-on or switch-off the memory devices. In brief, the transparent organic memory devices could be programmed/erased relatively well, but the longer bias pulses (>0.1 s) typically had to be applied to obtain larger Vth shifts. The switching time is critically depending on the accumulated charge density induced by the applied gate. Therefore, the switching time could be faster by applying higher gate pulses or by reducing the film thickness of the ZnO-polymer nanocomposite. In addition to the writing/erasing efficiency, the photo stability is another important issue for the transparent devices. The device of ZnOPVPK30 showed negligible voltage shifts under an illumination with different wave lengths in the visible light range, as shown in the following Figure S5, indicating good photo stability. The photo-stable performance may be attributed to low absorbance in the visible light range. Additionally, the very thin pentacene layer (30 nm) may be one of reasons for low photosensitivity.

Here we proposed a possible mechanism in terms of the energy level diagram for ZnO/PVPK in Fig. 5. The charge transfer from pentacene into the charge storage sites is induced by the applied gate electric field. Due to the external electrical field, the electrons on the LUMO energy level of pentacene may overcome the energy barrier of the PVPK matrix and are transferred to ZnO. The lower LUMO level (−4.4 eV) of ZnO than that of pentacene (−2.9 eV) could stabilize the trapped electrons and thus the trapped electron charges would not be transferred back to pentacene without external voltage bias. It is energetically favorable for charge transfer when blending a strong acceptor into the dielectric. The electrons retained in ZnO change the built-in electric field under the applied electric field and thus the hole carriers of pentacene are easily accumulated at the interface, leading to a profound positive Vth shift. For the erasing process, the hole carrier in the channel would inject and neutralized the electrons in PVPK/ZnO, leading to returning to the OFF state of the device. In the ZnO/PS composite, ZnO plays the role of an electron acceptor in the storage layer. However, in the ZnO/PVPK system, the stored electrons might not be fully detrapped in the erasing process due to the hole transporting characteristic of PVPK, leading to the recombination between the electrons and holes. The residue electrons in the dielectric after the erasing process would become more in the higher ZnO composition. Thus, we found a slightly smaller Vth shift with the increasing amount of ZnO loading in ZnO/PVPK system compared to the pure PVPK system.

The Retention Characteristics

Long-term data retention properties are essential for nonvolatile memory applications. The charge retention characteristics of the transparent OFET memory devices are shown in Fig. 6. The retention capability of the OFET memory devices using the ZnO/PS and ZnO/PVPK electrets was measured after the application of + 70 V (ON state) and −70 V (OFF state) gate pulses for 1 s. To compare the endurance of the behavior in different composites (ZnO-PS and ZnO-PVPK), we evaluated the charge retention time in the devices using the same ZnO composition of ZnOPS30 and ZnOPVPK30. Similar experiment result has been observed for both of ZnO-PS and ZnO-PVPK systems. When reading at a gate-source voltage of −10 V, the high and low conducting states can keep over 105 s and high ON/OFF current ratio (>106) is obtained, implying no significant charge leakage. The high ON/OFF ratio make “0” and “1” clearly be distinguished in these memory devices. This could be contributed to the good dispersion of ZnO in polymer dielectric, which could prevent lateral charge diffusion, the slow relaxation of charges renders the superior operating reliability of the device. To evaluate the operating stability of the electrical switching, the WRER (writing/reading/erasing/reading) cycles were performed and shown in Fig. 7. Note that the writing, reading and erasing voltages are set to the Vg of 70, −10 and −70 V, respectively. The responding ON and OFF currents of ZnOPS30 are maintained over 200 cycles with the on/off current ratio of ca. 1.3 × 103, showing an excellent stress endurance, which reveals the promising potential applications for nonvolatile transistor memory devices. This may be attributed to that the insulating PS matrix incorporated with the separated ZnO NPs provides a high energy barrier between ZnO and pentacene to effectively suppresses the occurrence of current leakage during the readout. In ZnOPVPK30, the OFF current is relatively stable to the ZnO/PS system because of the hole transporting property of dielectric, PVPK. The on/off current ratio shows a small decrease from 3.7 × 103 to 7.28 × 102. This difference is possibly attributed to the recombination between the electrons and holes. During the repeated writing and erasing cycling, the stored holes in the PVPK matrix might recombine the electrons trapped in ZnO, thus resulting in decreasing the amount of trapped electrons during the writing process.

Conclusion

Transparent nonvolatile nano-floating gate memory devices are demonstrated through using ZnO NPs/polymer electret nanocomposite as a charge storage layer. The ZnO NPs were treated by the ligand, n-butylamine, leading the stable and well-separated NPs in solution. Furthermore, high transparent dielectric layers can be made, despite adding ZnO NPs into PS or PVPK polymer electret. Spray-coated PEDOT:PSS was exploited as the gate and source–drain electrodes for the fabrication of the transparent memory devices. The overall transmittance is 90% at the wavelength of 500 nm, showing high potential for transparent memory. A large memory window, long charge retention time over 105 s and the WRER process over 200 cycles were obtained in this ZnO nanocomposite-based memory devices. Additionally, all of the processes were carried out in the low temperature and without using noble metals as floating-gate. Therefore, these methods could potentially be used in integrated electronic components/circuits and transparent electronic device applications.

Methods

Materials

PEDOT:PSS solutions (CLEVIOS PH 1000) were purchased from Heraeus. The solid content of the PH 1000 solution was 1–1.3% and had a PEDOT to PSS ratio of 1:2.5 by weight. Poly(4-vinylphenol) (PVP,MW = 20 000 g mol−1), polystyrene (PS,MW = g mol−1), Zonyl FS-300 (Zonyl) and DMSO were purchased from Aldrich and used without further treatment. The poly 9-(4-vinylphenyl) carbazole (PVPK) were synthesized according to the literature method.

ZnO NPs Synthesis

ZnO NPs were prepared using an adapted procedure based on the work of Weller. The general procedure used for the preparation of NPs was as follows: zinc acetate dihydrate (Acros, >98%, 2.95 g, 13.4 mmol) was dissolved in methanol (125 mL) at 60 °C, a solution of KOH (Merck, 87%, 1.48 g, 23 mmol) in methanol (65 mL) was added in 10 min to the zinc acetate dihydrate solution under vigorous stirring. Zinc hydroxides precipitated but dissolved again. After 5 min, the solution became translucent and remained translucent. After 1.5 h, the NPs started to precipitate and the solution became turbid. Precipitate and mother liquor were separated and the precipitate was washed twice with methanol (50 mL). After the washing steps (5 min), the suspension was left unstirred for a minimum of 1 h to reach full precipitation. The washed precipitate was treated with n-butylamine and dissolving by the mixing solvent of methanol: chloroform = 1:3. This solution was only slightly translucent, almost transparent and was stable for more than two weeks.

Transistor Memory Device fabrication

The schematic configuration of the fabricated pentacene based transistor memory devices using ZnO/PVPK as nano floating-gate is shown in Fig. 2b. The memory devices were fabricated on an ITO glass and PEDOT:PSS was used for transparent electrode. Cross-linked PVP acting as a blocking organic dielectric was prepared from 12 wt% PVP and 5 wt% cross-linking agent (poly(melamine-coformaldehyde, PMF) in propylene glycol monomethyl ether acetate (PGMEA). The PVP solutions were filtered through a 0.22 μm polytetrafluoroethylene (PTFE) syringe filter. The crosslinked PVP blocking organic dielectric layer was spin-coated and then cured at 180 °C for 2 h in a vacuum oven. The polymer/ZnO NPs solutions were prepared in chloroform solution (10 mg/ml) and were stirred overnight to obtain homogeneous dispersion. Thereafter, the solution was filtered through the PTFE membrane syringe filter (pore size, 0.22 μm) and then spin-coated onto the cPVP layer at 1000 rpm for 60 s. The thickness of the cross-linked PVP, PS and PVPK are 400, 55 and 50 nm, respectively, which was measured using Micro figure Measuring Instrument. The PEDOT:PSS solution containing 5% DMSO was filtered through a syringe filter (0.22 μm pore size) to remove precipitated material for the ink of spray coating. Prior to the deposition of the PEDOT:PSS , 1 wt% Zonyl was added to the PEDOT:PSS solution to enhance the wettability of PEDOT:PSS on hydrophobic substrate. Where noted in the main text, 1% Zonyl by volume was added to the PEDOT:PSS. Shadow mask was used to pattern source-drain and the channel length (L) and width (W) of the devices were 100 and 2000 μm, respectively. Figure S6 shows the transparency testing of the PEDOT:PSS electrodes with different thickness. The sheet resistance is about 1200(Ω/sq) at a film thickness of 298 nm. The pentacene was thermally deposited with a deposition rate of 0.35 nm s−1 at 90 °C under vacuum (10−7 torr) to form the 30 nm thick film.

Characterization

The degree of aggregation of NPs were performed through field emission scanning electron microscope (FE-SEM, JEOL JSM-6330F). The energy level of the polymers were investigated by cyclic voltammetry (CV)39 and the thickness of polymer film was measured with Microfigure Measuring Instrument (Surfcorder ET3000, Kosaka Laboratory Ltd.).The morphology of polymer thin film surface were obtained with a Nanoscope 3D Controller atomic force micrographs (AFM, Digital Instruments) operated in the tapping mode at room temperature. The electrical characteristics of the fabricated transistor memory devices were measured using a Keithley 4200 semiconductor parametric analyzer. The field-effect mobility μ FET (cm2V−1s−1), on/off ratios (Ion/off) and threshold voltages (Vth) of these fabricated devices were obtained using equation (1) in the saturation regime:

where Id is the drain current, Vg is the gate voltage, Vth is the threshold voltage, μ is the hole mobility, W is the channel width, L is the channel length and Ctot is the capacitance per unit area of total dielectric layer, respectively.

Additional Information

How to cite this article: Shih, C.-C. et al. High Performance Transparent Transistor Memory Devices Using Nano-Floating Gate of Polymer/ZnO Nanocomposites. Sci. Rep. 6, 20129; doi: 10.1038/srep20129 (2016).

References

Chang, H.-C., Lu, C., Liu, C.-L. & Chen, W.-C. Single-Crystal C60 Needle/CuPc Nanoparticle double floating-gate for low-voltage organic transistors based non-volatile memory devices. Adv. Mater. 27, 27–33 (2015).

Wei, Q. et al. Additive-driven assembly of block copolymer–nanoparticle hybrid materials for solution processable floating gate memory. ACS Nano 6, 1188–1194 (2012).

Chiu, Y.-C. et al. High-performance nonvolatile organic transistor memory devices using the electrets of semiconducting blends. Appl. Mater. Interfaces 6, 12780–12788 (2014).

Chang, H.-C., Liu, C.-L. & Chen, W.-C. Flexible Nonvolatile transistor memory devices based on one-dimensional electrospun P3HT:Au hybrid nanofibers. Adv. Funct. Mater. 23, 4960–4968 (2013).

Kang, M. et al. Printed, flexible, organic nano-floating-gate memory: Effects of metal nanoparticles and blocking dielectrics on memory characteristics. Adv. Funct. Mater. 23, 3503–3512 (2013).

Tsai, T.-D., Chang, J.-W., Wen, T.-C. & Guo, T.-F. Manipulating the hysteresis in Poly(vinyl alcohol)-dielectric organic field-effect transistors toward memory elements. Adv. Funct. Mater. 23, 4206–4214 (2013).

Chiu, Y.-C. et al. High performance nonvolatile transistor memories of pentacene using the electrets of star-branched p-type polymers and their donor–acceptor blends. J. Mater. Chem. 2, 1436–1446 (2014).

Ling, Q.-D. et al. Polymer electronic memories: Materials, devices and mechanisms. Prog. Polym. Sci. 33, 917–978 (2008).

Lee, W. Y. et al. Effect of Non-Chlorinated mixed solvents on charge transport and morphology of solution-processed polymer field-effect transistors. Adv. Funct. Mater. 24, 3524–3534 (2014).

Lei, T., Dou, J. H. & Pei, J. Influence of alkyl chain branching positions on the hole mobilities of polymer thin-film transistors. Adv. Mater. 24, 6457–6461 (2012).

Naber, R. C. G. et al. High-performance solution-processed polymer ferroelectric field-effect transistors. Nat. Mater. 4, 243–248 (2005).

Schroeder, R., Majewski, L. A. & Grell, M. All-Organic permanent memory transistor using an amorphous, spin-cast ferroelectric-like gate insulator. Adv. Mater. 16, 633–636 (2004).

Liu, J. et al. Organic field-effect transistor nonvolatile memories utilizing sputtered C Nanoparticles as nano-floating-gate. Appl. Phys. Lett. 105, 163302 (2014).

Han, S.-T. et al. Energy-Band engineering for tunable memory characteristics through controlled doping of reduced graphene oxide. ACS Nano 8, 1923–1931 (2014).

Chou, Y.-H. et al. Nonvolatile organic field-effect transistor memory devices using polymer electrets with different thiophene chain lengths. Polym. Chem. 5, 1063–1071 (2014).

Jung, J. H. et al. High-Performance Flexible Organic Nano-Floating Gate Memory Devices Functionalized with Cobalt Ferrite Nanoparticles. Small 11, 4976–4984 (2015).

Park, Y.-S. & Lee, J.-S. Towards the development of flexible non-volatile memories. Adv. Mater. 27, 706–711 (2015).

Baeg, K.-J., Noh, Y.-Y., Sirringhaus, H. & Kim, D.-Y. Controllable shifts in threshold voltage of top-gate polymer field-effect transistors for applications in organic nano floating gate memory. Adv. Funct. Mater. 20, 224–230 (2010).

Jang, S. et al. Graphene–graphene oxide floating gate transistor memory. Small 11, 311–318 (2015).

Han, S.-T. et al. Layer-by-layer-assembled reduced graphene oxide/gold nanoparticle hybrid double-floating-gate structure for low-voltage flexible flash memory. Adv. Mater. 25, 872–877 (2013).

Leong, W. L. et al. Micellar poly(styrene-b-4-vinylpyridine)-nanoparticle hybrid system for non-volatile organic transistor memory. J. Mater. Chem. 19, 7354–7361 (2009).

Chen, C.-M. et al. Non-volatile organic field-effect transistor memory comprising sequestered metal nanoparticles in a diblock copolymer film. J. Mater. Chem. 22, 454–461 (2012).

Jang, S., Hwang, E. & Cho, J. H. Graphene nano-floating gate transistor memory on plastic. Nanoscale 6, 15286–15292 (2014).

Kim, C., Song, J. M., Lee, J. S. & Lee, M. J. All-solution-processed nonvolatile flexible nano-floating gate memory devices. Nanotechnology 25, 014016 (2014).

Suresh, A. et al. Transparent indium gallium zinc oxide transistor based floating gate memory with platinum Nanoparticles in the gate dielectric. Appl. Phys. Lett. 94, 123501 (2009).

Kim, S.-J., Song, J.-M. & Lee, J.-S. Transparent organic thin-film transistors and nonvolatile memory devices fabricated on flexible plastic substrates. J. Mater. Chem. 21, 14516–14522 (2011).

Chang, H.-C. et al. Improving the characteristics of an organic nano floating gate memory by a self-assembled monolayer. Nanoscale 4, 6629–6636 (2012).

Shih, C.-C. et al. Conjugated polymer nanoparticles as nano floating gate electrets for high performance nonvolatile organic transistor memory devices. Adv. Funct. Mater. 25, 1511–1519 (2015).

Kanoun, M., Souifi, A., Baron, T. & Mazen, F. Electrical study of Ge-nanocrystal-based metal-oxide-semiconductor structures for p-type nonvolatile memory applications. Appl. Phys. Lett. 84, 5079–5081 (2004).

Pal, B. N., Trottman, P., Sun, J. & Katz, H. E. Solution-deposited zinc oxide and zinc oxide/pentacene bilayer transistors: High mobility n-channel, ambipolar and nonvolatile devices. Adv. Funct. Mater. 18, 1832–1839 (2008).

Hirschmann, J., Faber, H. & Halik, M. Concept of a thin film memory transistor based on ZnO nanoparticles insulated by a ligand shell. Nanoscale 2012 4, 444–447 (2012).

Sun, B. & Sirringhaus, H. Solution-Processed Zinc Oxide Field-effect transistors based on self-assembly of colloidal nanorods. Nano Letters 5, 2408–2413 (2005).

Thiemann, S. et al. High-nobility ZnO nanorod field-effect transistors by self-alignment and electrolyte-gating. Appl. Mater. Interfaces 5, 1656–1662 (2013).

Tu, Y. et al. Transparent and flexible thin films of ZnO-polystyrene nanocomposite for UV-shielding applications. J. Mater. Chem. 20, 1594–1599 (2010).

Snedeker, L. P. et al. Organic phase conversion of bulk (wurtzite) ZnO to nanophase (wurtzite and zinc blende) ZnO. Solid State Sci 7, 1500–1505 (2005).

Sun, D., Miyatake, N. & Sue, H. J. Transparent PMMA/ZnO nanocomposite films based on colloidal ZnO quantum dots. Nanotechnology 18, 215606 (2007).

Jang, Y. et al. Patterning the organic electrodes of all-organic thin film transistors with a simple spray printing technique. Appl. Phys. Lett. 89, 183501 (2006).

Chiu, Y.-C., Shih, C.-C. & Chen, W.-C. Nonvolatile memories using the electrets of conjugated rod-coil block copolymer and its nanocomposite with single wall carbon nanotubes. J. Mater. Chem. C 3, 551–558 (2015).

Fang, Y.-K., Liu, C.-L. & Chen, W.-C. New random copolymers with pendant carbazole donor and 1,3,4-oxadiazole acceptor for high performance memory device applications. J. Mater. Chem., 21, 4778–4786 (2011).

Acknowledgements

The authors thank Ministry of Science and Technology (MOST), Taiwan, for the financial support.

Author information

Authors and Affiliations

Contributions

C.C.S. contributed to nanoparticle preparation, device fabrication and wrote the manuscript. W.Y.L. and Y.C.C. advised C.C.S. to fabricate and characterized the devices. H.C.C. advised C.C.S. to prepare nanoparticles. H.W.H. and C.L.L. advised C.C.S. to make transparent electrodes and devices. W.C.C. led and supervised the whole project.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Shih, CC., Lee, WY., Chiu, YC. et al. High Performance Transparent Transistor Memory Devices Using Nano-Floating Gate of Polymer/ZnO Nanocomposites. Sci Rep 6, 20129 (2016). https://doi.org/10.1038/srep20129

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep20129

This article is cited by

-

Why do nanowires grow with their c-axis vertically-aligned in the absence of epitaxy?

Scientific Reports (2020)

-

Aminobenzene stabilized bismuth halide nanoparticles with O-shaped hysteresis behaviour

Journal of Materials Science: Materials in Electronics (2020)

-

Hybrid organic–metal oxide multilayer channel transistors with high operational stability

Nature Electronics (2019)

-

AZO transparent electrodes grown in situ during the deposition of zinc acetate dihydrate onto aluminum thin film by spray pyrolysis

Journal of Materials Science: Materials in Electronics (2019)

-

Low temperature processing of BaTiO3-PMMA-PVP hybrid films as transparent dielectric gate

Journal of Materials Science: Materials in Electronics (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.