Abstract

High density 3-dimensional (3D) crossbar resistive random access memory (RRAM) is one of the major focus of the new age technologies. To compete with the ultra-high density NAND and NOR memories, understanding of reliability mechanisms and scaling potential of 3D RRAM crossbar array is needed. Thermal crosstalk is one of the most critical effects that should be considered in 3D crossbar array application. The Joule heat generated inside the RRAM device will determine the switching behavior itself and for dense memory arrays, the temperature surrounding may lead to a consequent resistance degradation of neighboring devices. In this work, thermal crosstalk effect and scaling potential under thermal effect in 3D RRAM crossbar array are systematically investigated. It is revealed that the reset process is dominated by transient thermal effect in 3D RRAM array. More importantly, thermal crosstalk phenomena could deteriorate device retention performance and even lead to data storage state failure from LRS (low resistance state) to HRS (high resistance state) of the disturbed RRAM cell. In addition, the resistance state degradation will be more serious with continuously scaling down the feature size. Possible methods for alleviating thermal crosstalk effect while further advancing the scaling potential are also provided and verified by numerical simulation.

Similar content being viewed by others

Introduction

To satisfy the growing requirements for enormous data densities and nonvolatile storage, new memory technologies are currently attracting much attention due to their significant potential for the replacement of FLASH memory1,2,3,4,5,6,7,8,9,10,11,12. High density 3-dimensional (3D) RRAM crossbar array is one of the major focuses for the new age technology12,13,14,15,16,17. To compete with the ultra-high density 3D NAND FLASH, understanding of reliability mechanisms and scaling potential of 3D RRAM crossbar array during operation is necessary. Thermal crosstalk is one of the most critical effects that should be considered in 3D crossbar array application. The Joule heat generated inside the RRAM device will determine the switching behavior of the device and for high density memory arrays, the temperature surrounding may lead to a consequent resistance degradation of neighboring devices during cycling. Moreover, due to the crosstalk issue between the adjacent devices, scaling potential of the integrated array under thermal effect must be seriously addressed.

Generally, to suppress the current sneak path, an additional selective component is always required in the crossbar integration12,18,19,20,21,22,23,24 and 1D1R (one Diode one RRAM) structure is very attractive for 3D cross-point architecture in terms of the vertical stackable ability and the simplicity of the erasing/programing method24,25,26,27,28. 1D1R storage element usually displays unipolar switching (set and reset operation at the same voltage polarity)26,29 and the reset process is controlled by Joule heating26,30. Understanding of programming and reliability mechanisms in unipolar 1D1R crossbar array requires a detailed characterization of the electrical and thermal conduction properties of the memory device. Many researches have been performed in the thermal effects of RRAM30,31,32,33,34, however, all the previous works were based on an individual device level and neglected the diode device. Thermal effect in 3D RRAM crossbar array is still lacking up to date.

In this work, thermal crosstalk effect in 3D RRAM crossbar array was systematically investigated. It is revealed that the transient thermal effect plays a dominant role in reset process. More importantly, thermal crosstalk phenomena could deteriorate device retention performance and even lead to data storage state failure from LRS (low resistance state) to HRS (high resistance state) of the disturbed RRAM cell. In addition, the resistance state degradation will be more serious with continuously scaling down the feature size. Possible methods for alleviating thermal crosstalk effect are also provided and verified by numerical simulation. The results in this work were computed for unipolar 1D1R crossbar arrays but are likely to be a reference to bipolar RRAM device based arrays as well, due to the thermal nature in the resistive switching process.

Physical Model Description

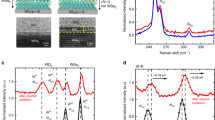

Figure 1a,b show the schematic diagrams of 1D1R crossbar array structure and 1D1R data storage element which is composed of a RRAM and a diode connected in series, respectively. Figure 1c shows the schematic of typical I-V characteristics including set and reset operations of 1D1R structure26. Both set and reset occur at the same voltage polarity. In this full manuscript, voltage is applied to the electrode connected with RRAM while keeping the opposite electrode ground for the set/reset operations. Thermal behavior in a cross-point array can be described through 3D Fourier heat flow equation,

(a) Schematic of 3D 1D1R crossbar array structure. (b) Schematic of 1D1R storage element which is composed of a RRAM device and a diode connected in series. (c) Schematic diagram of typical DC I-V characteristic of the 1D1R element. In this work, voltage is applied to the electrode (WL/BL) that is connected with RRAM cell while keeping the opposite electrode ground for the reset operation.

where kth is the thermal conductivity, T is the temperature, c is the thermal capacity, ρ is the mass density of the materials in the crossbar array system, V is the imposed voltage, t is time and σ is the electric conductivity which empirically reads as

where α is the resistivity temperature coefficient and σ0 is the electric conductivity at room temperature T0. Word lines (WL) or bit lines (BL) in the top and bottom layers of 3D array system are assumed to connect with ideal heat dissipation packaging structure and keep at room temperature T0 = 300 K during the calculation, as

Ni/HfO2/Pt RRAM device and Ti/TiO2/Pt diode based 1D1R structure and their corresponding electrical parameters in ref. 26 are used as a reference in this work. The insulating material between each 1D1R cell is HfO2. The resistive switching behavior of Ni/HfO2/Pt RRAM device is widely accepted to via formation/rupture of Ni conductive filament (CF)35,36. The reset current Ireset is 1.7 × 10−4 A. Detailed parameters used in the calculation are listed in Table 1.

Results and Discussion

Firstly, dynamic temperature evolution in crossbar array system was studied. Figure 2 shows the temperature evolution during reset operation for several cross-point arrays with different sizes. Here, all the RRAM cells are in LRS. Figure 2a–d illustrate the schematics of array structures in the simulation, including an individual RRAM cell and 3D RRAM arrays with various sizes from a 1 × 1 × 1 1D1R element to 3 × 3 × 3 block array, respectively. The WL/BLs with Vreset are marked in white and the ones being grounded are marked in black. The programmed RRAM cells are connected with on-state diodes (marked in green) and the unprogrammed RRAMs are connected with off-state diodes (marked in red). At the periphery of the array structures, heat dissipates through the surface of the simulated volume with a typical heat transfer coefficient 10 W/m2K of air. Figure 2e–h show the corresponding temperature evolution maps of the cross-section (blue planes in Fig. 2a–d inside the arrays). Figure 2i shows the highest temperature evolution in the programmed RRAM device of the array systems in Fig. 2. Figure 2j shows the corresponding time ts, ts is the time that array system consumes to reach thermal steady state. From Fig. 2i, one can clearly see that ts increases with the increase of array size as the heat capacity of the system gets higher. In Fig. 2j, the derived ts is 50 ns for a 1D1R element, which is much higher than that for the individual RRAM (less than 5 ns) since the diode part could hold certain amount of heat during the heating process. For the 3 × 3 × 3 block array, ts would be over 500 ns, which is about 10 times as that of a single 1D1R element. 3D 1D1R crossbar array includes masses of devices, hence the thermal effect is highly complex. The peak temperature of steady state also varies remarkably with the array sizes (e.g. 500 K for a single 1D1R device and 605 K for that in 3 × 3 × 3 array system), since the distances between thermal source (the programmed RRAM cell) and the thermal dissipation boundaries (top/bottom electrodes in this work) are different. For an array with small size, the programmed cell is close to the top/bottom boundary, the generated Joule heat can be easily dissipated to the thermal sink boundaries, hence the corresponding temperature of the cell would be lower. While For an array with large size, the generated Joule heat could hardly dissipate. Finally the accumulated Joule heat would increase the final temperature of array with the large size. Besides that, in a 3D crossbar array with multiple stack layer, the temperature is also very different when the programmed RRAM cell locates in different layers, e.g. in a 3 × 3 × 3 block array, the difference of the final temperature for the programmed RRAM device in different layers could reach about 50 K (as shown in Figure S1-S2, Supporting Information). The typical reset time of RRAM devices usually varies from tens of ns to hundreds of ns37,38,39,40,41. For a single RRAM device, ts is much shorter than the typical reset time, i.e. RRAM device could reach steady thermal state far before the reset process is completed and it is reasonable to use the steady thermal state temperature in device model and simulation. While for dense memory arrays, ts could be much larger than the typical reset time, which means that the individual RRAM device model based on steady thermal state is not suitable for 3D cross-point array.

(a) Schematic of the structure of an individual RRAM cell. (b–d) Schematics of the structure of 1D1R crossbar block with 1 × 1 × 1, 3 × 1 × 2 and 3 × 3 × 3 array size, respectively. (e,f) Calculated temperature evolution maps of the cross-sections (blue planes) in (a–d). (i) Highest temperature evolution in the programmed RRAM device for the 4 selected structure in (a–d). (j) ts (time that array system consumes to reach thermal steady state) as a function of the array size. The WL/BLs with Vreset are marked in white and the ones being grounded are marked in black. The programmed RRAM cells are connected in series with on-state diodes (marked in green) and the unprogrammed RRAMs are connected with off-state diodes (marked in red).

From Fig. 2, it is clear that thermal transfer is fast along the WL/BLs and the CFs of RRAMs in both horizontal and vertical directions due to their high thermal transfer ability. In this situation, passive temperature increase in the adjacent RRAM devices would be induced by thermal crosstalk, which may deteriorate device reliability and even lead to failure of disturbed RRAM cells. To evaluate the reliability of the 3D RRAM array under a parasitic thermal crosstalk, we calculated the 3D temperature profiles in a small 3 × 3 × 3 block array consisting of 27 cells with feature size of 80 nm, as shown in Fig. 3a,b.

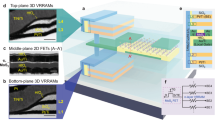

(a,b) Schematics of the two selected “worst cases” in thermal crosstalk analysis. (b) A crossbar array with shared WL/BLs, which could realize parallel erasing/programming at different layers. (c,d) Potential maps inside the array structures in (a,b). The WL/BLs imposed with Vreset are marked in white and the ones being grounded are marked in black. The programmed RRAM cells are connected in series with on-state diodes (marked in green) and the unprogrammed RRAMs are connected with off-state diodes (marked in red). The disturbed RRAM cell (labeled as D222) locates in the center of crossbar array surrounded by multiple programmed RRAM devices. (e,f) Temperature evolutions of the cross-sections (blue planes in (a,b)) for the two array structures. (g) Highest temperature evolution in the disturbed RRAM cell (D222) in the two selected “worst cases” array structures. Case 1 and Case 2 correspond to the cases in (a,b), respectively. (h) Arrhenius plot of the measured and modeled retention time (reference from ref. 26 in which the conductive path of the RRAM device is modeled as metallic Ni rich filament) and the evaluation of the device reliability under thermal crosstalk. The disturbed RRAM cell may be failure from LRS to HRS after 7.0 × 1011 and 2.0 × 1013 consecutive erase/program cycles for the two cases in (a,b).

To understand clearly the thermal crosstalk effect, the temperature profile was calculated for the two “worst cases”. Here all the RRAM cells are in LRS before their resistance change from LRS to HRS by applying a reset pulse in the programmed cells. Figure 3a shows the typical crossbar array structure and Fig. 3b shows the crossbar array with shared WL/BLs28, which could realize parallel erasing/programming devices at different stack layers. The programmed RRAM devices are connected in series with on-state diodes (marked in green) and the unprogrammed RRAMs are connected with off-state diodes (marked in red). The disturbed RRAM cell (labeled as D222) locates in the center of the crossbar array surrounded by multiple programming RRAM devices. In Fig. 3a, thermal crosstalk effect mainly results from the neighboring RRAM devices in vertical direction of different layers. While in Fig. 3b, crosstalk influence results from adjacent RRAM devices in both vertical direction of different layers and horizonal direction within the same layer.

Figure 3c–f show the calculated potential distributions and temperature evolutions of the cross-sections in the 3D array systems, respectively, corresponding to the two selected cases in Fig. 3a,b. Here, periodical boundary condition is adopted at the periphery of the array structures during the simulation as there could be masses of devices within the same stack layer for dense memory arrays. It is found obviously that temperatures in the programmed RRAM devices rise much faster than those in the unprogrammed ones. In addition, temperature in the unprogrammed RRAM region passively increases with increasing time due to the thermal crosstalk effect. Figure 3g illustrates the highest temperature evolution in the disturbed RRAM device (D222) for the two selected “worst case” array structures. Case 1 and Case 2 correspond to the selected cases in Fig. 3a,b, respectively. The temperature in the disturbed RRAM device increases with time and could ultimately reach 792 K and 807 K, respectively.

Figure 3g shows the Arrhenius plot of the experimental and simulated retention performance of NiO based RRAM device42, where the conductive path is treated as metallic Ni filament30. Thermal dissolution of the metallic-conductivity filament, which may be induced by the dissipation of conductive elements from the filament, may result in premature loss of the resistance state of RRAM, thus causing a retention reliability concern43. Considering the dominant role of transient thermal effect plays during reset operation in 3D crossbar array, transient temperature is adopted to evaluate the thermal crosstalk effect on device reliability. Here, we used a conservative estimation method44: assuming the typical reset time treset is 100 ns for a standalone 1D1R device. The temperature in the RRAM filament can be converted into retention time tretention according to the Arrhenius plot in Fig. 3g. The highest temperature Tp at t = 50 ns in the disturbed RRAM cell is 523 K and 475 K, as shown in Fig. 3h. Based on the experimental data, the derived tretention at Tp = 523 K and Tp = 475 K is 3.5 × 104 s and 1.0 × 106 s, respectively. Here, consecutive program/erase operations is conservatively assumed to have similar effect of continuously heating at a constant temperature (T = Tp), with effective heating time th = treset − 50 ns for each program/erase cycle. Then the derived tretention correspond to a sequence of tretention/(treset − 50 ns) = 7.0 × 1011 and 2.0 × 1013 program/erase pulses, respectively (i.e., reasonable cycling expectations for RRAM devices), whereas the disturbed bit is not programmed in the same time frame. In other words, the thermal crosstalk deteriorates the LRS retention reliability and the disturbed RRAM cell may be failure from LRS to HRS after 7.0 × 1011 and 2.0 × 1013 consecutive program/erase cycles for the 2 cases in Fig. 3. Here, self-heating effect due to the application of a set pulse to the programmed bit is neglected since the temperature is much lower than that in the reset operation due to the lower programming current. It should be mentioned that this is a relative conservative estimation method due to the transient nature of the Joule heating effect in 3D RRAM array (in order to give an intuitive and feasible estimation of thermal crosstalk, in this work, the influence of interval time between each program/erase pulse was neglected for the sake of simplicity) and the actual case in the very large scale 3D array could be more complex.

Understanding the thermal crosstalk between neighboring RRAM devices is a critical step to understand the scaling potential and performance tradeoffs associated with miniaturization. In scaling analysis, we use the same method in Fig. 3h to evaluate thermal crosstalk on LRS reliability. Figure 4 shows the highest temperature at t = 50 ns in the disturbed cell (D222) for 3 selected “worst cases” (Fig. 4a) with feature size F scaling down from 100 nm to 30 nm node. RRAM devices in HRS (with 5 nm gap in the CF) are also included. Here, the crossbar structure in Case 1 and Case 2 is similar (blue lines in Fig. 4b). In Case 1, the crosstalk results from the neighboring RRAM devices in horizontal direction. While in Case 2, the crosstalk results from the neighboring RRAM cells in different layers in vertical direction. The array structure in Case 3 adopts shared WL/BLs (shown in Fig. 4a), which could realize parallel programming/erasing at different layer28 (red line in Fig. 4b). One can see in Fig. 4b that the temperature in the disturbed RRAM device increases with F scaling down for the 3 selected cases. For the array structure in Case 1 and Case 2, thermal crosstalk from the neighboring CFs within the same layer (Case 1) is smaller than that in vertical direction (Case 2) in the range of 100 nm to 30 nm node and thermal crosstalk of Case 3 will be stronger than that in Case 2 at 62 nm node. The temperature in the disturbed RRAM filament could even reach 1780 K for Case 3 at 30 nm node, which corresponds to 4.18 × 102 consecutive program/erase cycles (the disturbed cell will be failure from LRS to HRS after 4.18 × 102 consecutive program/erase cycles due to thermal crosstalk).

Schematic diagrams of the “worst cases” selected in scaling analysis.

(b) Highest temperature at t = 50 ns in the disturbed RRAM device with feature size F scaling down from 100 nm to 30 nm node for the 3 selected cases in (a). RRAM in HRS (with 5 nm gap in the CF) are also included. Case 1 and Case 2 adopt the typical crossbar structure (blue lines in (b)). Case 3 adopts the structure with shared WL/BL, which could realize parallel erasing/programming at different layer (red line in (b)). The WL/BLs imposed with Vreset are marked in white and the ones being grounded are marked in black. The programmed RRAM cells are connected in series with on-state diodes (marked in green) and the unprogrammed RRAMs are connected with off-state diodes (marked in red). The disturbed RRAM cell (labeled as D222) locates in the center of crossbar array surrounded by multiple programmed RRAM devices.

It should be noted that the values in this work have been performed for the purpose of scaling analysis and although reasonable, they should not be considered as mandatory values for the 1D1R crossbar array scaling roadmap.

Decreasing the reset current Ireset could effectively alleviate thermal crosstalk. Figure 5 shows the calculated highest temperature at t = 50 ns in the disturbed RRAM device as a function of Ireset for F = 30 nm. In the figure, the values were calculated for 3 “worst cases” in Fig. 4. With the decrease of Ireset from 1.7 × 10−4 A to 1.0 × 10−7 A, temperature in the disturbed RRAM filament decreases remarkably. Using the same evaluation method in Fig. 3h, the storage state of the disturbed RRAM could stand 1.0 × 1016 consecutive program/erase cycles (endurance requirement of DRAM devices) with temperature at t = 50 ns equals to 406 K, which corresponds to Ireset = 1.2 × 10−5 A, Ireset = 1.2 × 10−5 A and Ireset = 4.7 × 10−6 A (reasonable expectations of unipolar RRAM devices45,46) for the 3 “worst cases”, respectively.

Highest temperature at t = 50 ns in the disturbed RRAM device as a function of reset current Ireset for F = 30 nm.

Case 1-Case 3 correspond to the 3 “worst cases” in Fig. 4, respectively. With the decrease of Ireset from 1.7 × 10−4 A to 1.0 × 10−7 A, temperature in the disturbed RRAM filament decreases remarkably. Using the same evaluation method in Fig. 3h, the storage state of the disturbed RRAM could stand 1.0 × 1016 consecutive program/erase cycles (endurance requirement of DRAM devices) with temperature at t = 50 ns equals to 406 K, which corresponds to Ireset = 1.2 × 10−5 A, Ireset = 1.2 × 10−5 A and Ireset = 4.7 × 10−6 A (reasonable expectations of unipolar RRAM devices45,46) for the 3 “worst cases”, respectively.

Besides that, to continue miniaturization, a simple cycle-rehabilitate technique can also be used: erasing and reprogramming the LRS of RRAM cells in the array system after a certain operation cycles cr (making sure that after cr cycles, the deteriorated LRS can still be used to distinguish HRS and LRS). Using this method, the resistance of RRAM devices in LRS deteriorated by thermal crosstalk could be rehabilitated by the reprogram operation and the scaling potential of crossbar array can be further advanced.

In summary, the dominant role of transient thermal effect on the reset mechanisms was demonstrated, thermal crosstalk on the RRAM retention property and the scaling potential of 3D RRAM array under thermal effect were analyzed in detail based on the numerical simulation in this work. According to theoretical analysis, it is revealed that 1) the individual RRAM device models based on steady state thermal effect may not be applicable in 3D device crossbar array; 2) thermal crosstalk phenomena could deteriorate device retention performance and even lead to disturbed RRAM component failure from LRS to HRS, especially with continuously scaling down the feature size; 3) decreasing the reset current and adopting the cycle-rehabilitate technique could alleviate thermal crosstalk phenomena for LRS retention characteristics of the array while further advancing the scaling potential.

Additional Information

How to cite this article: Sun, P. et al. Thermal crosstalk in 3-dimensional RRAM crossbar array. Sci. Rep. 5, 13504; doi: 10.1038/srep13504 (2015).

References

Yao, Y. et al. In situ electron holography study of charge distribution in high-κ charge-trapping memory. Nat. Commun. 4, 2764 (2013).

Zhou, Y., Han, S.-T., Sonar, P. & Roy, V. Nonvolatile multilevel data storage memory device from controlled ambipolar charge trapping mechanism. Sci. Rep. 3, 2319 (2013).

Kusuma, D. Y. & Lee, P. S. Ferroelectric tunnel junction memory devices made from monolayers of vinylidene fluoride oligomers. Adv. Mater. 24, 4163 (2012).

Kundu, S. et al. Integration of lead-free ferroelectric on HfO2/Si(100) for high performance non-volatile memory applications. Sci. Rep. 5, 8494 (2015).

Zhao, F. et al. Functionalized graphitic carbon nitride for metal-free, flexible and rewritable nonvolatile memory device via direct laser-writing. Sci. Rep. 4, 5882 (2014).

Hosseini, P., Wright, C. D. & Bhaskaran, H. An optoelectronic framework enabled by low-dimensional phase-change films. Nature 511, 206 (2014).

Dunand, D. C. & Mullner, P. Size effects on magnetic actuation in Ni-Mn-Ga shape-memory alloys. Adv. Mater. 23, 216 (2011).

Long, S. et al. Voltage and power-controlled regimes in the progressive unipolar RESET transition of HfO2-based RRAM. Sci. Rep. 3, 2929 (2013).

Wang, M. et al. Thermoelectric Seebeck effect in oxide-based resistive switching memory. Nat. Commun. 5, 4598 (2014).

Wang, H. et al. Sericin for resistance switching device with multilevel nonvolatile memory. Adv. Mater. 25, 5498 (2013).

Balatti, S., Larentis, S., Gilmer, D. & Ielmini, D. Multiple memory states in resistive switching devices through controlled size and orientation of the conductive filament. Adv. Mater. 25, 1474 (2013).

Seok, J. Y. et al. A review of three-dimensional resistive switching cross-bar array memories from the integration and materials property points of view. Adv. Funct. Mater. 24, 5316 (2014).

Song, S. et al. Three-dimensional integration of organic resistive memory devices. Adv. Mater. 22, 5048 (2010).

Lin, P., Pi, S. & Xia, Q. 3D integration of planar crossbar memristive devices with CMOS substrate. Nanotechnology 25, 405202 (2014).

Bai, Y. et al. Study of multi-level characteristics for 3D vertical resistive switching memory. Sci. Rep. 4, 5780 (2014).

Chen, H.-Y. et al. Experimental study of plane electrode thickness scaling for 3D vertical resistive random access memory. Nanotechnology 24, 465201 (2013).

Chen, F. T., Chen, Y.-S., Wu, T.-Y. & Ku, T.-K. Write scheme allowing reduced LRS nonlinearity requirement in a 3D-RRAM array with selector-less 1TNR architecture. IEEE Electron Dev. Lett. 35, 223 (2014).

Kim, T.-W. et al. One Transistor–One Resistor devices for polymer non-volatile memory applications. Adv. Mater. 21, 2497 (2009).

Koveshnikov, S. et al. Real-time study of switching kinetics in integrated 1T/HfOx 1R RRAM: Intrinsic tunability of set/reset voltage and trade-off with switching time. Electron Devices Meeting (IEDM), 2012 IEEE Int. 20.4.1–20.4.3 (IEEE, 10–13 Dec., San Francisco, 2012).

Govoreanu, B. et al. 10×10 nm2 Hf/HfOx crossbar resistive ram with excellent performance, reliability and low-energy operation. Electron Devices Meeting (IEDM), 2011 IEEE Int. 31.6.1–31.6.4 (IEEE, 5–7 Dec., Washington, 2011).

Shin, J. et al. MIM-type cell selector for high-density and low-power cross-point memory application. Microelectron. Eng. 93, 81 (2012).

Lee, W. et al. Varistor-type bidirectional switch (JMAX>107 A/cm2, selectivity~104) for 3D bipolar resistive memory arrays. VLSI Technology, Systems and Applications (VLSI-TSA), 2013 International Symposium on IEEE, 37–38 (IEEE, 12–14 June, Honolulu, 2012).

Kim, G. H. et al. 32×32 crossbar array resistive memory composed of a stacked schottky diode and unipolar resistive memory. Adv. Funct. Mater. 23, 1440 (2013).

Wang, G. et al. High-performance and low-power rewritable SiOx 1 kbit one diode–one resistor crossbar memory array. Adv. Mater. 25, 4789 (2013).

Liu, Z.-J., Gan, J.-Y. & Yew, T.-R. ZnO-based one diode-one resistor device structure for crossbar memory applications. Appl. Phys. Lett. 100, 153503 (2012).

Huang, J.-J. et al. Flexible one diode–one resistor crossbar resistive-switching memory. Jpn. J. Appl. Phys. 51, 04DD09 (2012).

Lo, C.-L., Chen, M.-C., Huang, J.-J. & Hou, T.-H. On the potential of CRS, 1D1R and 1S1R crossbar RRAM for storage-class memory. VLSI Technology, Systems and Applications (VLSI-TSA), 2013 International Symposium on. 1–2 (IEEE, 22–24 Apr., Hsinchu, 2013).

Lee, M.-J. et al. 2-stack 1D-1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications. Electron Devices Meeting (IEDM), 2007 IEEE Int. 771–774 (IEEE, 10–12 Dec., Washington, 2007).

Zhang, Y. et al. Vertically integrated ZnO-Based 1D1R structure for resistive switching. J. Phys. D. Appl. Phys. 46, 145101 (2013).

Russo, U., Ielmini, D., Cagli, C. & Lacaita, A. L. Self-accelerated thermal dissolution model for reset programming in unipolar resistive-switching memory (RRAM) devices. IEEE Trans. Electron Dev. 56, 193–200 (2009).

Mickel, P. R., Lohn, A. J., James, C. D. & Marinella, M. J. Isothermal switching and detailed filament evolution in memristive systems. Adv. Mater. 26, 4486 (2014).

Sun, P. et al. Physical model of dynamic Joule heating effect for reset process in conductive-bridge random access memory. J. Comput. Electron. 13, 432 (2014).

Ielmini, D. Modeling the universal set/reset characteristics of bipolar RRAM by field-and temperature-driven filament growth. IEEE Trans. Electron Dev. 58, 4309 (2011).

Chang, S. et al. Effects of heat dissipation on unipolar resistance switching in Pt/NiO/Pt capacitors. Appl. Phys. Lett. 92, 183507 (2008).

Lin, K.-L. et al. Electrode dependence of filament formation in HfO2 resistive-switching memory. J. Appl. Phys. 109, 084104 (2011).

Sun, J. et al. In situ observation of nickel as an oxidizable electrode material for the solid-electrolyte-based resistive random access memory. Appl. Phys. Lett. 102, 053502 (2013).

Tran, X. et al. A high-yield-based unipolar resistive RAM employing Ni electrode compatible with Si-diode selector for crossbar integration. IEEE Electron Dev. Lett. 32, 396 (2011).

Tran, X. et al. Self-selection unipolar-based RRAM. IEEE Trans. Electron Dev. 60, 391 (2013).

Yan, Z., Guo, Y., Zhang, G. & Liu, J.-M. High-performance programmable memory devices based on Co-doped BaTiO3 . Adv. Mater. 23, 1351 (2011).

Wang, L.-H. et al. The mechanism of the asymmetric SET and RESET speed of graphene oxide based flexible resistive switching memories. Appl. Phys. Lett. 100, 063509 (2012).

Akinaga, H. & Shima, H. Resistive random access memory (ReRAM) based on metal oxides. P. IEEE 98, 2237 (2010).

Larentis, S., Cagli, C., Nardi, F. & Ielmini, D. Filament diffusion model for simulating reset and retention processes in RRAM. Microelectron. Eng. 88, 1119 (2011).

Ielmini, D. Reliability issues and modeling of flash and post-flash memory. Microelectron. Eng. 86, 1870 (2009).

Russo, U., Ielmini, D., Redaelli, A. & Lacaita, A. L. Modeling of programming and read performance in phase-change memories—Part II: Program disturb and mixed-scaling approach. IEEE Trans. Electron Dev. 55, 515 (2008).

Nardi, F. et al. Control of filament size and reduction of reset current below 10 μA in NiO resistance switching memories. Solid-State Electron. 58, 42 (2011).

Ielmini, D., Nardi, F. & Cagli, C. Universal reset characteristics of unipolar and bipolar metal-oxide RRAM. IEEE Trans. Electron Dev. 58, 3246 (2011).

Haynes, W. M. CRC handbook of chemistry and physics (CRC Press, Boston, 2011).

Kim, K. M. & Seong Hwang, C. The conical shape filament growth model in unipolar resistance switching of TiO2 thin film. Appl. Phys. Lett. 94, 122109 (2009).

Lee, B. Y. & Kurtis, K. E. Proposed acceleratory effect of TiO2 nanoparticles on Belite hydration: preliminary results. J. Am. Chem. Soc. 95, 365 (2012).

Panzer, M. A. et al. Thermal properties of ultrathin hafnium oxide gate dielectric films. IEEE Electron Dev. Lett. 30, 1269 (2009).

Acknowledgements

This work was supported in part by the Opening Project of Key Laboratory of Microelectronics Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, in part by the National 973 Program under Grant 2013CBA01604, National 863 Program under Grant 2014AA032901 and in part by the National Natural Science Foundation of China under Grant 61306117, Grant 61322408, Grant 61221004, Grant 61334007 and Grant 61274091.

Author information

Authors and Affiliations

Contributions

P.X.S., L.L. and M.L. conceived the idea and designed this work. P.X.S. preformed the numerical simulations and calculations. P.X.S., N.D.L., Y.T.L., H.W. and S.L. analysed the result. H.B.L., Q.L. and S.B.L. made scientific comment on the results. P.X.S. and N.D.L. wrote the paper, which all authors reviewed and refined. L.L. and M.L. coordinated and supervised the whole work.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Sun, P., Lu, N., Li, L. et al. Thermal crosstalk in 3-dimensional RRAM crossbar array. Sci Rep 5, 13504 (2015). https://doi.org/10.1038/srep13504

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep13504

This article is cited by

-

In-memory computing with emerging nonvolatile memory devices

Science China Information Sciences (2021)

-

A Collective Study on Modeling and Simulation of Resistive Random Access Memory

Nanoscale Research Letters (2018)

-

Graphene/h-BN Heterostructures for Vertical Architecture of RRAM Design

Scientific Reports (2017)

-

Electric Crosstalk Effect in Valence Change Resistive Random Access Memory

Journal of Electronic Materials (2017)

-

Mechanisms of Low-Temperature Nitridation Technology on a TaN Thin Film Resistor for Temperature Sensor Applications

Nanoscale Research Letters (2016)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.