# SCIENTIFIC REPORTS

### **OPEN**

#### SUBJECT AREAS:

ELECTRONIC AND SPINTRONIC DEVICES

ELECTRICAL AND ELECTRONIC ENGINEERING

ELECTRONIC DEVICES

Received 12 August 2014

Accepted 17 March 2015

Published 29 April 2015

Correspondence and requests for materials should be addressed to M.M.H. (muhammad mustafa.hussain@ kaust.edu.sa)

## InAs/Si Hetero-Junction Nanotube Tunnel Transistors

Amir N. Hanna<sup>1</sup>, Hossain M. Fahad<sup>1</sup> & Muhammad M. Hussain<sup>1</sup>

<sup>1</sup>Integrated Nanotechnology Lab, Electrical Engineering, Computer Electrical and Mathematical Sciences & Engineering Division, King Abdullah University of Science and Technology, Thuwal 23955-6900, Saudi Arabia.

Hetero-structure tunnel junctions in non-planar gate-all-around nanowire (GAA NW) tunnel FETs (TFETs) have shown significant enhancement in 'ON' state tunnel current over their all-silicon counterpart. Here we show the unique concept of nanotube TFET in a hetero-structure configuration that is capable of much higher drive current as opposed to that of GAA NW TFETs. Through the use of inner/outer core-shell gates, a single III-V hetero-structured nanotube TFET leverages physically larger tunneling area while achieving higher driver current ( $I_{ON}$ ) and saving real estates by eliminating arraying requirement. Numerical simulations has shown that a 10 nm thin nanotube TFET with a 100 nm core gate has a  $5 \times$  normalized output current compared to a 10 nm diameter GAA NW TFET.

In unneling field effect transistors (TFETs) offer interesting opportunities to address two major challenges faced by aggressively scaled conventional CMOS technology: (i) the increasing difficulty in scaling the supply voltage ( $V_{DD}$ ), and (ii) minimizing the leakage currents that degrade the  $I_{ON}/I_{OFF}$  switching ratio. Both of them lead to more power consumption in devices whereas we need exactly the opposite (energy efficiency) for wide-range deployment of ultra-mobile computation capability. As the transistor gate length is reduced, improved performance, requires the supply voltage,  $V_{DD}$ , and simultaneously the threshold voltage,  $V_T$ , to be lowered to maintain a high overdrive factor ( $V_{DD} - V_T$ )<sup>1</sup>. Doing this, however, exponentially increases the 'OFF' state leakage current ( $I_{OFF}$ ) due to a physical limitation commonly referred to as the 60 mV/dec sub-threshold slope (SS) bottleneck. This is inherent in all current generation electronics that utilizes CMOS transistors with over-the-barrier charge transport physics.

Additionally, transistor off-state power dissipation is considered to be empirically proportional to<sup>1</sup>:

$$P \alpha I_{OFF} V_{DD}^3$$

(1)

In order to reduce power consumption, reducing V<sub>DD</sub> is absolutely critical, which in turn demands devices with steep SS enabling faster turn on at low supply voltages. Contrary to classical MOSFETs, where charge carriers are thermally injected by lowering an energy barrier, the primary transport mechanism in a TFET is inter-band tunneling, where charge carriers transfer from one energy band into another at a heavily doped  $p^+/n^+$  junction. In a TFET, inter-band tunneling can be switched "ON" and "OFF" abruptly by controlling the band bending in the channel region using gate-to-source bias, Vgs. This can be realized in a reverse-biased p-i-n structure, where asymmetric doping is used to suppress ambipolar transport<sup>1</sup>. While all-silicon TFETs have been studied rigorously using technology drive current boosters such as the use of a high- $\kappa$  gate dielectric, abrupt doping profiles at the tunnel junction, ultra-thin body, higher source doping, a double gate, a gate oxide aligned with the intrinsic region, and a shorter intrinsic region (and gate) length,  $I_{ON}$  of just 100  $\mu$ A/ $\mu$ m have been achieved<sup>2</sup>. One of the more efficient ways to radically improve  $I_{ON}$  is by using a low band gap material as the source injector. Here, the smaller effective mass of charge carriers increases the tunneling probability, according to the triangular Wentzel-Kramer-Brillouin (WKB) approximation<sup>3,4</sup>. Potential source material candidates for N/PMOS TFETs are Germanium (Ge) and Indium Arsenide (InAs), respectively. Simulation studies using the above materials in a hetero-structure have shown  $I_{ON}$  values of 244  $\mu$ A/ $\mu$ m and 83 µA/µm for Ge and InAs NTFET and PTFET, respectively, which corresponded to I<sub>ON</sub> enhancements by factors > 400 $\times$  and > 100 $\times$ , respectively, over their all-Si planar counterparts<sup>1</sup>. Combining this with new and unique nonplanar architectures opens up new opportunities for TFETs that are on-par with traditional Boltzmann transistors. Table 1 summarizes some recent state-of-the-art III-V source TFET demonstrations.

We have recently shown the unique advantages of vertical nanotube architecture with core-shell gates for improved drive current capability compared to nanowires on silicon. Inspired by carbon nanotubes, the nanotube

|                     |      |      | rt III-V TFET demonstrati |                                                                                | 1 (4)                            |                          |             |

|---------------------|------|------|---------------------------|--------------------------------------------------------------------------------|----------------------------------|--------------------------|-------------|

| Affiliation         | Ref. | Year | Technology                | Material System                                                                | I <sub>on</sub> (A) per nanowire | I <sub>on</sub> (μΑ /μm) | SS (mV/dec) |

| Penn State          | [26] | 2010 | Non planar single gate    | In <sub>0.53</sub> Ga <sub>0.47</sub> As                                       | NA                               | 4×10 <sup>-1</sup>       | 100–216     |

| Intel               | [27] | 2011 | Planar                    | InGaAs                                                                         | NA                               | ~ 7                      | 60          |

| UC Berkeley         | [11] | 2011 | Planar                    | InAs                                                                           | NA                               | 0.5                      | 190         |

| Univ. of Notre Dame | [28] | 2011 | Vertical InGaAs/ InP      | InGaAs                                                                         | NA                               | 20                       | 130         |

| IBM                 | [29] | 2011 | GAA NW                    | InAs/Si                                                                        | 10-7                             | 0.4                      | 220         |

| UT Austin           | [30] | 2011 | Vertical single gate      | In <sub>0.7</sub> Ga <sub>0.3</sub> As                                         | NA                               | 40                       | 84–380      |

| IBM                 | [24] | 2012 | GAA NW                    | InAs/Si                                                                        | Not reported                     | 2.4                      | 150         |

| Hokkaido Univ       | [31] | 2012 | Vertical hetero NW        | InAs/Si                                                                        | Not reported                     | $\sim 0.005$             | 21/114      |

| Univ. of Notre Dame | [32] | 2012 | Planar single gate        | GaSb-InAs                                                                      | NA                               | 180                      | 200–400     |

| Univ. of Notre Dame | [33] | 2012 | Planar single gate        | InP-InGaAs                                                                     | NA                               | 20                       | 93-310      |

| Penn State          | [34] | 2012 | Vertical single gate      | GaAsSb-InGaAs                                                                  | NA                               | 135                      | 230-350     |

| Univ. of Notre Dame | [35] | 2012 | Planar single gate        | AlGaSb-InAs                                                                    | NA                               | 78                       | 125–470     |

| Hokkaido Univ       | [12] | 2013 | Vertical hetero NW        | InAs/Si                                                                        | Not reported                     | 1                        | 21          |

| MIT                 | [36] | 2013 | Vertical single gate      | InGa <sub>0.53</sub> As <sub>0.47</sub> -GaAs <sub>0.5</sub> Sb <sub>0.5</sub> | NA                               | 0.5                      | 140         |

Hokkaido Univ[31]2012Vertical hetero NWInAs/SiUniv. of Notre Dame[32]2012Planar single gateGaSb-InAsUniv. of Notre Dame[33]2012Planar single gateInP-InGaAsPenn State[34]2012Vertical single gateGaAsSb-InGaAsUniv. of Notre Dame[35]2012Planar single gateAlGaSb-InAsHokkaido Univ[12]2013Vertical hetero NWInAs/SiMIT[36]2013Vertical single gateInGa<sub>0.53</sub>As<sub>0.47</sub>-GaAs<sub>0.5</sub>Sb<sub>0.5</sub>architecture mimics the gate all-around nanowire (GAA NW) devicesultra-thin body (Uby having an outer (shell) gate, as well as, an inner (core) gate insideultra-thin body (Uhigher  $\lambda$  values<sup>10</sup>. Pis also sensitive to genhanced by usingpared to arrays of nanowires, the nanotube architecture outperformsin terms of drive current capability, CV/I metric (i.e. intrinsic gatebody thickness. Adelay), power consumption, and area efficiency<sup>5-8</sup>. In this paper wetunnel junction is a

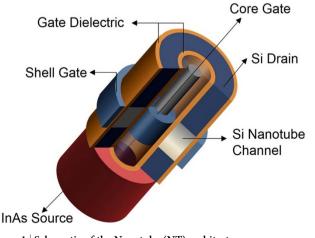

present a hetero-structure Si/InAs p-channel TFET device concept that combines the advantages of a low band-gap source injector and inherent high drive current advantage in NTFET (Figure 1). Tunneling in TFET devices is governed by the inter-band tunneling probability across the tunneling barrier, which is typically calcu-

ing probability across the tunneling barrier, which is typically calculated using WKB approximation<sup>9</sup>:

$$T_{WKB} \approx \exp\left(-\frac{4\lambda\sqrt{2m^*}\sqrt{E_g^3}}{3q\,\hbar(E_g + \Delta\Phi)}\right) \tag{2}$$

Where m\* is the effective mass,  $E_g$  is the band gap,  $\lambda$  is the screening tunneling length, and  $\Delta \Phi$  is the potential difference between the source valence band and channel conduction bands. From this simple triangular approximation, we can see that that the band gap ( $E_g$ ), the effective carrier mass (m\*) and the screening tunneling length ( $\lambda$ ) should be minimized to increase the tunneling probability. While  $E_g$  and m\* are material dependent parameters,  $\lambda$  depends on other parameters such as the device geometry, doping profiles and gate capacitance. A small  $\lambda$  value would result in a strong modulation of the channel bands by the gate<sup>1</sup>. It has been shown that the highest tunneling rate and hence lowest  $\lambda$  values were found for the gate-all-around (GAA) architecture for a 10 nm diameter nanowire, while

Figure 1 | Schematic of the Nanotube (NT) architecture.

ultra-thin body (UTB) double gate FETs has shown comparatively higher  $\lambda$  values<sup>10</sup>. Planar UTBs have the highest  $\lambda$  values<sup>10</sup>. Because  $\lambda$ is also sensitive to gate capacitance, tunneling probability can also be enhanced by using high- $\kappa$  gate dielectrics, as well as, small channel body thickness. Also, the abruptness of the doping profile at the tunnel junction is also important to control  $\Delta \Phi$ . In order to minimize the tunneling barrier, the high source doping level must fall off to the intrinsic channel in as short a width as possible. Typically this requires a change in the doping concentration of about 4–5 orders of magnitude within a distance of only a few nanometers<sup>1</sup>.

With the above in mind, we hypothesize that the nanotube TFET's excellent electrostatic control would enable steep turn on characteristics, while maintaining low I<sub>OFF</sub> values comparable to NW TFET. This transistor architecture in conjunction with a low band gap source material in a hetero-structure configuration would enable a higher inter-band tunneling rate, when compared to all-silicon TFET structure. For this reason, InAs was chosen as a source material, for a p-type TFET application, since theoretically it has a band gap of 0.385 eV and electron effective mass of 0.026 mo<sup>11</sup>. Also, a recent experimental demonstration of InAs NW on Si(111) has shown the possibility of growing NW without misfit dislocation for diameters less than 20 nm, which is attributed to the reduction of strain field owing to the nanometer-scale footprint of NW12. The authors found that the hetero-structure with small diameter NW possesses fewer misfit dislocations, which quantitatively suppress trap assisted tunneling via dislocation levels, and has pure band-to-band tunneling as the dominant tunneling process. The highest InAs normalized current by the same group is 0.5 mA/ $\mu$ m for n-type using p+ Si source, and Zn doped n + InAs channel<sup>12</sup>.

#### Results

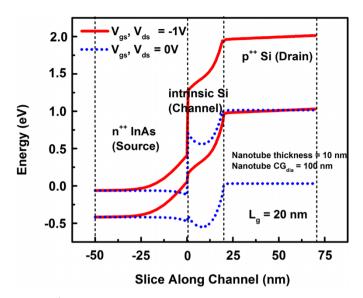

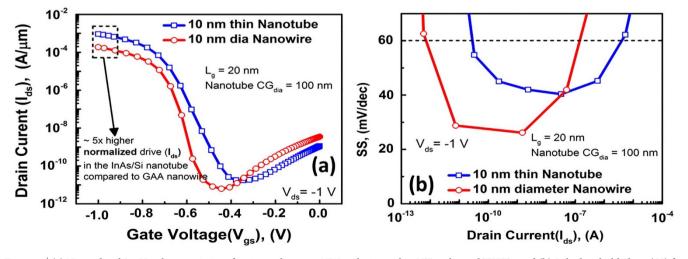

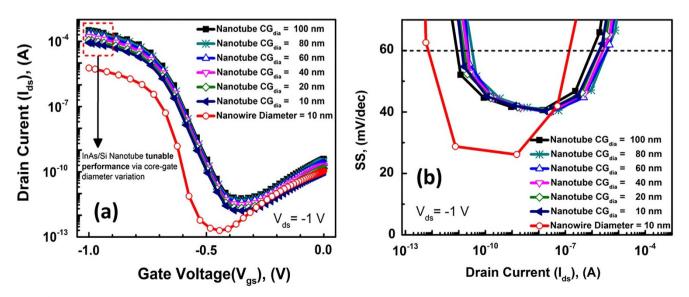

(Figure 2) shows the energy band diagram of the simulated p-channel nanotube TFET. (Figure 3(a)) compares the normalized  $I_{ds}$ - $V_{gs}$ characteristics of a 10 nm thin NTFET (with 100 nm inner core-gate diameter,  $CG_{dia}$ ) and 10 nm diameter NWFET at  $V_{dd} = 1V$ . Transfer characteristics at lower supply voltages are shown in Supporting Figure S1<sup>13</sup>. We have used the NW circumference ( $\pi$ d), where d is the NW diameter, in the case of the NT we have used average circumference  $(\pi \times (CG_{dia} + NT_w))$ , where  $CG_{dia}$  and  $NT_w$ are the nanotube core-gate diameter and thickness respectively. As it can be seen the nanotube architecture has  $5 \times$  higher normalized current output than that of the GAA NW architecture. Both architectures provide I<sub>ON</sub>/I<sub>OFF</sub> of more than 10<sup>5</sup>. We have compared threshold voltage, V<sub>T</sub>, values for both devices, and they were -0.58V and -0.63V for the NT and NW TFETs, respectively, showing a difference of 0.05V, using the constant current method defining  $V_T$  at a normalized current of  $I_{ds} = 10^{-7} A/\mu m^{14}$ . However, we have also used the proposed threshold definition by Boucart et al. arguing

Figure 2 | Band diagram of the P-type nanotube architecture TFET showing both ON state OFF states.

that TFET threshold voltages can be physically defined based on the saturation of the barrier width narrowing with respect to V<sub>gs</sub><sup>15</sup>. According to the new definition of threshold voltage, V<sub>TG</sub>, is the voltage at which the first derivative of the transconductance,  $g_{m}$ , shows a maxima with respect to V<sub>gs</sub><sup>15</sup>. We have found that V<sub>TG</sub> = -0.73 and -0.72V for the NT and NW TFETs, respectively, which shows that the two devices have similar threshold voltage values. Both threshold voltage extraction methods are shown in Supporting Figure S2. So, this confirms the fairness of the comparison as both devices show similar normalized I<sub>OFF</sub>, and V<sub>TG</sub> values.

Figure 3(b) compares the SS values of the 10 nm NT and NW FETs. Both architectures show SS values less than 60 mV/dec over 5 decades<sup>1</sup>. However, the NW architecture TFET shows lower point SS values as low as 25 mV/dec, while the lowest SS values for the NTFET is ~ 40 mV/dec. We have shown before in the past this is due to the ultimate electrostatic control in the GAA architecture<sup>6</sup>. However, smaller drain bias has been experimentally reported to yield lower point and average SS<sup>16</sup>, as is also shown in Supporting Figure S3 at  $V_{ds} = -0.8V$ , where the NT TFET shows a minimum point SS of 22 mV/dec, and the NW TFET shows a minimum if 23 mV/dec. The reason for this is that lower  $V_{ds}$  provides in principle lower  $I_{ON min}$ , the  $I_{ON}$  value at the knee of the SS swing, thus also the average SS

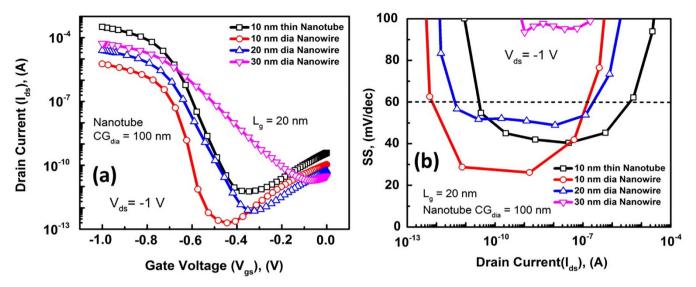

slope would be reduced. We have also compared the non-normalized "ON" current of the 10, 20, 30 nm NW TFETs with the 10 nm NT TFET in (Figure 4(a)). The 10 nm NT TFET shows a non-normalized  $I_{ON} \sim 0.32$  mA, while the NW TFETs show  $I_{ON} \sim 5.9 \times 10^{-6}$ A,  $2.51 \times 10^{-5}$ A,  $5.31 \times 10^{-5}$ A for the 10, 20 and 30 nm NWs, respectively. This means that the 10 nm NTFET shows  $54 \times$ ,  $13 \times$  and  $6 \times$  increase in drive current over that of the 10, 20 and 30 nm diameter NW TFETs. As for SS, (Figure 4(b)) shows that only 10 and 20 nm NW TFET and the 10 nm NT TFET can achieve sub 60 mV/dec SS. So, having a small diameter NW is essential to maintain a low SS.

#### Discussion

In order to supply high drive current while maintaining small SS, arraying small diameter NWs is inevitable. However, this would come at the expense of chip area and off-state leakage as will be seen the following sections. Additionally, the low "OFF" current characteristic of the TFET would be lost as arraying would cause, at the least, multiplying the "OFF" state leakage current by the number of NWs in the array needed to supply the same "ON" current as one NT. Therefore, in the case of 54 NW array of 10 nm diameter NWs, the leakage would be at least  $13 \times$  higher compared to a single 10 nm NT. Finally, although it could be argued that arraying could boost the "ON" current value, sensitivity of parameters like threshold voltage, for example, variations in NW width could lead to degradation of the SS swing for a large array of devices<sup>17</sup>. Recent demonstrations of sub 60 mV/dec of have been for all silicon single NW p and n-type TFET of diameter < 20 nm which supplies a maximum ON current in the nA regime and a normalized "ON" current of 1.2 µA/µm<sup>18,19</sup>. However, when an array of TFETs is tested sub 60 mV/dec SS have been demonstrated for currents as low as 0.01 µA/µm<sup>20</sup>. Also, degraded SS slope was noticed for higher drain current giving a maximum  $I_{\rm ON}$  = 64  $\mu A/\mu m$  at  $V_{\rm DD}$  = 1.0 V and at a higher gate bias  $V_{GS} = 2$  V. On the other hand, a SS of 52 mV/dec have been shown at an even higher  $I_{\rm ON}$  = 100  $\mu A/\mu m$  at  $V_{\rm DD}$  = 1.0 V and  $V_{gs}$  = 1 V for all-silicon single gated SOI based TFETs with vertical self-aligned top gate structure supplying and for 70 nm thick SOI with 2 nm Effective Oxide Thickness (EOT)<sup>21</sup>. Even higher drain currents have been shown for double gate strained-Ge hetero-structure TFET with a drive current of 300 µA/µm at a SS of 50 mV/dec<sup>22</sup>. That is why we think the NT architecture could be an excellent candidate for as a vertical structure that resembles double gate structure and could provide a higher integration density compared to the NW structure.

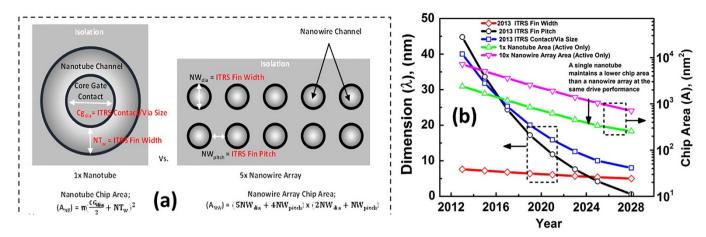

To consider the scalability of the nanotube architecture, we studied the non-normalized drain current as a function of the inner core-gate diameter (Figure 5(a)). An important observation here is

Figure 3 | (a) Normalized I<sub>ds</sub>-V<sub>gs</sub> characteristics of a 10 nm diameter NW and 10 nm thin NT p-channel TFETs; and (b) Sub-threshold Slope (SS) for the NT and NW TFET showing sub 60 mV/dec for more than 5 orders of magnitude of current.

Figure 4 | (a) Transfer ( $I_{ds}$ - $V_{gs}$ ) characteristics of NWs of 10, 20, 30, 40 and 50 nm diameter and 10 nm NT; and (b) SS comparison between 10 nm thick NT and 10, 20, and 30 nm diameter NW TFETs.

that the core-gate contact scaling tunes the on-state drive performance without compromising the sub-threshold swing, as can be seen from (Figure 5(b)). This becomes a competitive technology option compared to GAA NWFETs. To fully comprehend this concept, consider the top-down plan-view chip layout perspective of a single nanotube and an array of GAA nanowires. (Figure 6(a)). In vertical GAA nanowire technology, maintaining a small nanowire pitch (NW<sub>pitch</sub>) ensures high integration density and drivability. In order to compete with this, the core-gate diameter (CG<sub>dia</sub>) of the nanotube should be highly scalable just like the nanowire pitch. One pragmatic approach to investigate this is by studying the device dimension scalability effects on chip area. Using the 2013 International Technology Roadmap for Semiconductors (ITRS) Overall Roadmap Technology Characteristics (ORTC), scalable parameters for current generation FinFET technology are adapted here, which are summarized in Table 2. In this comparison, the nanowire pitch is assumed to be equal to the fin half-pitch and the nanotube core-gate diameter is assumed to be equal to contact/via size as specified in the 2013 ORTC target for future technology nodes. The contact/via size scaling is considered equal to the M1 metal halfpitch. The other parameters in the comparison are the nanowire diameter (NW<sub>dia</sub>) and the nanotube thickness (NT<sub>w</sub>), both of which are assumed equal to the fin width target given in Table 2. From (Figure 4(a)), a 100 nm core-gate diameter, 10 nm thin InAs/Si nanotube has greater than 10× higher non-normalized drive capability compared to a single 10 nm diameter GAA InAs/Si nanowire. To achieve similar performance levels as the nanotube, more than  $10 \times$  nanowires need to be stacked in an array. Using the above parameters and assuming that the normalized drive current scales linearly with channel thickness (NTw and NWdia) in both the nanotube and nanowire architecture, chip-area estimates of the single nanotube and a 10× nanowire array are carried out at different technology nodes using simple analytical calculations. As it can be seen from (Figure 6(b)), the contact/via scaling at the moment is comparable to the nanowire-pitch. But at around the 7 nm technology node (2017), the pitch scaling will start to become more aggressive. However, even after this and considering the fact that large nanowire arrays are required to achieve similar drivability as a single nanotube, the InAs/Si nanotube architecture will outperform InAs/Si GAA nanowire arrays at the extreme scaling limit in terms of chip area consumed.

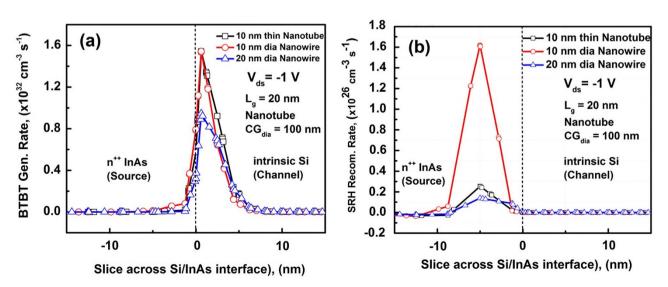

We also compared the BTBT generation rate of both the 10 nm nanotube and 10 and 20 nm GAA NW TFETs in (Figure 7(a)). Color

Figure 5 | Non-normalized NT drive current (a) and SS (b) as a function of inner core gate diameter.

Figure 6 | (a) Illustrated top-down plan-view comparison of between; and (b) chip area comparison using ITRS predicted parameters between a single nanotube device and an array of  $10 \times \text{GAA}$  nanowires.

| Table 2   2013 ITRS ORTC FinFET SCALING PARAMETERS |      |                             |                     |                   |  |  |  |  |  |  |

|----------------------------------------------------|------|-----------------------------|---------------------|-------------------|--|--|--|--|--|--|

| Technology Node                                    | Year | MPU/ASIC M1<br>½-Pitch (nm) | Fin ½-Pitch<br>(nm) | Fin Width<br>(nm) |  |  |  |  |  |  |

| 16/14                                              | 2013 | 40                          | 30                  | 7.6               |  |  |  |  |  |  |

| 10                                                 | 2015 | 31.8                        | 24                  | 7.2               |  |  |  |  |  |  |

| 7                                                  | 2017 | 25.3                        | 19                  | 6.8               |  |  |  |  |  |  |

| 5                                                  | 2019 | 20                          | 15                  | 6.4               |  |  |  |  |  |  |

| 3.5                                                | 2021 | 15.9                        | 12                  | 6.1               |  |  |  |  |  |  |

| 2.5                                                | 2023 | 12.6                        | 9.5                 | 5.7               |  |  |  |  |  |  |

| 1.8                                                | 2025 | 10                          | 7.5                 | 5.4               |  |  |  |  |  |  |

maps of BTBT generation rate and SRH Recombination rate of the 10 nm NT, 10 nm NW and 20 nm NW TFETs are provided in Supporting Figures S4, S5 and S6, showing the cross sections in the middle of the channel along which we made the measurements. The 10 nm diameter nanowire shows a slightly higher peak BTBT generation of  $1.6 \times 10^{32}$  (cm<sup>-3</sup>s<sup>-1</sup>), when compared to the 10 nm thick nanotube, showing  $\sim 1.5 \times 10^{32}$  (cm<sup>-3</sup>s<sup>-1</sup>), due to the shorter tunneling length,  $\lambda$ , for the nanowire architecture. Similar peak BTBT generation rate is expected as it has been theoretically shown that the differences in the scaling tunneling length,  $\lambda$ , between the GAA and double gate architectures, which resembles the NT Core-Shell

gates architecture, reduces for body thickness  $\leq 10$  nm and almost diminishes for body thickness of 5 nm<sup>10</sup>. On the other hand, the larger diameter nanowire (20 nm) shows lower peak tunneling rate of  $5.53 \times 10^{31}$  (cm<sup>-3</sup>s<sup>-1</sup>) due to larger body thickness leading to higher tunneling length,  $\lambda$ , values. However, one major difference between the two architectures is the distance over which BTBT generation is significant away from the Si/InAs interface. For the case of the NT, we observe that BTBT generation rate is higher over a larger distance, almost 7 nm into the Silicon channel, when compared to both the 10 nm and 20 nm NW, as shown in (Figure 7(a)). This is an indication of higher lateral tunneling across the Si-InAs interface for the NT architecture when compared to the NW architecture, which could explain the higher normalized current. This reason for this is that when analyzing the band diagrams for the 10 nm NT and NW TFETs, shown in Figure S7, it was found that the gradient of the holes quasi Fermi level is higher for the NT TFET as we move from the Si/InAs interface into the Si channel. This is important since the BTBT tunneling is proportional to the valence band gradient, according to the mode used. So, a higher gradient corresponds to lower scanning tunneling length,  $\lambda$ . In addition, lateral tunneling is fundamentally limited by the inversion layer thickness of in the 'ON' state, and thus is sensitive to the Channel/Source interface cross sectional area.

On the other hand, the 10 nm NW TFET is shows higher BTBT generation rate when moving away from the interface into the InAs

Figure 7 | (a) BTBT Generation Rate; and (b) SRH Recombination Rate for the 10 nm NT and 10, 20 nm NWs as function of the distance from the Si/InAs interface.

source, indicating higher vertical tunneling within the source, when compared to both the 10 nm NT and 20 nm NW TFETs. Although higher vertical tunneling is desired in hetero-structure TFETs for increasing the drive current<sup>23</sup>, it could also lead to higher Shockley-Reed-Hall (SRH) recombination in the small direct band gap InAs source. When analyzing the SRH recombination rate in (Figure 7(b)), it was found that the peak SRH recombination rate for the 10 nm NW is almost an order of magnitude higher than the 10 nm NT TFET, as well as, the 20 nm NW TFET. To get a quantitative sense of the effect of BTBT generation and SRH recombination rates on the drive current, we analyzed the integrated area under the curve for (Figure 7(a-b)). For the 10 nm NT BTBT generation curve, the area under the curve was found to be 8.4% higher than that of the 10 nm NW curve, and 45% higher than that of the 20 nm NW curve. This can partially account for the larger non-normalized current seen for 10 NT TFET, 54×, compared to that of the 10 nm nanowire TFET. The nanotube has larger available cross sectional area for tunneling when compared to the 10 nm nanowire. Since a 100 nm core-gate diameter nanotube with 10 nm thickness has  $44 \times$ the cross sectional area of a 10 nm nanowire. Hence, doing a back-ofthe-envelope multiplication the extra 8.4% in volumetric band-band generation by the additional cross sectional area gives  $47.7 \times$  the anticipated increase in the current. The area under the SRH recombination curve for the 10 nm NW 8.7 $\times$  of that of the 10 nm NT and  $12 \times$  of that of the 20 nm NW. This demonstrates the potential of the nanotube transistor architecture to radically enhance the drive current capability of tunnel FETs to values comparable to state-of-theart CMOS due to both higher BTBT generation rate and lower SRH recombination rate when compared to NW architecture at the same body thickness.

We precluded discussion over the fabrication of nanotube TFET as it is out of the scope of this paper and can be found in our pertinent work. With the advent of III-V channel material growth on silicon<sup>12,24</sup>, the nanotube device formation using bottom-up approach is very much possible.

#### Conclusion

We have presented the advantages of nanotube architecture with inner/outer core-shell gates for hetero-structure (Si/InAs) TFET application, when compared to gate-all-around nanowire based TFETs. 3D device simulations have shown that a p-channel nanotube TFET is able to outperform nanowire arrays, while preserving chip area and at comparable SS values. We believe the nanotube architecture combined with hetero-structure III-V/IV material systems holds a great promise for high performance, ultra-low power consumer computing applications.

#### **Methods**

To study the benefits of a nanotube architecture over a nanowire on a hetero-structure Si/InAs TFET platform, 3D simulations of a NT (Figure 1) and GAA NW TFET using Synopsys<sup>TM</sup> using the dynamic nonlocal path BTBT model<sup>11,24,25</sup>. For this case, indirect BTBT model was assumed as Si is an indirect bandgap material. The tunneling path for this model is calculated as a straight line straight line with its direction opposite to the gradient of the valence band and ends conduction band. Both devices are compared for a gate length (Lg) of 20 nm. Silicon drain is p-doped with acceptor active concentration  $N_{\rm A}=1\times10^{20}$  cm $^{-3}$ , while an intrinsic channel is used. The InAs source was used with n-doping with donor active concentration  $N_D = 1 \times 10^{18}$  cm<sup>-3</sup>, both typical to the previously demonstrated device<sup>24</sup>. Both the nanotube thickness and nanowire diameter are kept at 10 nm. The gate metal in both devices has a work function of 4.53 eV, and a nitride gate dielectric is assumed with an (effective oxide thickness) EOT of 0.5 nm. A dynamic nonlocal band-to-band (BTB) tunneling model is utilized in conjunction with Shockley-Reed-Hall recombination and driftdiffusion physics. The band-to-band tunneling (BTBT) parameters, 'A' and 'B' for silicon are  $4 \times 10^{14}$  cm<sup>-3</sup> s<sup>-1</sup> and  $1.9 \times 10^7$  V cm<sup>-1</sup> respectively<sup>24,25</sup>. While for InAs the BTBT parameters were taken as  $9 \times 10^{19}$  cm<sup>-3</sup> s<sup>-1</sup> and  $1.3 \times 10^{6}$  V cm<sup>-1</sup> respectively11.

This comparative simulation study does not include any gate overlap with the source, assumes an ideal interface with no defects due to strain and takes into account trap-assisted tunneling due to dopants induced defect levels. However, it does not take into account bandoffsets due to strain, quantum confinement effects, and

multiple valley BTBT effects. The dynamic nonlocal BTBT model uses the Kane twoband model which is a simple two-band model capable of including one conduction band and one valence band and it is formulated as two coupled Schrodinger-like equations for the conduction-band and valence-band envelope functions. The coupling term is treated by the k•p perturbation method, which gives the solutions of the single electron Schrodinger equation in the neighborhood of the bottom of the conduction band and the top of the valence bands, where most of the electrons and holes, respectively, are concentrated. The valence band and conduction band dispersion relationship are assumed to be bulk-like. This simulation framework has been previously utilized in the literature for simulating tunneling in hetero-structures for both Si/InAs Esaki diodes and TFETs<sup>11,25</sup>. The nanotube TFET has a silicon channel thickness of 10 nm and an inner core gate diameter ( $CG_{dia}$ ) of 100 nm. All contacts are assumed to be Ohmic with zero contact resistance.

- Ionescu, A. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. *Nature* 479, 329–337 (2011).

- Loh, Wei-Yip. *et al.*, Sub-60nm Si Tunnel Field Effect Transistors with I<sub>on</sub> >100 μA/μm. Paper presented at *IEEE Euro. Sol. Stat. Dev. Res. Conf.*, Sevilla, Spain. Sevilla: IEEE.(DOI: 10.1109/ESSDERC.2010.5618418). (2010, September).

- Verhulst, A., Vandenberghe, W., Maex, K. & Groeseneken, G. Boosting the oncurrent of a n-channel nanowire tunnel field-effect. J. Appl. Phys. 104, 064514–064510 (2008).

- Verhulst, A. *et al.*, Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. *IEEE Electron Device Lett.* 29, 1398–1401 (2008).

- Chau, R. et al. Benchmarking nanotechnology for high-performance and lowpower logic transistor applications. *IEEE Trans. Nanotechnol.* 4, 153–158 (2005).

- Fahad, H. & Hussain, M. High-Performance Silicon Nanotube Tunneling FET for Ultralow-Power Logic Applications. *IEEE Trans. Electron Devices.* 60, 1034–1039 (2013).

- Fahad, H. & Hussain, M. Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci. Rep. 2 (2012).

- Fahad, H., Smith, C., Rojas, J. & Hussain, M. Silicon Nanotube Field Effect Transistor with Core-Shell Gate Stacks for Enhanced High-Performance Operation and Area Scaling Benefits. *Nano Lett.* **11**, 4393–4399 (2011).

- 9. Sze, S. Physics of semiconductor devices Ch. 9 (Wiley, New York, 1981).

- Lu, Y. *et al.*, Geometry dependent tunnel FET performance-dilemma of electrostatics vs. quantum confinement. Paper presented at *IEEE Device Research Conference*, South Bend, IN, USA. South Bend: IEEE. (DOI:10.1109/ DRC.2010.5551905). (2010, June).

- Ford, A. et al. Ultrathin body InAs tunneling field-effect transistors on Si substrates. Appl. Phys. Lett. 98, 113105–113108 (2011).

- Tomioka, K., Yoshimura, M. & Fukui, T. Sub 60 mV/decade Switch Using an InAs Nanowire–Si Heterojunction and Turn-on Voltage Shift with a Pulsed Doping Technique. *Nano Lett.* 13, 5822–5826 (2013).

- Hanna, A. & Hussain, M.Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 117, 014310–014317 (2015).

- Bhuwalka, K., Schulze, J. & Eisele, I. A Simulation Approach to Optimize the Electrical Parameters of a Vertical Tunnel FET. *IEEE Trans. Electron Devices.* 52, 1541–1547 (2005).

- Boucart, K. & Ionescu, A. Threshold voltage in tunnel FETs: physical definition, extraction, scaling and impact on IC design. Paper presented at *IEEE Euro. Sol. Stat. Dev. Res. Conf.*, Munich, Germany. Munich: IEEE. (DOI:10.1109/ ESSDERC.2007.4430937). (2007, September)

- Tomioka, K. & Fukui, T. Tunnel field-effect transistor using InAs nanowire/Si heterojunction. Appl. Phys. Lett. 98, 083114–083117 (2011).

- Choi, S., Moon, D., Kim, S., Duarte, J. & Choi, Y. Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. *IEEE Electron Device Lett.* 32, 125–127 (2011).

- Gandhi, R., Chen, Z., Singh, N., Banerjee, K. & Lee, S. CMOS-Compatible Vertical-Silicon-Nanowire Gate-All-Around p-Type Tunneling FETs With ≤ 50 mV/decade Subthreshold Swing. *IEEE Electron Device Lett.* **32**, 1504–1506 (2011).

- Gandhi, R., Chen, Z., Singh, N., Banerjee, K. & Lee, S. Vertical Si-Nanowire-Type Tunneling FETs With Low Subthreshold Swing (≤ 50 mV/decade) at Room Temperature. *IEEE Electron Device Lett.* 32, 437–439 (2011).

- 20. Knoll, L. *et al.*, Demonstration of Improved Transient Response of Inverters with Steep Slope Strained Si NW TFETs by Reduction of TAT with Pulsed IV and NW Scaling. Paper presented at *IEEE Int. Electron Devices Meet.*, Washignton, DC, USA. Washignton: IEEE. (DOI: 10.1109/IEDM.2013.6724560).(2013, December).

- Woo Young, C., Park, B., Jong-Duk, L. & Tsu-Jae King, L. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. *IEEE Electron Device Lett.* 28, 743–745 (2007).

- 22. Krishnamohan, T., Donghyun, K., Raghunathan, S. & Saraswat, K., Double gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60 mV/dec subthreshold slope. Paper presented at *IEEE Int. Electron Devices Meet.*,SanFrancisco,CA,USA.IEDM:IEEE.(DOI:10.1109/ IEDM.2008.4796839)(2008, December).

- Sung Hwan, K., Hei, K., Chenming, H. & Tsu-Jae King, L., Germanium-source tunnel field effect transistors with record high ION/IOFF. Paper presented at *IEEE Symp. on VLSI Tech.*, Honolulu, HI, USA. Honolulu: IEEE. (2009, June).

- 24. Riel, H. *et al.*, InAs-Si heterojunction nanowire tunnel diodes and tunnel FETs. Paper presented at *IEEE Int. Electron Devices Meet.*, San Francisco, CA, USA. San Francisco: IEEE.(DOI: 10.1109/IEDM.2012.6479056).(2012, December).

- 25. Schenk, A., Rhyner, R., Luisier, M. & Bessire, C., Analysis of Si, InAs, and Si-InAs tunnel diodes and tunnel FETs using different transport models. Paper presented at *Int. Conf. Simul. Semicond. Processes Devices.*, Yokohama, Japan. Yokohama: IEEE.(DOI: 10.1109/SISPAD.2011.6035075). (2011, September).

- Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V. & Datta, S. Temperature-Dependent IV Characteristics of a Vertical In<sub>0.53</sub>Ga<sub>0.47</sub>As Tunnel FET. Paper presented at *IEEE Electron Device Lett.* **31**, 564 (2010).

- 27. Dewey, G. et al. Fabrication, characterization, and physics of III–V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing. Paper presented at *IEEE Int. Electron Devices Meet.*, *Washignton, DC, USA. Washignton: IEEE.* (DOI:10.1109/IEDM.2011.6131666). (2011, December).

- Guangle, Z. et al. Vertical InGaAs/InP Tunnel FETs With Tunneling Normal to the Gate. IEEE Electron Device Lett. 32, 1516–1518 (2011).

- Schmid, H. *et al.* Fabrication of vertical InAs-Si heterojunction tunnel field effect transistors. Paper presented at *IEEE Device Research Conference*. , *Santa Barbara, CA, USA. IEEE.* (DOI: 10.1109/DRC.2011.5994479). (2011, June).

- 30. Zhao, H. *et al.* Improving the on-current of In<sub>0.7</sub>Ga<sub>0.3</sub>As tunneling field-effect-transistors by p++/n+ tunneling junction. *Appl. Phys. Lett.* **98**, 093501–093503 (2011).

- Tomioka, K., Yoshimura, M. & Fukui, T. Steep-slope tunnel field-effect transistors using III-V nanowire/Si heterojunction. Paper presented at *IEEE Symp. on VLSI Tech.*,Honolulu,HI,USA.Honolulu:IEEE.(DOI: 10.1109/VLSIT.2012.6242454) (2012, June).

- 32. Zhou, G. *et al.* Novel gate-recessed vertical InAs/GaSb TFETs with record high  $I_{ON}$  of 180  $\mu$ A/ $\mu$ m at  $V_{DS} = 0.5$  V. Paper presented at *IEEE Int. Electron Devices Meet.*,SanFrancisco,CA,USA. IEEE. (DOI:10.1109/IEDM.2012. 6479154) (2012).

- Zhou, G. et al. InGaAs/InP Tunnel FETs With a Subthreshold Swing of 93 mV/dec and Ratio Near. IEEE Electron Device Lett. 33, 782–784 (2012).

- 34. Mohata, D. *et al.* Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction tunnel FETs with high drive current and high on-off ratio. Paper presented at *IEEE Symp. on VLSI*

*Tech.*,Honolulu,HI,USA.Honolulu:IEEE.(DOI: 10.1109/VLSIT.2012.6242457) (2012, June).

- 35. Li, R. et al. AlGaSb/InAs tunnel field-effect transistor with on-current of 78 μA/ μm at 0.5 V. IEEE Electron Device Lett. 33, 363–365 (2012).

- 36. Yu, T., Teherani, J., Antoniadis, D. & Hoyt, J. InGa<sub>0.53</sub>As<sub>0.47</sub>- GaAs<sub>0.5</sub>Sb Quantum-Well Tunnel-FETs With Tunable Backward Diode Characteristics. IEEE Electron Device Lett. 34, 1503–1505 (2013)

#### **Acknowledgments**

We acknowledge the financial support under KAUST Office of Competitive Research Grants CRG-1 Award (CRG-1-2012-HUS-008) for this work.

#### Author contributions

MMH conceived the idea and directed the experiment. ANH carried out the experiment. HMF provided experimental support. All analyzed the data and wrote the paper.

#### Additional information

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Hanna, A.N., Fahad, H.M. & Hussain, M.M. InAs/Si Hetero-Junction Nanotube Tunnel Transistors. *Sci. Rep.* 5, 9843; DOI:10.1038/srep09843 (2015).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/