# SCIENTIFIC REPORTS

### **OPEN**

SUBJECT AREAS: APPLIED PHYSICS ELECTRICAL AND ELECTRONIC ENGINEERING

> Received 5 August 2013

Accepted 6 March 2014

> Published 9 April 2014

Correspondence and requests for materials should be addressed to T.G.K. (tgkim1@korea. ac.kr)

## Transparent Multi-level Resistive Switching Phenomena Observed in ITO/ RGO/ITO Memory Cells by the Sol-Gel Dip-Coating Method

Hee-Dong Kim, Min Ju Yun, Jae Hoon Lee, Kyoeng Heon Kim & Tae Geun Kim

School of Electrical Engineering, Korea University, Anam-dong 5-ga, Sungbuk-gu, Seoul 136-701, Republic of Korea.

A reduced graphene oxide (RGO)-based transparent electronic memory cell with multi-level resistive switching (RS) was successfully realized by a dip-coating method. Using ITO/RGO/ITO structures, the memory device exhibited a transmittance above 80% (including the substrate) in the visible region and multi-level RS behavior in the 00, 01, 10, and 11 states by varying the pulse height from 2 V to 7 V. In the reliability test, the device exhibited a good endurance of over  $10^5$  cycles and a long data retention of over  $10^5$  s at 85°C in each state. We believe that the RGO-based transparent memory presented in this work could be a milestone for future transparent electronic devices.

Transparent devices are important because of their potential applications in areas of invisible electronics used in transparent transistors and diodes. However, studies on transparent nonvolatile memory devices, which are indispensable for invisible electronics, are still lacking because of the inherent opaqueness of silicon, a basic material used in the silicon-based technology that captures the majority of the nonvolatile memory market<sup>1</sup>. Among the various types of memory devices, resistive random access memory (ReRAM) devices have attracted much attention for use in high integration density and fast memory applications using several metal oxides (or nitrides), organic materials, and carbon-based materials as the resistance layer<sup>2-9</sup>. Further, these ReRAM devices exhibit good electrical performance. Among the various resistance materials, carbon materials have recently drawn attention from various research fields because of their excellent electrical, optical, and mechanical properties.

Recently, various carbon materials such as carbon nanotubes, graphene and graphene-oxide (GO) are being explored as alternatives to the metals and resistance layers in ReRAM devices owing to their superior properties such as flexibility and transparency. In previous works<sup>7,8</sup>, some researchers have studied GO as a resistance material and successfully demonstrated the feasibility of bipolar switching in a GO-based ReRAM with an on/off current ratio (CR) of 10<sup>3</sup>, while possessing flexibility and transparency. However, only the feasibility of the resistance materials was studied without considering either their reliability, such as retention and endurance, or multi-level operation along with their pulsed mode AC characteristics.

In particular, fluctuations in the critical switching parameters such as the set/reset pulse conditions for multilevel operations and the limiting factor for endurance are still issues that must be overcome in potential transparent/flexible ReRAM applications using carbon materials. Moreover, the resistive switching (RS) characteristics and physical mechanism of reduced GO (RGO) has not been reported yet. RGO is made by chemically removing the oxygen ion from GO with a high resistive state (HRS). Accordingly, one carbon atom in the RGO exists in the cationic state, and its resistance is changed electrically to a low resistance state (LRS). This means that the soft breakdown process for a first set operation (or forming process) can be omitted. According to the reported literature<sup>10</sup>, the soft breakdown process is known as a major cause of device degradation. Therefore, for these reasons, it can be expected that device reliability can be improved without destruction from a high electrical field during the forming process. In addition, in this system, we can operate the RS of RGO-based ReRAM cells from the HRS and LRS by using a metal such as indium tin oxide (ITO) that can supply oxygen ions.

In this work, we investigate the electrical/optical characteristics of the transparent ITO/RGO/ITO memory cells to show their multilevel switching properties and their reliability as a transparent ReRAM device in pulsed operation.

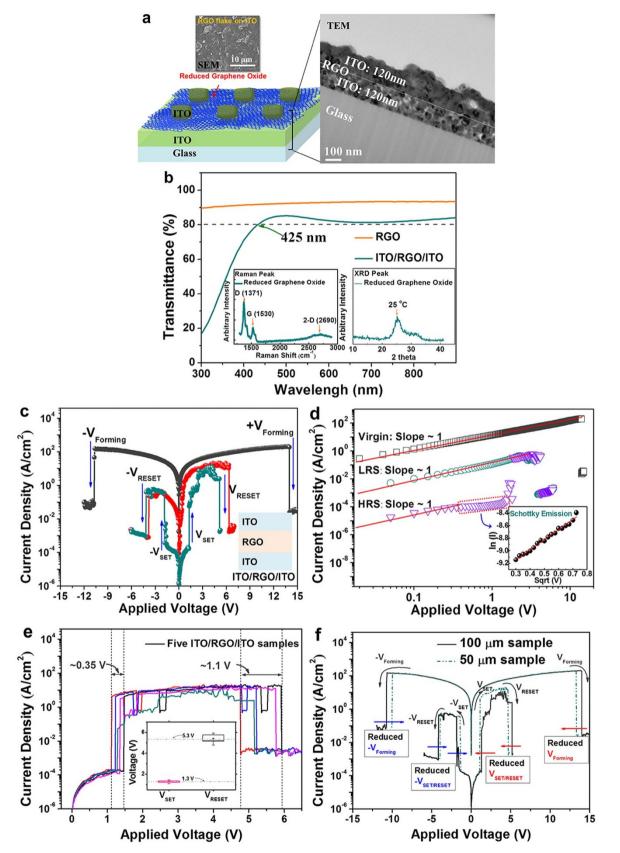

#### Results

In order to quantitatively evaluate the transparency of the ITO/RGO/ ITO cells, we measured the transmittance of the sample as a function of the wavelength from 300 nm to 900 nm, as shown in Fig. 1(b). The optical transparency of the ITO/RGO/ITO/glass structure was approximately 80%, averaged over the visible wavelength region from 425 nm to 900 nm. Therefore, we believe that this result can be immediately applied to a fully transparent ReRAM. To identify the sp<sup>2</sup> structure of the RGO, the Raman spectra of the RGO were obtained using a micro-Raman microscope, as shown in the inset in Fig. 1(b). The D peak, G peak, and 2D peak were observed at around 1371, 1530, and 2690 cm<sup>-1</sup>, respectively, indicating that the RGO mainly consists of sp<sup>2</sup> graphitic-bonded carbon<sup>11,12</sup>. The strong D peak intensity originated from the scattering of the abundant edges of the RGO. In addition, we measured the X-ray diffraction (XRD) spectra of the RGO to confirm the RGO structure, as shown in the inset in Fig. 1(b). The RGO exhibited a (002) peak centered at  $2\theta = 25^{\circ}$ , corresponding to an interlayer distance of 3.53 Å<sup>12</sup>. This XRD result was related to the exfoliation and reduction processes of GO and the removal of the intercalated water molecules and the oxide groups.

#### Discussion

We measured the unipolar switching current-voltage (I-V) characteristic curves using a dc voltage sweep (0 V  $\rightarrow \pm 15$  V) applied to the ITO/RGO/ITO cell at room temperature to confirm the RS properties of the RGO-based ReRAM cell, as shown in Fig. 1(c). The details of the measurement setup are shown in Fig. S3 of the Supplementary Information. In the I-V characteristic curves, the current density was normalized using  $I/\pi r^2$  with a radius of 50  $\mu$ m. Initially, RS behavior was not observed; however, following the formation process (or first reset operation) with voltages from 0 V to +15 V (or -15 V), a sudden decrease in the current was observed near +13 V (or -11 V). The ITO/RGO/ITO device was thereby switched to its HRS mode. The device then achieved a LRS at approximately  $\pm 2 \text{ V} (\text{V}_{\text{SET}})$  when the voltage was swept from zero to a positive (or negative) value. When the voltage was swept to a positive (or negative) voltage over the reset voltage, the device switched back to the HRS at approximately  $\pm 5$  V (V<sub>RESET</sub>), and nonvolatile switching was achieved. On the other hand, when we used conventional Ti and Pt electrodes as the top/bottom electrodes in the RGO-based ReRAM cells (Fig. S4), the first reset operation did not occur at  $\pm 15$  V. From this result, we can conclude that the oxygen ions in the ITO-electrode are the main key for the reset switching process.

To explain the conduction mechanism of the ITO/RGO/ITO cell, the *I*-*V* curves were replotted on a log-log plot to reveal the power law relation (I  $\propto$  V<sup>m</sup>)<sup>13-17</sup>, as shown in Fig. 1(d). The slopes of the virgin state and the LRS were approximately one, indicating ohmic behavior (I  $\propto \sim V^1$ ). However, the *I*-*V* characteristics of the HRS were more complicated and could be divided into two regions. In the low-voltage region from 0 to 0.4 V, the I-V characteristics exhibited a linear relation, corresponding to ohmic behavior due to thermally generated free electrons<sup>13,16</sup>. In the high-voltage region from 0.4 V to V<sub>SET</sub>, the *I*–*V* curve exhibited a nonlinear relation, suggesting a different conduction mechanism. Further analysis indicated a linear relation between ln(I) and V1/2, as shown in the inset of Fig. 1(d), suggesting that Schottky emission is the dominant conduction mechanism in the higher voltage region of the HRS since the GO layer acts as an energy barrier between the ITO electrode and RGO layer<sup>14,17,18</sup>. To argue the Schottky emission<sup>19</sup>, we evaluated the effective barrier height ( $\Phi_{\text{eff}}$ ), using a temperature dependency on the current to ague the Schottky emission, as shown in Fig. S5. It was calculated to be  $\sim$ 0.1 eV in the temperature range of 30–100°C. This value reasonably agree to the one typically reported in the literature (<0.15 eV) to explain the Schottky emission<sup>16</sup>.

Then, to evaluate the device-to-device uniformity of the RGO based ReRAM, we measured the I–V characteristics in the positive bias region for five ITO/RGO/ITO devices, as shown in Fig. 1(e). In this experiment, the variations in V<sub>SET</sub> and in V<sub>RESET</sub> are ~0.35 V and ~1.1 V, respectively, and the average V<sub>SET</sub> and in V<sub>RESET</sub> are ~1.3 V and ~5.3 V, as shown in the inset of Fig. 1(e). In addition, to investigate the size dependence of the ITO/RGO/ITO cell, we fabricated two samples with different diameters of 50 µm and 100 µm, and measured the V<sub>Forming</sub>, V<sub>SET</sub> and V<sub>RESET</sub>, as shown in Fig. 1(f). As a result, we found that both samples successfully operated without problems but slightly reduced V<sub>Forming</sub>, V<sub>SET</sub> and V<sub>RESET</sub> and V<sub>RESET</sub> were observed for the 50 µm diameter sample.

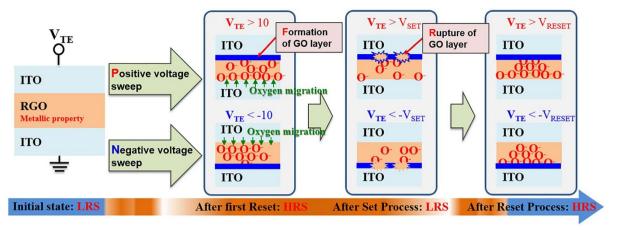

Further, we present a schematic for the set and reset process of the ITO/RGO/ITO cell with respect to the voltage sweep in the positive and negative bias region in Fig. 2. On the basis of the electrical analyses, we propose a possible reaction model as schematically illustrated in Fig. 2 to explain the RS process in the RGO films. The initial resistance state of the RGO-based ReRAM cell is electrically LRS. However, the memory state is changed from the LRS to high resistance state (HRS), when first-round reset voltage (or V<sub>Forming</sub>) is applied to the ITO top electrode, by forming a GO layer through the migration of oxygen ions within the RGO layer from the ITO electrode. The formed GO layer plays a role of an energy barrier like Schottky barrier, which maintains the device at the HRS until second-round set voltage is applied to the device. On the other hand, once the set voltage is applied to the device, the GO layer in the active region is ruptured by out-diffusion of oxygen ions, and the memory state returns to the LRS. Consequently, we conclude that the migration of oxygen ions is a main key to form the GO layer for the reset switching process. In addition, as shown in Fig. 1(d), we observed the asymmetrical DC I-V behavior, which is attributed to the I-V behavior of *n*-type materials. This is because the oxygen ions injected form the ITO during the forming process play a role of *n*-type dopant in the RGO layer.

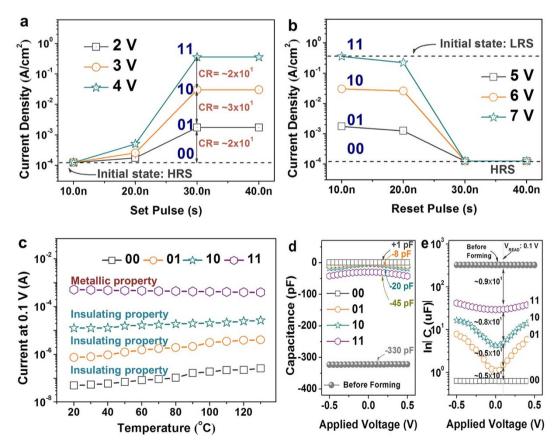

To define the program and erase (P/E) conditions for multilevel memory applications, we investigated the pulse characteristics of the ITO/RGO/ITO device. In this experiment, we measured the typical P/E properties of the unipolar cells under ac pulse biases in the pulse width range from 10 ns to 40 ns and pulse height range from 2 V to 4 V. Figures 3(a) and (b) show the sample current versus P/E speed. In the program test, the sample switched perfectly from the 00 state to the 01 state at +2 V/30 ns, 10 state at +3 V/30 ns, and 11 state at +4 V/30 ns and changed completely from the 01, 10, and 11 states to the reset state at +5 V/30 ns, 10 state at +6 V/30 ns, and 11 state at +7 V/30 ns, respectively, in the erase test, which was close to the highest reported values for GO-based ReRAMs so far.

Figure 3(c) shows the resistance at the 00, 01, 10, and 11 states as a function of temperature in the range from 290 K to 410 K. The resistance increases with increasing temperature, corresponding to the conduction properties of metallic materials. The conductive resistance as a function of temperature change can be written as  $R(T) = R_0[1 + \alpha(T - T_0)]$ , where  $R_0$  is the resistance at temperature  $T_0$  (300 K), and  $\alpha$  is the resistance temperature coefficient<sup>20–22</sup>. Thus, we can calculate the temperature coefficient of the resistance at the LRS (11 state) to be  $\alpha = 49.8 \times 10^{-4} \text{ K}^{-1}$ . In contrast to the conductive behavior of the resistance at each state, the device clearly shows insulating or semiconducting behavior. On the other hand, compared with the 00 state, the current increment at 01/10 states were reduced. These results indicate that the insulating properties of the materials have weakened, similar to the metal-doped insulator materials.

We measured the capacitance–voltage (C–V) characteristics of each state for bipolar switching to more thoroughly understand the switching mechanism. Figure 3(d) shows the typical C–V characteristic curves of the ITO/RGO/ITO MIM structure devices. In this result, the capacitance at 0 V was observed to be from ~1 pF (pos-

Figure 1 | Material property of proposed RGO-based ReRAM and its resistive switching in dc mode. (a), Schematic drawing and TEM image of the proposed ITO/RGO/ITO memory cell, with SEM image of the RGO flakes adsorbed on the ITO layer. (b), Optical transmission spectrum of the ITO/RGO/ITO/glass device; the inset shows the Raman shift and XRD results of RGO on the glass. (c), *I*–*V* characteristics of the ITO/RGO/ITO device; the inset shows the ITO/RGO/ITO structures. (d), Linear fitting for the *I*-*V* curves on a log-log plot; the inset shows the ln(I) versus  $V^{1/2}$  plot in the higher voltage region of the HRS. (e), Statistical results of set and reset voltages for five ITO/RGO/ITO devices. (f), Area dependence of forming process, set and reset voltages for ITO/RGO/ITO devices.

Figure 2 | Switching mechanism of RGO-based ReRAMs. Schematics for the set and reset processes of the ITO/RGO/ITO memory cell with respect to the voltage sweep in the positive and negative bias region.

itive value) at the HRS to -45 pF (negative value) at the LRS. A similar *C*-*V* result was reported for the ReRAM capacitance analysis at the HRS and LRS with unipolar switching<sup>23</sup>. On the other hand, a positive capacitance value was measured at the 00 state, whereas the capacitances at the 01, 10, and 11 states showed negative values. In a previous report<sup>24</sup>, You et al. presented results for NiO thin films using impedance spectroscopy analysis. They reported that the reset state could be described as a Conventional RLC circuit, whereas the set state could be described as an LRR' circuit, which is composed of a

series connection of an inductor and resistors. The reactance (X), capacitance (C), and inductance (L) have the following relation:  $X = \omega L = -1/\omega C$ , (X > 0, inductive; X < 0, capacitive).

For example, if the sample is capacitive, the measurement system exhibits negative reactance and capacitance values equivalent to  $-1/\omega X$ , which is positive as expected. On the other hand, if the sample is inductive, the measurement system exhibits positive reactance and negative capacitance. Therefore, we believe that the reset state can be regarded as a conventional LRC circuit with a series

Figure 3 | Resistive switching in pulse mode and conduction behavior of the proposed RGO-based ReRAMs. (a), (b), Typical (a) program and (b) erase characteristics measured using ac pulse biases with pulse widths that range from 10 ns to 40 ns and pulse heights that range from 2 V to 7 V for the ITO/RGO/ITO cell. (c), Effect of temperature in the range from  $20^{\circ}$ C to  $130^{\circ}$ C on the 00, 01, 10, and 11 states of the ITO/RGO/ITO memory cells. (d), (e), *C*–V characteristic curves of the 00, 01, 10, and 11 states of the ITO/RGO/ITO memory cells. (d), (e), *C*–V

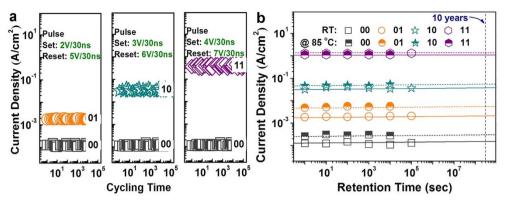

Figure 4 | Reliability of the proposed RGO-based ReRAMs. (a), Endurance characteristics for up to  $10^5$  cycles measured at  $V_{READ} = 0.1$  V for the ITO/RGO/ITO cells. (b), Retention characteristics measured at  $V_{READ} = 0.1$  V for the ITO/RGO/ITO cells at  $25^{\circ}$ C and  $85^{\circ}$ C.

connection of inductor/resistor/capacitor, whereas the set state is an LRR' circuit with a series connection of inductor/resistors. In addition, the capacitance ratio (C<sub>p</sub>R) is clearly distinguished to be ~0.5 × 10<sup>1</sup> for the 00 and 01 states, ~0.5 × 10<sup>1</sup> for the 01 and 10 states, and ~0.8 × 10<sup>1</sup> for the 10 and 11 states, as shown in Fig. 3(e) using a semi-log plot. Compared with the CR in the *I*-V curves, the correlation with the C<sub>p</sub>R is expressed as C<sub>p</sub>R = ~0.5CR in this study.

In addition, we performed an endurance test for the ReRAM device to examine the reliability of the ITO/RGO/ITO device, as shown in Fig. 4(a). We used pulses of 2 V/30 ns, 3 V/30 ns, and 4 V/30 ns for the 01, 10, and 11 states, respectively, and 5 V/30 ns, 6 V/30 ns, and 7 V/30 ns pulses for the reset (00) state. Steady RS characteristics without degradation over 10<sup>5</sup> cycles in the 00, 01, 10, and 11 states were observed at  $V_{READ} = +0.1$  V, indicating excellent nonvolatile and nondestructive readout properties of the proposed ITO/RGO/ITO cell. Moreover, good retention characteristics were observed for the ITO/RGO/ITO memory cell, shown by the log-log plot in Fig. 4(b). The retention test was started in the reset state at 25°C and 85°C after 10<sup>5</sup> cycles. The resistance values in the 00, 01, 10, and 11 states were stable without degradation over 10<sup>5</sup> s, indicating that the devices are nonvolatile and can be read nondestructively. Using these results, we extrapolated the current density against the read delay time to predict the long-term retention of the sample, and the observed CRs at 85°C were as follows:  $\sim 10^1$  between the 00 and 01 states,  $\sim 10^1$  between the 01 and 10 states, and  $\sim 10^1$  between the 10 and 11 states at 3  $\times$  10<sup>8</sup> s. Therefore, the ITO/RGO/ITO cells displayed excellent nonvolatile and nondestructive readout properties.

In conclusion, we have fabricated RGO-based transparent ReRAM devices by dip-coating. These device exhibited unipolar RS characteristics with a CR of  $10^5$  and multilevel RS of 00, 01, 10, and 11. An endurance of  $10^5$  cycles for each state was achieved, and the retention time of the device was maintained over 10 years at  $85^\circ$ C. This demonstration of the performance of RGO-based transparent ReRAM devices provides an important step toward enabling future transparent device applications.

#### Methods

Preparation for the ITO/RGO/ITO samples by the dip-coating method and RF sputtering. A 120-nm thick ITO-metal electrode was deposited on glass using a radio-frequency (RF) sputtering system. Prior to dip-coating, the RGO powders dissolved in a known volume of dichlorobenzene (DCB) were subjected to ultrasonication for 2 hours to yield a stable suspension of RGO (concentration = 1 mg/mL). This suspension was used for RGO adsorption. Subsequently, we fabricated flake films of pristine RGO on the ITO layers by the dip-coating method. The thickness of RGO film measured by  $\alpha$ -step scanner was ~17 nm. Because the thickness of a monolayer of RGO has been reported to be 0.9–1.1 nm in a tapping AFM mode<sup>12</sup>, the RGO film used in this experiment is estimated to be approximately 15–18 monolayers of RGO. Finally, an ITO electrode with a thickness of 120 nm and a diameter of 100 µm was deposited. Figure 1(a) shows a schematic drawing and a transmission electron microscopy (TEM) cross-sectional image of the proposed ITO/

SCIENTIFIC REPORTS | 4:4614 | DOI: 10.1038/srep04614

RGO/ITO memory cell, together with a scanning electron microscopy (SEM) image of the RGO flake. Detailed fabrication process of the RGO is also presented in Figs. S1 and S2 of the Supplementary Information.

- 1. Wager, J. F. Transparent Electronics. Science 300, 1245-1246 (2003).

- Kim, H.-D. et al. Large resistive-switching phenomena observed in Ag/Si<sub>3</sub>N<sub>4</sub>/Al memory cells. Semicond. Sci. Technol. 25, 065002 (2010).

- Chen, L. et al. Highly Uniform Bipolar Resistive Switching With Al<sub>2</sub>O<sub>3</sub> Buffer Layer in Robust NbAlO-Based RRAM. *IEEE Electron Device Lett.* 31, 356–358 (2010).

- Ji, Y., Lee, S., Cho, B., Song, S. & Lee, T. Flexible Organic Memory Devices with Multilayer Graphene Electrodes. ACS Nano 5, 5995–6000 (2011).

- Kim, H.-D., An, H.-M., Seo, Y. & Kim, T. G. Transparent Resistive Switching Memory Using ITO/AlN/ITO Capacitors. *IEEE Electron Device Lett.* 32, 1125–1127 (2011).

- Wu, M.-C., Jang, W.-Y., Lin, C.-H. & Tseng, T.-Y. A study on low-power, nanosecond operation and multilevel bipolar resistance switching in Ti/ZrO<sub>2</sub>/Pt nonvolatile memory with 1T1R architecture. *Semicond. Sci. Technol.* 27, 065010 (2012).

- Zhuge, F. et al. Mechanism of nonvolatile resistive switching in graphene oxide thin films. Carbon 49, 3796–3802 (2011).

- Hong, S. K., Kim, J. E., Kim, S. O., Choi, S.-Y. & Cho, B. J. Flexible Resistive Switching Memory Device Based on Graphene Oxide. *IEEE Electron Device Lett.* 31, 1005–1007 (2010).

- He, C. et al. Multilevel resistive switching in planar graphene/SiO<sub>2</sub> nanogap structures. ACS Nano 6, 4214–4221 (2012).

- Liu, C.-Y., Huang, J. J., Lai, C. H. & Lin, C. H. Influence of embedding Cu nanoparticles into a Cu/SiO<sub>2</sub>/Pt structure on its resistive switching. *Nanoscale Res. Lett.* 8, 156 (2013).

- Zhang, J. & Zhao, X. S. Conducting Polymers Directly Coated on Reduced Graphene Oxide Sheets as High-Performance Supercapacitor Electrodes. J. Phys. Chem. C 116, 5420–5426 (2012).

- Moon, I. K., Lee, J., Ruoff, R. S. & Lee, H. Reduced graphene oxide by chemical graphitization. *Nat. Commun.* 1, 1–6 (2010).

- Kim, H.-D., An, H.-M. & Kim, T. G. Ultrafast Resistive-Switching Phenomena Observed in NiN-Based ReRAM Cells. *IEEE Trans. Electron Devices* 59, 2302–2307 (2012).

- Hu, W. et al. Opportunity of Spinel Ferrite Materials in Nonvolatile Memory Device Applications Based on Their Resistive Switching Performances. J. Am. Chem. Soc. 134, 14658–14661 (2012).

- 15. Ye, C. et al. Multilevel Conductance Switching of Memory Device through Photoelectric Effect. J. Am. Chem. Soc. 134, 20053–20059 (2012).

- Ahn, Y. et al. Concurrent presence of unipolar and bipolar resistive switching phenomena in pnictogen oxide Sb<sub>2</sub>O<sub>5</sub> films. Appl. Phys. Lett. 112, 114105 (2012).

- 17. Bishop, S. M. *et al.* Ion implantation synthesis and conduction of tantalum oxide resistive memory layers. *J. Vac. Sci. Technol. B* **31**, 012203 (2013).

- Zhu, Y. *et al.* Nonvolatile resistive switching behaviour and the mechanism in Nd:BiFeO<sub>3</sub>/Nb:SrTiO<sub>3</sub> heterostructure. *J. Phys. D: Appl. Phys.* 46, 215305 (2013).

- Kenney, C., Saraswat, C., Taylor, B. & Majhi, P. Thermionic field emission explanation for nonlinear Richardson plots. *IEEE Trans. Electron Devices* 58, 2423–2429 (2011).

- You, Y.-H. *et al.* Impedance spectroscopy characterization of resistance switching NiO thin films prepared through atomic layer deposition. *Appl. Phys. Lett.* 89, 222105 (2006).

- Zhu, X. *et al.* Observation of conductance quantization in oxide-based resistive switching memory. *Adv. Mater.* 24, 3941–3946 (2012).

- White, S. I., Vora, P. M., Kikkawa, J. M., Fischer, J. E. & Winey, K. I. Temperature-Dependent Resistive Switching in Bulk Silver Nanowire – Polystyrene Composites. J. Phys. Chem. C 114, 22106–22112 (2010).

- 23. Choi, J. S. et al. Different resistance switching behaviors of NiO thin films deposited on Pt and SrRuO3 electrodes. Appl. Phys. Lett. 95, 022109 (2009).

- 24. You, Y.-H. et al. Impedance spectroscopy characterization of resistance switching NiO thin films prepared through atomic layer deposition. Appl. Phys. Lett. 89, 222105 (2006).

#### Acknowledgments

This research was supported by a National Research Foundation of Korea (NRF) grant funded by the Ministry of Education, Science and Technology (MEST) (No. 2011-0028769, 2013-044975). The authors also thank for the support of the Samsung Semiconductor Research Center at Korea University.

#### Author contributions

T.G.K. and H.-D.K. conceived and designed the experiment. M.J.Y., J.H.L. and K.H.K. prepared the samples and H.-D.K., M.J.Y., J.H.L., K.H.K. conducted the experiment. T.G.K. and H.-D.K. analyzed the data and wrote the manuscript. T.G.K. supervised the

experiments and contributed to manuscript preparation. All authors discussed the progress of research and reviewed the manuscript.

#### Additional information

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Kim, H.-D., Yun, M.J., Lee, J.H., Kim, K.H. & Kim, T.G. Transparent Multi-level Resistive Switching Phenomena Observed in ITO/RGO/ITO Memory Cells by the Sol-Gel Dip-Coating Method. Sci. Rep. 4, 4614; DOI:10.1038/ srep04614 (2014).

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. The images in this article are included in the article's Creative Commons license, unless indicated otherwise in the image credit; if the image is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the image. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/