# SCIENTIFIC REPORTS

### **OPEN**

SUBJECT AREAS: NANOWIRES SYNTHESIS AND PROCESSING

> Received 5 September 2013

Accepted 15 January 2014

Published 3 February 2014

Correspondence and requests for materials should be addressed to C.H.Y. (chye@issp.ac. cn)

## Automatic Release of Silicon Nanowire Arrays with a High Integrity for Flexible Electronic Devices

Luo Wu, Shuxin Li, Weiwei He, Dayong Teng, Ke Wang & Changhui Ye

Key Laboratory of Materials Physics, Institute of Solid State Physics, and Key Laboratory of New Thin Film Solar Cells, Chinese Academy of Sciences, Hefei 230031, P. R. China.

Automatic release and vertical transferring of silicon/silicon oxide nanowire arrays with a high integrity are demonstrated by an Ag-assisted ammonia etching method. By adding a water steaming step between Ag-assisted HF/H<sub>2</sub>O<sub>2</sub> and ammonia etching to form a SiO<sub>x</sub> protective layer sheathing Si nanowires, we can tune the composition of the nanowires from SiO<sub>x</sub> ( $0 \le x \le 2$ ) to Si nanowires. Ag plays a key role to the neat and uniform release of Si/SiO<sub>x</sub> nanowire arrays from Si wafer in the ammonia etching process. The vertical Si nanowire array device, with both sides having high-quality Ohmic contact, can be transferred to arbitrary substrates, especially on a flexible substrate. The method developed here offers a facile method to realize flexible Si nanowire array functional devices.

ecause of their abilities to scatter and trap incident light, large surface to volume ratio, and other special electronic and optical properties, vertical silicon nanowire (SiNW) arrays are considered as promising D building blocks for a range of applications, such as solar cells<sup>1-3</sup>, biosensors<sup>4-7</sup>, thermoelectric devices<sup>8-10</sup>, vertical surround-gate field-effect transistors<sup>11-13</sup>, and Li batteries<sup>14,15</sup>. To date, a wide range of methods including vapor-liquid-solid growth<sup>16,17</sup>, reactive ion etching<sup>18</sup>, electron beam lithography<sup>19,20</sup>, and metal-assisted chemical etching (MACE)<sup>21,22</sup> have been developed as common ways to produce SiNW arrays. Considering the low-cost, simplicity, and tunability of SiNW parameters (e.g., length, diameter, cross-sectional shape, orientation, and crystalline quality), the MACE method is highly promising. However, with the ever-increasing demand for flexibility in the applications in portable devices, SiNW arrays grown on the rigid Si wafer render the difficulty in the real-world applications. It is still a great challenge to release and transfer the as-grown SiNW arrays to an arbitrary flexible substrate with a high integrity. So far, several methods have been developed to detach SiNWs from Si substrates, such as sonication<sup>23,24</sup>, mechanical scraping by razor blade<sup>2,25,26</sup>, dry removal with a polymer (polydimethylsiloxane (PDMS), polymethylmethacrylate (PMMA), or polyvinylidene fluoride-hexafluoropropylene copolymer (PVDF-HFP))<sup>15,27,28</sup>, and alkali hydroxides wet chemical etching<sup>29</sup>. Sonication is based on mechanical force to release SiNWs, which usually leads to the shortening of long SiNWs during the process because of the random distribution of the force along the length of vertical SiNWs. Mechanical scraping by razor blade leads to the similar results to sonication. The polymer-based peeling off of SiNWs either results in the bundling of SiNW tips within the polymer and damage of the vertical alignment because of extremely high insertion pressure<sup>28</sup>, or leads to nonuniform length for SiNWs because of the fracture of SiNWs at random locations during the transferring process<sup>15</sup>. Alkali hydroxides wet chemical etching releases SiNWs with uniform length, however, the released SiNWs differ in diameter and thus lead to the successive release of SiNWs, with thin nanowires releasing before thicker ones, limiting the integrity of the released SiNW arrays. Recently, Zheng's group has proposed an approach to releasing SiNW arrays from Si wafer<sup>30,31</sup>. In their work, Ag selective etching was proposed to weaken the attachment of SiNWs on Si wafer, and SiNWs could be released with a polymer-based peeling off process.

#### Results

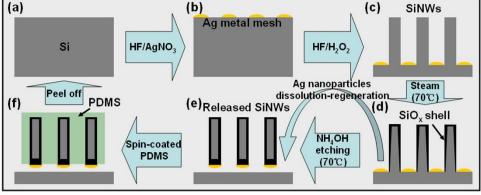

Herein, we report an effective method to automatically release SiNW arrays readily from Si wafer with a high integrity. We do not need to apply external forces to peel off SiNWs from Si wafer, and therefore, damage to SiNWs could be suppressed dramatically. The advantage of our method lies in that SiNW arrays could be released as a whole with an unprecedented integrity. The process for releasing SiNW arrays is illustrated in Figure 1. In the first step, we prepared SiNW arrays following the method as reported previously (Figure 1a–c, Supplementary Fig. S1)<sup>32</sup>. Subsequently, a protective SiO<sub>x</sub> layer, which was found to be a key factor to prevent the SiNW arrays

Figure 1 | Schematic illustrations of the fabrication procedure for auto-releasing SiNW arrays. (a) Clean Si substrate, (b) Ag metal mesh film on Si substrate, (c) SiNW arrays after the  $HF/H_2O_2$  etching, (d) Formation of SiO<sub>x</sub> layer on the outer wall of SiNW after a steaming step, (e) Automatic release of SiNW arrays from Si substrate after an ammonia etching step (but still attached to the mother wafer due to the capillary force), (f) Spin-coating PDMS layer on the detached SiNW arrays.

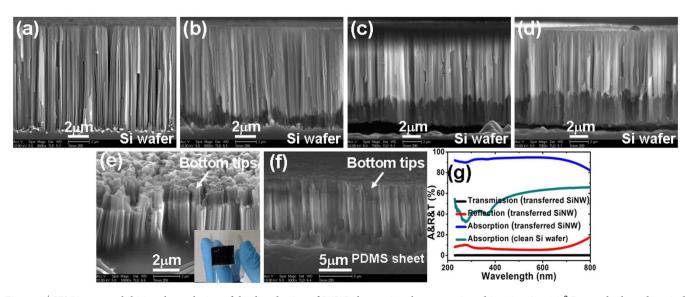

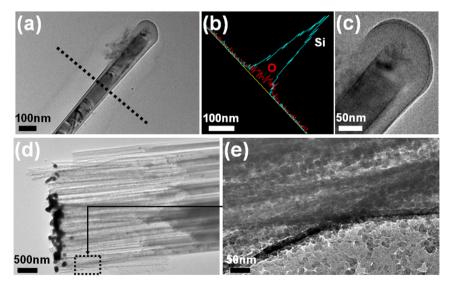

from being fully oxidized in a later ammonia etching process, was produced on the outer wall of SiNWs by steaming in a 70 °C water bath (Figure 1d). To automatically release SiNW array from Si wafer, we immersed the wafer in the ammonia etching solution to weaken the attachment of SiNW array on Si wafers (by faster Ag-catalyzed oxidization of Si at the root of SiNWs, we will discuss this later) and release SiNW arrays from the wafer (Figure 1e). SiNW arrays could automatically release from the mother wafer without changing the orientation and the structure. To transfer the automatically released SiNW arrays to an arbitrary receiver substrate, a layer of spin-coated PDMS was applied (Figure 1f) (The process for automatic release and vertical transferring SiO<sub>x</sub>NW arrays is illustrated in Supplementary Fig. S2). Figure 2a-d show scanning electron microscopy (SEM) images of SiNW arrays with different ammonia etching times, where a clear bright-dark contrast can be observed close to the bottom of SiNWs. From the selective-area electron diffraction (SAED) patterns in transmission electron microscopy (TEM) (Figure 3a-d), the bottom of SiNWs is oxidized, whereas the bulk of the nanowires are still monocrystalline. The darker contrast in Figure 2b-d close to the bottom of the nanowires is due to the formation of SiO<sub>x</sub> which is

less conductive compared to Si. From the elemental mapping analysis in Figure 3e–g, we clearly see the distribution of oxygen at the bottom as well as the shell of SiNWs. Interestingly, we can assign the dark particles at the bottom of SiNWs (Figure 3a) as Ag, as evidenced from Figure 3g. It is noteworthy that the surface of the released SiNW arrays is still smooth after detaching from Si wafer (Figure 3h top, upper and lower), which indicates that the hillock formation issue is irrelevant herein.

Auto-releasing from the mother wafer renders the ease of transferring the SiNW arrays to arbitrary substrates (especially flexible substrates) and facilitates the fabrication of functional electronic devices. Vertical transferring of the released nanowire arrays to a substrate was realized readily by attaching an adhesive receiver substrate to the top of the nanowire arrays and picking up from Si mother wafer. Figure 2e and f show examples of using flexible transparent tape and PDMS as the adhesive receiver substrates. Automatically released SiNW arrays can be readily transferred to a PDMS sheet by a spin-coating and heating process. The nanowire arrays are of high integrity (Figure 2f). Figure 2e shows that SiNW arrays were transferred to a transparent adhesive tape over a large

Figure 2 | SEM images exhibiting the evolution of the distribution of Si/SiO<sub>x</sub> by varying the ammonia etching time in a 70 °C water bath, and vertical transferring of the released SiNW arrays on flexible substrates. Steamed samples, ammonia etching for (a) 0 min, (b) 5 min, (c) 10 min, and (d) 20 min. Vertical transferring SiNW array (e) on a transparent adhesive tape (inset is the optical image of the sample) and (f) on a PDMS sheet. (g) The optical spectra of the transferred SiNW array in (e) and clean Si wafer. The darker contrast in (b)–(d) of the lower part of the nanowires is due to the formation of SiO<sub>x</sub> which is less conductive compared to Si.

Figure 3 | TEM and SEM characterization of the released SiNW arrays. (a) TEM image of a cluster of SiNWs. The electron diffraction patterns of SiNW arrays at different positions: (b) 1 µm, (c) 2.5 µm, and (d) 4 µm from the very bottom of SiNW. The elemental mapping of the released SiNWs in square dashed box in (a): (e) Si, (f) O, and (g) Ag. (h) SEM image of the SiNW arrays at different locations.

area with a high degree of vertical alignment. From the insets in Supplementary Fig. S2j and Figure 2e, SiO<sub>x</sub>NW arrays are in a pale color, whereas SiNW arrays in a black color, reflecting the difference in the visible light absorption. Although the thickness of SiNW array films is only several micrometers (compared to Si wafer of hundreds of micrometers in thickness in the application of solar cells), the

(e)

absorption of the visible light is greater than 90% (Figure 2g), which indicates a rather striking light trapping effect.

500nm

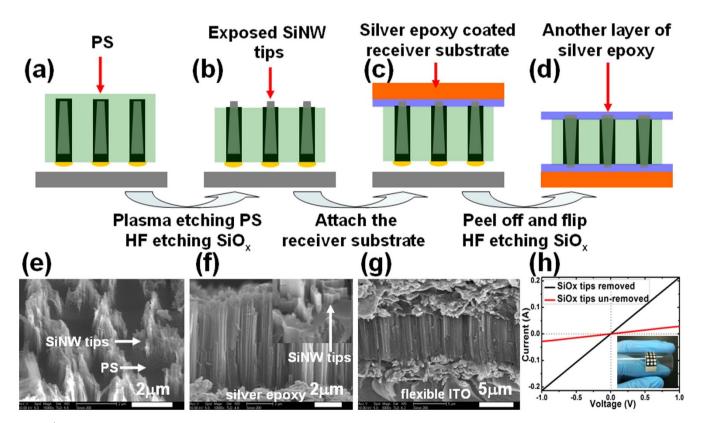

Finally, vertical transferring of SiNW arrays, with metallic contacts on both sides, to arbitrary substrates was realized by using Ag epoxy as the intermediary adhesive. The overhead images in Figure 4 are the schematic illustration of the entire process. The current-voltage (I-V)

Figure 4 | Schematic illustration of the fabrication procedure for flexible SiNW array electronic devices. (a) Just released SiNW arrays are filled with PS. (b) SiNW arrays embedded in PS with exposed tips. (c) SiNW arrays are attached to a flexible substrate with a thin layer of silver epoxy on the surface. (d) SiNW arrays with both ends contacting Ag epoxy, and PS act as the insulating layer between the two electrodes. (e) SEM image of SiNW arrays embedded in PS without removing the outer SiO<sub>x</sub> layer at the tip of SiNWs. (f) SiNW arrays on a flexible transparent ITO-coated substrate with a thin layer of silver epoxy in between. The outer SiO<sub>x</sub> layer at the tip of SiNWs is removed with diluted HF. Inset is the tilt and zoom in view. (g) SiNW arrays with both ends contacting Ag epoxy. (h) The current-voltage (I-V) curves of the final device with (red curve) and without SiO<sub>x</sub> tip (black curve). Inset is the optical image of the final device.

curve of the final flexible device was measured and shown in Figure 4h. The linear I-V characteristics (the inner single crystalline SiNWs, the charge transport path, are still in high quality) with an average electrical resistivity value ~ 10  $\Omega$ ·cm (the electrical resistivity of Si wafer in this work is 1–10  $\Omega$ ·cm) demonstrate that our device forms good quality Ohmic contact on both ends of the nanowire arrays, which is important for its further application as flexible functional electronic devices. The linear I-V characteristics for single crystalline SiNWs have been observed by other researchers as well, however, for porous SiNWs, a typical nonlinear I-V characteristic was reported<sup>33,34</sup>.

#### Discussion

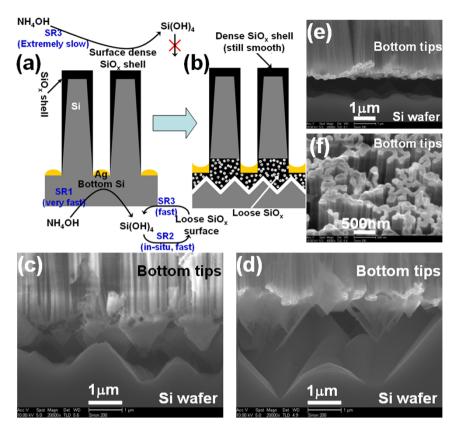

From the experimental observations, we can conclude that the steamed samples were rapidly attacked at the bottom portion of SiNWs. Through detailed investigation, we find that the key step in the automatic release of SiNW arrays is the water steaming process, which converts the surface of SiNWs into a dense layer of SiO<sub>x</sub> (Supplementary Reactions SR1-3)35 with a gradient distribution in thickness (Figure 5a), usually thicker at the top because of the higher oxygen concentration during the steaming process (the thickness of the  $SiO_x$  outerwall layer is about 25 nm at the top and 5 nm at the very bottom (SiNWs of 10 µm in length)). It is well-known that ammonia can etch both Si and SiOx, and generally the former is much faster than the latter (Supplementary Reactions SR4-6)<sup>36-41</sup>. Under the protection of the dense SiO<sub>x</sub> layer formed by the steaming process, the etching of SiNWs by ammonia was rather slow because ammonia could not diffuse readily through the dense SiO<sub>x</sub> layer. However, at the bottom portion of SiNWs, SiO<sub>x</sub> layer is thin enough and the etching of SiNWs could initiate after a certain time (Figure 2b), therefore, although the bottom portion of SiNWs have already been completely converted into SiO<sub>x</sub> and the oxide layer expands upward gradually, the remaining part of SiNWs do not vary much (see Figure 3h top, upper and lower, and Figure 6a and b). It is noteworthy that SiO<sub>x</sub> produced by ammonia oxidation is loose or somewhat porous in structure (compare Figure 5c and e), which is the reason that without the steaming step SiNWs were rapidly oxidized to  $SiO_x$  in the ammonia solution (Supplementary Fig. S2g-i). The gas generated in the ammonia oxidation step might be one possible reason for the loose/porous structure of SiOx layer (Supplementary Reactions SR4-6). Therefore, we can conclude that SiO<sub>x</sub> layer produced with steaming can protect Si from being etched

by ammonia, whereas the layer produced by ammonia oxidation cannot (compare Supplementary Fig. S2g–i to Figure 2b–d). As the etching by ammonia continues, SiNWs eventually auto-released from the mother wafer because of the internal stress developed during the oxidation and possibly facilitated by the rearrangement of Ag particles at the root of the nanowires (Figure 6b and c). It is interesting to note that after releasing, the upper and the lower surfaces were shaped in matching pyramid and anti-pyramid structures, respectively (Figure 6b, c, and d), probably because of the anisotropic etching behaviour of Si single crystals<sup>39–43</sup>.

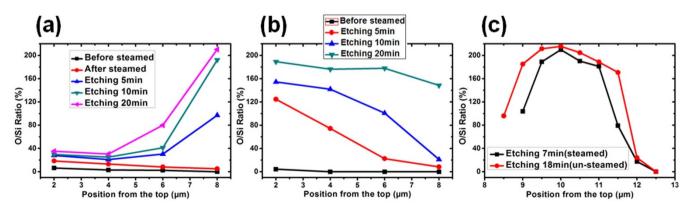

Here we emphasize that in our process, Si at the very bottom root of SiNW was oxidized (Supplementary Reaction SR4) even more quickly in the presence of the Ag metal mesh films. In this process, Ag plays the role of a catalyst as in the formation process of SiNW in HF/H<sub>2</sub>O<sub>2</sub> etching solution. And accompanying the oxidation of Si at the bottom portion of SiNW arrays, Ag nanoparticles on the bottom portion surface of SiNWs moved toward the root of the SiNWs by a dissolution-regeneration process<sup>30,32</sup>, and finally formed a new film at the bottom of SiNW arrays (Figure 6e and f). This Ag film somewhat enhanced the connection between SiNWs, and played an important role in the neatly releasing of SiNW arrays with a high integrity. SiNW arrays were rather difficult to detach from the mother substrate if there was no Ag film at the bottom of the nanowires, where even after the top of the nanowires being oxidized (Supplementary Fig. S3a and b) or dissolved (Supplementary Fig. S3c and d), the roots were still connected to the substrate. To further confirm the catalytic effect of Ag in Supplementary Reaction SR4, we also analyzed the vertical distribution of O/Si ratio along the nanowires from samples with different etching times via EDS (Figure 7), where all the Figures, especially Figure 7c, reveal that Ag possesses a powerful capability in promoting the oxidization of Si (Supplementary Reaction SR4). In a word, the different protective effects of dense/loose SiOx that strongly suppressed/weakly suppressed the etching of the bulk of SiNWs and the fast Ag-catalyzed oxidization of Si at the root of SiNWs as well as the rearrangement of Ag particles that generated high stress at the interface between Si wafer and the bottom of SiNW arrays resulted in the automatic release of SiNW arrays from Si wafer.

In order to gain deeper insights into the understanding of the effect of ammonia as the etchant to achieve an automatic release of SiNW arrays from Si wafers, we examined stronger alkaline chemicals in etching Si. We used 0.15 M potassium hydroxide to make a comparison. The results (Supplementary Fig. S4) are very different from

**Figure 5** | TEM image of (a) a steamed SiNW with protecting SiO<sub>x</sub> layer and its (b) cross-line element spectrum analysis and (c)zoom-in view of the tip of the nanowire in (a), showing the very dense SiO<sub>x</sub> layer formed by the steaming step. (d) TEM image of the root of ammonia etched SiNW arrays and (e) zoom-in view of the nanowires in (d), showing the very loose structure of SiO<sub>x</sub> root formed by the ammonia oxidation step.

Figure 6 | The whole process of the automatic release of SiNW arrays from the mother wafer. (a) Schematic illustrations of the different parts of SiNWs ammonia etching, (b) SiNWs just automatic releasing after a short time ammonia etching. At the root of SiNW arrays, the upper pyramid and the lower anti-pyramid surfaces (c) just departing from each other because of the stress between Si and SiO<sub>x</sub> and (d) after partial dissolution by ammonia etching. (e) As the upper SiO<sub>x</sub> pyramid being completely dissolved, the Ag film at the root of SiNWs forms a new metal mesh film. Image (f) is the tilt view of the root tips in (e).

those of using ammonia. Instead of detaching from the mother wafer as a whole array, SiNWs released separately, depending on the diameter of the nanowires as the reactions continued, similar to the observations by Khang and coworkers<sup>29</sup> (Supplementary Fig. S4d and e). From Supplementary Fig. S4g, we can clearly see that the root of SiNWs were directly etched away (through Supplementary Reaction SR7)<sup>38,42,44</sup> instead of being oxidized into SiO<sub>x</sub>, thus the root of SiNWs thinned with the etching time. SiNWs with smaller diameters automatically released from Si wafer, with thicker SiNWs releasing later and the SiNW arrays were etched randomly and the integrity of the arrays was destroyed (Supplementary Fig. S4d and e). At the same time, the Si underneath the protective layer exposed to KOH solution due to the complete dissolution of SiO<sub>x</sub> (through Supplementary Reactions SR8)<sup>36</sup>, and then the whole SiNW surface began to dissolve away (Supplementary Fig. S4i) and even more seriously over time (Supplementary Fig. S4b, e, and h). When the concentration of KOH was reduced to 0.075 M, similar etching results were observed. One may argue that SiO<sub>x</sub> also formed because of the etching by KOH, similar to ammonia case, and SiO<sub>x</sub> layer was rapidly dissolve away by the stronger alkaline KOH solution. However, in a control experiment, we put the released SiNW arrays with SiO<sub>x</sub> on the root (obtained by ammonia etching for 9 min) in

Figure 7 | The analysis of the O/Si ratio distribution along the nanowires with different ammonia etching time via EDS. (a) In SiNW arrays, the O/Si ratio along the nanowires with different etching time (etching 0, 5, 10, and 20 min) increases from the top to the bottom. (b) In SiOxNW arrays, the O/Si ratio along the nanowires with different etching time (etching 0, 5, 10, and 20 min) decreases from the top to the bottom. (c) The O/Si ratio close to the junction between the nanowires and Si wafer, showing the fast oxidation at the junction and the oxidation of Si wafer.

0.15 M KOH solution, and found that the dissolution of SiO<sub>x</sub> at the root was rather slow, which indicated that the random detachment of SiNWs by KOH etching was not caused by quick etching of SiO<sub>x</sub> by KOH (Supplementary Fig. S5). Room temperature etching of the steamed SiNW by KOH was also found to be unable to release SiNW array as a whole (Supplementary Fig. S6). In another control experiment, we examined the etching behaviour by a less alkaline K<sub>2</sub>CO<sub>3</sub> solution (0.15 M), and the results were similar to those observed for KOH etching (Supplementary Fig. S7). These observations may indicate that ammonia solution is especially suitable to release SiNW arrays with a high integrity, because of the formation of loose SiO<sub>x</sub> section at the root of the nanowire arrays that makes the detachment of the nanowires as an entity. Last but not least, we found that under optimized experimental conditions (coordinated combination of SiNW length, steaming time, and ammonia etching time), auto-releasing SiNW with good length control and high integrity could be achieved (Supplementary Fig. S8). It is noted however, if the length of SiNW changed, the steaming time and the ammonia etching time should also be varied accordingly, or otherwise autorelease will be unsuccessful (Supplementary Fig. S9). Systematic investigation is underway.

In summary, a method for automatic release of SiNW arrays with an unprecedented integrity was demonstrated via Ag-assisted ammonia etching. The key factors for the success of this method were a protecting  $SiO_x$  layer on the nanowire sidewall formed by a steaming step and the fast Ag-assisted oxidization of Si at the root of the nanowires in the presence of ammonia solution. SiNW arrays could be transferred to flexible substrates, and functional electronic devices could be fabricated with ease. We believe that our method is viable in promoting the flexible SiNW electronic devices for realworld applications.

#### Methods

Materials and chemicals. Si wafers were of single crystalline n-type (100) ( $\rho = 1-10 \ \Omega \cdot cm$ ) (Jingyifang Electronics Co.). AgNO<sub>3</sub> (AR reagent, 99.8+ wt %), HF (GR reagent, 40 wt %), NH<sub>4</sub>OH (AR reagent, 25–28 wt %), H<sub>2</sub>SO<sub>4</sub> (AR reagent, 98 wt %), H<sub>2</sub>O<sub>2</sub> (AR reagent, 30 wt %), ethanol (AR reagent, 99.7+ wt %), acetone (AR reagent, 99.5+ wt %), and N-hexane (AR reagent, 97+ wt %) were used as received (Sinopharm Chemical Reagent Co., Ltd). Styrene (99.5+ wt %, Aladdin) and PDMS (Elrt 601, Wacker-Chemie) were also used without further treatment.

Preparation of clean silicon substrates and fabrication of SiNW arrays. Si

substrates were cut into small squares (about 1 cm<sup>2</sup>). To create a hydrophilic surface, the wafers were ultrasonically cleaned in ethanol, acetone, and deionized water for 20 min each and then in piranha solution (3:1, v/v, 98% H<sub>2</sub>SO<sub>4</sub>/30% H<sub>2</sub>O<sub>2</sub>) for 8 h at room temperature. The Ag metal mesh film was then deposited on the pre-cleaned Si (100) wafer by immersing the substrate in a solution of 4.6 M HF and 5 mM AgNO<sub>3</sub> for 2 minutes. Ag metal mesh with randomly shaped nanopores (80–700 nm in width, 100–1000 nm in length) was obtained. Subsequently, SiNW arrays with varied thickness were obtained by immersing Ag-coated Si wafers in the etching solution of 4.6 M HF/0.4 M H<sub>2</sub>O<sub>2</sub> for several minutes at room temperature. The average diameter and height of SiNW we obtained are: 200 nm and and 10  $\mu$ m (etched for 30 min).

Automatic release of SiNW arrays. The wafers with desired SiNW length were put in a dry container and steamed in a 70 °C water bath for 48 h to produce a protective SiO<sub>x</sub> layer on the outer wall of SiNWs. Subsequently, the wafers were immersed in the etching solution of 0.2 M ammonia (NH<sub>4</sub>OH) for several minutes in a 70 °C water bath. Then, the nanowires could automatically release from Si wafers.

Vertical transferring of the auto-released SiNW arrays. A certain volume of n-hexane diluted PDMS liquid (3:1, v/v, n-hexane/PDMS) was spin-coated on the SiNW arrays. After partial volatilization of n-hexane, the samples were put on a hot plate at 100 °C to accelerate the solidification of PDMS. Then the PDMS-embedded SiNW arrays can be readily peeled off with a high integrity and transferred to arbitrary substrates.

**Preparation of flexible SiNW array electronic devices.** A certain amount of styrene was spin-coated on the as prepared SiNW arrays. After a period of polymerization, the polystyrene (PS) film was cured on a hot plate at 150 °C. This curing step made PS smoother and formed a better contact to SiNWs. PS film not only rendered good mechanical support to SiNW arrays, but also electrically insulated metal electrodes at the two ends of SiNW arrays in a subsequent step in depositing the electrical contacts to SiNW arrays. The wafer was then dry-etched by using Ar plasma etching at an

**Characterization**. The scanning electron microscope images of SiNW arrays, and the O/Si ratio distribution were characterized by using a Sirion 200 field emission scanning electron microscope. The transmission electron microscopy images and the elemental mapping were obtained by using a JEM-2010 high resolution transmission electron microscopy. The optical spectra of the flexible SiNW arrays were measured by using a SolidSpec3700DUV UV-vis spectrophotometer. And the current-voltage (I-V) curves of the final device were measured by using a Keithley 2440(5A) SourceMeter.

- Garnett, E. & Yang, P. D. Light trapping in silicon nanowire solar cells. *Nano Lett.* 10, 1082–1087 (2010).

- Kelzenberg, M. D. et al. Enhanced absorption and carrier collection in Si wire arrays for photovoltaic applications. Nat. Mater. 9, 239–244 (2010).

- Kim, D. R., Lee, C. H., Rao, P. M., Cho, I. S. & Zheng, X. Hybrid Si Microwire and planar solar cells: passivation and characterization. *Nano Lett.* 11, 2704–2708 (2011).

- Kim, D. R. & Zheng, X. L. Numerical characterization and optimization of the microfluidics for nanowire biosensors. *Nano Lett.* 8, 3233–3237 (2008).

- Patolsky, F., Zheng, G. F. & Lieber, C. M. Nanowire-based biosensors. Anal. Chem. 78, 4260–4269 (2006).

- Li, Z. et al. Sequence-specific label-free DNA sensors based on silicon nanowires. Nano Lett. 4, 245–247 (2004).

- Zheng, G. F., Patolsky, F., Cui, Y., Wang, W. U. & Lieber, C. M. Multiplexed electrical detection of cancer markers with nanowire sensor arrays. *Nat. Biotechnol.* 23, 1294–1301 (2005).

- Abramson, A. R. *et al.* Fabrication and characterization of a nanowire/polymerbased nanocomposite for a prototype thermoelectric device. *J. Microelectromech. Syst.* 13, 505–513 (2004).

- Hochbaum, A. I. et al. Enhanced thermoelectric performance of rough silicon nanowires. Nature 451, 163–167 (2008).

- Boukai, A. I. *et al.* Silicon nanowires as efficient thermoelectric materials. *Nature* 451, 168–171 (2008).

- Goldberger, J., Hochbaum, A. I., Fan, R. & Yang, P. D. Silicon vertically integrated nanowire field effect transistors. *Nano Lett.* 6, 973–977 (2006).

- Schmidt, V. *et al.* Realization of a silicon nanowire vertical surround-gate fieldeffect transistor. *Small* 2, 85–88 (2006).

- Lugstein, A., Steinmair, M., Henkel, C. & Bertagnolli, E. Scalable approach for vertical device integration of epitaxial nanowires. *Nano Lett.* 9, 1830–1834 (2009).

- Chan, C. K. et al. High-performance lithium battery anodes using silicon nanowires. Nat. Nanotechnol. 3, 31–35 (2008).

- Vlad, A. *et al.* Roll up nanowire battery from silicon chips. *Proc. Natl. Acad. Sci.* U.S.A. **109**, 15168–15173 (2012).

- 16. Kumar, V. Nanosilicon (Elsevier, New York, 2008).

- Wagner, R. S. & Ellis, W. C. Vapor-liquid-solid mechanism of single crystal growth (new method growth catalysis from impurity whisker epitaxial + large crystals Si e). *Appl. Phys. Lett.* 4, 89–90 (1964).

- Morton, K. J., Nieberg, G., Bai, S. & Chou, S. Y. Wafer-scale patterning of sub-40 nm diameter and high aspect ratio (>50:1) silicon pillar arrays by nanoimprint and etching. *Nanotechnology* 19, 345301 (2008).

- Juhasz, R., Elfstrom, N. & Linnros, J. Controlled fabrication of silicon nanowires by electron beam lithography and electrochemical size reduction. *Nano Lett.* 5, 275–280 (2005).

- Choi, Y. K., Zhu, J., Grunes, J., Bokor, J. & Somorjai, G. A. Fabrication of sub-10nm silicon nanowire arrays by size reduction lithography. *J. Phys. Chem. B* 107, 3340–3343 (2003).

- Huang, Z. P., Geyer, N., Werner, P., de Boor, J. & Goesele, U. Metal-assisted chemical etching of silicon: a review. *Adv. Mater.* 23, 285–308 (2011).

- Peng, K. Q., Yan, Y. J., Gao, S. P. & Zhu, J. Synthesis of large-area silicon nanowire arrays via self-assembling nanoelectrochemistry. *Adv. Mater.* 14, 1164–1167 (2002).

- Xu, W., Palshin, V. & Flake, J. C. Nickel monosilicide contact formation in electrolessly etched silicon nanowires deposited onto nickel electrodes. *J. Electrochem. Soc.* 156, H544–H547 (2009).

- Lee, T. I. et al. Programmable direct-printing nanowire electronic components. Nano Lett. 10, 1016–1021 (2010).

- Yuan, G. D. et al. Tunable electrical properties of silicon nanowires via surfaceambient chemistry. ACS Nano 4, 3045–3052 (2010).

- 26. Choi, J. H. *et al.* Intrinsic memory behavior of rough silicon nanowires and enhancement via facile Ag NPs decoration. *J. Mater. Chem.* **21**, 13256–13261 (2011).

- Pevzner, A. *et al.* Knocking down highly-ordered large-scale nanowire arrays. Nano Lett. 10, 1202–1208 (2010).

- Shiu, S. C., Hung, S. C., Chao, J. J. & Lin, C. F. Massive transfer of vertically aligned Si nanowire array onto alien substrates and their characteristics. *Appl. Surf. Sci.* 255, 8566–8570 (2009).

- Yoon, S. S. & Khang, D. Y. Facile and clean release of vertical Si nanowires by wet chemical etching based on alkali hydroxides. *Small* 9, 905–912 (2013).

- Weisse, J. M., Kim, D. R., Lee, C. H. & Zheng, X. L. Vertical transfer of uniform silicon nanowire arrays via crack formation. *Nano Lett.* 11, 1300–1305 (2011).

- 31. Weisse, J. M., Lee, C. H., Kim, D. R. & Zheng, X. L. Fabrication of flexible and vertical silicon nanowire electronics. *Nano Lett.* **12**, 3339–3343 (2012).

- 32. Wu, L., He, W. W., Teng, D. Y., Ji, S. L. & Ye, C. H. A new route to fabricate largearea, compact Ag metal mesh films with ordered pores. *Langmuir* 28, 7476–7483 (2012).

- Benchorin, M., Moller, F. & Koch, F. Nonlinear electrical transport in porous silicon. *Phys. Rev. B* 49, 2981–2984 (1994).

- Remaki, B., Populaire, C., Lysenko, V. & Barbier, D. Electrical barrier properties of meso-porous silicon. *Mater. Sci. Eng. B* 101, 313–317 (2003).

- Vanderzwan, M., Bardwell, J., Sproule, G. & Graham, M. Mechanism of the growth of native oxide on hydrogen passivated silicon surfaces. *Appl. Phys. Lett.* 64, 446–447 (1994).

- Seidel, H., Csepregi, L., Heuberger, A. & Baumgartel, H. Anisotropic etching of crystalline silicon in alkaline-solutions. 1. Orientation dependence and behavior of passivation layers. J. Electrochem. Soc. 137, 3612–3626 (1990).

- Seidel, H., Csepregi, L., Heuberger, A. & Baumgartel, H. Anisotropic etching of crystalline silicon in alkaline-solutions. 2. Influence of dopants. J. Electrochem. Soc. 137, 3626–3632 (1990).

- Wu, X. P., Wu, Q. H. & Ko, W. H. in Digest of Technical Papers of The Third International Conference on Solid-State Sensors and Actuators, p. 291 (Philadelphia, PA, 1985).

- 39. Tabata, O., Asahi, R., Funabashi, H., Shimaoka, K. & Sugiyama, S. Anisotropic etching of silicon in tmah solutions. *Sens. Actua. A* 34, 51–57 (1992).

- Schnakenberg, U., Benecke, W. & Lochel, B. NH<sub>4</sub>OH-based etchants for silicon micromachining. *Sens. Actuat. A* 23, 1031–1035 (1990).

- Gould, G. & Irene, E. A. An in situ ellipsometric study of aqueous NH<sub>4</sub>OH treatment of silicon. J. Electrochem. Soc. 136, 375–390 (1989).

- Finne, R. M. & Klein, D. L. A water-amine-complexing agent system for etching silicon. J. Electrochem. Soc. 114, 965–970 (1967).

- Chaturvedi, N., Hsiao, E., Velegol, D. & Kim, S. H. Maskless fabrication of nanowells using chemically reactive colloids. *Nano Lett.* 11, 672–676 (2011).

- 44. Tanaka, H., Cheng, D., Shikida, M. & Sato, K. Characterization of anisotropic wet etching properties of single crystal silicon: effects of ppb-level of Cu and Pb in KOH solution. *Sens. Actuat. A* **128**, 125–131 (2006).

#### Acknowledgments

This work was supported by National Basic Research Program of China (973 Program, Grant No. 2011CB302103), National Natural Science Foundation of China (Grant Nos. 11074255 and 11274308), and the Hundred Talents Program of the Chinese Academy of Sciences.

#### Author contributions

L.W. and C.Y. contributed to the conception and design of the experiment, analysis of the data and writing the manuscript. S.L., W.H., D.T. and K.W. assisted L.W. by carrying out synthesis of materials, optical, electrical and structural characterizations of the synthesized products.

#### **Additional information**

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Wu, L. *et al*. Automatic Release of Silicon Nanowire Arrays with a High Integrity for Flexible Electronic Devices. *Sci. Rep.* **4**, 3940; DOI:10.1038/srep03940 (2014).

This work is licensed under a Creative Commons Attribution-

Visit http://creativecommons.org/licenses/by-nc-nd/3.0