Abstract

Magnetoresistance (MR) effects are at the heart of modern information technology. However, future progress of giant and tunnelling MR based storage and logic devices is limited by the usable MR ratios of currently about 200% at room-temperature. Colossal MR structures, on the other hand, achieve their high MR ratios of up to 106% only at low temperatures and high magnetic fields. We introduce the extraordinary Hall balance (EHB) and demonstrate room-temperature MR ratios in excess of 31,000%. The new device concept exploits the extraordinary Hall effect in two separated ferromagnetic layers with perpendicular anisotropy in which the Hall voltages can be configured to be carefully balanced or tipped out of balance. Reprogrammable logic and memory is realised using a single EHB element. PACS numbers: 85.75.Nn,85.70.Kh,72.15.Gd,75.60.Ej.

Similar content being viewed by others

Introduction

The extraordinary (or anomalous) Hall effect (EHE) occurs in ferromagnetic materials and describes a Hall voltage perpendicular to the applied current which reverses sign when the magnetisation is reversed, originating from the spin-orbit interaction1. It can be decomposed into an intrinsic term, which can be expressed in terms of Berry-phase curvature which is associated with the crystal potential and an extrinsic term, which relates to skew-scattering from impurities and disorder, dominating for highly-conductive ferromagnets2. The planar or pseudo Hall effect3, which is proportional to the in-plane magnetisation component, is negligible for a system with a strong perpendicular magnetic anisotropy in saturation. The Hall voltage, which is proportional to the magnetisation, is a useful tool for studying magnetic properties of thin films. The potential of the EHE for sensor, memory and magnetic logic applications has only recently been discussed4. In general, EHE-based devices can be widely used in the form of magnetic multilayer structures, similar to giant magnetoresistance (GMR), tunnel magnetoresistance (TMR) and spin-valve devices.

Despite the fact that EHE-based Hall sensors outperform semiconductor-based magnetic field sensors5, EHE-based devices have not been used to their full potential and magnetic devices are still dominated by magnetoresistance (MR) elements6. For instance, disk drives using sensors based on the GMR effect and the TMR effect in magnetic tunnel junctions (MTJs), are extremely successful7,8. Non-volatile magnetoresistive random-access memory (MRAM) is still a niche application due to practical issues such as scaling, compared to the established solutions. Nevertheless, due to its overwhelming advantages, the perspective of MRAM – or a similar concept – is to eventually become the fast, non-volatile and lowpower universal memory solution. Moreover, MRAM-based logic has been proposed9 which is non-volatile and reconfigurable. A general problem of GMR- and TMR-based elements is their relatively low MR ratio, i.e., the ratio between the resistances in the parallel (P) and antiparallel (AP) states of the device, (RAP – RP)/RP. Typical values10 of a couple of 100% are still very low when compared with the on/off-current ratios of complementary metal oxide semiconductor (CMOS) transistors which exceed 105. Consequently, CMOS transistors are an integral part of MRAM devices both for read-out and addressing of the memory cells.

Here, we demonstrate an EHE-based device concept – the extraordinary Hall balance (EHB) – which provides a broad platform for spintronic applications, due to the EHB's logic capabilities and extremely large experimental MR ratio of 31,400%. Both memory and logic elements are demonstrated and device applications are discussed.

Results

Device concept

In ferromagnetic materials, the Hall effect is dominated by two contributions: the normal Hall resistance originating from the Lorentz force on the carriers, which is proportional to the applied magnetic field and the ‘extraordinary’ Hall resistance which is linearly proportional to the magnetisation1. As the magnetisation saturates at higher fields, the EHE term saturates as well and the resistance is dominated by the normal contribution to the Hall effect.

We consider a layer stack with two ferromagnetic layers, separated by a non-ferromagnetic insulator, in which the overall Hall effect in a Hall cross structure (cf. Fig. 1a) is determined by the Hall resistivities of the two layers. As shown in Fig. 1b, the layer stack is contacted from the sides by a common contact, making the layers electrically parallel. Choosing the magnetic properties to be different leads to different hall resistivities. Thus four different magnetic (and resistive) states can be prepared (cf. Fig. 1f):  ,

,  ,

,  and

and  . Illustrations of the different states are shown in Fig. 1c–e: a large positive Hall voltage is measured when both layers are in the

. Illustrations of the different states are shown in Fig. 1c–e: a large positive Hall voltage is measured when both layers are in the configuration, a small positive and negative voltage is measured for

configuration, a small positive and negative voltage is measured for and

and  , respectively, while a large negative Hall voltage is measured for

, respectively, while a large negative Hall voltage is measured for  . This behaviour resembles that of a balance that can be tipped either way by rearranging the ‘weights’. Ideally, if the EHE generated in the two ferromagnetic layers is identical, the magnitude of the two high voltage states is twice the Hall voltage of each layer (

. This behaviour resembles that of a balance that can be tipped either way by rearranging the ‘weights’. Ideally, if the EHE generated in the two ferromagnetic layers is identical, the magnitude of the two high voltage states is twice the Hall voltage of each layer ( ‘on’ state) and the voltage Vlow is exactly cancelling out (

‘on’ state) and the voltage Vlow is exactly cancelling out ( ‘off’ state). Thus, in principle, an infinite on/off voltage ratio can be realised. Moreover, all three – or in case of asymmetric ferromagnetic layers all four – states can be used for complex logic functions.

‘off’ state). Thus, in principle, an infinite on/off voltage ratio can be realised. Moreover, all three – or in case of asymmetric ferromagnetic layers all four – states can be used for complex logic functions.

Basic design of the EHB device.

(a) At the core of the EHB is a Hall cross with electrical side contacts. The Hall voltage is measured, as usual, across the structure by applying a perpendicular magnetic field and forcing the current along the structure. All experiments are done at room-temperature. For simplicity, the prototype device structure was fabricated on the micrometre scale (l1 = 60 μm, w1 = 20 μm, l2 = 30 μm and w2 = 10 μm). (b) The EHB consists of a stack of at least two magnetic layers with perpendicular anisotropy, which are separated by an insulating layer. For our experiments, both FM stacks are made up of [Co/Pt] multilayers, wherein the bottom stack is in intimate contact with an antiferromagnetic NiO layer which increases its coercivity. The electrical side contacts bridge across the entire layer stack, as in the conventional current-in-plane geometry. (c) to (e) illustrate the function of the extraordinary Hall balance: depending on the magnetisation direction in the FM layer, electrons of a particular spin orientation are preferably scattered to the left- or the right-hand side. If both FM layers are magnetised in the same (upward or downward) direction, the spin-dependent scattering mechanism gives rise to a large (positive or negative) Hall voltage. If the layers are oppositely magnetised, there is a balance between the scattered carriers in the two layers and a low (or zero) Hall resistance is measured. (f) shows the Hall resistance as a function of applied field for identical FM layers. Four distinct states, corresponding to the four magnetisation configurations of the layers, can be observed.

Device structure

A (Co/Pt)3 multilayer stack (denoted as [Co/Pt]) is selected as the bottom and top ferromagnetic layer due to its perpendicular anisotropy and strong spin-orbit coupling that results in a large EHE11. In order to make the hysteretic properties of the two layers different and in order to be able to engineer the behaviour of the device, an antiferromagnetic (AFM) NiO layer is combined with the bottom [Co/Pt] layer. Depending on the thickness of the AFM NiO, the hysteresis of the system can be shifted either through the exchange biasing effect, or the coercive field can be enhanced in case of a symmetric hysteresis loop. The multilayer samples were grown by magnetron sputtering and subsequently processed into device structures (see Methods section and Fig. 1a).

In all of the presented measurements, the (transverse) Hall voltage VH was measured as a result of an applied longitudinal current of I = 1 mA at room-temperature, giving a Hall resistance according to RH = VH/I. The magnetic field of typically up to ± 300 Oe is applied perpendicular to the film plane. The Hall resistance ratio (HRR) is defined analogous to the MR ratio in GMR elements by:

where  and

and  are the Hall resistances of the parallel and antiparallel state, respectively. For the presented devices with dimensions on the μm scale, output voltages are on the order of mV for input current densities on the order of 106 A/cm2. It has to be noted that the effective fields resulting from this current density are too low to switch the magnetisation via the Rashba effect12,13. Using the experimentally determined value of 1 T/108 A cm−2 for a Co/Pt system in contact with AlOx12, a transverse (in-plane) field of ~ 100 Oe can be expected, which is not large enough to affect the perpendicular magentisation.

are the Hall resistances of the parallel and antiparallel state, respectively. For the presented devices with dimensions on the μm scale, output voltages are on the order of mV for input current densities on the order of 106 A/cm2. It has to be noted that the effective fields resulting from this current density are too low to switch the magnetisation via the Rashba effect12,13. Using the experimentally determined value of 1 T/108 A cm−2 for a Co/Pt system in contact with AlOx12, a transverse (in-plane) field of ~ 100 Oe can be expected, which is not large enough to affect the perpendicular magentisation.

Figure 1f shows the Hall resistance (RH) as a function of applied magnetic field for a NiO(20)/[Co(0.4)/Pt(1.2)]/MgO(8)/[Co(0.4)/Pt(1.2)]/NiO(1) (layer thickness in nm) structure. The contributions of the two ferromagnetic layers, with their different coercivities, are easy to identify: the narrower loop reflects the stronger anisotropy of the top layer, while the wider loop is indicative of the effect of the NiO on the bottom layer. Note that  is not exactly vanishing, even with the two ferromagnetic layers having an identical internal multilayer structure. The reason for this behaviour lies in the fact that the interfaces of the two layers are different and that (extrinsic) interface scattering affects the EHE as well2,11. The resulting four RH states are +650 mΩ (

is not exactly vanishing, even with the two ferromagnetic layers having an identical internal multilayer structure. The reason for this behaviour lies in the fact that the interfaces of the two layers are different and that (extrinsic) interface scattering affects the EHE as well2,11. The resulting four RH states are +650 mΩ ( configuration), +70 mΩ (

configuration), +70 mΩ ( ), −70 mΩ (

), −70 mΩ ( ) and −650 mΩ (

) and −650 mΩ ( ). The HRR reaches about 830%, which is higher than the highest reported room-temperature MR in MTJs (604%)10. Compared to MTJs which can only distinguish between parallel and antiparallel magnetisation configurations, the EHB can resolve four states, enabling logic operations (see section ‘Universal logic’) and multivalued logic14. It should be noted that the number of states can be in fact increased further to 2N, where N is the number of ferromagnetic layers.

). The HRR reaches about 830%, which is higher than the highest reported room-temperature MR in MTJs (604%)10. Compared to MTJs which can only distinguish between parallel and antiparallel magnetisation configurations, the EHB can resolve four states, enabling logic operations (see section ‘Universal logic’) and multivalued logic14. It should be noted that the number of states can be in fact increased further to 2N, where N is the number of ferromagnetic layers.

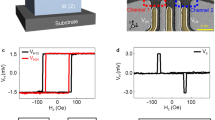

Magnetic storage

Memory devices require non-volatility, low switching power, simple read-out capability, as well as thermal and long-term stability. Thus, in order to transform the EHB introduced in Fig. 1f into a non-volatile storage element, one of the layers has to be easily switchable and the low resistance value should vanish. These goals are achieved by exploiting the exchange biasing effect and carefully engineering the multilayer structure (see supplemental information). Figure 2a shows an EHB storage element in which the binary information is encoded by the magnetisation orientation of the top ferromagnetic layer (↑ or ↓). The switching field required to reverse the magnetisation is 30 Oe. The Hall resistance is 630 mΩ (↑) in the high-resistance state and 2 mΩ (↓) in the low-resistance state, resulting in a HRR of 31,400%. Consequently, the EHB should be able to overcome the major obstacle of MTJ-based device concepts, namely their low on/off ratios.

EHB memory concept.

(a) By tuning the physical parameters of the structure, the EHE in the two FM layers was designed to become identical – consequently cancelling the two contributions to the Hall voltage in antiparallel alignment (‘off’ state). The HRR for the structure shown in the inset is 31,400%. Using this structure as a single bit, one can envision three-dimensional magnetic memory networks as illustrated in (b). The binary information is encoded in the magnetisation of the top FM layer and can be switched by applying a field of ± 30 Oe [cf. (a)]. For read-out of the information stored in the cell, a current is driven along the ‘read line’ and the resulting Hall resistance switches between 3 and 621 mΩ. For writing information into the cell, three orthogonal Oersted fields (originating from the x, y and floor line wires) are simultaneously applied to switch the magnetisation. To simplify the circuitry, the x and y lines join into a ‘site line’ which carries the sum current and runs perpendicularly to the x and y lines. The choice of floor line finally determines the bit to be written.

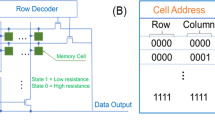

The current-in-plane configuration employed in the EHB, in conjunction with the layers' perpendicular anisotropy, allow for the integration into three-dimensional memory arrays. Figure 2b illustrates a three-dimensional, EHB-based MRAM concept. Each MRAM cell contains a single EHB that encodes one bit of information in the magnetisation of the ferromagnetic top layer, while keeping the bottom layer ‘pinned’. To read-out the bit, the transverse Hall voltage is measured by applying a current to the ‘read line’. Since the ultra-high HRR of the read-out signal is, in principle, not limited by intrinsic properties, the HRR can potentially come close to the on/off ratio of a (poorly performing) transistor. Consequently, the number of CMOS elements can be greatly reduced.

For illustrative purposes, logic input in the EHB cell is achieved using three orthogonal Oersted fields from three separate wires (‘x line’, ‘y line’ and ‘floor line’). The layer properties are tuned in such a way that the simultaneous application of all three fields is required to reverse the magnetisation of the top layer. Each EHB cell in space could be addressed in the following way: the location in the plane is selected by the ‘x line’ (red) and the ‘y line’ (blue), while both currents are drained through a ‘site line’ (yellow) selected by addressing a layer-specific ‘floor line’ (green). One of the shortcomings of first-generation MRAM technology was the large device footprint due to the infrastructure required to provide Oersted fields. More recently, space- and energy-saving writing concepts make use of the spin-transfer torque (STT) effect15, also in combination with perpendicular anisotropy layers16, current-induced domain wall motion17, direct electrical switching of the layer magnetisation18, optically-induced switching19 and thermal stimuli via the spin Seebeck effect20. In case of STT switching, the two layers can be independently addressed by introducing a third set layer with a larger magnetic anisotropy. Depending on the current direction, strength and sequence, all four input states can be prepared in the two layers. For the read-out of the memory cell, the measured Hall voltage is compared with reference values and logic states are assigned accordingly. STT-based EHB-MRAM has the potential to achieve high-density and low-complexity circuits with simplified fabrication requirements and at a lower cost compared to conventional MRAM technology.

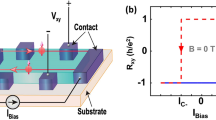

Universal logic

The concept of reprogrammable logic involves a physical system being able to switch between different logic operations9,21,22,23,24. The shortcoming of many proposed and currently realised reconfigurable logic devices is that the logic operation has to be preselected from a collection of basic Boolean operations prior to the actual computational step. The computing efficiency can be significantly improved if no ‘preset’ step is needed. By utilising the three states of an EHB, a single-element universal logic gate can be realised. The EHB gate does not require a preset step as the output is a ternary code that comprises all basic Boolean functions. The binary result that corresponds to a particular Boolean operation can be acquired by reading out the element in different ways. Consequently, this extrinsic universal logic gate offers faster computational speeds and lower power consumption.

To realise universal logic functionality another type of EHB was optimised and fabricated in which the two symmetric [Co/Pt] layers are antiferromagnetically coupled across a 1.1-nm-thick AFM NiO spacer layer22. The resulting Hall resistance shows only three states and the Hall loops are symmetric about zero field. (cf. Fig. 3). Two magnetic inputs, A and B, are used as shown in Fig. 3a, which can be realised as positive or negative currents (IA and IB) of equal magnitude. The field values are chosen in such a way that only both input fields together are able to reverse the magnetisation of the two ferromagnetic layers. The assignment of the magnetic fields to the logic states is as follows: +180 Oe (−180 Oe) along the perpendicular direction corresponds to logic 1 (0) for both A and B. Thus, the input state ‘0,0’ corresponds to the ( ) magnetisation state, resulting in a negative maximum RH; ‘1,0’ and ‘0,1’ correspond to zero net external field bringing the EHB back into its remanent state (RH ≈ 0), while ‘1,1’ (

) magnetisation state, resulting in a negative maximum RH; ‘1,0’ and ‘0,1’ correspond to zero net external field bringing the EHB back into its remanent state (RH ≈ 0), while ‘1,1’ ( ) shows a positive maximum RH. By defining the maximum (zero) Hall signal as 1 (0), the XNOR gate is realised (the truth table is shown in the inset of Fig. 3b).

) shows a positive maximum RH. By defining the maximum (zero) Hall signal as 1 (0), the XNOR gate is realised (the truth table is shown in the inset of Fig. 3b).

Universal logic gate.

(a) The two inputs A and B of the universal logic gate are encoded as perpendicular Oersted fields. The result of the logic operation can be instantly read-out via the sign of the Hall voltage. By introducing two additional control parameters, the signs of the longitudinal current I and the transverse bias voltage Vbias, the logic gate can be reconfigured ‘on the fly’. The core of the logic gate is a tri-state EHB, in which the relative position and direction of the hysteresis curve is determined by I and Vbias. In the unbiased case (+I), an XNOR gate is obtained (b). A positive bias (+I) gives the OR function (c), while a negative bias yields the AND function (d). Similarly, for a negative current, the NOR (e) and NAND (f) functions are obtained, respectively.

To achieve OR and AND gates a biased voltage (Vbias) is applied which offsets the entire Hall loop by the applied value. By defining the positive (negative) output RH as output 1 (0), as shown in Fig. 3c & d, OR and AND operation can be achieved. Analogously, in Fig. 3e & f, NOR and NAND gates can be built simply by reversing the longitudinal current I. Thus, all basic Boolean logic functions have been demonstrated using a single EHB – without the need to preselect the function prior to the computation. The EHB-based logic gate can significantly improve computing efficiency and reduce the complexity of logic circuits in the future.

Discussion

The Extraordinary Hall Balance presented in this work exploits the extraordinary Hall effect in a unique way to read out information encoded in the quaternary state of a magnetic layer stack. The core of the device is a Hall cross consisting of two ferromagnetic Co/Pt multilayers with perpendicular anisotropy, separated by an insulating MgO or NiO layer, making the fabrication much less challenging than a common MTJ structure. The bottom ferromagnetic layer is further pinned by an antiferromagnetic NiO layer of varying thickness to allow for precise engineering of the magnetic response. By matching/mismatching the Hall resistances of two ferromagnetic layers in parallel, ultrahigh resistance ratios in excess of 31,000% are achieved – which comes much closer to the on/off ratios of traditional semiconductor-based transistors. There is, however, no fundamental limit as to how high the MR defined in the usual way can be increased as this only depends on the ability to bring the compensated resistance down to zero. It is therefore possible to speculate about a single EHB element replacing the hybrid MTJ/CMOS circuitry needed for MRAM-based logic9. Using a NiO spacer layer, values as low as 2 mΩ have been reached. Other, fabrication-related issues that become increasingly important for scaled, submicron-sized devices manifest themselves in voltage offsets and thus non-zero resistances. Another source of offsets is local heating. In symmetric Hall-type geometries, greater immunity to offset effects can be achieved by averaging over the symmetric inputs or by grouping four cells together into a single memory element.

In the most general structure the Hall resistance can take four values representing the four combinations of layer magnetisations (see Fig. 1f). By varying the layer thicknesses, these four states can be reduced to three and the magnetisation curve can be further manipulated to show different coercive fields (see Fig. 2a) or, by applying an electric field, to exhibit a non-zero resistance of the two antiparallel magnetisation states. By choosing the range of operating magnetic fields between −50 Oe and +50 Oe, two magnetic states are obtained as can be seen in the minor loop in Fig. 2a. As a simple resistance measurement can distinguish between the magnetisation states of the EHB, a single element can directly realise Boolean operations, which are further reconfigurable ‘on the fly’ and serve as magnetic memory. This added flexibility leads to increased computing efficiency and, due to the non-volatility, low power consumption. Through device engineering, the same basic EHB structure can be used as non-volatile memory as well as universal logic and further applications such as full adders, sensors and multivalued logic devices, thus having the potential to greatly influence the area of spintronics. Again, by increasing the number, N, of ferromagnetic layers involved, 2N logic states can be addressed.

Methods

Preparation of the magnetic multilayer structure

The multilayers were deposited onto thermally oxidised Si wafers at room-temperature by magnetron sputtering. The sputterer was kept at a base pressure of 10−8 Torr. During sputtering, the partial pressure of Ar was typically 4 mTorr. The deposition rate of Co, Pt (DC sputtering), MgO and NiO (RF sputtering) was 0.071, 0.068, 0.005 and 0.034 nm/s, respectively. A perpendicular magnetic field of 200 Oe was applied to the substrate during sputtering to align the magnetic layers. The antiferromagnetic NiO layer exhibits a critical thickness tcrit between 30 and 35 nm, above which the magnetisation curve is shifted due to exchange biasing. Typical values of  were ≈ 130 Oe. Below tcrit, no exchange is observed, however, the coercive field is increased as compared to the unbiased system.

were ≈ 130 Oe. Below tcrit, no exchange is observed, however, the coercive field is increased as compared to the unbiased system.

Device fabrication

The cross-shaped EHB structure was patterned into the magnetic multilayer stack. Electric side contacts, which bridge the different metallic layers, were attached for current-in-plane transport measurements. Photolithography, in combination with reactive ion etching, was used to fabricate crossed rectangular parallelepipeds measuring 60 μm and 30 μm in length and 20 μm and 10 μm in width, respectively. Subsequently, a 100-nm-thick Cu layer was deposited and side contacts were fabricated in a second fabrication step (cf. Fig. 1e). Wires were bonded to the device structure and typical currents of 1 mA were applied. The transport measurements were performed at room-temperature using the four-point probe technique, while the magnetic field was swept between ± 1000 Oe.

References

Karplus, R. & Luttinger, J. M. Hall Effect in Ferromagnetics. Phys. Rev. 95, 1154–1160 (1954).

Nagaosa, N., Sinova, J., Onoda, S., MacDonald, A. H. & Ong, N. P. Anomalous Hall effect. Rev. Mod. Phys. 82, 1539–1592 (2010).

Pan, J. P. Galvanomagnetic and thermomagnetic effects in metals,. in Solid State Physics, Seitz F., & Turnbull D. eds. (Academic Press, New York, 1957), Vol. 5, p. 1–96.

Moritz, J., Rodmacq, B., Auffret, S. & Dieny, B. Extraordinary Hall effect in thin magnetic films and its potential for sensors, memories and magnetic logic applications. J. Phys. D: Appl. Phys. 41, 135001 (2008).

Gerber, A. & Riss, O. Perspective of Spintronics Applications Based on the Extraordinary Hall Effect. J. Nanoelectron. Optoe. 3, 35 (2008).

Sinova, J. & Žutić, I. New moves of the spintronics tango. Nature Mater. 11, 368–371 (2012).

Parkin, S. S. P. et al. Giant tunnelling magnetoresistance at room temperature with MgO (100) tunnel barriers. Nature Mater. 3, 862–867 (2004).

Yuasa, S., Nagahama, T., Fukushima, A., Suzuki, Y. & Ando, K. Giant room-temperature magnetoresistance in single-crystal Fe/MgO/Fe magnetic tunnel junctions. Nature Mater. 3, 868–871 (2004).

Ney, A., Pampuch, C., Koch, R. & Ploog, K. H. Programmable computing with a single magnetoresistive element. Nature 425, 485–487 (2003).

Ikeda, S. et al. Tunnel magnetoresistance of 604% at 300 K by suppression of Ta diffusion in CoFeB/MgO/CoFeB pseudo-spin-valves annealed at high temperature. Appl. Phys. Lett. 93, 082508 (2008).

Zhang, S. L. et al. Large enhancement of the anomalous Hall effect in Co/Pt multilayers sandwiched by MgO layers. Appl. Phys. Lett. 97, 222504 (2010).

Miron, I. M. et al. Current-driven spin torque induced by the Rashba effect in a ferromagnetic metal layer. Nature Mater. 9, 230234 (2010).

Kim, J. et al. Layer thickness dependence of the current-induced effective field vector in Ta—CoFeB—MgO. Nature Mater. 12, 240245 (2013).

Profeanu, I. A Ternary Arithmetic and Logic. Lecture Notes in Engineering and Computer Science 1, 193–196 (2010).

Ralph, D. C. & Stiles, M. D. Spin transfer torques. J. Magn. Magn. Mater. 320, 1190–1216 (2008).

Mangin, S. et al. Current-induced magnetization reversal in nanopillars with perpendicular anisotropy. Nature Mater. 5, 210–215 (2006).

Parkin, S. S. P., Hayashi, M. & Thomas, L. Magnetic domain-wall racetrack memory. Science 320, 190–194 (2008).

Fiebig, M. Revival of the magnetoelectric effect. J. Phys. D - Appl. Phys. 38, R123–R152 (2005).

Kimel, A. V. et al. Ultrafast non-thermal control of magnetization by instantaneous photomagnetic pulses. Nature 435, 655–657 (2005).

Uchida, K. et al. Observation of the spin Seebeck effect. Nature 455, 778–781 (2008).

Black, W. C. & Das, B. Programmable logic using giant-magnetoresistance and spindependent tunneling devices (invited). J. Appl. Phys. 87, 6674 (2000).

Liu, Z. Y. & Adenwalla, S. Oscillatory interlayer exchange coupling and its temperature dependence in [Pt/Co]3/NiO/[Co/Pt]3 multilayers with perpendicular anisotropy. Phys. Rev. Lett. 91, 037207 (2003).

Allwood, D. A. et al. Magnetic domain-wall logic. Science 309, 1688–1692 (2005).

Imre, A. et al. Majority Logic Gate for Magnetic Quantum-Dot Cellular Automata. Science 311, 205–208 (2006).

Acknowledgements

We thank Prof. W.Y. Lai for discussions, Prof. L.J. Wang for sharing his expertise in device measurements and Mr. A.A. Baker for critically reviewing the manuscript. This work was supported by the Semiconductor Research Corporation (SRC), the National Key Basic Research Program of China (Grant No. 2009CB929203), the National Natural Science Foundation of China (Grant No. 11274371) and the National Key Scientific Instrument & Equipment Development Project of China (Grant No. 2012YQ120048). LCM acknowledges partial support by the EPSRC (UK) and TH support by the University of Oxford's John Fell Fund.

Author information

Authors and Affiliations

Contributions

S.L.Z. conceived and designed the device structure. S.L.Z. and J.Y.Z. grew the magnetic thin films and carried out the device fabrication. S.L.Z., Y.L., T.H., J.Y.Z., S.G.W. and G.H.Y. analysed the data and developed the EHB concept. T.H., S.L.Z. and L.C.M. co-wrote the paper. All authors discussed the results and commented on the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Supplementary Information

Supplementary Information

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/

About this article

Cite this article

Zhang, S., Liu, Y., Collins-McIntyre, L. et al. Extraordinary hall balance. Sci Rep 3, 2087 (2013). https://doi.org/10.1038/srep02087

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep02087

This article is cited by

-

Multilevel information storage using magnetoelastic layer stacks

Scientific Reports (2019)

-

Encoding, training and retrieval in ferroelectric tunnel junctions

Scientific Reports (2016)

-

Topological computation based on direct magnetic logic communication

Scientific Reports (2015)

-

Three dimensional magnetic abacus memory

Scientific Reports (2014)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.