Abstract

In-memory computing architectures based on memristive crossbar arrays could offer higher computing efficiency than traditional hardware in deep learning applications. However, the core memory devices must be capable of performing high-speed and symmetric analogue programming with small variability. They should also be compatible with silicon technology and scalable to nanometre-sized footprints. Here we report an electrochemical synaptic transistor that operates by shuffling protons between a hydrogenated tungsten oxide channel and gate through a zirconium dioxide protonic electrolyte. These devices offer multistate and symmetric programming of channel conductance via gate-voltage pulse control and small cycle-to-cycle variation. They can be programmed at frequencies approaching the megahertz range and exhibit endurances of over 100 million read–write cycles. They are also compatible with complementary metal–oxide–semiconductor technology and can be scaled to lateral dimensions of 150 × 150 nm2. Through monolithic integration with silicon transistors, we show that pseudo-crossbar arrays can be created for area- and energy-efficient deep learning accelerator applications.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Anthony, L. F. W., Kanding, B. & Selvan, R. Carbontracker: tracking and predicting the carbon footprint of training deep learning models. Preprint at https://arxiv.org/abs/2007.03051 (2020).

Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

Haensch, W., Gokmen, T. & Puri, R. The next generation of deep learning hardware: analog computing. Proc. IEEE 107, 108–122 (2019).

Yu, S. Neuro-inspired computing with emerging nonvolatile memorys. Proc. IEEE 106, 260–285 (2018).

Xi, Y. et al. In-memory learning with analog resistive switching memory: a review and perspective. Proc. IEEE 109, 14–42 (2021).

Gokmen, T. & Vlasov, Y. Acceleration of deep neural network training with resistive cross-point devices: design considerations. Front. Neurosci. 10, 333 (2016).

Ambrogio, S. et al. Equivalent-accuracy accelerated neural-network training using analogue memory. Nature 558, 60–67 (2018).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64 (2015).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Dutta, S. et al. Monolithic 3D integration of high endurance multi-bit ferroelectric FET for accelerating compute-in-memory. In 2020 IEEE International Electron Devices Meeting (IEDM) 36.4.1–36.4.4 (IEEE, 2020).

Gokmen, T. & Haensch, W. Algorithm for training neural networks on resistive device arrays. Front. Neurosci. 14, 103 (2020).

Woo, J. et al. Improved synaptic behavior under identical pulses using AlOx/HfO2 bilayer RRAM array for neuromorphic systems. IEEE Electron Device Lett. 37, 994–997 (2016).

Wu, W. et al. A methodology to improve linearity of analog RRAM for neuromorphic computing. In 2018 IEEE Symposium on VLSI Technology 103–104 (IEEE, 2018).

Choi, S. et al. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nat. Mater. 17, 335–340 (2018).

Mou, X. et al. Analog memristive synapse based on topotactic phase transition for high-performance neuromorphic computing and neural network pruning. Sci. Adv. 7, eabh0648 (2021).

Widrow, B. Generalization and Information Storage in Networks of Adaline Neurons 435–461 (Spartan Books, 1962).

Fuller, E. J. et al. Redox transistors for neuromorphic computing. IBM J. Res. Dev. 63, 9:1–9:9 (2019).

Gkoupidenis, P., Schaefer, N., Garlan, B. & Malliaras, G. G. Neuromorphic functions in PEDOT:PSS organic electrochemical transistors. Adv. Mater. 27, 7176–7180 (2015).

Yao, X. et al. Protonic solid-state electrochemical synapse for physical neural networks. Nat. Commun. 11, 3134 (2020).

Fuller, E. J. et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 364, 570–574 (2019).

Onen, M., Emond, N., Li, J., Yildiz, B. & del Alamo, J. A. CMOS-compatible protonic programmable resistor based on phosphosilicate glass electrolyte for analog deep learning. Nano Lett. 21, 6111–6116 (2021).

Onen, M. et al. Nanosecond protonic programmable resistors for analog deep learning. Science 377, 539–543 (2022).

Fuller, E. J. et al. Li-ion synaptic transistor for low power analog computing. Adv. Mater. 29, 1604310 (2017).

Tang, J. et al. ECRAM as scalable synaptic cell for high-speed, low-power neuromorphic computing. In 2018 IEEE International Electron Devices Meeting (IEDM) 13.1.1–13.1.4 (IEEE, 2018).

Shi, J., Ha, S. D., Zhou, Y., Schoofs, F. & Ramanathan, S. A correlated nickelate synaptic transistor. Nat. Commun. 4, 2676 (2013).

Kim, S. et al. Metal-oxide based, CMOS-compatible ECRAM for deep learning accelerator. In 2019 IEEE International Electron Devices Meeting (IEDM) 35.7.1–35.7.4 (IEEE, 2019).

Lee, C., Choi, W., Kwak, M., Kim, S. & Hwang, H. Excellent synapse characteristics of 50 nm vertical transistor with WOx channel for high density neuromorphic system. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

Solomon, P. M. et al. Transient investigation of metal-oxide based, CMOS-compatible ECRAM. In 2021 IEEE International Reliability Physics Symposium (IRPS) 1–7 (IEEE, 2021).

Bishop, D. et al. Time-resolved conductance in electrochemical systems for neuromorphic computing. In 2018 International Conference on Solid State Devices and Materials 23–24 (2018).

Jo, M. et al. Gate-induced massive and reversible phase transition of VO2 channels using solid-state proton electrolytes. Adv. Funct. Mater. 28, 1802003 (2018).

Oh, C. et al. Deep proton insertion assisted by oxygen vacancies for long-term memory in VO2 synaptic transistor. Adv. Electron. Mater. 7, 2000802 (2021).

Leng, X. et al. Insulator to metal transition in WO3 induced by electrolyte gating. npj Quantum Mater. 2, 35 (2017).

Meng, Y. et al. Review: recent progress in low-temperature proton-conducting ceramics. J. Mater. Sci. 54, 9291–9312 (2019).

Ding, K. et al. Phase-change heterostructure enables ultralow noise and drift for memory operation. Science 366, 210–215 (2019).

Li, Y. et al. Capacitor-based cross-point array for analog neural network with record symmetry and linearity. In 2018 IEEE Symposium on VLSI Technology 25–26 (IEEE, 2018).

Zhang, J.-G., Benson, D., Tracy, C. E., Webb, J. & Deb, S. Self-bleaching mechanism of electrochromic WO3 films. In Proc. SPIE 2017, Optical Materials Technology for Energy Efficiency and Solar Energy Conversion XII 104–112 (SPIE, 1993).

Chen, P., Peng, X. & Yu, S. NeuroSim: a circuit-level macro model for benchmarking neuro-inspired architectures in online learning. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 37, 3067–3080 (2018).

Wen, R.-T., Granqvist, C. G. & Niklasson, G. A. Eliminating degradation and uncovering ion-trapping dynamics in electrochromic WO3 thin films. Nat. Mater. 14, 996–1001 (2015).

Melianas, A. et al. Temperature-resilient solid-state organic artificial synapses for neuromorphic computing. Sci. Adv. 6, eabb2958 (2020).

Katase, T., Onozato, T., Hirono, M., Mizuno, T. & Ohta, H. A transparent electrochromic metal-insulator switching device with three-terminal transistor geometry. Sci. Rep. 6, 25819 (2016).

Walczyk, C. et al. Impact of temperature on the resistive switching behavior of embedded HfO2-based RRAM devices. IEEE Trans. Electron Devices 58, 3124–3131 (2011).

Chen, P., Peng, X. & Yu, S. NeuroSim+: an integrated device-to-algorithm framework for benchmarking synaptic devices and array architectures. In 2017 IEEE International Electron Devices Meeting (IEDM) 6.1.1–6.1.4 (IEEE, 2017).

Peng, X., Huang, S., Jiang, H., Lu, A. & Yu, S. DNN+NeuroSim V2.0: an end-to-end benchmarking framework for compute-in-memory accelerators for on-chip training. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 40, 2306–2319 (2021).

Zhou, Y. et al. Enhanced transmittance modulation of ITO/NiOx/ZrO2:H/WO3/ITO electrochromic devices. Ionics 22, 25–32 (2016).

Park, J. S. et al. Evidence of proton transport in atomic layer deposited yttria-stabilized zirconia films. Chem. Mater. 22, 5366–5370 (2010).

Kindratenko, V. et al. in Practice and Experience in Advanced Research Computing (PEARC’ 20) 41–48 (ACM, 2020).

Acknowledgements

This work was supported by the US National Science Foundation grant 1950182 (Q.C.) and 2139185 (Q.C. and J.-M.Z.). Substantial aspects of the material characterizations and device fabrications were performed using the shared user facilities of the University of Illinois Fredrick Seitz Materials Research Laboratory and Holonyak Micro and Nanotechnology Laboratory. This work also made use of the Illinois Campus Cluster HAL, utilized resources supported by the National Science Foundation’s Major Research Instrumentation program grant 1725729 and the University of Illinois Urbana-Champaign. We thank T. Spila for assistance with the Rutherford backscattering spectrometry and SIMS measurements, and J. Baltrus for performing the X-ray photoelectron spectroscopy measurements.

Author information

Authors and Affiliations

Contributions

Q.C. conceived and designed the experiments. J.C., F.A., Y.W. and L.L.S. performed the experiments. J.Q., S.P. and J.-M.Z. performed the STEM-EDS analysis. Q.C. and J.C. wrote the paper. All the authors discussed the results (all of which are reported in the main text and Supplementary Information) and commented on the paper.

Corresponding author

Ethics declarations

Competing interests

J.-S.C. and Q.C. are inventors on a provisional patent application entitled ‘Solid-state electrochemical random access memory (ECRAM) and methods of making and operating a solid-state ECRAM’ (US 63/434,627) submitted by the Board of Trustees of the University of Illinois.

Peer review

Peer review information

Nature Electronics thanks Junwoo Son, Sanghyeon Kim and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

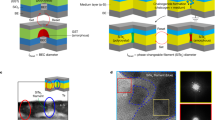

Extended Data Fig. 1 ECRAM fabrication flow.

Schematics illustrating the process flow to fabricate the CMOS-compatible, all-inorganic protonic ECRAM.

Extended Data Fig. 2 All-inorganic protonic ECRAM with elemental metal gate.

a, Schematic of the protonic ECRAM employing only Cr/Au as the gate electrode. b, Symmetric programing of the device channel conductance under gate-current pulses (100 potentiation then 100 depression pulses with the gate-current pulse amplitude of 100 pA and width of 3 s). c, Asymmetric programing of the same device but under gate-voltage pulses (50 potentiation then 50 depression pulses with the gate-voltage pulse amplitude of ±4 V and width of 3 s), caused by the non-zero built-in open-circuit potential.

Extended Data Fig. 3 Read noise and cycle-to-cycle variability of ECRAM operated with 10 µsec programming gate-voltage pulses.

a, Zoom-in view of the programing characteristics showing the readout of four discrete conductance states with low read noise during the 10 microseconds sensing period shaded in green, after 10 microseconds settling time, out of the 300 conductance states shown in Fig. 2b. Red dotted lines serve as visual guide to mark the average channel conductance in each state. b, Zoom-in view of the read-out conductance (black circle) after the corresponding weight-update pulses. The red solid line is the expected conductance value obtained through fitting the depression curve. The small deviation of the experimental data to the expectation indicates small cycle-to-cycle variation. Blue dotted lines serve as visual guide to mark the measured conductance values on y axis.

Extended Data Fig. 4 ECRAM pulse-measurement setups to extract the read transients.

a, Measurement configuration to extract tread. WGFMUs are connected to the ECRAM source and drain terminals. The gate is grounded. During measurement, the voltage pulse is applied on the drain side and the other channel of WGFMU reads the current signal. b, Measurement configuration to perform the microsecond pulse write operations and extract tread-after-write. WGFMUs are connected to the ECRAM gate and drain terminals. The source is grounded. During measurement, the voltage pulse is applied on the gate terminal for the weight-update and the other channel of WGFMU applies a small voltage pulse to reads the current flowing across the channel afterwards. SMU: source-measurement unit (Keysight B1517A). WGFMU: waveform generator/fast-measurement unit (Keysight B1530A). GND: ground. Red and blue dashed lines mark the WGFMU and SMU channels, respectively.

Extended Data Fig. 5 Platinum contact resistance to HxWO3.

a, SEM micrograph showing the transmission-line structure fabricated with Lch varied from 6 µm down to 150 nm but identical W of 60 µm. Scale bar, 50 µm. b, Width normalized overall resistance R as a function of Lch for HxWO3 switched between high (180 MΩ·sq-1) and low (150 kΩ·sq-1) sheet resistance corresponding to the operating dynamic range of ECRAM, showing a degradation of the device on/off ratio with the scaling of the Lch.

Extended Data Fig. 6 HxWO3 channel after the endurance test.

a, STEM micrograph showing the gate stack of the ECRAM after operation with 100 million read-write cycles. Scale bar, 100 nm. b, The depth profiles showing the atomic fractions of W (black), Hf (blue), and O (red) before (solid lines) and after (dotted lines) the 108 cycle endurance test, as measured by energy dispersive X-ray spectroscopy. The orange dashed line serves as a visual guide to mark the interface between WO3 and HfO2.

Extended Data Fig. 7 Operation and reliability of all-inorganic protonic ECRAMs under elevated temperature.

a, Programing of an all-inorganic protonic ECRAM with Al2O3 passivation measured at the same temperature after being annealed at 100 °C (black square), 150 °C (red circle), and 200 °C (blue triangle), respectively. b, Programing an all-inorganic protonic ECRAM at 80 °C (black) and 100 °C (red). G0 and ∆G increased due to the thermal excitation of additional carriers in the HxWO3 channel and the increase of proton diffusivity, respectively. c, Logarithmic scale plot showing the average ∆G per weight-update step as a function of the device operating temperature. Red dotted line represents the linear fitting to the data. d, Retention of the fully on-state conductance of the ECRAM cell at 80 °C (black) and 100 °C (red), and the corresponding drift coefficient (v), measured with the gate floating. e, ECRAM endurance test at 80 °C for 107 write-read pulses, showing no device degradation with the intermediate switching cycles plotted after 104, 105, 106, and 107 pulses.

Extended Data Fig. 8 One-transistor-one-ECRAM cell fabrication flow.

Schematics illustrating the process flow to fabricate a 1-transistor-1-ECRAM memory cell, consisted of an all-inorganic protonic ECRAM and a silicon MOSFET in different layers monolithically integrated together on a SOI wafer substrate.

Extended Data Fig. 9 Current-voltage characteristics of the silicon MOSFET selector measured before (part a) and after (part b) fabricating the protonic ECRAM layer on top with 40 nm HfO2 as the interlayer dielectric.

VDS: source-drain bias; IDS: source-drain current.

Extended Data Fig. 10 Device-to-device variation extracted from 8×8 ECRAM array.

a, Optical micrograph showing the completed 8 by 8 ECRAM array. Scale bar, 500 µm. b-d, Spatial mapping of the non-linearity (part b, standard deviation around 10%), minimum conductance (part c, standard deviation about 12%), and maximum conductance (part d, standard deviation about 13%) of the fabricated ECRAMs. Red indicated failed devices resulting from lithography or material defects. e-f, Collections of the programing characteristics of ECRAMs in row 1-4 (from top to bottom, part e) and row 5-8 (part f) of the array, respectively.

Supplementary information

Supplementary information

Supplementary Notes 1–7, Figs. 1–7, Tables 1 and 2 and refs. 1–42.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Cui, J., An, F., Qian, J. et al. CMOS-compatible electrochemical synaptic transistor arrays for deep learning accelerators. Nat Electron 6, 292–300 (2023). https://doi.org/10.1038/s41928-023-00939-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-00939-7

This article is cited by

-

Electrochemical random-access memory: recent advances in materials, devices, and systems towards neuromorphic computing

Nano Convergence (2024)

-

Strategy to improve synaptic behavior of ion-actuated synaptic transistors—the use of ion blocking layer to improve state retention

Scientific Reports (2024)

-

All-silicon multidimensionally-encoded optical physical unclonable functions for integrated circuit anti-counterfeiting

Nature Communications (2024)

-

A low-power vertical dual-gate neurotransistor with short-term memory for high energy-efficient neuromorphic computing

Nature Communications (2023)

-

Open-loop analog programmable electrochemical memory array

Nature Communications (2023)