Abstract

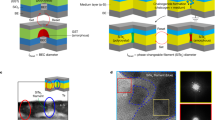

In-memory computing can be used to overcome the von Neumann bottleneck—the need to shuffle data between separate memory and computational units—and help improve computing performance. Co-integrated vertical transistor selectors (1T) and resistive memory elements (1R) in a 1T1R configuration offer advantages of scalability, speed and energy efficiency in current mass storage applications, and such 1T1R cells could also be potentially used for in-memory computation architectures. Here we show that a vertical transistor and resistive memory can be integrated onto a single vertical indium arsenide nanowire on silicon. The approach relies on an interface between the III–V semiconductor nanowire and a high-κ dielectric (hafnium oxide), which provides an oxide layer that can operate either as a vertical transistor selector or a high-performance resistive memory. The resulting 1T1R cells allow Boolean logic operations to be implemented in a single vertical nanowire with a minimal area footprint.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The datasets analysed in this study are available from the corresponding authors upon reasonable request.

References

Ielmini, D. & Wong, H. In-memory computing with resistive switching devices. Nat. Electron. 1, 333–343 (2018).

Wulf, W. & McKee, S. Hitting the memory wall. ACM Comp. Ar. 23, 20–24 (1995).

Xue, C. et al. A CMOS-integrated compute-in-memory macro based on resistive random-access memory for AI edge devices. Nat. Electron. 4, 81–90 (2021).

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Shulaker, M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Burr, G. et al. Access devices for 3D crosspoint memory. J. Vac. Sci. Technol. B 32, 040802 (2014).

International Roadmap for Devices and Systems (IRDS)—More Moore (IEEE, 2020).

Fang, Z. et al. Fully CMOS-compatible 1T1R integration of vertical nanopillar GAA transistor and oxide-based RRAM cell for high-density nonvolatile memory application. IEEE Trans. Electron Devices 60, 1108–1113 (2013).

Chen, B. et al. Highly compact (4F2) and well behaved nano-pillar transistor controlled resistive switching cell for neuromorphic system application. Sci. Rep. 4, 6863 (2014).

Yakimets, D. et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans. Electron Devices 62, 1433–1439 (2015).

Grossi, A. et al. Resistive RAM endurance: array-level characterization and correction techniques targeting deep learning applications. IEEE Trans. Electron Devices 66, 1281–1288 (2019).

Lee, M. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x/TaO2−x bilayer structures. Nat. Mater. 10, 625–630 (2011).

Persson, K., Ram, M. S. & Wernersson, L. E. Ultra-scaled AlOx diffusion barriers for multibit HfOx RRAM operation. IEEE J. Electron Devices Soc. 9, 564–569 (2021).

Jansson, K., Lind, E. & Wernersson, L. Performance evaluation of III–V nanowire transistors. IEEE Trans. Electron Devices 59, 2375–2382 (2012).

Kilpi, O., Hellenbrand, M., Svensson, J., Lind, E. & Wernersson, L. Vertical nanowire III–V MOSFETs with improved high‐frequency gain. Electron. Lett. 56, 669–671 (2020).

Kilpi, O., Svensson, J., Lind, E. & Wernersson, L. Electrical properties of vertical InAs/InGaAs heterostructure MOSFETs. IEEE J. Electron Devices Soc. 7, 70–75 (2019).

Kilpi, O. et al. High-performance vertical III-V nanowire MOSFETs on Si with gm > 3 mS/μm. IEEE Electron Device Lett. 41, 1161–1164 (2020).

Ram, M. S., Persson, K., Borg, M. & Wernersson, L. Low-power resistive memory integrated on III–V vertical nanowire MOSFETs on silicon. IEEE Electron Device Lett. 41, 1432–1435 (2020).

Hellenbrand, M., Kilpi, O., Svensson, J., Lind, E. & Wernersson, L. Low-frequency noise in nanowire and planar III-V MOSFETs. Microelectron. Eng. 215, 110986 (2019).

Navarro, C. et al. Capacitor-less dynamic random access memory based on a III–V transistor with a gate length of 14 nm. Nat. Electron. 2, 412–419 (2019).

Convertino, C. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Wang, Z. et al. Efficient implementation of Boolean and full-adder functions with 1T1R RRAMs for beyond von Neumann in-memory computing. IEEE Trans. Electron Devices 65, 4659–4666 (2018).

Pacheco, P. & Malensek, M. An Introduction to Parallel Programming (Morgan Kaufmann, 2011).

Timm, R. et al. Self-cleaning and surface chemical reactions during hafnium dioxide atomic layer deposition on indium arsenide. Nat. Commun. 9, 1412 (2018).

Svensson, J., Dey, A., Jacobsson, D. & Wernersson, L. III–V nanowire complementary metal–oxide semiconductor transistors monolithically integrated on Si. Nano Lett. 15, 7898–7904 (2015).

Sivan, M. et al. All WSe2 1T1R resistive RAM cell for future monolithic 3D embedded memory integration. Nat. Commun. 10, 5201 (2019).

Berg, M. et al. Electrical characterization and modeling of gate-last vertical InAs nanowire MOSFETs on Si. IEEE Electron Device Lett. 37, 966–969 (2016).

Kilpi, O. et al. Sub-100-nm gate-length scaling of vertical InAs/InGaAs nanowire MOSFETs on Si. In 2017 IEEE International Electron Devices Meeting (IEDM) 17.3.1–17.3.4 (IEEE, 2018).

Zhao, X. et al. Sub-10-nm-diameter InGaAs vertical nanowire MOSFETs: Ni versus Mo contacts. IEEE Trans. Electron Devices 65, 3762–3768 (2018).

Jonsson, A., Svensson, J. & Wernersson, L. A self-aligned gate-last process applied to all-III–V CMOS on Si. IEEE Electron Device Lett. 39, 935–938 (2018).

Persson, K., Ram, M. S., Kilpi, O., Borg, M. & Wernersson, L. Cross-point arrays with low-power ITO-HfO2 resistive memory cells integrated on vertical III-V nanowires. Adv. Electron. Mater. 6, 2000154 (2020).

Yong, Z. et al. Tuning oxygen vacancies and resistive switching properties in ultra-thin HfO2 RRAM via TiN bottom electrode and interface engineering. Appl. Surf. Sci. 551, 149386 (2021).

Li, K. et al. Utilizing sub-5 nm sidewall electrode technology for atomic-scale resistive memory fabrication. In 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers 1–2 (IEEE, 2014).

Borghetti, J. et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Wang, Z. et al. Functionally complete Boolean logic in 1T1R resistive random access memory. IEEE Electron Device Lett. 38, 179–182 (2017).

Wei, H., Wang, Z., Tian, X., Käll, M. & Xu, H. Cascaded logic gates in nanophotonic plasmon networks. Nat. Commun. 2, 387 (2011).

He, Z. et al. Atomic layer-deposited HfAlOx-based RRAM with low operating voltage for computing in-memory applications. Nanoscale Res. Lett. 125, 51 (2019).

Yeap, G. Smart mobile SoCs driving the semiconductor industry: technology trend, challenges and opportunities. In 2013 IEEE International Electron Devices Meeting 1.3.1–1.3.8 (IEEE, 2013).

Song, J. et al. Effects of RESET current overshoot and resistance state on reliability of RRAM. IEEE Electron Device Lett. 35, 636–638 (2014).

Timm, R. et al. Reduction of native oxides on InAs by atomic layer deposited Al2O3 and HfO2. Appl. Phys. Lett. 97, 132904 (2010).

Schwartz, G. P., Sunder, W. A., Griffiths, J. E. & Gualtieri, G. J. Condensed phase diagram for the In–As–O system. Thin Solid Films 94, 205 (1982).

Lin, S. et al. Improving performance by inserting an indium oxide layer as an oxygen ion storage layer in HfO2-based resistive random access memory. IEEE Trans. Electron Devices 68, 1037–1040 (2021).

Timm, R. et al. Interface composition of InAs nanowires with Al2O3 and HfO2 thin films. Appl. Phys. Lett. 99, 222907 (2011).

Palumbo, F., Shekhter, P. & Eizenberg, M. Influence of the oxide–semiconductor interface on the resistive switching phenomenon in metal/Al2O3/InGaAs. Solid-State Electron. 93, 56–60 (2014).

Sun, J., Lind, E., Maximov, I. & Xu, H. Memristive and memcapacitive characteristics of a Au/Ti–HfO2-InP/InGaAs diode. IEEE Electron Device Lett. 32, 131–133 (2011).

Acknowledgements

We would like to thank J. Svensson for growing the nanowires for this work. This work is financed through the Swedish Research Council grant no. 2016-06186 Electronics beyond kT/q (L.-E.W.).

Author information

Authors and Affiliations

Contributions

M.S.R. fabricated the 1T1R devices. M.S.R. and K.-M.P. performed the electrical characterization of 1T1R devices. K.-M.P. fabricated the planar devices for XPS characterization. A.I. and R.T. performed the XPS characterization and prepared Fig. 4 with the corresponding analysis. K.-M.P. actively contributed to the writing process and performed the array simulations. A.J. helped with the SiO2 process module and prepared Fig. 1a. M.S.R. conceptualized the idea of the metal electrode-less RRAM integration. M.S.R. and L.-E.W. wrote the manuscript. L.-E.W. initialized and supervised the project. All the authors discussed and revised the final manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Electronics thanks Cezhou Zhao and the other, anonymous, reviewer(s) for their contribution to the peer review of this work

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–7 and Tables 1–4.

Rights and permissions

About this article

Cite this article

Ram, M.S., Persson, KM., Irish, A. et al. High-density logic-in-memory devices using vertical indium arsenide nanowires on silicon. Nat Electron 4, 914–920 (2021). https://doi.org/10.1038/s41928-021-00688-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-021-00688-5

This article is cited by

-

Strong coupling between a microwave photon and a singlet-triplet qubit

Nature Communications (2024)

-

Steep-slope vertical-transport transistors built from sub-5 nm Thin van der Waals heterostructures

Nature Communications (2024)

-

The role of arsenic in the operation of sulfur-based electrical threshold switches

Nature Communications (2023)

-

Insights into the performance of InAs-based devices in extreme environments from multiscale simulations

Applied Physics A (2023)

-

Controlled growth of two-dimensional InAs single crystals via van der Waals epitaxy

Nano Research (2022)