Abstract

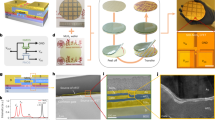

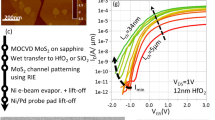

Tunnel field-effect transistors (TFETs) rely on quantum-mechanical tunnelling and, unlike conventional metal–oxide–semiconductor field-effect transistors (MOSFETs), require less than 60 mV of gate voltage swing to induce one order of magnitude variation in the drain current at ambient temperature. III–V heterostructure TFETs are promising for low-power applications, but are outperformed by MOSFETs in terms of speed and energy efficiency when high performance is required at higher drive voltages. Hybrid technologies—combining both TFETs and MOSFETs—could enable low-power and high-performance applications, but require the co-integration of different materials in a scalable complementary metal–oxide–semiconductor (CMOS) platform. Here, we report a scaled III–V hybrid TFET–MOSFET technology on silicon that achieves a minimum subthreshold slope of 42 mV dec−1 for TFET devices and 62 mV dec−1 for MOSFET devices. The InGaAs/GaAsSb TFETs are co-integrated with the InGaAs MOSFETs on the same silicon substrate by means of a CMOS-compatible replacement-metal-gate fabrication flow, allowing independent optimization of both device types.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

De, V., Vangal, S. & Krishnamurthy, R. Near threshold voltage (NTV) computing: computing in the dark silicon era. IEEE Des. Test 34, 24–30 (2016).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Ionescu, A. M. Negative capacitance gives a positive boost.Nat. Nanotechnol. 13, 7–8 (2018).

Salvatore, G. A., Bouvet, D. & Ionescu, A. M. Demonstration of subthreshold swing smaller than 60mV/decade in Fe-FET with P (VDF-TrFE)/ SiO2 gate stack. Nano 8, 479–481 (2008).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 14–28 (2017).

Chen, F. et al. Integrated circuit design with NEM relays. In 2008 IEEE/ACM International Conference on Computer-Aided Design, Digest of Technical Papers, ICCAD 750–757 (IEEE, 2008).

Gopalakrishnan, K., Woo, R., Jungemann, C., Griffin, P. B. & Plummer, J. D. Impact ionization MOS (I-MOS)—Part II: experimental results. IEEE Trans. Electron Devices 52, 77–84 (2005).

Abelein, U. et al. A novel vertical impact ionisation MOSFET (I-MOS) concept. In Proc. 2006 25th International Conference on Microelectronics, MIEL 2006 127–130 (IEEE, 2006).

Avci, U. E., Morris, D. H. & Young, I. A. Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Devices Soc. 3, 88–95 (2015).

Webster, J. G., Verreck, D., Groeseneken, G. & Verhulst, A. in Wiley Encyclopedia of Electrical and Electronics Engineering 1–24 (John Wiley & Sons, 2016); https://doi.org/10.1002/047134608x.w8333

Seabaugh, B. A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010).

Choi, W. Y., Park, B., Lee, J. D. & Liu, T. K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28, 743–745 (2007).

Jeon, K. et al. Si tunnel transistors with a novel silicided source and 46 mV/dec swing. In Symposium on VLSI Technology Digest of Technical Papers 121–122 (IEEE, 2010).

Knoll, L. et al. Inverters with strained Si nanowire complementary tunnel field-effect transistors. IEEE Electron Device Lett. 34, 813–815 (2013).

del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Sant, S. & Schenk, A. Trap-tolerant device geometry for InAs/Si pTFETs. IEEE Electron Device Lett. 38, 1363–1366 (2017).

Sant, S. et al. Lateral InAs/Si p-type tunnel FETs integrated on Si—Part 2: simulation study of the impact of interface traps. IEEE Trans. Electron Devices 63, 4240–4247 (2016).

Kim, D. et al. Low power circuit design based on heterojunction tunneling transistors (HETTs). In Proc. International Symposium on Low Power Electronics and Design 219–224 (ACM Press, 2009).

Young, I. A., Avci, U. E. & Morris, D. H. Tunneling field effect transistors: device and circuit considerations for energy efficient logic opportunities. In Proc. 2015 IEEE International Electron Devices Meeting (IEDM) 22.1.1–22.1.4 (IEEE, 2015); https://doi.org/10.1109/IEDM.2015.7409755

Saripalli, V., Mishra, A., Datta, S. & Narayanan, V. An energy-efficient heterogeneous CMP based on hybrid TFET-CMOS cores. In Proc. 2011 48th ACM/EDAC/IEEE Design Automation Conference 729–734 (IEEE, 2011); https://doi.org/10.1145/2024724.2024889

Memisevic, E., Svensson, J., Hellenbrand, M., Lind, E. & Wernersson, L. E. Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion = 10 µA/µm for Ioff = 1 nA/µm at VDS = 0.3 V. In Proc. IEEE International Electron Devices Meeting 19.1.1–19.1.4 (IEEE, 2016); https://doi.org/10.1109/IEDM.2016.7838450

Alian, A. et al. InGaAs tunnel FET with sub-nanometer EOT and sub-60 mV/dec sub-threshold swing at room temperature. Appl. Phys. Lett. 109, 243502 (2016).

Zota, C. B. et al. High performance quantum well InGaAs-On-Si MOSFETs with sub-20 nm gate length for RF applications. In Proc. 2018 IEEE International Electron Devices Meeting (IEDM) 39.4.1–39.4.4 (IEEE, 2018); https://doi.org/10.1109/IEDM.2018.8614530

Zota, C. B. et al. InGaAs-on-insulator MOSFETs featuring scaled logic devices and record RF performance. In 2018 Symposium on VLSI Technology Digest of Technical Papers 165–166 (IEEE, 2018).

Czornomaz, L. et al. Co-integration of InGaAs n- and SiGe p-MOSFETs into digital CMOS circuits using hybrid dual-channel ETXOI substrates. In Proc. 2013 International Electron Devices Meeting 2.8.1–2.8.4 (IEEE, 2013); https://doi.org/10.1109/IEDM.2013.6724548

Cutaia, D. et al. Complementary III–V heterojunction lateral NW Tunnel FET technology on Si. In 2016 Symposium on VLSI Technology Digest of Technical Papers 1–2 (IEEE, 2016).

Convertino, C. et al. Sub-thermionic scalable III–V tunnel field-effect transistors integrated on Si (100). In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) 37.1.1–37.1.4 (IEEE, 2019).

Gopireddy, B., Skarlatos, D., Zhu, W. & Torrellas, J. HetCore: TFET-CMOS hetero-device architecture for CPUs and GPUs. In Proc. 2018 ACM/IEEE 45th Annual International Symposium on Computer Architecture (ISCA) 802–815 (IEEE, 2018); https://doi.org/10.1109/ISCA.2018.00072

Convertino, C., Zota, C. B., Schmid, H., Ionescu, A. M. & Moselund, K. E. III–V heterostructure tunnel field-effect transistor. J. Phys. Condens. Matter 30, 264005 (2018).

Alian, A. et al. Record 47 mV/dec top-down vertical nanowire InGaAs/GaAsSb tunnel FETs. In 2018 Symposium on VLSI Technology Digest of Technical Papers 133–134 (IEEE, 2018).

Smets, Q. et al. Calibration of the effective tunneling bandgap in GaAsSb/InGaAs for improved TFET performance prediction. IEEE Trans. Electron Devices 63, 4248–4254 (2016).

Convertino, C. et al. InGaAs-on-insulator FinFETs with reduced off-current and record performance. In Proc. 2018 IEEE International Electron Devices Meeting (IEDM) 39.2.1–39.2.4 (IEEE, 2018); https://doi.org/10.1109/IEDM.2018.8614640

Daix, N. et al. Towards large size substrates for III–V co-integration made by direct wafer bonding on Si. APL Mater. 2, 086104 (2014).

Lin, J., Zhao, X., Antoniadis, D. A. & del Alamo, J. A. A novel digital etch technique for deeply scaled III–V MOSFETs. IEEE Electron Device Lett. 35, 440–442 (2014).

Convertino, C. et al. High performance InGaAs FinFETs with raised source/drain extensions. Jpn. J. Appl. Phys. 58, 080901 (2019).

Rosca, T., Saeidi, A., Memisevic, E., Wernersson, L. E. & Ionescu, A. M. An experimental study of heterostructure tunnel FET nanowire arrays: digital and analog figures of merit from 300 K to 10 K. In Proc. 2018 IEEE International Electron Devices Meeting (IEDM) 13.5.1–13.5.4 (IEEE, 2019).

Ganjipour, B. et al. High current density Esaki tunnel diodes based on GaSb-InAsSb heterostructure nanowires. Nano Lett. 11, 4222–4226 (2011).

Agarwal, S. & Yablonovitch, E. Band-edge steepness obtained from Esaki/backward diode current—voltage characteristics. IEEE Trans. Electron Devices 61, 1488–1493 (2014).

Memisevic, E., Lind, E., Hellenbrand, M., Svensson, J. & Wernersson, L.-E. Impact of band-tails on the subthreshold swing of III–V tunnel field-effect transistor. IEEE Electron Device Lett. 3106, 1 (2017).

Sajjad, R. N., Chern, W., Hoyt, J. L. & Antoniadis, D. A. Trap assisted tunneling and its effect on subthreshold swing of tunnel FETs. IEEE Trans. Electron Devices 63, 4380–4387 (2016).

Schenk, A. et al. The impact of hetero-junction and oxide-interface traps on the performance of InAs/Si and InAs/GaAsSb nanowire tunnel FETs. In Proc. 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) 273–276 (IEEE, 2017).

Alian, A. et al. InGaAs tunnel FET with sub-nanometer EOT and sub-60-mV/dec sub-threshold swing at room temperature. Appl. Phys. Lett. 109, 243502 (2016).

Bessire, C. D. et al. Trap-assisted tunneling in Si-InAs nanowire heterojunction tunnel diodes. Nano Lett. 11, 4195–4199 (2011).

Verhulst, A. S., Vandenberghe, W. G., Maex, K. & Groeseneken, G. Tunnel field-effect transistor without gate-drain overlap. Appl. Phys. Lett. 91, 053102 (2007).

Le Royer, C. & Mayer, F. Exhaustive experimental study of tunnel field effect transistors (TFETs): from materials to architecture. In Proc. 10th International Conference on Ultimate Integration of Silicon 53–56 (IEEE, 2009); https://doi.org/10.1109/ULIS.2009.4897537

Appenzeller, J. et al. Toward nanowire electronics. IEEE Trans. Electron Devices 55, 2827–2845 (2008).

Zhao, X., Member, S., Vardi, A. & Alamo, J. A. Sub-thermal subthreshold characteristics in top–down InGaAs/InAs heterojunction vertical nanowire tunnel FETs. IEEE Electron Device Lett. 38, 855–858 (2017).

Noguchi, M. et al. High Ion/Ioff and low subthreshold slope planar-type InGaAs tunnel FETs with Zn-diffused source junctions. In 2013 IEEE International Electron Devices Meeting (IEEE, 2013); https://ieeexplore.ieee.org/document/6724707.

Dewey, G. et al. Fabrication, characterization and physics of III–V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing. Tech. Dig. IEDM 3, 785–788 (2011).

Convertino, C., Zota, C. B., Caimi, D., Sousa, M. & Czornomaz, L. InGaAs FinFETs 3-D sequentially integrated on FDSOI Si CMOS with record perfomance. IEEE J. Electron Devices Soc. 7, 1170–1174 (IEEE, 2019); https://doi.org/10.1109/JEDS.2019.2928471

Ahn, D. H., Ji, S. M., Takenaka, M. & Takagi, S. Performance improvement of InxGa1−xAs tunnel FETs with quantum well and EOT scaling. In 2016 IEEE Symposium on VLSI Technology (IEEE, 2016); https://ieeexplore.ieee.org/abstract/document/7573443

Acknowledgements

This work was partially funded by the European FP7 programme under grant no. 619509 (E2SWITCH) and by the Horizon 2020 programmes under grant nos. 688784 (INSIGHT) and 871764 (SEQUENCE). We acknowledge M. Sousa, Y. Baumgartner, P. Staudinger and C. Marty for helpful technical discussions and support, as well as the entire IBM BRNC operations team.

Author information

Authors and Affiliations

Contributions

C.C. carried out the experiments and wrote the initial manuscript. C.B.Z. contributed to transistor fabrication and actively participated in the experimental characterization. C.C., H.S. and K.E.M. conceived the concept for the TFET integration. L.C., C.C. and C.B.Z. developed the transistor fabrication process. L.C. and D.C. developed the wafer bonding approach. C.C. developed the material epitaxial growth. K.E.M. and A.M.I. coordinated and supervised the whole work. All authors discussed the final results and revised and commented on the submitted manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–4.

Rights and permissions

About this article

Cite this article

Convertino, C., Zota, C.B., Schmid, H. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat Electron 4, 162–170 (2021). https://doi.org/10.1038/s41928-020-00531-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-020-00531-3

This article is cited by

-

Design and Analysis of Si/GaSb HTFET-Based 7T SRAM Cell for Ultra-Low Voltage Applications

Silicon (2024)

-

A new line tunneling SiGe/Si iTFET with control gate for leakage suppression and subthreshold swing improvement

Discover Nano (2023)

-

Vertical GeSn nanowire MOSFETs for CMOS beyond silicon

Communications Engineering (2023)

-

Ferroelectric gating of two-dimensional semiconductors for the integration of steep-slope logic and neuromorphic devices

Nature Electronics (2023)

-

Reconfigurable signal modulation in a ferroelectric tunnel field-effect transistor

Nature Communications (2023)