Abstract

The discovery of ferroelectricity in oxides that are compatible with modern semiconductor manufacturing processes, such as hafnium oxide, has led to a re-emergence of the ferroelectric field-effect transistor in advanced microelectronics. A ferroelectric field-effect transistor combines a ferroelectric material with a semiconductor in a transistor structure. In doing so, it merges logic and memory functionalities at the single-device level, delivering some of the most pressing hardware-level demands for emerging computing paradigms. Here, we examine the potential of the ferroelectric field-effect transistor technologies in current embedded non-volatile memory applications and future in-memory, biomimetic and alternative computing models. We highlight the material- and device-level challenges involved in high-volume manufacturing in advanced technology nodes (≤10 nm), which are reminiscent of those encountered in the early days of high-K-metal-gate transistor development. We argue that the ferroelectric field-effect transistors can be a key hardware component in the future of computing, providing a new approach to electronics that we term ferroelectronics.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Ma, T. & Han, J.-P. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron Device Lett. 23, 386–388 (2002).

Mikolajick, T., Schroeder, U. & Slesazeck, S. The past, the present, and the future of ferroelectric memories. IEEE Trans. Electron Devices 67, 1434–1443 (2020).

Sugibuchi, K., Kurogi, Y. & Endo, N. Ferroelectric field-effect memory device using Bi4Ti3O12 film. J. Appl. Phys. 46, 2877–2881 (1975). This work demonstrated one of the earliest ferroelectric field-effect transistors and used a perovskite oxide based ferroelectric.

Scott, J. F. Ferroelectric Memories Vol. 3 (Springer, 2000).

Böscke, T. et al. Phase transitions in ferroelectric silicon doped hafnium oxide. Appl. Phys. Lett. 99, 112904 (2011).

Böscke, T., Müller, J., Bräuhaus, D., Schröder, U. & Böttger, U. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In 2011 Int. Electron Devices Meeting 24.5.1–24.5.4 (IEEE, 2011). This work demonstrated a ferroelectric field-effect transistor with a hafnium oxide based ferroelectric.

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat. Electron. 1, 442–450 (2018).

Aly, M. M. S. et al. Energy-efficient abundant-data computing: The N3XT 1,000x. Computer 48, 24–33 (2015).

Keshavarzi, A. & van den Hoek, W. Edge intelligence—on the challenging road to a trillion smart connected iot devices. IEEE Des. Test 36, 41–64 (2019).

Wong, J. C. & Salahuddin, S. Negative capacitance transistors. Proc. IEEE 107, 49–62 (2018).

Diestelhorst, M. & Drozhdin, K. Stochastic resonance and domain switching. Ferroelectrics 291, 217–224 (2003).

Heron, J. et al. Deterministic switching of ferromagnetism at room temperature using an electric field. Nature 516, 370–373 (2014).

Si, M. et al. A ferroelectric semiconductor field-effect transistor. Nat. Electron. 2, 580–586 (2019).

Ievlev, A. et al. Intermittency, quasiperiodicity and chaos in probe-induced ferroelectric domain switching. Nat. Phys. 10, 59–66 (2014).

Müller, K. A. & Burkard, H. SrTiO3: an intrinsic quantum paraelectric below 4 K. Phys. Rev. B 19, 3593 (1979).

Jerry, M. et al. Ferroelectric FET analog synapse for acceleration of deep neural network training. In 2017 IEEE Int. Electron Devices Meeting (IEDM), 6.2.1–6.1.4 (IEEE, 2017). This work demonstrated multi-state (5-bit) weight cell/analogue synapse based on a ferroelectric field-effect transistor for deep neural network accelerator applications with a ×4 conductance modulation and ~75 ns program pulses.

Seo, M. et al. First demonstration of a logic-process compatible junctionless ferroelectric finfet synapse for neuromorphic applications. IEEE Electron Device Lett. 39, 1445–1448 (2018).

Chung, W., Si, M. & Peide, D. Y. First demonstration of Ge ferroelectric nanowire FET as synaptic device for online learning in neural network with high number of conductance state and gmax/gmin. In 2018 IEEE International Electron Devices Meeting (IEDM), 15.2.1–15.2.4 (IEEE, 2018).

Ni, K. et al. SoC logic compatible multi-bit FeMFET weight cell for neuromorphic applications. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 13.2.1–13.2.4 (IEEE, 2018).

Sun, X., Wang, P., Ni, K., Datta, S. & Yu, S. Exploiting hybrid precision for training and inference: A 2T-1FeFET based analog synaptic weight cell. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 3.1.1–3.1.4 (IEEE, 2018).

Li, X. et al. Enabling energy-efficient nonvolatile computing with negative capacitance FET. IEEE Trans. Electron Devices 64, 3452–3458 (2017).

Wang, Z. et al. Experimental demonstration of ferroelectric spiking neurons for unsupervised clustering. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 13.3.1–13.3.4 (IEEE, 2018). This work experimentally demonstrated the concept of a ferroelectric field-effect transistor based oscillators and spiking neurons.

Fang, Y. et al. Neuro-mimetic dynamics of a ferroelectric FET-based spiking neuron. IEEE Electron Device Lett. 40, 1213–1216 (2019).

Wang, Z., Khandelwal, S. & Khan, A. I. Ferroelectric oscillators and their coupled networks. IEEE Electron Device Lett. 38, 1614–1617 (2017).

Fang, Y. et al. A swarm optimization solver based on ferroelectric spiking neural networks. Front. Neurosci. 13, 855 (2019).

Oh, S., Hwang, H. & Yoo, I. Ferroelectric materials for neuromorphic computing. APL Mater. 7, 091109 (2019).

Gokmen, T. & Vlasov, Y. Acceleration of deep neural network training with resistive cross-point devices: Design considerations. Front. Neurosci. 10, 333 (2016).

Ni, K. et al. Ferroelectric ternary content-addressable memory for one-shot learning. Nat. Electron. 2, 521–529 (2019).

Tan, A. J. et al. Experimental demonstration of a ferroelectric HfO2-based content addressable memory cell. IEEE Electron Device Lett. (2019).

Wang, Y. et al. A 3 µs wake-up time nonvolatile processor based on ferroelectric flip-flops. In 2012 Proc. ESSCIRC 149–152 (IEEE, 2012).

Mulaosmanovic, H., Mikolajick, T. & Slesazeck, S. Accumulative polarization reversal in nanoscale ferroelectric transistors. ACS Appl. Mater. Interfaces 10, 23997–24002 (2018). This work demonstrated non-trivial effects related to ferroelectric polarization switching at scaled lateral dimensions, namely meta-plasticity/polarization accumulation, single-domain-like switching and probabilistic switching, in short channel ferroelectric field-effect transistors.

Ni, K. et al. In-memory computing primitive for sensor data fusion in 28 nm HKMG FeFET technology. In 2018 IEEE International Electron Devices Meeting (IEDM), 16.1.1–16.1.4 (IEEE, 2018).

Mulaosmanovic, H., Mikolajick, T. & Slesazeck, S. Random number generation based on ferroelectric switching. IEEE Electron Device Lett. 39, 135–138 (2017).

Luo, J. et al. Capacitor-less stochastic leaky-FeFET neuron of both excitatory and inhibitory connections for SNN with reduced hardware cost. In 2019 IEEE Int. Electron Devices Meeting (IEDM) 6–4 (IEEE, 2019).

Florent, K. et al. Vertical ferroelectric HfO2 FET based on 3-D NAND architecture: towards dense low-power memory. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 2.5.1–2.5.4 (IEEE, 2018).

Thirumala, S. K. & Gupta, S. K. Reconfigurable ferroelectric transistor—part I: device design and operation. IEEE Trans. Electron Devices 66, 2771–2779 (2019).

Tasneem, N. & Khan, A. I. On the possibility of dynamically tuning and collapsing the ferroelectric hysteresis/memory window in an asymmetric DG MOS device: a path to a reconfigurable logic-memory device. In 2018 76th Device Research Conference (DRC) 1–2 (IEEE, 2018).

Wang, Z. et al. Cryogenic characterization of a ferroelectric field-effect-transistor. Appl. Phys. Lett. 116, 042902 (2020).

Chen, K.-Y., Tsai, Y.-S. & Wu, Y.-H. Ionizing radiation effect on memory characteristics for HfO2-based ferroelectric field-effect transistors. IEEE Electron Device Lett. 40, 1370–1373 (2019).

Shum, D. et al. Functionality demonstration of a high-density 1.1 V self-aligned split-gate NVM cell embedded into LP 40 nm CMOS for automotive and smart card applications. In 2015 IEEE Int. Memory Workshop (IMW) https://doi.org/10.1109/IMW.2015.7150288 (IEEE, 2015).

Kanda, A. et al. A 24-MB embedded flash system based on 28-nm SG-MONOS Featuring 240-MHz read operations and robust over-the-air software update for automotive applications. IEEE Solid-State Circ. Lett. 2, 273–276 (2019).

Tsuda, S. et al. First demonstration of FinFET split-gate MONOS for high-speed and highly-reliable embedded flash in 16/14 nm-node and beyond. In 2016 IEEE Int. Electron Devices Meeting (IEDM), 11.1.1–11.1.4 (IEEE, 2016).

Wei, L. et al. A 7Mb STT-MRAM in 22FFL FinFET technology with 4 ns read sensing time at 0.9 V using write-verify-write scheme and offset-cancellation sensing technique. In 2019 IEEE Int. Solid-State Circuits Conference-(ISSCC), 214–216 (IEEE, 2019).

Lee, K. et al. 1Gbit high density embedded STT-MRAM in 28nm FDSOI technology. In 2019 IEEE Int. Electron Devices Meeting (IEDM) 2.2.1–2.2.4 (IEEE, 2019).

Jain, P. et al. A 3.6 Mb 10.1 Mb/mm2 embedded non-volatile ReRAM macro in 22 nm FinFET technology with adaptive forming/set/reset schemes yielding down to 0.5 V with sensing time of 5ns at 0.7 V. In 2019 IEEE Int. Solid-State Circuits Conference-(ISSCC) 212–214 (IEEE, 2019).

Wu, J. et al. A 40 nm low-power logic compatible phase change memory technology. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 27–6 (IEEE, 2018).

Dünkel, S. et al. A FEFET based super-low-power ultra-fast embedded nvm technology for 22 nm FDSOI and beyond. In 2017 IEEE Int. Electron Devices Meeting (IEDM) 19–7 (IEEE, 2017). This work demonstrated scaled ferroelectric field-effect transistors in the fully depleted silicon-on-insulator (SOI) platform at the 22 nm node.

Trentzsch, M. et al. A 28 nm HKMG super low power embedded NVM technology based on ferroelectric FETs. In 2016 IEEE Int. Electron Devices Meeting (IEDM), 11–5 (IEEE, 2016).

Lyu, X., Si, M., Shrestha, P., Cheung, K. & Ye, P. First direct measurement of sub-nanosecond polarization switching in ferroelectric hafnium zirconium oxide. In 2019 IEEE Int. Electron Devices Meeting (IEDM) 15–2 (IEEE, 2019).

Wei, Y. et al. Magneto-ionic control of spin polarization in multiferroic tunnel junctions. npj Quant. Mater. 4, 1–6 (2019).

Cheema, S. S. et al. Enhanced ferroelectricity in ultrathin films grown directly on silicon. Nature 580, 478–482 (2020). This work demonstrated the thickness scalability of hafnium oxide based ferroelectrics.

Lederer, M. et al. Local crystallographic phase detection and texture mapping in ferroelectric Zr doped HfO2 films by transmission-EBSD. Appl. Phys. Lett. 115, 222902 (2019).

Grimley, E. D., Schenk, T., Mikolajick, T., Schroeder, U. & LeBeau, J. M. Atomic structure of domain and interphase boundaries in ferroelectric HfO2. Adv. Mater. Interf. 5, 1701258 (2018).

Ni, K., Chakraborty, W., Smith, J., Grisafe, B. & Datta, S. Fundamental understanding and control of device-to-device variation in deeply scaled ferroelectric fets. In 2019 Symposium on VLSI Technology, T40–T41 (IEEE, 2019).

Maekawa, K. et al. Impact of homogeneously dispersed al nanoclusters by Si-monolayer insertion into Hf0.5Zr0.5O2 film on FeFET memory array with tight threshold voltage distribution. In 2019 IEEE Int. Electron Devices Meeting (IEDM) 15–4 (IEEE, 2019).

Migita, S., Morita, Y., Mizubayashi, W. & Ota, H. Preparation of epitaxial HfO2 film (EOT=0.5 nm) on Si substrate using atomic-layer deposition of amorphous film and rapid thermal crystallization (RTC) in an abrupt temperature gradient. In 2010 Int. Electron Devices Meeting, 11.5.1–11.5.4 (IEEE, 2010).

Chatterjee, K. et al. Self-aligned, gate last, FDSOI, ferroelectric gate memory device with 5.5-nm Hf0.8Zr0.2O2, high endurance and breakdown recovery. IEEE Electron Device Lett. 38, 1379–1382 (2017).

Chau, R. Process and packaging innovations for Moore’s Law continuation and beyond. In 2019 Int. Electron Devices Meeting 1.1 (IEEE, 2019).

Kozodaev, M. G. et al. Mitigating wakeup effect and improving endurance of ferroelectric HfO2-ZrO2 thin films by careful La-doping. J. Appl. Phys. 125, 034101 (2019).

Muller, J. et al. High endurance strategies for hafnium oxide based ferroelectric field effect transistor. In 2016 16th Non-Volatile Memory Technology Symposium (NVMTS) https://doi.org/10.1109/NVMTS.2016.7781517 (IEEE, 2016).

Ni, K. et al. Critical role of interlayer in Hf0.5Zr0.5O2 ferroelectric FET nonvolatile memory performance. IEEE Trans. Electron Devices 65, 2461–2469 (2018). This work provides insights towards the design optimization of the gate stack of a modern ferroelectric field-effect transistor for improved reliability.

Yurchuk, E. et al. Origin of the endurance degradation in the novel HfO2-based 1T ferroelectric non-volatile memories. In 2014 IEEE Int. Reliability Physics Symposium 2E.5.1–2E.5.5 (IEEE, 2014).

Toprasertpong, K., Takenaka, M. & Takagi, S. Direct observation of interface charge behaviors in FeFET by quasi-static split CV and Hall techniques: Revealing FeFET operation. In 2019 IEEE Int. Electron Devices Meeting (IEDM) 23.7.1–23.7.4 (IEEE, 2019). This work demonstrated a method to calculate the number of trapped carriers at the interfaces that screen the ferroelectric polarization in a ferroelectric field-effect transistor.

Tan, A. et al. Hot electrons as the dominant source of degradation for sub-5nm HZO FeFETs. In 2020 Symposium on VLSI Technology (IEEE, in the press).

Ando, T. Ultimate scaling of high-κ gate dielectrics: Higher-κ or interfacial layer scavenging? Materials 5, 478–500 (2012).

Cheng, C.-H. & Chin, A. Low-leakage-current DRAM-like memory using a one-transistor ferroelectric MOSFET with a Hf-based gate dielectric. IEEE Electron Device Lett. 35, 138–140 (2013).

Khanna, S. et al. An FRAM-based nonvolatile logic MCU SoC Exhibiting 100% digital state retention at VDD= 0 V Achieving Zero Leakage With < 400-ns Wakeup Time for ULP Applications. IEEE J. Solid-State Circ. 49, 95–106 (2013).

Moise, T. et al. Demonstration of a 4 Mb, high density ferroelectric memory embedded within a 130 nm, 5 LM Cu/FSG logic process. In Digest Int. Electron Devices Meeting 535–538 (IEEE, 2002).

A century of ferroelectricity. Nat. Mater. 19, 129 (2020).

Meterelliyoz, M. et al. 2nd generation embedded DRAM with 4X lower self refresh power in 22 nm Tri-Gate CMOS technology. In 2014 Symposium on VLSI Circuits Digest of Technical Papers https://doi.org/10.1109/VLSIC.2014.6858415 (IEEE, 2014).

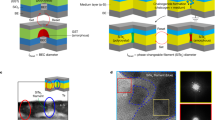

Lombardo, S. et al. Atomic-scale imaging of polarization switching in an (anti-)ferroelectric memory material: Zirconia (ZrO2). In 2020 Symposium on VLSI Technology (in the press). This work studied the microstructural evolution during polarization switching in antiferroelectric zirconium oxide using in-situ transmission electron microscopy.

Acknowledgements

This work was supported by the Applications and Systems-Driven Center for Energy-Efficient Integrated Nano Technologies (ASCENT), one of six centers in the Joint University Microelectronics Program (JUMP), an SRC program sponsored by the Defense Advanced Research Program Agency (DARPA), the Center for Advanced Self-Powered Systems of Integrated Sensors and Technologies (ASSIST), an Engineering Research Center sponsored by the National Science Foundation (NSF), and the National Science Foundation (grant no. 1810005). We thank S. Yu, S. Mahapatra, W. van den Hoek, A. Raychowdhury, S. Salahuddin, K. Ni, S. Gupta, S.K. Thirumala, M.M. Islam and M. Hoffmann for insightful discussions.

Author information

Authors and Affiliations

Contributions

All authors discussed the ideas and wrote the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare that they have no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Khan, A.I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat Electron 3, 588–597 (2020). https://doi.org/10.1038/s41928-020-00492-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-020-00492-7

This article is cited by

-

Realization of sextuple polarization states and interstate switching in antiferroelectric CuInP2S6

Nature Communications (2024)

-

Giant tunnelling electroresistance in atomic-scale ferroelectric tunnel junctions

Nature Communications (2024)

-

High-performance ferroelectric field-effect transistors with ultra-thin indium tin oxide channels for flexible and transparent electronics

Nature Communications (2024)

-

Transistors with ferroelectric ZrXAl1−XOY crystallized by ZnO growth for multi-level memory and neuromorphic computing

Communications Materials (2024)

-

A ferroelectric fin diode for robust non-volatile memory

Nature Communications (2024)